# Low-Voltage Micropower Latch for Industrial Applications

### FEATURES AND BENEFITS

- 2.2 to 5.5 V operation

- Ultra-low power consumption (micropower)

- Omnipolar and unipolar latch threshold options

- Sleep time options

- High and low sensitivity magnetic latch point options

- Choice of output polarity

- Chopper stabilization

Low latch point drift over temperature

- □ Insensitive to physical stress

- Push-pull output

- Solid-state reliability

**APPLICATIONS**

E-mobility

Home appliances

.

Brushless DC motors Medical equipment

Battery-critical applications

Incremental rotary encoding

Smart meters, flow meters

Doors, covers, lids, and tray position detection

· Industry-standard package and pinout

### DESCRIPTION

The APS12753 micropower Hall-effect latch ICs are qualified for low-voltage applications. These sensors are temperature-stable and suited for operation over extended junction temperature ranges up to 165°C. This family of Hall-effect latches provides contactless control of a push-pull output, which actuates in response to a magnetic field applied to the branded package face. Additionally, the micropower logic allows ultra-low power consumption and operation from 2.2 to 5.5 V.

These devices are equipped with chopper stabilization, which reduces the residual offset normally caused by device overmolding, temperature dependencies, and thermal stress, allowing superior high-temperature performance.

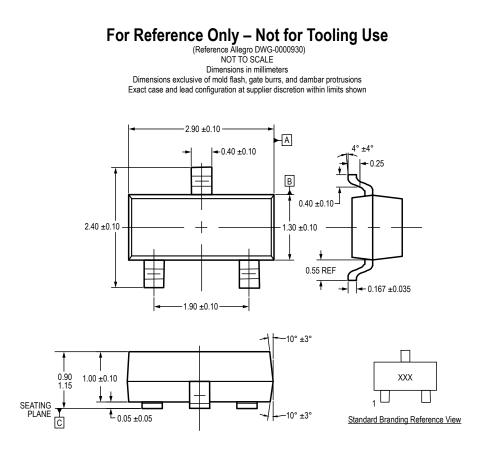

The APS12753 is offered in package type MD-3, a standard 3-pin SOT23-3 surface-mount package. The package is lead (Pb) free.

#### PACKAGE

Not to scale

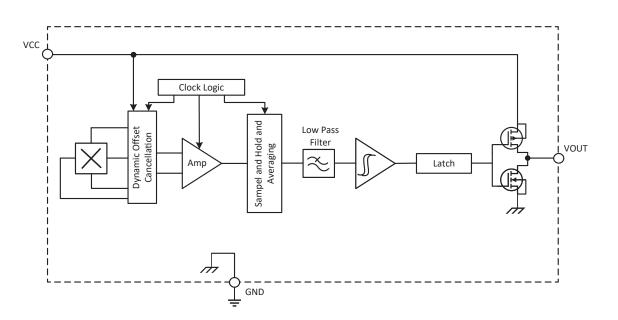

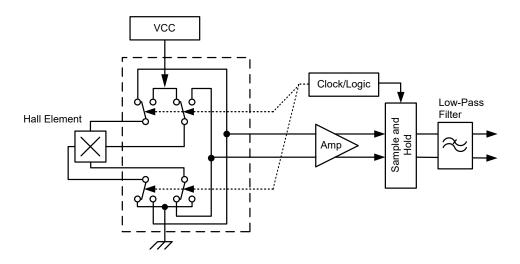

#### Figure 1: Functional Block Diagram

# Low-Voltage Micropower Latch for Industrial Applications

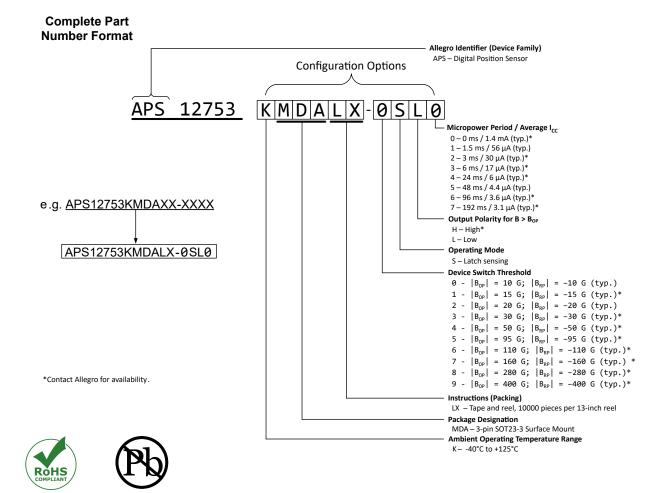

#### SELECTION

#### GUIDE

| Part Number <sup>[1]</sup> | Sleep Time | Average                | Typ. Latch Point Magnitude |                     | Operating           | Marratian     | Packing <sup>[2]</sup>            |

|----------------------------|------------|------------------------|----------------------------|---------------------|---------------------|---------------|-----------------------------------|

|                            | (ms)       | Supply<br>Current (µA) | B <sub>OP</sub> (G)        | B <sub>RP</sub> (G) | Temperature<br>(°C) | Mounting      | Facking                           |

| APS12753KMDALX-0SL5        | 1.5        | 56                     | 10                         | -10                 |                     | 3-pin SOT23-3 | Tape and Reel,                    |

| APS12753KMDALX-2SL5        | 50         | 4.4                    | 20                         | -20                 | -40 to 125          | surface mount | 10,000 pieces per<br>13-inch reel |

<sup>[1]</sup> Contact Allegro MicroSystems for options not listed in the selection guide. <sup>[2]</sup> Contact Allegro MicroSystems for additional packing options.

# Low-Voltage Micropower Latch for Industrial Applications

#### **ABSOLUTE MAXIMUM RATINGS**

| Characteristic                | Symbol Notes        |                | Rating     | Units |  |

|-------------------------------|---------------------|----------------|------------|-------|--|

| Supply Voltage                | V <sub>CC</sub>     |                | 6          | V     |  |

| Reverse Supply Voltage        | V <sub>RCC</sub>    |                | -0.3       | V     |  |

| Output Current                | I <sub>OUT</sub>    | Source or sink | ±5         | mA    |  |

| Operating Ambient Temperature | T <sub>A</sub>      | Range K        | -40 to 125 | °C    |  |

| Maximum Junction Temperature  | T <sub>J(max)</sub> |                | 165        | °C    |  |

| Storage Temperature           | T <sub>stg</sub>    |                | –65 to 170 | °C    |  |

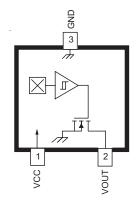

### PINOUT DIAGRAM AND TERMINAL LIST

(View from branded face)

| Terminal List |                                |        |  |  |  |  |

|---------------|--------------------------------|--------|--|--|--|--|

| Name          | Description                    | Number |  |  |  |  |

| VCC           | Connects power supply to chip  | 1      |  |  |  |  |

| VOUT          | Output from circuit            | 2      |  |  |  |  |

| GND           | Terminal for ground connection | 3      |  |  |  |  |

3-pin SOT23-3 (suffix MD)

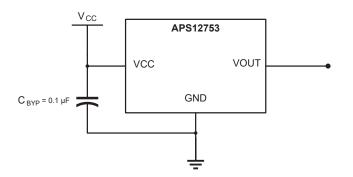

#### **TYPICAL APPLICATION CIRCUIT**

Figure 2: Typical Application Circuit

## ELECTRICAL CHARACTERISTICS <sup>[1]</sup>: Valid over full operating voltage and ambient temperature ranges for T<sub>J</sub> < T<sub>J</sub>(max) and

$C_{BYP}$  = 0.1 µF, unless otherwise specified

| Characteristics              | Symbol                              | Test Conditions                          | Min.                  | Typ. <sup>[2]</sup>   | Max.  | Unit |

|------------------------------|-------------------------------------|------------------------------------------|-----------------------|-----------------------|-------|------|

| SUPPLY AND STARTUP           | ·                                   |                                          |                       |                       |       |      |

| Supply Voltage               | V <sub>CC</sub>                     | Operating, T <sub>J</sub> < 165°C        | 2.2                   | _                     | 5.5   | V    |

|                              | T [3]                               | -xxx5 option: 48 ms sleep period         | _                     | 4.4                   | 11.5  | μA   |

|                              | I <sub>CC(AVG)</sub> <sup>[3]</sup> | -xxx1 option: 1.5 ms sleep period        | _                     | 56.4                  | 251.8 | μA   |

| Cumple Cumpet                |                                     | Device is awake, V <sub>CC</sub> = 2.2 V | _                     | 1                     | 1.5   | mA   |

| Supply Current               | I <sub>CC(AWAKE)</sub>              | Device is awake, V <sub>CC</sub> = 3.5 V | _                     | 1.4                   | 2.3   | mA   |

|                              |                                     | Device is awake, V <sub>CC</sub> = 5.5 V | _                     | 2.2                   | 3.5   | mA   |

|                              | I <sub>CC(SLEEP)</sub>              | Device is asleep                         | _                     | 2.7                   | 6     | μA   |

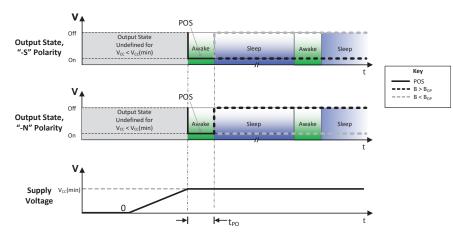

| Power-On State [4]           | POS                                 |                                          |                       | Low                   | Low   |      |

| Power-On Time <sup>[4]</sup> | t <sub>PO</sub>                     | $V_{CC} \ge V_{CC(min)}$                 | _                     | 60                    | 100   | μs   |

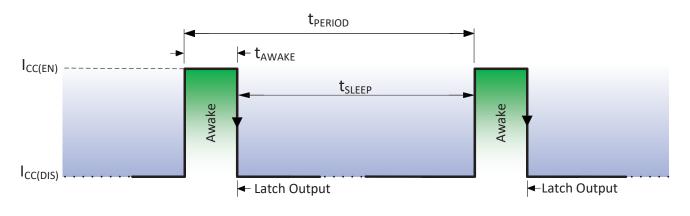

| MICROPOWER OPERATION (       | See Figure 6)                       |                                          |                       |                       |       |      |

| Awake                        | t <sub>AWAKE</sub>                  |                                          | -                     | -                     | 60    | μs   |

| Sleep                        |                                     | -xxx5 option                             | 25                    | 48                    | 90    | ms   |

|                              | t <sub>SLEEP</sub>                  | -xxx1 option                             | 0.5                   | 1.5                   | 2.5   | ms   |

| CHOPPER STABILIZATION A      | ND OUTPUT CHAR                      | ACTERISTICS                              |                       |                       |       |      |

| Chopping Frequency           | f <sub>c</sub>                      |                                          | _                     | 250                   | _     | kHz  |

| Output Saturation Voltage    | V <sub>OUT(SAT)HIGH</sub>           | I <sub>OUT</sub> = 1 mA (Sink)           | V <sub>CC</sub> - 300 | V <sub>CC</sub> – 150 | _     | mV   |

|                              | V <sub>OUT(SAT)LOW</sub>            | I <sub>OUT</sub> = 1 mA (Source)         | _                     | 150                   | 300   | mV   |

| Supply Slew Rate             | SR                                  |                                          | 20                    | -                     | _     | V/ms |

<sup>[1]</sup> Temperature performance is guaranteed by design and characterization.

$^{[2]}$  Typical data is at  $T_A$  = 25°C and  $V_{CC}$  = 3.5 V unless otherwise noted.

$^{[3]}\ensuremath{\mathsf{I}_{CC}}$  average is calculated with the equation:

$$I_{CC(awake)} \times t_{awake} + I_{CC(sleep)} \times t_{sleep}$$

$t_{awake} + t_{sleep}$

<sup>[4]</sup> Guaranteed by device design and characterization; not tested in final production.

Figure 3: Device Power-on Behavior ("L" Polarity Shown) The output remains latched in the last sampled state during the sleep time (output on or output off).

### **MAGNETIC SWITCH CHARACTERISTICS** [1]: Valid over full operating voltage and ambient temperature ranges for $T_J < T_J(max)$

and  $C_{BYP}$  = 0.1 µF, unless otherwise specified

| Characteristics | Symbol           | Test Conditions | Min. | Typ. [2] | Max. | Unit <sup>[3]</sup> |

|-----------------|------------------|-----------------|------|----------|------|---------------------|

| Operate Reint   | Р                | -0xx Option     | 1    | 10       | 20   | G                   |

| Operate Point   | B <sub>OP</sub>  | -2xx Option     | 5    | 20       | 35   | G                   |

| Release Deint   | B <sub>RP</sub>  | -0xx Option     | -20  | -10      | -1   | G                   |

| Release Point   |                  | -2xx Option     | -35  | -20      | -5   | G                   |

| Livetorogia     | Р                | -0xx Option     | 2    | 20       | 40   | G                   |

| Hysteresis      | B <sub>HYS</sub> | -2xx Option     | 10   | 40       | 70   | G                   |

<sup>[1]</sup> Temperature performance is guaranteed by design and characterization.

$^{[2]}$  Typical data is at  $T_{A}$  = 25°C and Vcc = 3.5 V, unless otherwise noted.

[3] Magnetic flux density, B, is indicated as a negative value for north-polarity magnetic fields, and a positive value for south-polarity magnetic fields.

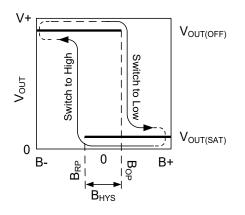

#### Figure 4: Hall Latch Output State vs. Magnetic Field

B- indicates increasing north polarity magnetic field strength, and B+ indicates increasing south polarity magnetic field strength.

# Low-Voltage Micropower Latch for Industrial Applications

PACKAGE THERMAL CHARACTERISTICS: Device power consumption is extremely low. On-chip power dissipation will not be an issue under normal operating conditions.

| Characteristic             | Symbol           | Test Conditions                | Value | Units |

|----------------------------|------------------|--------------------------------|-------|-------|

| Package Thermal Resistance | P                | Package MD, 2-layer PCB (1S0P) |       | °C/W  |

| Package mermai Resistance  | R <sub>0JA</sub> | Package MD, 4-layer PCB (2S2P) | 203.6 | °C/W  |

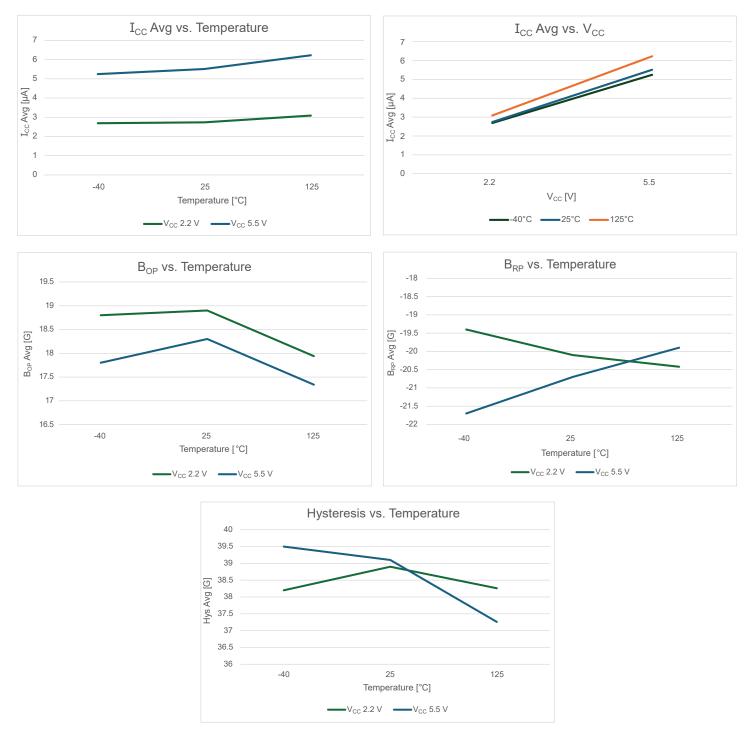

### APS12753-2SL5 CHARACTERIZATION PLOTS

### Low-Voltage Micropower Latch for Industrial Applications

### FUNCTIONAL DESCRIPTION

#### Operation

The APS12753 is an integrated Hall-effect sensor ICs with a latch output. The output is a push-pull configuration that actuates in response to a magnetic field applied to the branded package face (Figure 4). The devices are offered in package with a 3-pin surface-mount configuration. See the Selection Guide for a complete list of available options.

The difference in the magnetic operate and release points is the hysteresis,  $B_{HYS}$ , of the device. This built-in hysteresis allows clean latching of the output even in the presence of external mechanical vibration and electrical noise.

Powering-on the device in the hysteresis range (less than  $B_{OP}$  and higher than  $B_{RP}$ ) will give an output state of  $V_{OUT(OFF)}$ . In this case, the correct state is attained after the first excursion beyond  $B_{OP}$  or  $B_{RP}$ .

Figure 5: Magnetic Sensing Orientations

#### Low Average Power

The built-in micropower control periodically activates the Hall latch circuitry for a short period of time ( $t_{AWAKE}$ ), and deactivates it for the remainder of the period ( $t_{PERIOD}$ ). See Figure 6: Micropower Operation, for an example of the system timing. The short duration awake state allows for sensor stabilization prior

to sampling the Hall latch and latching the state on the output. The output is latched on the falling edge of the timing pulse and held in the last sampled state during the sleep period; updates to the output only occur on the falling edge of the timing pulse. The micropower control operates independently of the output driver state. At initial power-on, the APS12753 will sample a  $t_{AWAKE}$  cycle before the first  $t_{SLEEP}$  cycle (see Figure 6).

Figure 6: Micropower Operation

### **CHOPPER STABILIZATION**

A limiting factor for latch point accuracy when using Hall-effect technology is the small signal voltage developed across the Hall plate. This voltage is proportionally small relative to the offset that can be produced at the output of the Hall sensor. This makes it difficult to process the signal and maintain an accurate, reliable output over the specified temperature and voltage range. Chopper Stabilization is a proven approach used to minimize Hall offset.

The Allegro technique, dynamic quadrature offset cancellation, removes key sources of the output drift induced by temperature and package stress. This offset reduction technique is based on a signal modulation-demodulation process. Figure 7: Model of Chopper Stabilization Circuit (Dynamic Offset Cancellation) illustrates how it is implemented.

The undesired offset signal is separated from the magnetically induced signal in the frequency domain through modulation. The subsequent demodulation acts as a modulation process for the offset causing the magnetically induced signal to recover its original spectrum at baseband while the dc offset becomes a high frequency signal. Then, using a low-pass filter, the signal passes while the modulated DC offset is suppressed. Allegro's innovative chopper-stabilization technique uses a high frequency clock.

The high-frequency operation allows a greater sampling rate that produces higher accuracy, reduced jitter, and faster signal processing. Additionally, filtering is more effective and results in a lower noise analog signal at the sensor output. Devices such as the APS12753 that use this approach have an extremely stable quiescent Hall output voltage, are immune to thermal stress, and have precise recoverability after temperature cycling. This technique is made possible through the use of a BiCMOS process which allows the use of low offset and low noise amplifiers in combination with high-density logic and sample and hold circuits.

Figure 7: Model of Chopper Stabilization Circuit (Dynamic Offset Cancellation)

### PACKAGE OUTLINE DRAWING

Figure 8: Package MD, 3-Pin SMD (SOT23-3)

## Low-Voltage Micropower Latch for Industrial Applications

#### **Revision History**

| Number | Date               | Description                                                                                                                                                             |

|--------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| _      | September 24, 2024 | Initial release                                                                                                                                                         |

| 1      | October 17, 2024   | Updated title, features and benefits, and description (page 1), selection guide (page 2), absolute maximum ratings table (page 3), and characterization plots (page 7). |

| 2      | December 6, 2024   | Updated Complete Part Number Format schematic (page 2)                                                                                                                  |

Copyright 2024, Allegro MicroSystems.

Allegro MicroSystems reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro's products are not to be used in any devices or systems, including but not limited to life support devices or systems, in which a failure of Allegro's product can reasonably be expected to cause bodily harm.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

Copies of this document are considered uncontrolled documents.

For the latest version of this document, visit our website: www.allegromicro.com