# **Data Sheet**

PRELIMINARY April 2006

# AR2317 Single Chip MAC/Baseband/Radio and Processor for 2.4 GHz Wireless LANs

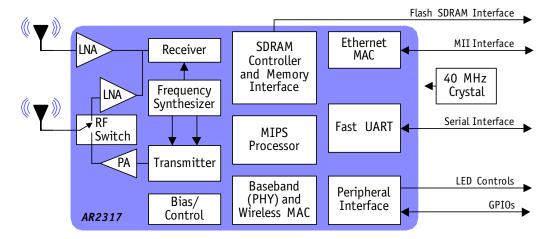

# **General Description**

The Atheros AR2317 is an all-CMOS, fullyintegrated, single-chip 802.11b/g WLAN solution. It integrates the PA, LNA, 2.4GHz radio, baseband PHY, MAC, and a MIPS 4000 CPU into a single chip for wireless access point and router applications. Other major modules include 802.3 Ethernet MAC and MII interface, SDRAM controller, external memory interface for Flash, ROM, or RAM, a UART, GPIOs as well as LED controls.

The AR2317 implements an 802.11 MAC/BB processor supporting all IEEE 802.11g data rates (1 to 54 Mbps) and all IEEE 802.11b complementary key coding (CCK) data rates (1 to 11 Mbps). Additional features include forward error correction coding at rates for 1/2, 2/3, and 3/4, signal detection, automatic gain control, frequency offset estimation, symbol timing, channel estimation, error recovery, enhanced security, and quality of service (QoS). The AR2317 performs receive and transmit filtering for IEEE 802.3 and 802.11 networks.

# Features

- Integrated high-output PA

- Integrated LNA/optional external LNA support

- Integrated 1.8 V voltage regulator; NO need for a 1.8 V supply

- Switched Rx antenna diversity

- Integrated Rx/Tx antenna switch

- Integrated power detector

- 25 MHz output for Ethernet switch

- Integrated MIPS 4000 processor

- 180 MHz processor frequency

- IEEE 802.11b/g Access Point, Ad Hoc, and station functions supported

- OFDM and CCK modulation schemes supported

- Data rates of 1, 2, 5.5, 6, 9, 11, 12, 18, 24, 36, 48, 54 Mbps

- IEEE 802.3 Ethernet MAC supporting 10/ 100 Mbps, full and half duplex, and MII interface to external Ethernet PHY

- UART for console support

- IEEE 1149.1 standard test access port and boundary scan architecture supported

- EJTAG based debugging of the processor core supported

- Standard 0.18 µm CMOS technology

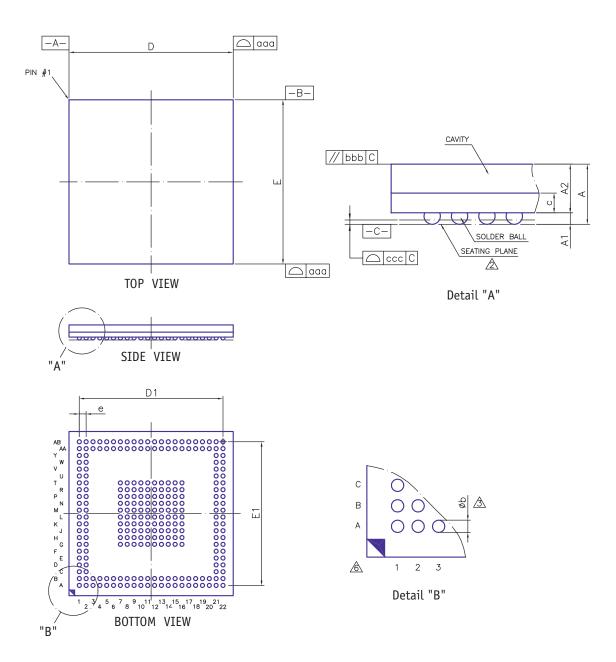

- 12 mm x 12 mm 260 BGA package

# System Block Diagram

© 2000-2006 by Atheros Communications, Inc. All rights reserved. Atheros<sup>TM</sup>, 5-UP<sup>TM</sup>, Driving the Wireless Future<sup>TM</sup>, Atheros Driven<sup>TM</sup>, Atheros Turbo Mode<sup>TM</sup>, and the Air is Cleaner at 5-GHz<sup>TM</sup> are trademarks of Atheros Communications, Inc. The Atheros logo is a registered trademark of Atheros Communications, Inc. All other trademarks are the property of their respective holders.

Subject to change without notice.

General Description 1 Features 1 System Block Diagram 1 1 Pin Descriptions 5 2 Electrical Characteristics 11 2.1 Absolute Maximum Ratings 11 2.1.1 Recommended Operating Conditions 11 2.2 General DC Electrical Characteristics 11 2.2.1 Radio Receiver Characteristics 12 2.2.2 Radio Transmitter Characteristics 13 2.2.3 Synthesizer Characteristics 14 2.3 Power Consumption 14 3 Register Descriptions 15 3.1 Reset/Configuration Control Registers 15 3.1.1 Cold Reset Control (RST\_COLD\_CTL) 16 3.1.2 Warm Reset Control (RST\_WARM\_CTL) 16 3.1.3 AHB Master Arbitration Control (RST\_AHB\_ARB\_CTL) 17 3.1.4 Byteswap Control (RST\_BYTESWAP\_CTL) 17 3.1.5 CPU Non-Maskable Interrupt (NMI) Control (RST\_NMI\_CTL) 18 3.1.6 Silicon Revision (RST\_SREV) 18 3.1.7 Miscellaneous Interrupt Status (RST\_MISR) 19 3.1.8 Miscellaneous Interrupt Mask (RST\_MIMR) 19 3.1.9 Global Interrupt Status (RST\_GISR) 20 3.1.10 General Timer (RST\_GTIME) 20 3.1.11 General Timer Reload Value (RST\_GTIME\_RELOAD) 20 3.1.12 Watchdog Timer (RST\_WDOG) 21 3.1.13 Watchdog Timer Control (RST\_WDOG\_CTL) 21 3.1.14 SDR-DRAM Memory Controller

Parameters (RST\_MEMCTL) 21 3.1.15 CPU Performance Counter Control (RST CPUPERF CTL) 22 3.1.16 CPU Performance Counter 0 (RST CPUPERF 0) 22 3.1.17 CPU Performance Counter 1 (RST\_CPUPERF\_1) 23 3.1.18 AHB Error Status Register 0 (RST\_AHBERR0) 23 3.1.19 AHB Error Status Register 1 (RST\_AHBERR1) 23 3.1.20 AHB Error Status Register 2 (RST\_AHBERR2) 24 3.1.21 AHB Error Status Register 3 (RST\_AHBERR3) 24 3.1.22 AHB Error Status Register 4 (RST\_AHBERR4) 24 3.1.23 CPU/AHB/APB PLL (PLLc) Control (RST\_PLLC\_CTL) 25 3.1.24 CPU Final Clock MUX/Divider Control (RST\_CPUCLK\_CTL) 26 3.1.25 AHB/APB Final Clock MUX/Divider Control (RST\_AMBACLK\_CTL) 26 3.1.26 GPIO Input, Set 0 (RST\_GPIOIN0) 26 3.1.27 GPIO Output, Set 0 (RST\_GPIOOUT0) 27 3.1.28 GPIO Direction, Set 0 (RST\_GPIODIR0) 27 3.1.29 GPIO Interrupt Control (RST\_GPIOINTR) 27 3.1.30 Scratch Register 0 (RST\_SCRATCH0) 28 3.1.31 Scratch Register 1 (RST\_SCRATCH1) 28 3.1.32 Observation Control (RST\_OBS\_CTL) 28 3.1.33 General Clock Control (RST\_MISCCLK\_CTL) 29 3.1.34 Client Interrupt Mask (RST CIMR) 29 3.1.35 PLL Programming Notes 30 3.2 SDR-DRAM Controller Registers 31 3.2.1 SDR-DRAM Configuration Register (MEMCTL\_SCONR) 31

- 3.2.2 SSDR-DRAM Timing Register 0 (MEMCTL\_STMG0R) 32

- 3.2.3 SDR-DRAM Timing Register 1 (MEMCTL\_STMG1R) 32

- 3.2.4 SDR-DRAM Control Register (MEMCTL\_SCTLR) 33

- 3.2.5 SDR-DRAM Refresh Interval Register (MEMCTL\_SREFR) 33

- 3.3 UART Registers 34

- 3.3.1 Receive Buffer Register (UART\_RBR); Transmit Holding Register (UART\_THR); Divisor Latch Low Register (UART\_DLL) 34

- 3.3.2 Interrupt Enable Register (UART\_IER); Divisor Latch High (UART\_DLH) 34

- 3.3.3 Interrupt Identity Register (UART\_IIR); FIFO Control Register (UART\_FCR) 35

- 3.3.4 Line Control Register (UART\_LCR) 35

- 3.3.5 Modem Control Register (UART\_MCR) 36

- 3.3.6 Line Status Register (UART\_LSR) 36

- 3.3.7 Modem Status Register (UART\_MSR) 37

- 3.3.8 Scratch Register (UART\_SCR) 37

- 3.4 SPI Flash Interface Registers 38

- 3.4.1 SPI Control/Status (SPI\_CS) 38

- 3.4.2 SPI Address/Opcode (SPI\_AO) 39

- 3.4.3 SPI Data (SPI\_D) 39

- 3.4.4 SPI Register Notes 39

- 4 Package Dimensions 41

- 5 Ordering Information 43

COR

# 1. Pin Descriptions

This section contains both a package pinout (see Table 1-1 through Table 1-3) and tabular listings of the signal descriptions.

The following nomenclature is used for signal names:

- NC indicates no connection should be made to this pin.

- L at the end of the signal name indicates active low signal.

- P at the end of the signal name indicates the positive side of a differential signal.

- N at the end of the signal name indicates the negative side of a differential signal.

The following nomenclature is used for signal types:

- IA indicates an analog input signal.

- I indicates a digital input signal.

- IH indicates input signals with weak internal pull-up, to prevent signals from floating when left open.

- IL indicates input signals with weak internal pull-down, to prevent signals from floating when left open.

- I/O indicates a digital bidirectional signal.

- OA indicates an analog output signal.

- O indicates a digital output signal.

P indicates a power or ground signal.

|    | 1                | 2                | 3                | 4          | 5          | 6         | 7            | 8         | 9         | 10        | 11       |

|----|------------------|------------------|------------------|------------|------------|-----------|--------------|-----------|-----------|-----------|----------|

| A  | GND              | GND              | VDD18_<br>BYPASS | SD_DATA_14 | SD_DATA_15 | GPIO_2    | GPIO_7       | GPIO_5    | GPIO_3    | NC        | AVDD33   |

| В  | GND              | GND              | GND              | SD_DATA_1  | SD_DATA_13 | SD_DATA_0 | PROC_REF_CLK | GPIO_4    | GPIO_1    | GPIO_0    | AVDD33   |

| C  | VDD33            | GND              | NA               | NA         | NA         | NA        | NA           | NA        | NA        | NA        | NA       |

| D  | SD_DATA_12       | SD_DATA_2        | NA               | NA         | NA         | NA        | NA           | NA        | NA        | NA        | NA       |

| Ε  | SD_DATA_11       | SD_DATA_3        | NA               | NA         | NA         | NA        | NA           | NA        | NA        | NA        | NA       |

| F  | SD_DATA_5        | SD_DATA_4        | NA               | NA         | NA         | NA        | NA           | NA        | NA        | NA        | NA       |

| G  | SD_DATA_6        | SD_DATA_10       | NA               | NA         | NA         | NA        | GND          | GND       | GND       | GND       | GND      |

| H  | SD_DATA_7        | SD_DATA_9        | NA               | NA         | NA         | NA        | GND          | GND       | GND       | GND       | GND      |

| J  | VDD33            | SD_DATA_8        | NA               | NA         | NA         | NA        | GND          | GND       | GND       | GND       | GND      |

| К  | VDD33            | VDD33            | NA               | NA         | NA         | NA        | GND          | GND       | GND       | GND       | GND      |

| L  | VDD33            | VDD33            | NA               | NA         | NA         | NA        | GND          | GND       | GND       | GND       | GND      |

| м  | VDD18_<br>BYPASS | VDD18_<br>BYPASS | NA               | NA         | NA         | NA        | GND          | GND       | GND       | GND       | GND      |

| N  | VDD18_<br>BYPASS | VDD18_<br>BYPASS | NA               | NA         | NA         | NA        | GND          | GND       | GND       | GND       | GND      |

| P  | SD_DQM_0         | DLDO_PWD         | NA               | NA         | NA         | NA        | GND          | GND       | GND       | GND       | GND      |

| R  | DLDO_SEL1        | SD_WE_L          | NA               | NA         | NA         | NA        | GND          | GND       | GND       | GND       | GND      |

| T  | DLDO_SEL0        | SD_DQM_1         | NA               | NA         | NA         | NA        | GND          | GND       | GND       | GND       | GND      |

| U  | SD_CAS_L         | SD_CLK_FB        | NA               | NA         | NA         | NA        | NA           | NA        | NA        | NA        | NA       |

| V  | SD_CKE           | SD_CLK           | NA               | NA         | NA         | NA        | NA           | NA        | NA        | NA        | NA       |

| W  | SD_RAS_L         | SD_ADDR_12       | NA               | NA         | NA         | NA        | NA           | NA        | NA        | NA        | NA       |

| Y  | VDD18_<br>BYPASS | GND              | NA               | NA         | NA         | NA        | NA           | NA        | NA        | NA        | NA       |

| AA | GND              | GND              | GND              | SD_ADDR_11 | SD_ADDR_9  | SD_ADDR_8 | SD_ADDR_7    | SD_ADDR_6 | SD_ADDR_5 | SD_ADDR_4 | CLK_25   |

|    | GND              | GND              | VDD33            | SD_CS_L    | SD_BANK_1  | SD_BANK_0 | SD_ADDR_10   | SD_ADDR_0 | SD_ADDR_1 | SD_ADDR_2 | SD_ADDR_ |

Table 1-1. AR2317 Pin Assignments (1–11)

|    | 12        | 13          | 14       | 15       | 16        | 17        | 18        | 19        | 20               | 21        | 22               |

|----|-----------|-------------|----------|----------|-----------|-----------|-----------|-----------|------------------|-----------|------------------|

| Α  | RFANT1P   | RFANT1P     | RFANT1N  | RFANT1N  | PABIAS    | AVDD33    | RFANT2N   | RFANT2P   | AVDD33           | GND       | GND              |

| В  | PABIAS    | PABIAS      | PABIAS   | PABIAS   | PABIAS    | AVDD33    | GND       | ALDO_PWD  | GND              | GND       | GND              |

| С  | NA        | NA          | NA       | NA       | NA        | NA        | NA        | NA        | NA               | ATBN      | NC               |

| D  | NA        | NA          | NA       | NA       | NA        | NA        | NA        | NA        | NA               | ALDO_SEL1 | ALDO_SEL(        |

| E  | NA        | NA          | NA       | NA       | NA        | NA        | NA        | NA        | NA               | AVDD33    | RXVDD_<br>BYPASS |

| F  | NA        | NA          | NA       | NA       | NA        | NA        | NA        | NA        | NA               | AVDD33    | AVDD_BYPAS       |

| G  | GND       | GND         | GND      | GND      | GND       | NA        | NA        | NA        | NA               | AVDD33    | AVDD33           |

| Н  | GND       | GND         | GND      | GND      | GND       | NA        | NA        | NA        | NA               | RES       | RES              |

| J  | GND       | GND         | GND      | GND      | GND       | NA        | NA        | NA        | NA               | RES       | BIASREF          |

| к  | GND       | GND         | GND      | GND      | GND       | NA        | NA        | NA        | NA               | RES       | XTALI            |

| L  | GND       | GND         | GND      | GND      | GND       | NA        | NA        | NA        | NA               | AVDD33    | XTALO            |

| м  | GND       | GND         | GND      | GND      | GND       | NA        | NA        | NA        | NA               | UART_SOUT | UART_SIN         |

| N  | GND       | GND         | GND      | GND      | GND       | NA        | NA        | NA        | NA               | TCLK      | TMS              |

| Р  | GND       | GND         | GND      | GND      | GND       | NA        | NA        | NA        | NA               | TDO       | TDI              |

| R  | GND       | GND         | GND      | GND      | GND       | NA        | NA        | NA        | NA               | TRST_L    | GPIO_6           |

| т  | GND       | GND         | GND      | GND      | GND       | NA        | NA        | NA        | NA               | EJTAG_SEL | COLD_RST_1       |

| U  | NA        | NA          | NA       | NA       | NA        | NA        | NA        | NA        | NA               | SPI_CK    | VDD33            |

| v  | NA        | NA          | NA       | NA       | NA        | NA        | NA        | NA        | NA               | SPI_CS_L  | SPI_MOSI         |

| w  | NA        | NA          | NA       | NA       | NA        | NA        | NA        | NA        | NA               | ETH_TXD_0 | SPI_MISO         |

| Y  | NA        | NA          | NA       | NA       | NA        | NA        | NA        | NA        | NA               | GND       | ETH_TXD_1        |

| AA | ETH_COL   | ETH_MDC     | ETH_MDIO | ETH_TXC  | ETH_CRS   | ETH_RXD_2 | ETH_TXEN  | ETH_TXD_2 | GND              | GND       | GND              |

| AB | ETH_RXERR | ETH_RESET_L | ETH_RXC  | ETH_RXDV | ETH_RXD_0 | ETH_RXD_1 | ETH_RXD_3 | ETH_TXD_3 | VDD18_<br>BYPASS | GND       | GND              |

Table 1-2. AR2317 Pin Assignments (12-22)

7

| Table 1-3. Signal-to-Pin Relationships |                |            |                                                          |  |  |  |

|----------------------------------------|----------------|------------|----------------------------------------------------------|--|--|--|

| Signal Name                            | Pin            | Direction  | Description                                              |  |  |  |

| Radio Control                          |                |            |                                                          |  |  |  |

| RFANT1N                                | A14, A15       | О          | Antenna 1 interface. RF transmitter output and alternate |  |  |  |

| RFANT1P                                | A12, A13       | 0          | receiver input.                                          |  |  |  |

| RFANT2N                                | A18            | 0          | Antenna 2 interface. RF receiver input.                  |  |  |  |

| RFANT2P                                | A19            | 0          |                                                          |  |  |  |

| BIASREF                                | J22            | IA         | Connects a 6.19 K $\Omega$ ±1% resistor to ground        |  |  |  |

| ATBN                                   | C21            | 0          | Enable for optional external LNA                         |  |  |  |

| General                                |                |            | -                                                        |  |  |  |

| GPIO_0                                 | B10            | I/O        | General purpose GPIO pins                                |  |  |  |

| GPIO_1                                 | B9             | I/O        |                                                          |  |  |  |

| GPIO_2                                 | A6             | I/O        | -                                                        |  |  |  |

| GPIO_3                                 | A9             | I/O        | -                                                        |  |  |  |

| GPIO_4                                 | B8             | I/O        | -                                                        |  |  |  |

| GPIO_5                                 | A8             | I/O        |                                                          |  |  |  |

| GPIO_6                                 | R22            | I/O        |                                                          |  |  |  |

| GPIO_7                                 | A7             | I/O        |                                                          |  |  |  |

| COLD_RST_L                             | T22            | I          | Reset entire chip                                        |  |  |  |

| XTALI                                  | K22            | Ι          | 40 MHz crystal                                           |  |  |  |

| XTALO                                  | L22            | 0          | 40 MHz crystal                                           |  |  |  |

| PABIAS                                 | A16, B12, B13, | IA         | Connect to AVDD33                                        |  |  |  |

|                                        | B14, B15, B16  |            |                                                          |  |  |  |

| PROC_REF_CLK                           | B7             |            | Reserved, must be open                                   |  |  |  |

| Ethernet                               |                |            |                                                          |  |  |  |

| CLK_25                                 | AA11           | 0          | 25 MHz clock for external Ethernet hardware              |  |  |  |

| ETH_COL                                | AA12           | I          | Collision Detect                                         |  |  |  |

| ETH_CRS                                | AA16           | I          | Carrier Sense                                            |  |  |  |

| ETH_MDIO                               | AA14           | I/O        | PHY chip control bus data                                |  |  |  |

| ETH_MDC                                | AA13           | 0          | PHY chip control bus clock                               |  |  |  |

| ETH_RESET_L                            | AB13           | 0          | PHY Reset                                                |  |  |  |

| ETH_RXC                                | AB14           | Ι          | Receive Clock (2.5 MHz @ 10 Mb; 25 MHz @ 100 Mb)         |  |  |  |

| ETH_RXD_0                              | AB16           | Ι          | Receive Data                                             |  |  |  |

| ETH_RXD_1                              | AB17           | Ι          |                                                          |  |  |  |

| ETH_RXD_2                              | AA17           | Ι          |                                                          |  |  |  |

| ETH_RXD_3                              | AB18           | Ι          |                                                          |  |  |  |

| ETH_RXDV                               | AB15           | Ι          | Receive Data Valid                                       |  |  |  |

| ETH_RXERR                              | AB12           | Ι          | Receive Error                                            |  |  |  |

| ETH_TXC                                | AA15           | Ι          | Transmit Clock (2.5 MHz @ 10 Mb; 25 MHz @ 100 Mb)        |  |  |  |

| ETH_TXD_0                              | W21            | 0          | Transmit Data                                            |  |  |  |

| ETH_TXD_1                              | Y22            | 0          |                                                          |  |  |  |

| ETH_TXD_2                              | AA19           | 0          |                                                          |  |  |  |

| ETH_TXD_3                              | AB19           | 0          |                                                          |  |  |  |

| ETH_TXEN                               | AA18           | 0          | Transmit Enable                                          |  |  |  |

| SDRAM Interface                        |                |            |                                                          |  |  |  |

| SD_DATA_15                             | A5             | I/O        | Read/write data [15]                                     |  |  |  |

| SD_DATA_14                             | A4             | I/O        | Read/write data [14]                                     |  |  |  |

| SD_DATA_13                             | B5             | I/O        | Read/write data [13]                                     |  |  |  |

| SD_DATA_12                             | D1             | I/O        | Read/write data [12]                                     |  |  |  |

| SD_DATA_11                             | E1             | I/O        | Read/write data [11]                                     |  |  |  |

| SD_DATA_10                             | G2             | I/O        | Read/write data [10]                                     |  |  |  |

|                                        |                |            |                                                          |  |  |  |

| SD DATA 9                              | H2             | 1/0        | Read/write data [9]                                      |  |  |  |

| SD_DATA_9<br>SD_DATA_8                 | H2<br>J2       | I/O<br>I/O | Read/write data [9]<br>Read/write data [8]               |  |  |  |

# Table 1-3 provides the signal-to-pinrelationship information for the AR2317.

*Table 1-3.* Signal-to-Pin Relationships

| Signal Name           | Pin        | Direction | Description                                                                                            |

|-----------------------|------------|-----------|--------------------------------------------------------------------------------------------------------|

| SD_DATA_6             | G1         | I/O       | Read/write data [6]                                                                                    |

| SD_DATA_5             | F1         | I/O       | Read/write data [5]                                                                                    |

| SD_DATA_4             | F2         | I/O       | Read/write data [4]                                                                                    |

| SD_DATA_3             | E2         | I/O       | Read/write data [3]                                                                                    |

| SD_DATA_2             | D2         | I/O       | Read/write data [2]                                                                                    |

| SD_DATA_1             | B4         | I/O       | Read/write data [1]                                                                                    |

| SD_DATA_0             | B6         | I/O       | Read/write data [0]                                                                                    |

| SD_CLK                | V2         | 0         | SDRAM clock                                                                                            |

| SD_CKE                | V1         | 0         | SDRAM clock enable                                                                                     |

| SD_CLK_FB             | U2         | I         | SDRAM clock feedback                                                                                   |

| SD_CAS_L              | U1         | 0         | Column address select                                                                                  |

| SD_RAS_L              | W1         | 0         | Row address select                                                                                     |

| SD_CS_L               | AB4        | 0         | Chip select for DRAM                                                                                   |

| SD_BANK_1             | AB5        | 0         | Bank address [1]                                                                                       |

| SD_BANK_0             | AB6        | 0         | Bank address [0]                                                                                       |

| SD_DQM_1              | T2         | 0         | Data mask for byte 1                                                                                   |

| SD_DQM_0              | P1         | 0         | Data mask for byte 0                                                                                   |

| SD_DQWL0              | R2         | 0         | Write enable                                                                                           |

| SD_ADDR_12            | W2         | 0         | Row/column address within bank                                                                         |

| SD_ADDR_12            | AA4        | 0         |                                                                                                        |

| SD_ADDR_10            | AB7        | 0         |                                                                                                        |

| SD_ADDR_9             | AA5        | 0         |                                                                                                        |

| SD_ADDR_9             | AA5<br>AA6 | 0         |                                                                                                        |

| SD_ADDR_8             |            | 0         |                                                                                                        |

|                       | AA7        | 0         |                                                                                                        |

| SD_ADDR_6             | AA8        | 0         |                                                                                                        |

| SD_ADDR_5             | AA9        |           |                                                                                                        |

| SD_ADDR_4             | AA10       | 0         |                                                                                                        |

| SD_ADDR_3             | AB11       | 0         |                                                                                                        |

| SD_ADDR_2             | AB10       | 0         |                                                                                                        |

| SD_ADDR_1             | AB9        | 0         |                                                                                                        |

| SD_ADDR_0             | AB8        | 0         |                                                                                                        |

| UART Control          |            |           |                                                                                                        |

| UART_SOUT             | M21        | 0         | Serial output data                                                                                     |

| UART_SIN              | M22        | I         | Serial input data                                                                                      |

| SPI Interface         |            |           |                                                                                                        |

| SPI_CK                | U21        | 0         | SPI Serial Flash Clock                                                                                 |

| SPI_CS_L              | V21        | 0         | SPI Serial Flash Chip Select                                                                           |

| SPI_MISO              | W22        | I         | SPI Serial Flash Data: Master In, Slave out                                                            |

| SPI_MOSI              | V22        | 0         | SPI Serial Flash Data: Master Out, Slave In                                                            |

| JTAG Interface        |            | -         |                                                                                                        |

| EJTAG_SEL             | T21        | Ι         | When asserted, JTAG pins are routed to EJATAG TAP controller.                                          |

| EJING_JEL             | 141        | 1         | When deasserted, JTAG pins are routed to EJATAG TAP controller.                                        |

| TCLK                  | N21        | Ι         | JTAG test clock                                                                                        |

| TDI                   | P22        | I         | JTAG test clock                                                                                        |

| TDO                   | P22<br>P21 | 1<br>0    | JTAG data input<br>JTAG data output                                                                    |

| TMS                   | N22        | -         | JTAG data output<br>JTAG test mode                                                                     |

| TRST_L                | R21        | I         | JTAG test mode<br>JTAG test reset                                                                      |

|                       | NZ1        | Ι         | JIAG lest feset                                                                                        |

| LDO Control           |            |           |                                                                                                        |

| ALDO_SEL0             | D22        | Ι         | Control signals for internal regulators. Connect to GND. These                                         |

| T TO OTT 1            | D21        | Ι         | signals have internal pull-up to 3.3 V.                                                                |

| ALDO_SEL1             |            | Т         |                                                                                                        |

| ALDO_PWD              | B19        | I         |                                                                                                        |

| ALDO_PWD<br>DLDO_SEL0 | B19<br>T1  | I         | Control signals for internal regulators. Connect to GND. These                                         |

| ALDO_PWD              |            | -         | Control signals for internal regulators. Connect to GND. These signals have internal pull-up to 3.3 V. |

Table 1-3. Signal-to-Pin Relationships (continued)

| Signal Name   | Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Description                                                                       |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| Power         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                   |

| AVDD_BYPASS   | F22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Analog 1.8 V voltage regulator output, to connect to 2.2 $\mu$ F bypass capacitor |

| AVDD33        | A11, A17, A20, B11, B17, E21, G21, G22, L21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Analog 3.3V supply                                                                |

| RXVDD_BYPASS  | E22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Analog 1.8 V voltage regulator output, to connect to 2.2 $\mu$ F bypass capacitor |

| VDD18_BYPASS  | A3, M1, M2, N1, N2, Y1, AB20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Digital 1.8 V voltage regulator output, to connect to 2.2 µF bypass capacitor     |

| VDD33         | C1, J1, K1, K2, L1, L2, U22, AB3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Digital 3.3 V                                                                     |

| GND           | <ul> <li>A1, A2, A21, A22, B1, B2, B3, B18, B20, B21,<br/>B22, C2, G7, G8, G9, G10, G11, G12, G13,<br/>G14, G15, G16, H7, H8, H9, H10, H11, H12,<br/>H13, H14, H15, H16, J7, J8, J9, J10, J11, J12,<br/>J13, J14, J15, J16, K7, K8, K9, K10, K11, K12,<br/>K13, K14, K15, K16, L7, L8, L9, L10, L11,<br/>L12, L13, L14, L15, L16, M7, M8, M9, M10,<br/>M11, M12, M13, M14, M15, M16, N7, N8,<br/>N9, N10, N11, N12, N13, N14, N15, N16, P7,<br/>P8, P9, P10, P11, P12, P13, P14, P15, P16, R7,<br/>R8, R9, R10, R11, R12, R13, R14, R15, R16,<br/>T7, T8, T9, T10, T11, T12, T13, T14, T15, T16,<br/>Y2, AA1, AA2, AA3, AA20, AA21, AA22,<br/>AB1, AB2, AB21, AB22</li> </ul>                                                                                                                                                                                                                                                                                                                                                              | Digital ground                                                                    |

| No Connection |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                   |

| NC            | A10, C22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | No connect                                                                        |

| RES           | H21, H22, J21, K21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Reserved, high impedance. Can be left open<br>or connect to any power level.      |

| NA            | C3, C4, C5, C6, C7, C8, C9, C10, C11, C12,<br>C13, C14, C15, C16, C17, C18, C19, C20, D3,<br>D4, D5, D6, D7, D8, D9, D10, D11, D12, D13,<br>D14, D15, D16, D17, D18, D19, D20, E3, E4,<br>E5, E6, E7, E8, E9, E10, E11, E12, E13, E14,<br>E15, E16, E17, E18, E19, E20, F3, F4, F5, F6,<br>F7, F8, F9, F10, F11, F12, F13, F14, F15, F16,<br>F17, F18, F19, F20, G3, G4, G5, G6, G17, G18,<br>G19, G20, H3, H4, H5, H6, H17, H18, H19,<br>H20, J3, J4, J5, J6, J17, J18, J19, J20, K3, K4,<br>K5, K6, K17, K18, K19, K20, L3, L4, L5, L6,<br>L17, L18, L19, L20, M3, M4, M5, M6, M17,<br>M18, M19, M20, N3, N4, N5, N6, N17, N18,<br>N19, N20, P3, P4, P5, P6, P17, P18, P19, P20,<br>R3, R4, R5, R6, R17, R18, R19, R20, T3, T4,<br>T5, T6, T17, T18, T19, T20, U3, U4, U5, U6,<br>U7, U8, U9, U10, U11, U12, U13, U14, U15,<br>U16, U17, U18, U19, U20, V3, V4, V5, V6,<br>V7, V8, V9, V10, V11, V12, V13, V14, V15,<br>V16, V17, V18, V19, V20, Y3, Y4, Y5, Y6, Y7,<br>Y8, Y9, Y10, Y11, Y12, Y13, Y14, Y15, Y16,<br>Y17, Y18, Y19, Y20 | Not Applicable                                                                    |

# Table 1-4. Signal-to-Pin Relationships

# 2. Electrical Characteristics

# 2.1 Absolute Maximum Ratings

Table 2-1 summarizes the absolute maximumratings and Table 2-2 lists the recommendedoperating conditions for the AR2317. Absolute

#### Table 2-1. Absolute Maximum Ratings

Symbol Parameter Max. Rating Unit V V<sub>DD33</sub> I/O Supply Voltage (3.3 V) -0.3 to 4.6 °C Storage Temperature -65 to 150 T<sub>store</sub> ESD 2000 V Electrostatic Discharge Tolerance

# 2.1.1 Recommended Operating Conditions

#### Table 2-2. Recommended Operating Conditions

| Symbol            | Parameter                       | Conditions | Min | Тур | Max | Unit |

|-------------------|---------------------------------|------------|-----|-----|-----|------|

| V <sub>DD33</sub> | I/O Supply Voltage              | ± 10%      | 3.0 | 3.3 | 3.6 | V    |

| T <sub>case</sub> | Case Temperature                |            | 0   | 45  | 105 | °C   |

| T <sub>J</sub>    | Junction Temperature            |            | 0   | 50  | 115 | °C   |

| $\theta_{JA}$     | Junction to Ambient Temperature |            |     |     | 33  | °C/W |

# 2.2 General DC Electrical Characteristics

to all DC characteristics unless otherwise specified:

Table 2-3 lists the general DC electrical

characteristics. The following conditions apply

$V_{dd} = 3.3 \text{ V}, T_{amb} = 25 \text{ }^{\circ}\text{C}$

# Table 2-3. General DC Electrical Characteristics

| Symbol          | Parameter                 | Conditions                      | Min                  | Тур  | Max                   | Unit |

|-----------------|---------------------------|---------------------------------|----------------------|------|-----------------------|------|

| V <sub>IH</sub> | High Level Input Voltage  | $V_{out} = V_{OH (min)}$        | 2.0                  | _    | V <sub>dd</sub> + 0.3 | V    |

| V <sub>IL</sub> | Low Level Input Voltage   | $V_{out} = V_{OL (min)}$        | -0.3                 |      | 0.8                   | V    |

| $I_{IL}$        | Input Leakage Current     | Without Pull-up or<br>Pull-down |                      | ± 5  |                       | μA   |

|                 |                           | With Pull-up or<br>Pull-down    |                      | ± 65 | _                     | μA   |

| V <sub>OH</sub> | High Level Output Voltage | No Load $(I_0 = 0)$             | V <sub>dd</sub> -0.3 | _    | —                     | V    |

|                 |                           | $I_0 = 12 \text{ mA}$           | V <sub>dd</sub> -0.8 |      |                       | V    |

| V <sub>OL</sub> | Low Level Output Voltage  | No Load $(I_0 = 0)$             | —                    | —    | 0.20                  | V    |

|                 |                           | $I_o = 12 \text{ mA}$           | —                    | —    | 0.27                  | V    |

| I <sub>O</sub>  | Output Current            | $V_0 = 0$ to $V_{dd}$           | —                    | —    | 6 <sup>[1]</sup>      | mA   |

| C <sub>IN</sub> | Input Capacitance         | —                               |                      | 6    |                       | pF   |

[1]Note these exceptions: the pins SD\_ADDR[12:0] are 2 mA, SD\_DATA[15:0] are 2mA, and TDO is 8 mA.

# 2.2.1 Radio Receiver Characteristics

Table 2-4 summarizes the receiver characteristics for the AR2317.

| Symbol                  | Parameter                                    | Conditions                  | Min   | Тур | Max   | Unit   |

|-------------------------|----------------------------------------------|-----------------------------|-------|-----|-------|--------|

| F <sub>rx</sub>         | Receive input frequency range                | 5 MHz center<br>frequency   | 2.312 |     | 2.484 | GHz    |

| NF                      | Receive chain noise figure                   | _                           | _     | 6   | _     | dB     |

| S <sub>rf</sub>         | Sensitivity                                  | See Note <sup>[1]</sup>     |       |     |       | dBm    |

|                         | CCK, 1 Mbps                                  |                             | _     | -96 |       |        |

|                         | CCK, 11 Mbps                                 |                             | —     | -88 | —     |        |

|                         | OFDM, 6 Mbps                                 |                             | —     | -91 | _     |        |

|                         | OFDM, 54 Mbps                                |                             | —     | -74 | —     |        |

| IP1dB                   | Input 1 dB compression (min. gain)           | _                           | —     | -10 | _     | dBm    |

| IIP3                    | Input third intercept point<br>(min. gain)   | _                           | _     | -1  | —     | dBm    |

| Z <sub>RFin_input</sub> | Recommended LNA differential drive impedance | See Note <sup>[2]</sup>     |       | TBD | _     |        |

| ERphase                 | I,Q phase error                              |                             |       | 1   | _     | degree |

| ERamp                   | I,Q amplitude error                          |                             |       | 0.9 | _     | dB     |

| R <sub>adj</sub>        | Adjacent channel rejection                   | 10 to 20 MHz <sup>[3]</sup> |       | ~   |       | dB     |

|                         | ССК                                          |                             | 35    |     |       |        |

|                         | OFDM, 6 Mbps                                 |                             | 16    | 40  |       |        |

|                         | OFDM, 54 Mbps                                |                             | -1    | 20  | —     |        |

| TRpowup                 | Time for power up (from synth on)            | —                           | _     | 1   | _     | μs     |

#### Table 2-4. Receiver Characteristics for Antenna 2 (Primary Receiver)

[1]Performance is based on the Atheros reference design.

[2]Refer to the *Hardware Design Guide* for information. [3]Measured with AR2317.

# 2.2.2 Radio Transmitter Characteristics

Table 2-5 summarizes the transmitter characteristics for the AR2317.

| Symbol                          | Parameter                                      | Conditions              | Min   | Тур                 | Max   | Unit |

|---------------------------------|------------------------------------------------|-------------------------|-------|---------------------|-------|------|

| F <sub>tx</sub>                 | Transmit output frequency range                | 5 MHz center            | 2.312 | —                   | 2.484 | GHz  |

|                                 |                                                | frequency               |       |                     |       |      |

| P <sub>out</sub> <sup>[1]</sup> | EVM and mask compliant CCK output power        | 1–11 Mbps               | _     | 20 <sup>[2]</sup>   | —     | dBm  |

|                                 | EVM and mask compliant OFDM                    | 6–24 Mbps               | —     | 20 <sup>[2]</sup>   |       |      |

|                                 | output power                                   | 36 Mbps                 |       | 19 <sup>[2]</sup>   | -     |      |

|                                 |                                                | 48 Mbps                 |       | 17.5 <sup>[2]</sup> | -     |      |

|                                 |                                                | 54 Mbps                 | —     | 15.5 <sup>[2]</sup> | —     | -    |

| SPgain                          | PA gain step                                   |                         |       | 0.5                 | -     | dB   |

| A <sub>pl</sub>                 | Accuracy of power leveling loop                | See Note <sup>[3]</sup> | —     | ±1                  | —     | dB   |

| Z <sub>RFout_load</sub>         | Recommended PA differential load impedance     | See Note <sup>[4]</sup> |       | TBD                 |       | -    |

| OP1dB                           | Output P1dB (max. gain)                        | 2.442 GHz               |       | 20                  | —     | dBm  |

|                                 | Output third order intercept point (max. gain) | 2.442 GHz               |       | 30                  |       | dBm  |

| SS                              | Sideband suppression                           |                         | -     | TBD                 |       | dBc  |

| RS                              | Synthesizer reference spur:                    |                         | —     | TBD                 |       | dBc  |

| Tx <sub>mask</sub>              | Transmit spectral mask                         |                         |       |                     |       | dBr  |

|                                 | ССК                                            |                         |       |                     |       |      |

|                                 | At 11 MHz offset                               |                         | -30   | -40                 |       |      |

|                                 | At 22 MHz offset                               |                         | -50   | -54                 | —     |      |

|                                 | OFDM                                           |                         |       |                     |       |      |

|                                 | At 11 MHz offset                               |                         | -20   | -23                 | _     |      |

|                                 | At 20 MHz offset                               |                         | -28   | -36                 | _     |      |

|                                 | At 30 MHz offset                               |                         | -40   | -55                 | —     |      |

| TTpowup                         | Time for power up (from synth on)              | —                       |       | 1.5                 | _     | μs   |

Table 2-5. Transmitter Characteristics for Antenna 1

[1]Performance is based on the Atheros Reference Design.

[2]Output power variation ±1 dB.

[3]Manufacturing calibration required.

[4]Refer to the design guide for information.

# 2.2.3 Synthesizer Characteristics

Table 2-6 summarizes the synthesizercharacteristics for the AR2317.

| Symbol            | Parameter                      | Conditions                                                      | Min   | Тур  | Max   | Unit   |

|-------------------|--------------------------------|-----------------------------------------------------------------|-------|------|-------|--------|

| Pn                | Phase noise (at Tx_Out)        |                                                                 |       |      |       | dBc/Hz |

|                   | At 30 KHz offset               |                                                                 |       | -104 |       |        |

|                   | At 100 KHz offset              |                                                                 |       | -103 | _     |        |

|                   | At 500 KHz offset              |                                                                 |       | -115 | _     |        |

|                   | At 1 MHz offset                |                                                                 |       | -120 | —     |        |

| F <sub>c</sub>    | Center channel frequency       | Center frequency<br>at 5 MHz spacing<br>See Note <sup>[1]</sup> | 2.312 |      | 2.484 | GHz    |

| F <sub>ref</sub>  | Reference oscillator frequency | ± 20 ppm                                                        |       | 40   | _     | MHz    |

| F <sub>step</sub> | Frequency step size (at RF)    | See Note                                                        |       | 1    | -     | MHz    |

| TSpowup           | Time for power up (from sleep) |                                                                 | _     | 0.2  | _     | ms     |

0.7

# Table 2-6. Synthesizer Composite Characteristics for 2.4 GHz Operation

[1]Frequency is measured at the Tx output.

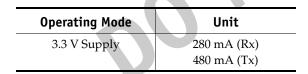

# 2.3 Power Consumption

These conditions apply to the following typical characteristics unless otherwise specified:

$$V_{DD33} = 3.3 V$$

,

$T_{amb} = 25 \ ^{\circ}C$

The following table depicts the typical power drain of the on-chip power supply domain as a function of the AR2317's operating mode.

# 3. Register Descriptions

This section describes internal registers for the various blocks of the AR2317.

# 3.1 Reset/Configuration Control Registers

Table 3-1 summarizes the AR2317 Reset/ Configuration registers. These registers use internal base address 0x1100\_0000.

| Table 3-1. | <b>Reset/Configuration</b> | Control Register Summary |

|------------|----------------------------|--------------------------|

|------------|----------------------------|--------------------------|

| Offset | Name             | Description                             | Page    |

|--------|------------------|-----------------------------------------|---------|

| 0x0000 | RST_COLD_CTL     | Cold reset control                      | page 16 |

| 0x0004 | RST_WARM_CTL     | Warm reset control                      | page 16 |

| 0x0008 | RST_AHB_ARB_CTL  | AHB master arbitration control          | page 17 |

| 0x000C | RST_BYTESWAP_CTL | Byteswap control                        | page 17 |

| 0x0010 | RST_NMI_CTL      | CPU non-maskable interrupt control      | page 18 |

| 0x0014 | RST_SREV         | Silicon revision                        | page 18 |

| 0x0020 | RST_MISR         | Miscellaneous interrupt status          | page 19 |

| 0x0024 | RST_MIMR         | Miscellaneous interrupt mask            | page 19 |

| 0x0028 | RST_GISR         | Global interrupt status                 | page 20 |

| 0x0030 | RST_GTIME        | General timer                           | page 20 |

| 0x0034 | RST_GTIME_RELOAD | General timer reload value              | page 20 |

| 0x0038 | RST_WDOG         | Watchdog timer                          | page 21 |

| 0x003C | RST_WDOG_CTL     | Watchdog timer control                  | page 21 |

| 0x0040 | RST_MEMCTL       | SDR-DRAM memory controller parameters   | page 21 |

| 0x0044 | RST_CPUPERF_CTL  | CPU performance counter control         | page 22 |

| 0x0048 | RST_CPUPERF_0    | CPU performance counter 0               | page 22 |

| 0x004C | RST_CPUPERF_1    | CPU performance counter 1               | page 23 |

| 0x0050 | RST_AHBERR0      | AHB error status register 0             | page 23 |

| 0x0054 | RST_AHBERR1      | AHB error status register 1             | page 23 |

| 0x0058 | RST_AHBERR2      | AHB error status register 2             | page 24 |

| 0x005C | RST_AHBERR3      | AHB error status register 3             | page 24 |

| 0x0060 | RST_AHBERR4      | AHB error status register 4             | page 24 |

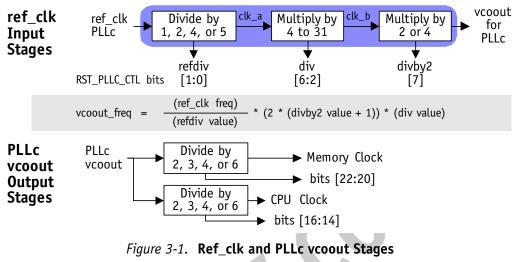

| 0x0064 | RST_PLLC_CTL     | CPU/AHB/APB PLL (PLLc) control          | page 25 |

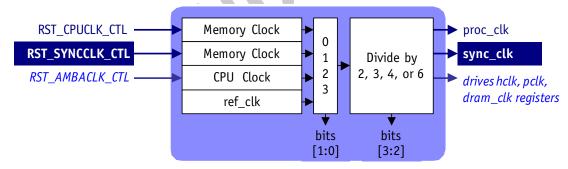

| 0x006C | RST_CPUCLK_CTL   | CPU final clock MUX/divider control     | page 26 |

| 0x0070 | RST_AMBACLK_CTL  | AHB/APB final clock MUX/divider control | page 26 |

| 0x0088 | RST_GPIOIN0      | GPIO input, set 0                       | page 26 |

| 0x0090 | RST_GPIOOUT0     | GPIO output, set 0                      | page 27 |

| 0x0098 | RST_GPIODIR0     | GPIO direction, set 0                   | page 27 |

| 0x00A0 | RST_GPIOINTR     | GPIO interrupt control                  | page 27 |

| 0x00A8 | RST_SCRATCH0     | Scratch register 0                      | page 28 |

| 0x00AC | RST_SCRATCH1     | Scratch register 1                      | page 28 |

| 0x00B0 | RST_OBS_CTL      | Observation control                     | page 28 |

| 0x00B4 | RST_MISCCLK_CTL  | General clock control                   | page 29 |

| 0x00B8 | RST_CIMR         | Client interrupt mask                   | page 29 |

# 3.1.1 Cold Reset Control (RST\_COLD\_CTL)

Offset: 0x0000 Internal Address: 0x1100\_0000 Access: Write-only (reads always return 0) Cold reset: (See field descriptions) Warm reset: Unaffected

| Bit  | Bit Name | Description                                                                                                                          |

|------|----------|--------------------------------------------------------------------------------------------------------------------------------------|

| 0    |          | AHB cold reset. Automatically asserted for 128 clocks on exit from chip reset. Thereafter, writes to this bit perform the following: |

|      |          | $\blacksquare$ 0 = No effect                                                                                                         |

|      |          | 1 = Issue a cold reset to the AHB arbitration and MUXing logic and all connected<br>blocks. Auto-clears after 128 clocks.            |

| 1    |          | APB cold reset. Automatically asserted for 128 clocks on exit from chip reset. Thereafter, writes to this bit perform the following: |

|      |          | $\blacksquare$ 0 = No effect                                                                                                         |

|      |          | 1 = Issue a cold reset to the APB arbitration and MUXing logic and all connected blocks. Auto-clears after 128 clocks.               |

| 2    |          | CPU cold reset. Automatically asserted for 128 clocks on exit from chip reset. Thereafter, writes to this bit perform the following: |

|      |          | $\blacksquare$ 0 = No effect                                                                                                         |

|      |          | 1 = Issue a cold reset to the MIPS CPU (asserts the CPU's SI_ColdReset and SI_Reset inputs). Auto-clears after 128 clocks.           |

| 3    |          | CPU warm reset. Automatically asserted for 128 clocks on exit from chip reset. Thereafter,                                           |

|      |          | writes to this bit perform the following:                                                                                            |

|      |          | $\blacksquare$ 0 = No effect                                                                                                         |

|      |          | ■ 1 = Issue a warm reset to the MIPS CPU (asserts the CPU's SI_Reset input). Auto-clears after 128 clocks.                           |

| 31:4 |          | Reserved                                                                                                                             |

# 3.1.2 Warm Reset Control (RST\_WARM\_CTL)

Offset: 0x0004 Internal address: 0x1100\_0004 Access: Read/Write Cold reset: (See field descriptions) Warm reset: Unaffected

| Bit   | Bit Name | Description                                   |

|-------|----------|-----------------------------------------------|

| 0     |          | WMAC warm reset. Resets to 0x1.               |

| 1     |          | WBB warm reset. Resets to 0x1.                |

| 3:2   | RES      | Reserved                                      |

| 4     |          | Memory controller warm reset. Resets to 0x0.  |

| 6:5   | RES      | Reserved                                      |

| 7     |          | SPI interface warm reset. Resets to 0x0.      |

| 8     |          | UART interface warm reset. Resets to 0x0.     |

| 9     | RES      | Reserved. Resets to 0x0                       |

| 10    |          | Ethernet interface warm reset. Resets to 0x1. |

| 11    |          | Ethernet MAC warm reset. Resets to 0x1.       |

| 31:12 | RES      | Reserved                                      |

#### 3.1.3 AHB Master Arbitration Control (RST\_AHB\_ARB\_CTL)

Offset: 0x0008 Internal address: 0x1100\_0008 Access: Read/Write Cold reset: (See field descriptions) Warm reset: Unaffected Notes: Bits [4:0] in this register control whether the associated interface can arbitrate for access to the AHB bus as master. This register does not affect operation of these interfaces as AHB targets. For each bit:

- 0 = Requests for AHB master access from the interface are ignored

- 1 = Requests for AHB master access from the interface process normally.

| Bit  | Bit Name | Description                                             |

|------|----------|---------------------------------------------------------|

| 0    |          | CPU AHB master arbitration control. Resets to 0x1.      |

| 1    |          | WMAC AHB master arbitration control. Resets to 0x0.     |

| 2    | RES      | Reserved                                                |

| 3    | res      | Reserved                                                |

| 4    | res      | Reserved                                                |

| 5    |          | Ethernet AHB master arbitration control. Resets to 0x0. |

| 31:6 | RES      | Reserved                                                |

#### 3.1.4 Byteswap Control (RST\_BYTESWAP\_CTL)

Offset: 0x000C Internal address: 0x1100\_000C Access: Read/Write Cold reset: (See field descriptions) Warm reset: Unaffected

| Bit | Bit Name | Description                                                                                                                                                               |

|-----|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   |          | EC-to-AHB bridge Endianness control. This signal affects how the EC-to-AHB bridge logic handles sub-word-sized reads and writes when acting as AHB master. Resets to 0x0. |

|     |          | <ul> <li>0 = EC-to-AHB interface operates in little Endian mode</li> <li>1 = EC-to-AHB interface operates in big Endian mode</li> </ul>                                   |

| 1   |          | WMAC AHB master byteswap control. Resets to CPU_BIG_ENDIAN_RST. See bit [10] of this register.                                                                            |

|     |          | <ul> <li>0 = WMAC AHB master interface does not byteswap data words</li> <li>1 = WMAC AHB master interface byteswaps data words for both writes and reads</li> </ul>      |

| 3:2 | RES      | Reserved                                                                                                                                                                  |

| 4   |          | Memory controller Endianness control. Resets to 0x0.                                                                                                                      |

|     |          | $\blacksquare$ 0 = The memory controller operates in little Endian mode                                                                                                   |

|     |          | ■ 1 = The memory controller operates in big Endian mode                                                                                                                   |

| 5   | RES      | Reserved                                                                                                                                                                  |

| 6   |          | Ethernet controller byteswap control. Resets to CPU_BIG_ENDIAN_RST. See bit [10] of this register.                                                                        |

|     |          | <ul> <li>0 = Ethernet controller master interface does not byteswap data words</li> <li>1 = Ethernet controller byteswaps data words for both writes and reads</li> </ul> |

| 8:7 | RES      | Reserved                                                                                                                                                                  |

| Bit   | Bit Name | Description                                                                                                                                                                                                                                            |

|-------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9     |          | CPU write buffer merge mode. Resets to 0x0.                                                                                                                                                                                                            |

|       |          | <ul> <li>■ 0 = No merge</li> <li>■ 1 = Full merge</li> </ul>                                                                                                                                                                                           |

| 10    |          | CPU Endian control. Resets to 0x1. The reset value of this bit (currently 1), defines the value of the CPU_BIG_ENDIAN_RST parameter referenced as the reset value for various other register fields in the chip.                                       |

|       |          | <ul> <li>0 = CPU operates in little Endian mode (CPU's SI_ENDIAN input negated)</li> <li>1 = CPU operates in big Endian mode (CPU's SI_ENDIAN input asserted)</li> </ul>                                                                               |

| 14:11 | RES      | Reserved                                                                                                                                                                                                                                               |

| 15    |          | CPU SPI access byteswap control. This bit controls whether the CPU swaps reads and writes to the two AHB SPI regions (AHB addresses 0x0800_0000-0x0FFF_FFFF and 0x1FC0_0000-0x1FFF_FFFF). Resets to CPU_BIG_ENDIAN_RST. See bit [10] of this register. |

|       |          | <ul> <li>0 = CPU does not swap SPI read/write data</li> <li>1 = CPU does swap SPI read/write data</li> </ul>                                                                                                                                           |

| 16    |          | CPU DRAM access byteswap control. This bit controls whether the CPU swaps reads and writes to the AHB DRAM region (AHB addresses 0x0000_0000-0x07ff_ffff). Resets to 0x0.                                                                              |

|       |          | <ul> <li>0 = CPU does not swap DRAM read/write data</li> <li>1 = CPU does swap DRAM read/write data</li> </ul>                                                                                                                                         |

| 17    | RES      | Reserved                                                                                                                                                                                                                                               |

| 18    |          | CPU MMR access byteswap control. This bit controls whether the CPU swaps reads and writes to the AHB MMR regions (AHB addresses 0x1000_0000-0x17FF_FFFF). Resets to 0x0.                                                                               |

|       |          | <ul> <li>0 = CPU does not swap MMR read/write data</li> <li>1 = CPU does swap MMR read/write data</li> </ul>                                                                                                                                           |

| 31:19 | RES      | Reserved                                                                                                                                                                                                                                               |

#### 3.1.5 CPU Non-Maskable Interrupt (NMI) Control (RST\_NMI\_CTL)

Offset: 0x0010 Internal address: 0x1100\_0010 Access: Write-only; reads always return 0x0 Cold reset: (See field descriptions) Warm reset: Unaffected

| Bit  | Bit Name | Description                                                                                                           |

|------|----------|-----------------------------------------------------------------------------------------------------------------------|

| 0    |          | NMI control to CPU. Resets to 0x0. Write of:                                                                          |

|      |          | <ul> <li>0 = No effect</li> <li>1 = Issues an NMI to the CPU (generates a pulse on the CPU's SI_NMI input)</li> </ul> |

| 31:1 | RES      | Reserved                                                                                                              |

# 3.1.6 Silicon Revision (RST\_SREV)

Offset: 0x0014 Internal address: 0x1100\_0014 Access: Read-only Cold reset: (See field descriptions) Warm reset: Unaffected

| Bit  | Bit Name | Description                                                         |

|------|----------|---------------------------------------------------------------------|

| 3:0  |          | AR2317 revision level                                               |

| 7:4  |          | AR2317 version level<br>■ 0x8 = AR2317 1.0<br>■ (others) = Reserved |

| 31:8 | RES      | Reserved                                                            |

# 3.1.7 Miscellaneous Interrupt Status (RST\_MISR)

Offset: 0x0020 Internal Address: 0x1100\_0020 Access: Read/Write-one-to-clear Cold reset: (See field descriptions) Warm reset: Unaffected Notes: Only bits [7:5] are cleared by a write to this register. To clear the other bits, software must clear the interrupt at the associated interface.

| Bit  | Bit Name | Description                                      |

|------|----------|--------------------------------------------------|

| 0    |          | UART interrupt pending. Resets to 0x0.           |

| 1    |          | Never asserted in the AR2317. Resets to 0x0.     |

| 2    |          | SPI interrupt pending. Resets to 0x0.            |

| 3    |          | AHB error interrupt pending. Resets to 0x0.      |

| 4    |          | APB error interrupt pending. Resets to 0x0       |

| 5    |          | General timer interrupt pending. Resets to 0x0.  |

| 6    |          | GPIO interrupt pending. Resets to 0x0.           |

| 7    |          | Watchdog timer interrupt pending. Resets to 0x0. |

| 8    |          | Never asserted. Resets to 0x0.                   |

| 31:9 | RES      | Reserved                                         |

#### 3.1.8 Miscellaneous Interrupt Mask (RST\_MIMR)

Offset: 0x0024 Internal Address: 0x1100\_0024 Access: Read/Write Cold reset: (See field descriptions) Warm reset: Unaffected

| Bit  | Bit Name | Description                                   |

|------|----------|-----------------------------------------------|

| 0    |          | UART interrupt mask. Resets to 0x0.           |

| 1    | RES      | Reserved. Resets to 0x0.                      |

| 2    |          | SPI interrupt mask. Resets to 0x0.            |