November 2011

# AR9271 Single-Chip 1x1 MAC/BB/Radio/PA/LNA with USB Interface for 802.11n 2.4 GHz WLANs

# **General Description**

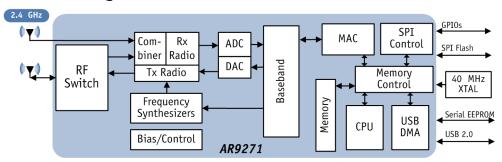

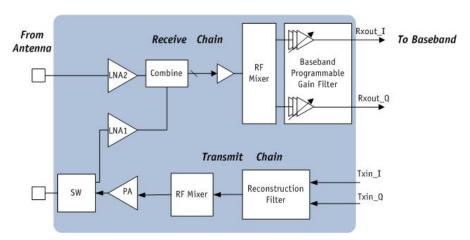

The Atheros AR9271 is a highly integrated single-chip solution for 2.4 GHz 802.11n-ready wireless local area networks (WLANs) that enables a high-performance 1x1 configuration for wireless station applications demanding robust link quality and maximum throughput and range. The AR9271 integrates a multi-protocol MAC, baseband processor, analog-to-digital and digital-to-analog (ADC/DAC) converters, 1x1 radio transceiver, RF switch, and USB interface in an all-CMOS device for low power and small form factor applications.

The AR9271 implements half-duplex OFDM, CCK, and DSSS baseband processing, supporting 72.2 Mbps for 20 MHz and 150 Mbps for 40 MHz channel and IEEE 802.11b/g data rates. Other features include signal detection, automatic gain control, frequency offset estimation, symbol timing, and channel estimation. The AR9271 MAC supports the 802.11 wireless MAC protocol, 802.11i security, receive and transmit filtering, error recovery, and quality of service (QoS).

The AR9271 supports one transmit traffic stream and one receive traffic stream using one integrated Tx chain and one receive chain for high throughput and range performance. The Tx chain combines baseband in-phase (I) and quadrature (Q) signals, converts them to the desired frequency, and drives the RF signal to the antenna. The frequency synthesizer supports frequencies defined by IEEE 802.11b/g/n specifications.

The AR9271 supports frame data transfer to and from the host using a USB interface that provides interrupt generation/reporting, power save, and status reporting. Other external interfaces include

serial EEPROM and GPIOs. The AR9271 is interoperable with standard legacy 802.11b/g devices.

#### **Features**

- All-CMOS solution interoperable with IEEE 802.11b/g/n WLANs

- Intergrated RF front end with high-output PA, LNA, Rx/Tx switch

- Internal diversity switch which selects antenna 1 or 2 for baseband signal processing

- Supports optional external LNA, PA

- 2.4 GHz WLAN MAC/BB processing

- BPSK, QPSK, 16 QAM, 64 QAM, DBPSK, DQPSK, and CCK modulation schemes

- Supports 72.2 Mbps for 20 MHz and 150 Mbps for 40 MHz channel operations

- Wireless multimedia enhancements quality of service support (QoS)

- 802.11e-compatible bursting

- Support for IEEE 802.11e and IEEE 802.11i standards

- WEP, TKIP, and AES hardware encryption

- Reduced (short) guard interval

- Frame aggregation

- Block ACK

- USB 2.0 interface

- Supports the access of a serial peripheral (SPI) compatible Flash memory, which includes booting from an SPI Flash and autoinstallation

- IEEE 1149.1 standard test access port and boundary scan architecture supported

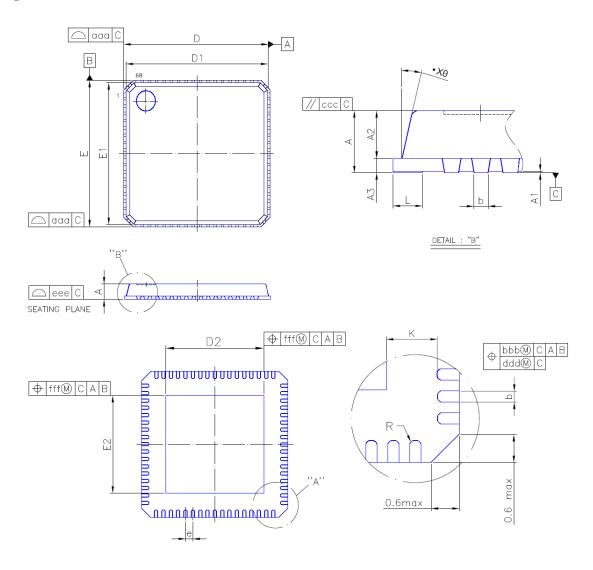

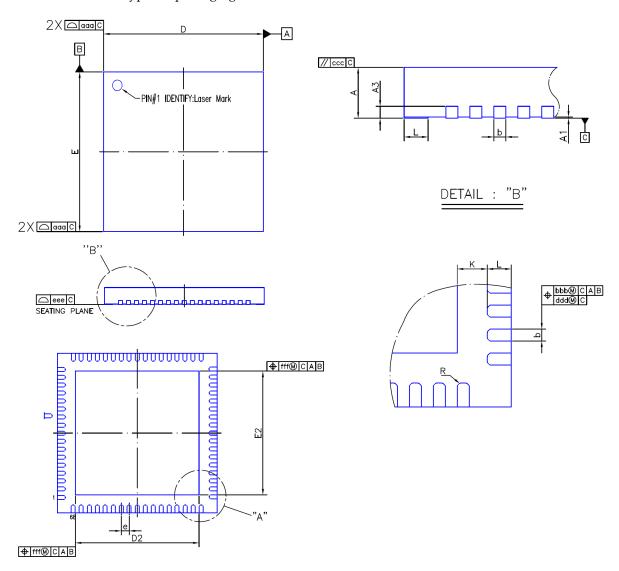

- 68-pin, 8 mm x 8 mm LPCC package

# AR9271 System Block Diagram

# **Revision History**

| Ver. | Date          | Description                                                                                                                                                                |  |

|------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1.0  | March 2011    | Initial release                                                                                                                                                            |  |

| 2.0  | November 2011 | Updated Table 8-1 D2/E2 dimensions, nominal from 5.49 to 5.84 mm, maximum from 5.64 to 6.35 mm. Added sawed-type package diagram and dimensions, Figure 8-2 and Table 8-2. |  |

| Ta  | ble of Contents                                            | 5 Radio Block                                            |      |

|-----|------------------------------------------------------------|----------------------------------------------------------|------|

|     |                                                            | 5.1 Receiver (Rx) Block                                  |      |

|     | neral Description1                                         | 5.2 Transmitter (Tx) Block                               |      |

|     | atures1                                                    | 5.3 Synthesizer (SYNTH) Block                            | 36   |

| AF  | 89271 System Block Diagram1                                | 5.4 Bias/Control (BIAS) Block                            | 36   |

| 1   | Pin Descriptions9                                          | 6 Register Descriptions<br>CPU Block 37                  | .37  |

|     | Functional Description                                     | 6.1 USB Controller PIO Registers                         | 37   |

| 2.1 | Overview                                                   | 6.1.1 Endpoint Data Port Register (EP0_DB)               | 38   |

|     | 2.1.2 AR9271 Address MAP                                   | 6.1.2 USB Data Width Control Regis                       |      |

|     | 2.1.3 Serial EEPROM Interface14                            | (UC_CTL)                                                 |      |

|     | 2.1.4 EEPROM Auto-Sizing Mechanism                         | 6.1.3 USB DMA Control Register                           |      |

|     | 14                                                         | (UD_CTRL)                                                | 38   |

|     | 2.1.5 EEPROM Read/Write Protection                         | 6.1.4 USB Upstream Stream Mode M                         | IAX  |

|     | Mechanism14                                                | Aggregate Register (REG_APK                              | T)   |

| 2.2 | Reset14                                                    | 39                                                       | 10   |

| 2.3 | GPIO14                                                     | 6.1.5 USB Upload Time Control                            |      |

| 2.4 | LED14                                                      | 6.1.6 USB DMA Reset Control Regist 40                    | ter  |

| 2.5 | USB Host Interface14                                       | 6.1.7 USB Controller Wake Up                             | 40   |

| 2.6 | The CPU Block15                                            | 6.1.8 USB Clock Status Register                          |      |

|     | 2.6.1 The CPU15                                            | (US_CLK_STS)                                             | 40   |

|     | 2.6.2 Memory Controller and the AHB                        | 6.2 Reset/Clock Control Register                         | 41   |

|     | Arbiter                                                    | 6.2.1 General Purpose Timer Registe                      |      |

|     | 2.6.3 Internal Memories                                    | (RST_GENERAL_TIMER)                                      |      |

|     | 2.6.4 The AHB Proc15                                       | 6.2.2 General Purpose Timer Reload<br>Register           |      |

|     | Medium Access Control (MAC) 17                             | (RST_GENERAL_TIMER_RELO                                  |      |

| 3.1 | Overview17                                                 | D)                                                       |      |

| 3.2 | Descriptor17                                               | 6.2.3 Watchdog Timer Control Regis (RST_WATCHDOG_TIMER_C |      |

| 3.3 | Descriptor Format18                                        | TROL)                                                    |      |

| 3.4 | Queue Control Unit (QCU)32                                 | 6.2.4 Watchdog Timer Register                            |      |

|     | 3.4.1 DCF Control Unit (DCU) 32                            | (RST_WATCHDOG_TIMER)                                     | 42   |

| 3.5 | Protocol Control Unit (PCU)32                              | 6.2.5 Reset Register (RST_RESET                          | ) 42 |

|     |                                                            | 6.2.6 Bootstrap Values                                   |      |

|     | Digital PHY Block 33                                       | (RST_BOOTSTRAP)                                          | 42   |

|     | Overview                                                   | 6.2.7 Watchdog Timer Interrupt (RST_WATCHDOG_INT)        | 43   |

| 4.2 | 802.11n Mode                                               | 6.2.8 General Timer Interrupt                            |      |

|     | 4.2.1 Transmitter (Tx)                                     | (RST_GENERAL_TIMER_INT)                                  | 43   |

| 4.0 | 4.2.2 Receiver (Rx)                                        | 6.2.9 Clock Control Register                             |      |

| 4.3 | 802.11b/g Legacy Mode34                                    | 6.2.10 Reset and Power Down Contro                       |      |

|     | 4.3.1 Transmitter       34         4.3.2 Receiver       34 | Register                                                 |      |

|     | 7.J.2 NECEIVEI                                             | 6.2.11 USB PLL Parameter Register                        | 46   |

|     | 6.2.12                                      | Reset Status Register47                                    |           | 52                                                            |

|-----|---------------------------------------------|------------------------------------------------------------|-----------|---------------------------------------------------------------|

|     | 6.2.13 Chip Revision ID (RST_REVISION_ID)47 |                                                            | 6.3.15    | 5 USB Rx Chain 2 AHB Burst Size<br>Register                   |

| 6.3 | USB C                                       | Controller DMA Registers 48                                |           | (USB_DMA_RX_2_BURST_SIZE)                                     |

|     | 6.3.1                                       | Interrupt Status Register<br>(USB_DMA_INTERRUPT) 48        | 6.3.16    | 52<br>5 USB Rx Chain 2 Packet Offset                          |

|     | 6.3.2                                       | Interrupt Mask Register<br>(USB_DMA_INTERRUPT_MASK)<br>49  |           | Register<br>(USB_DMA_RX_2_PKT_OFFSET)<br>52                   |

|     | 6.3.3                                       | USB Rx Chain 0 Descriptor Start<br>Address Register        |           | 7 Rx Chain 2 Data Swap Register<br>(USB_RX_2_DATA_SWAP) 52    |

|     |                                             | (USB_DMA_RX_0_DESC_START_<br>ADDRESS)49                    | 6.3.18    | 3 USB Tx Chain 0 Descriptor Start Address Register            |

|     | 6.3.4                                       | USB Rx Chain 0 DMA Start Register (USB_DMA_RX_0_DMA_START) |           | (USB_DMA_TX_0_DESC_START_<br>ADDRESS)53                       |

|     | 6.3.5                                       | 50<br>USB Rx Chain 0 AHB Burst Size                        | 6.3.19    | USB Tx Chain 0 DMA Start Register<br>(USB_DMA_TX_0_DMA_START) |

|     |                                             | Register<br>(USB_DMA_RX_0_BURST_SIZE)<br>50                | 6.3.20    | 53<br>) USB Tx Chain 0 Interrupt Limit<br>Register            |

|     | 6.3.6                                       | USB Rx Chain 0 Packet Offset<br>Register                   |           | (USB_DMA_TX_0_INTERRUPT_LI<br>MIT)53                          |

|     |                                             | (USB_DMA_RX_0_PKT_OFFSET) 50                               | 6.3.21    | Tx Chain 0 AHB Burst Size Register (USB_DMA_TX_0_BURST_SIZE)  |

|     |                                             | Rx Chain 0 Data Swap Register (USB_RX_0_DATA_SWAP)50       | 6.3.22    | 53 2 Tx Chain 0 Data Swap Register (USB_TX_0_DATA_SWAP) 53    |

|     | 6.3.8                                       | USB Rx Chain 1 Descriptor Start                            | 6.4 SPI C | Control Registers54                                           |

|     |                                             | Address Register (USB_DMA_RX_1_DESC_START_                 | SPI Co    | ontrol Register Notes 54                                      |

|     | 6.3.9                                       | ADDRESS)50 USB Rx Chain 1 DMA Start Register               | 6.4.1     | SPI Control/Status Register (SPI_CS)55                        |

|     |                                             | (USB_DMA_RX_1_DMA_START)<br>51                             | 6.4.2     | SPI Address/Opcode Register (SPI_AO)55                        |

|     |                                             | USB Rx Chain 1 AHB Burst Size                              | 6.4.3     | SPI Data Register (SPI_D) 56                                  |

|     |                                             | Register (USR DMA RY 1 BURST SIZE)                         | MAC       | Register Descriptions 57                                      |

|     |                                             | (USB_DMA_RX_1_BURST_SIZE) 51                               |           | ral DMA and Rx-Related Registers                              |

|     | 6.3.11                                      | USB Rx Chain 1 Packet Offset                               | 57        | C 1/CD) 50                                                    |

|     |                                             | Register                                                   |           | Command (CR)                                                  |

|     |                                             | (USB_DMA_RX_1_PKT_OFFSET) 51                               | 6.3.2     | Rx Queue Descriptor Pointer (RXDP)58                          |

|     | 6.3.12                                      | Rx Chain 1 Data Swap Register                              | 6.5.3     | , ,                                                           |

|     |                                             | (USB_RX_DATA_SWAP)51                                       | 6.5.4     | Maximum Interrupt Rate Threshold                              |

|     | 6.3.13                                      | USB Rx Chain 2 Descriptor Start                            | (         | (MIRT)                                                        |

|     |                                             | Address Register (USB_DMA_RX_2_DESC_START_                 | 6.5.5     | Interrupt Global Enable (IER) 60                              |

|     |                                             | ADDRESS)52                                                 | 6.5.6     | Tx Interrupt Mitigation Thresholds (TIMT)60                   |

|     | 6.3.14                                      | USB Rx Chain 2 DMA Start Register (USB_DMA_RX_2_DMA_START) | 6.5.7     |                                                               |

|                | Tx Configuration (TXCFG) 61<br>Rx Configuration (RXCFG) 62          | 6.5.37  | 7 Secondary Interrupt Status 3<br>(ISR_S3_S)74                |

|----------------|---------------------------------------------------------------------|---------|---------------------------------------------------------------|

|                | MIB Control (MIBC)62                                                | 6.5.38  | 8 Secondary Interrupt Status 4                                |

|                | Timeout Prescale (TOPS)                                             | 0.0.00  | (ISR_S4_S)75                                                  |

|                | Rx No Frame (RXNF)                                                  | 6.5.39  | 9 Secondary Interrupt Status 5                                |

|                | Tx No Frame (TXNF)63                                                |         | (ISR_S5_Ś)75                                                  |

|                | Rx Frame Gap Timeout (RFGTO)                                        | 6.6 QCU | Registers76                                                   |

| 0.5.14         | 63                                                                  |         | n Handling 76                                                 |

| 6.5.15         | Rx Frame Count Limit (RFCNT) 63                                     | 6.6.1   | Tx Queue Descriptor (Q_TXDP) 77                               |

|                | Global Tx Timeout (GTT) 64                                          | 6.6.2   | Tx Queue Enable (Q_TXE) 78                                    |

|                | Global Tx Timeout Mode (GTTM)                                       | 6.6.3   | Tx Queue Disable (Q_TXD) 78                                   |

|                | 64                                                                  | 6.6.4   | CBR Configuration (Q_CBRCFG)                                  |

| 6.5.18         | Carrier Sense Timeout (CST) 64                                      |         | 78                                                            |

|                | Primary Interrupt Status (ISR_P) 65<br>Secondary Interrupt Status 0 | 6.6.5   | ReadyTime Configuration (Q_RDYTIMECFG)79                      |

|                | (ISR_S0)67                                                          | 6.6.6   | OneShotArm Set Control (Q_ONESHOTARM_SC)                      |

|                | Secondary Interrupt Status 1 (ISR_S1)67                             | 6.6.7   | OneShotArm Clear Control (Q_ONESHOTARM_CC)                    |

| 6.3.22         | Secondary Interrupt Status 2 (ISR_S2)68                             | 6.6.8   |                                                               |

| 6523           | Secondary Interrupt Status 3                                        |         | Misc. QCU Status (Q_STS) 82                                   |

| 0.5.25         | (ISR_S3)68                                                          |         | ReadyTimeShutdown Status                                      |

| 6.5.24         | Secondary Interrupt Status 4                                        |         | (Q_RDYTIMESHDN) 82                                            |

|                | (ISR_S4)69                                                          | 6.7 DCU | Registers 83                                                  |

| 6.5.25         | Secondary Interrupt Status 5                                        |         | QCU Mask (D_QCUMASK) 83                                       |

| 6.5.26         | (ISR_S5)69<br>Primary Interrupt Mask (IMR_P) 70                     | 6.7.2   | DCU-Specific IFS Settings (D_LCL_IFS)84                       |

| 6.5.27         | Secondary Interrupt Mask 0                                          | 6.7.3   |                                                               |

|                | (IMR_S0)71                                                          | 6.7.4   | -                                                             |

| 6.5.28         | Secondary Interrupt Mask 1                                          |         | (D_CHNTIME) 85                                                |

|                | (IMR_S1)71                                                          | 6.7.5   | Misc. DCU-Specific Settings                                   |

| 6.5.29         | Secondary Interrupt Mask 2                                          |         | (D_MISC)85                                                    |

| ( <b>F 2</b> 0 | (IMR_S2)72                                                          | 6.7.6   | DCU-Global IFS Settings: SIFS                                 |

| 6.5.30         | Secondary Interrupt Mask 3                                          |         | Duration (D_GBL_IFS_SIFS) 87                                  |

| 6 E 21         | (IMR_S3)                                                            | 6.7.7   | DCU-Global IFS Settings: Slot                                 |

| 0.3.31         | Secondary Interrupt Mask 4 (IMR_S4)73                               |         | Duration (D_GBL_IFS_SLOT) 88                                  |

| 6 5 32         | Secondary Interrupt Mask 5                                          | 6.7.8   | DCU-Global IFS Settings: EIFS                                 |

| 0.5.52         | (IMR_S5)73                                                          | (70     | Duration (D_GBL_IFS_EIFS) 88                                  |

| 6.5.33         | Primary Interrupt Status Read and                                   | 6.7.9   | DCU-Global IFS Settings: Misc. Parameters (D_GBL_IFS_MISC) 88 |

| 0.0.00         | Clear (ISR_P_RAC)74                                                 | 6710    | DCU Tx Pause Control/Status                                   |

| 6.5.34         | Secondary Interrupt Status 0                                        | 0.7.10  | (D_TXPSE)89                                                   |

|                | (ISR_S0_S)74                                                        | 6.7 11  | 1 DCU Transmission Slot Mask                                  |

| 6.5.35         | Secondary Interrupt Status 1                                        | 0.7.11  | (D_TXSLOTMASK) 89                                             |

|                | (ISR_S1_S)74                                                        | 6.7.12  | 2 DCU Tx Filter Bits (D_TXBLK) . 91                           |

| 6.5.36         | Secondary Interrupt Status 2                                        |         | OM Interface Registers 93                                     |

|                | (ISR_S2_S)74                                                        |         | Interface Registers93                                         |

| 6.8.1   | Reset the MAC AHB/APB Interface                   | (MAC_AHB_BURST_MODE) 104                                    |

|---------|---------------------------------------------------|-------------------------------------------------------------|

|         | (H_RC)94                                          | 6.9 RTC Interface Registers104                              |

| 6.8.2   | EEPROM Control                                    | 6.9.1 RTC Reset and Force Sleep and                         |

|         | (H_EEPROM_CTRL)94                                 | Force Wakeup (RTC_RESET) . 105                              |

| 6.8.3   | MAC Silicon Revision ID                           | 6.9.2 RTC Sleep Status (RTC_STATUS)                         |

|         | (H_SREV_ID)94                                     | 105                                                         |

|         | AHB Mode (AHB_MODE)95                             | 6.9.3 RTC Force Derived RTC and Bypass                      |

| 6.8.5   | Interrupt Cause Clear                             | Derived RTC (RTC_DERIVED) 105                               |

|         | (H_INTR_CAUSE_CLR)96                              | 6.9.4 RTC Force Wake                                        |

| 6.8.6   | Synchronous Interrupt Cause                       | (RTC_FORCE_WAKE)105                                         |

| ( 0.7   | (H_INTR_SYNC_CAUS)96                              | 6.9.5 RTC Interrupt Cause                                   |

| 0.0.7   | Synchronous Interrupt Enable (H_INTR_SYNC_ENAB)97 | (RTC_INT_CAUSE) 106                                         |

| 6.8.8   | Asynchronous Interrupt Mask                       | 6.9.6 RTC Interrupt Cause Clear                             |

| 0.0.0   | (H_INTR_ASYN_MASK)97                              | (RTC_CAUSE_CLR)106                                          |

| 689     | Synchronous Interrupt Mask                        | 6.9.7 RTC Interrupt Enable (RTC_INT_ENABLE)107              |

| 0.0.7   | (H_INTR_SYN_MASK)97                               |                                                             |

| 6.8.10  | Asynchronous Interrupt Cause                      | 6.9.8 RTC Interrupt Mask (RTC_INT_MASK)107                  |

|         | (H_INTR_ASYN_CAUS)97                              |                                                             |

| 6.8.11  | Asynchronous Interrupt Enable                     | 6.10 MAC Interface Registers                                |

|         | (H_INTR_ASYN_ENAB)97                              | 6.10.1 MAC Sleep Status (MAC_SLEEP)<br>108                  |

| 6.8.12  | GPIO Input and Output                             |                                                             |

|         | (H_GPIO_IN_OUT)98                                 | 6.10.2 MAC LED Control (MAC_LED)<br>108                     |

| 6.8.13  | GPIO Output Enable Bits                           |                                                             |

|         | (H_GPIO_OE_BITS)98                                | 6.11 MAC PCU Registers                                      |

| 6.8.14  | GPIO Interrupt Polarity                           | 6.11.1 STA Address Lower 32 Bits (MAC_PCU_STA_ADDR_L32) 111 |

|         | (H_GPIO_IRQ_POLAR)99                              | 6.11.2 STA Address Upper 16 Bits                            |

| 6.8.15  | GPIO Input Enable and Value                       | (MAC_PCU_STA_ADDR_U16) 111                                  |

|         | (H_GP_INPT_EN_VAL)99                              | 6.11.3 BSSID Lower 32 Bits                                  |

| 6.8.16  | GPIO Input MUX1                                   | (MAC_PCU_BSSID_L32) 112                                     |

| (017    | (H_GP_INPT_MUX1)99                                | 6.11.4 BSSID Upper 16 Bits                                  |

| 0.0.17  | GPIO Input MUX2<br>(H_GP_INPT_MUX2)100            | (MAC_PCU_BSSID_U16) 112                                     |

| 6 2 1 2 | GPIO Output MUX1                                  | 6.11.5 Beacon RSSI Average                                  |

| 0.0.10  | (H_GP_OUTPT_MUX1)100                              | (MAC_PCU_BCN_RSSI_AVE) 112                                  |

| 6819    | GPIO Output MUX2                                  | 6.11.6 ACK and CTS Timeout                                  |

| 0.0.17  | (H_GP_OUTPT_MUX2)100                              | (MAC_PCU_ACK_CTS_TIMEOUT                                    |

| 6.8.20  | Input Values (H_INPUT_STATE)                      | ) 113                                                       |

| 0.0.00  | 101                                               | 6.11.7 Beacon RSSI Control                                  |

| 6.8.21  | EEPROM Status and Read Data                       | (MAC_PCU_BCN_RSSI_CTL) 113                                  |

|         | (H_EEP_STS_DATA)102                               | 6.11.8 Ms Counter and Rx/Tx Latency                         |

| 6.8.22  | RFSilent-Related Registers                        | (MAC_PCU_USEC_LATENCY)                                      |

|         | (H_RFSILENT)102                                   | 113                                                         |

| 6.8.23  | GPIO Pull-Up/Pull-Down                            | 6.11.9 Reset TSF (MAC POLL RESET TSE) 114                   |

|         | (H_GPIO_PDPU)103                                  | (MAC_PCU_RESET_TSF) 114<br>6.11.10 Maximum CFP Duration     |

| 6.8.24  | GPIO Drive Strength                               | (MAC_PCU_MAX_CFP_DUR) 114                                   |

|         | (H_GPIO_DS)103                                    | 6.11.11 Rx Filter                                           |

| 6825    | AHR Burst Mode                                    | 0.11.11 10.11101                                            |

| (MAC_PCU_RX_FILTER) 114<br>6.11.12 Multicast Filter Mask Lower 32 Bits | (MAC_PCU_ADDR1_MASK_L32)<br>120                                  |

|------------------------------------------------------------------------|------------------------------------------------------------------|

| (MAC_PCU_MCAST_FILTER_L32)                                             | 6.11.34 Address 1 Mask Upper 16 Bits<br>(MAC_PCU_ADDR1_MASK_U16) |

|                                                                        | (MAC_FCU_ADDR1_MASK_U16)<br>120                                  |

| 6.11.13 Multicast Filter Mask Upper 32 Bits (MAC_PCU_MCAST_FILTER_U32  | 6.11.35 Tx Power Control                                         |

| )115                                                                   | (MAC_PCU_TPC)121                                                 |

| 6.11.14 Diagnostic Switches                                            | 6.11.36 Tx Frame Counter                                         |

| (MAC_PCU_DIAG_SW) 115                                                  | (MAC_PCU_TX_FRAME_CNT)                                           |

| 6.11.15 TSF Lower 32 Bits                                              | 121                                                              |

| (MAC_PCU_TSF_L32)116                                                   | 6.11.37 Rx Frame Counter                                         |

| 6.11.16 TSF Upper 32 Bits                                              | (MAC_PCU_RX_FRAME_CNT)                                           |

| (MAC_PCU_TSF_U32)116                                                   | 121                                                              |

| 6.11.17 Default Antenna                                                | 6.11.38 Rx Clear Counter                                         |

| (MAC_PCU_DEF_ANTENNA) 116                                              | (MmAC_PCU_RX_CLEAR_CNT)                                          |

| 6.11.18 AES Mute Mask 0                                                | 121                                                              |

| (MAC_PCU_AES_MUTE_MASK_0                                               | 6.11.39 Cycle Counter                                            |

| )117                                                                   | (MAC_PCU_CYCLE_CNT) 122                                          |

| 6.11.19 AES Mute Mask 1                                                | 6.11.40 Quiet Time 1                                             |

| (MAC_PCU_AES_MUTE_MASK_1                                               | (MAC_PCU_QUIET_TIME_1) 122                                       |

| )117                                                                   | 6.11.41 Quiet Time 2                                             |

| 6.11.20 Last Rx Beacon TSF                                             | (MAC_PCU_QUIET_TIME_2) 122                                       |

| (MAC_PCU_LAST_BEACON_TSF)                                              | 6.11.42 QoS No ACK                                               |

| 117                                                                    | (MAC_PCU_QOS_NO_ACK) 123                                         |

| 6.11.21 Current NAV (MAC_PCU_NAV)                                      | 6.11.43 PHY Error Mask                                           |

| 117                                                                    | (MAC_PCU_PHY_ERROR_MASK)                                         |

| 6.11.22 Successful RTS Count                                           |                                                                  |

| (MAC_PCU_RTS_SUCCESS_CNT)                                              | 6.11.44 Rx Buffer Threshold                                      |

| 118                                                                    | (MAC_PCU_RXBUF_THRESHOL<br>D)124                                 |

| 6.11.23 Failed RTS Count                                               | •                                                                |

| (MAC_PCU_RTS_FAIL_CNT) 118                                             | 6.11.45 QoS Control                                              |

| 6.11.24 FAIL ACK Count                                                 | (MAC_PCU_MIC_QOS_CONTRO<br>L)124                                 |

| (MAC_PCU_ACK_FAIL_CNT) 118                                             | 6.11.46 Michael QoS Select                                       |

| 6.11.25 Failed FCS Count (MAC_PCU_FCS_FAIL_CNT) 118                    | (MAC_PCU_MIC_QOS_SELECT)                                         |

| 6.11.26 Beacon Count                                                   | 125                                                              |

| (MAC_PCU_BEACON_CNT) 119                                               | 6.11.47 Miscellaneous Mode                                       |

| 6.11.27 Max PCU Transmit Antenna                                       | (MAC_PCU_MISC_MODE) 125                                          |

| 1(MAC_PCU_TX_ANT_1) 119                                                | 6.11.48 Filtered OFDM Counter                                    |

| 6.11.28 Max PCU Transmit Antenna 2                                     | (MAC_PCU_FILTER_OFDM_CNT)                                        |

| (MAC_PCU_TX_ANT_2) 119                                                 |                                                                  |

| 6.11.29 Max PCU Transmit Antenna 3                                     | 6.11.49 Filtered CCK Counter                                     |

| (MAC_PCU_TX_ANT_3) 119                                                 | (MAC_PCU_Filter_CCK_CNT) 126                                     |

| 6.11.30 Max PCU Transmit Antenna 4                                     | 6.11.50 PHY Error Counter 1                                      |

| (MAC_PCU_TX_ANT_4) 119                                                 | (MAC_PCU_PHY_ERR_CNT_1) .                                        |

| 6.11.31 Sleep 1 (MAC_PCU_SLP1) 120                                     | 127                                                              |

| 6.11.32 Sleep 2 (MAC_PCU_SLP2) 120                                     | 6.11.51 PHY Error Counter 1 Mask                                 |

| * *                                                                    | (MAC_PCU_PHY_ERR_CNT_1_M                                         |

| 6.11.33 Address 1 Mask Lower 32 Bits                                   | $\Delta SK$ ) 127                                                |

| 6.11.52 PHY Error Counter 2                                                     | (MAC_PCU_SLP_MIB3) 135                                                 |

|---------------------------------------------------------------------------------|------------------------------------------------------------------------|

| (MAC_PCU_PHY_ERR_CNT_2)                                                         | 6.11.72 US Scalar (US_SCALAR) 135                                      |

| 127                                                                             | 6.11.73 Global Mode                                                    |

| 6.11.53 PHY Error Counter 2 Mask                                                | (MAC_PCU_20_40_MODE) 135                                               |

| (MAC_PCU_PHY_ERR_CNT_2_M                                                        | 6.11.74 Difference Rx_Clear Counter                                    |

| ASK)128                                                                         | (MAC_PCU_RX_CLEAR_DIFF_C                                               |

| 6.11.54 TSF Threshold                                                           | NT)135                                                                 |

| (MAC_PCU_TSF_THRESHOLD) .                                                       | 6.11.75 Control Registers for Block BA                                 |

| 128                                                                             | Control Fields                                                         |

| 6.11.55 PHY Error EIFS Mask                                                     | (MAC_PCU_BA_BAR_CONTROL)                                               |

| (MAC_PCU_PHY_ERROR_EIFS_<br>MASK)128                                            |                                                                        |

| 6.11.56 PHY Error Counter 3                                                     | 6.11.76 Legacy PLCP Spoof                                              |

| (MAC_PCU_PHY_ERR_CNT_3)                                                         | (MAC_PCU_LEGACY_PLCP_SPO<br>OF)136                                     |

| 128                                                                             | 6.11.77 PHY Error Mask and EIFS Mask                                   |

| 6.11.57 PHY Error Counter 3 Mask                                                | (MAC_PCU_PHY_ERROR_MASK                                                |

| (MAC_PCU_PHY_ERR_CNT_3_M                                                        | _CONT)136                                                              |

| ASK)129                                                                         | 6.11.78 Tx Timer                                                       |

| 6.11.58 HCF Timeout                                                             | (MAC_PCU_TX_TIMER) 137                                                 |

| (MAC_PCU_HCF_TIMEOUT) 129                                                       | 6.11.79 MAC Miscellaneous Mode                                         |

| 6.11.59 SIFS, Tx Latency and ACK Shift                                          | (MAC_MISC_MODE2)137                                                    |

| (MAC_PCU_TXSIFS)129                                                             | 5.4.3 Key Cache                                                        |

| 6.11.60 TxOP for Non-QoS Frames                                                 | (MAC_PCU_KEY_CACHE[0:1023])                                            |

| (MAC_PCU_TXOP_X)130                                                             |                                                                        |

| 6.11.61 TxOP for TID 0 to 3                                                     |                                                                        |

|                                                                                 |                                                                        |

| (MAC_PCU_TXOP_0_3)130                                                           | 6 Electrical Characteristics139                                        |

| (MAC_PCU_TXOP_0_3) 130<br>6.11.62 TXOP for TID 4 to 7                           | <b>6</b> Electrical Characteristics139 6.1 Absolute Maximum Ratings139 |

| (MAC_PCU_TXOP_0_3) 130<br>6.11.62 TXOP for TID 4 to 7<br>(MAC_PCU_TXOP_4_7) 130 |                                                                        |

| (MAC_PCU_TXOP_0_3)                                                              | 6.1 Absolute Maximum Ratings139                                        |

| (MAC_PCU_TXOP_0_3)                                                              | <ul><li>6.1 Absolute Maximum Ratings</li></ul>                         |

| (MAC_PCU_TXOP_0_3)                                                              | <ul> <li>6.1 Absolute Maximum Ratings</li></ul>                        |

| (MAC_PCU_TXOP_0_3)                                                              | <ul> <li>6.1 Absolute Maximum Ratings</li></ul>                        |

| (MAC_PCU_TXOP_0_3)                                                              | <ul> <li>6.1 Absolute Maximum Ratings</li></ul>                        |

| (MAC_PCU_TXOP_0_3)                                                              | <ul> <li>6.1 Absolute Maximum Ratings</li></ul>                        |

| (MAC_PCU_TXOP_0_3)                                                              | <ul> <li>6.1 Absolute Maximum Ratings</li></ul>                        |

| (MAC_PCU_TXOP_0_3)                                                              | <ul> <li>6.1 Absolute Maximum Ratings</li></ul>                        |

| (MAC_PCU_TXOP_0_3)                                                              | <ul> <li>6.1 Absolute Maximum Ratings</li></ul>                        |

| (MAC_PCU_TXOP_0_3)                                                              | <ul> <li>6.1 Absolute Maximum Ratings</li></ul>                        |

| (MAC_PCU_TXOP_0_3)                                                              | <ul> <li>6.1 Absolute Maximum Ratings</li></ul>                        |

| (MAC_PCU_TXOP_0_3)                                                              | 6.1 Absolute Maximum Ratings                                           |

| (MAC_PCU_TXOP_0_3)                                                              | <ul> <li>6.1 Absolute Maximum Ratings</li></ul>                        |

| (MAC_PCU_TXOP_0_3)                                                              | 6.1 Absolute Maximum Ratings                                           |

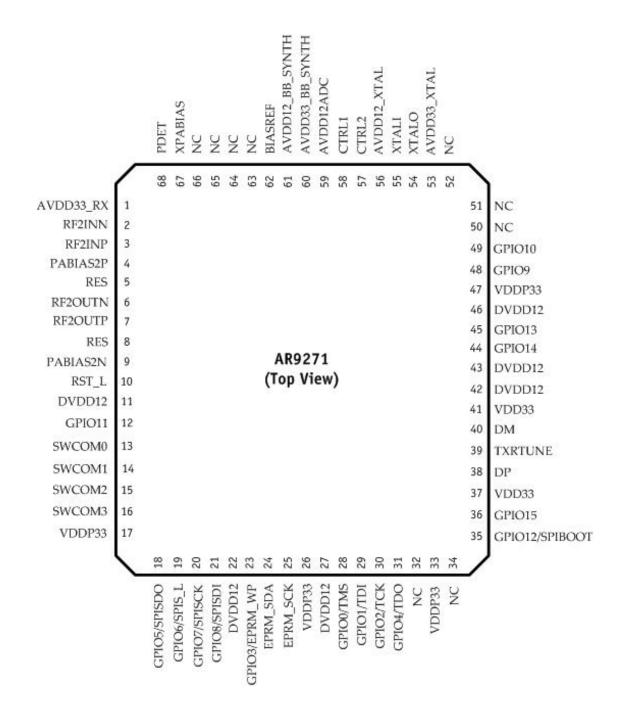

# 1. Pin Descriptions

This section contains a package pinout (see Figure 1-1 and Table 1-1) and a tabular listing of the signal descriptions.

The following nomenclature is used for signal names:

| NC | No connection should be made to |

|----|---------------------------------|

|    | this pin                        |

- \_L At the end of the signal name, indicates active low signals

- P At the end of the signal name, indicates the positive side of a differential signal

- N At the end of the signal name indicates the negative side of a differential signal

The following nomenclature is used for signal types:

| I Digital input sig | gnal |

|---------------------|------|

|---------------------|------|

I/O A digital bidirectional signal

IA Analog input signal

IA/OA Analog bidirectional signal

IH Input signals with weak internal pull-up, to prevent signals from floating when left open

IL Input signals with weak internal pull-down, to prevent signals from floating when left open

O A digital output signal

OA An analog output signal

OD A digital output signal with open drain

P A power or ground signal

Figure 1-1 shows the LPCC-68 package pinout.

Figure 1-1. LPCC-68 Package Pinout

10

Table 1-1. Signal-to-Pin Relationships and Descriptions

| Symbol                  | Pin | Type  | Description                                                                                                                                                                                                                    |

|-------------------------|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| USB Pins                |     | · L   |                                                                                                                                                                                                                                |

| TXRTUNE                 | 39  | IA/OA | Transmitter Resistor Tune Pin. Connects to an external resistor of 51 $\Omega$ that adjusts the USB 2.0 PHY high-speed source impedance.                                                                                       |

| DM                      | 40  | IA/OA | USB D- Signal. Carries USB data to and from the USB 2.0 PHY                                                                                                                                                                    |

| DP                      | 38  | IA/OA | USB D+ Signal. Carries USB data to and from the USB 2.0 PHY                                                                                                                                                                    |

| Radio                   | ·   |       |                                                                                                                                                                                                                                |

| BIASREF                 | 62  | IA    | BIASREF voltage is 310 mV; must connect a 6.19 K $\Omega$ ± 1% resistor to ground                                                                                                                                              |

| RF2INN                  | 2   | IA    | Differential RF inputs. Use one side for single-ended input.                                                                                                                                                                   |

| RF2INP                  | 3   | IA    |                                                                                                                                                                                                                                |

| RF2OUTN                 | 6   | IA/OA | Differential RF power amplifier output. Differential RF input                                                                                                                                                                  |

| RF2OUTP                 | 7   | IA/OA | for antenna 1. The RF amplifier output only appears on antenna 1. There is a diversity switch inside the AR9271 that selects antenna 1 or antenna 0 for baseband signal processing There is also a Tx/Rx switch for antenna 1. |

| Analog Interface        |     |       |                                                                                                                                                                                                                                |

| PABIAS2N                | 9   | IA    | Bias voltage for internal PA                                                                                                                                                                                                   |

| PABIAS2P                | 4   | IA    |                                                                                                                                                                                                                                |

| PDET                    | 68  | IA    | Input for optional external power detector                                                                                                                                                                                     |

| XPABIAS                 | 67  | OA    | Bias for optional external power amplifier                                                                                                                                                                                     |

| External Switch Control |     |       | 1                                                                                                                                                                                                                              |

| SWCOM0                  | 13  | О     | Common switch control                                                                                                                                                                                                          |

| SWCOM1                  | 14  | О     |                                                                                                                                                                                                                                |

| SWCOM2                  | 15  | О     |                                                                                                                                                                                                                                |

| SWCOM3                  | 16  | О     |                                                                                                                                                                                                                                |

| General                 |     |       |                                                                                                                                                                                                                                |

| RST_L                   | 10  | IH/OD | Reset for the AR9271. This pin has an active open drain pull down that forces it low if either the core or the IO supply is below safe operating limits.                                                                       |

| XTALI                   | 55  | I     | 40 MHz crystal.                                                                                                                                                                                                                |

| XTALO                   | 54  | О     |                                                                                                                                                                                                                                |

| GPIO                    |     |       |                                                                                                                                                                                                                                |

| GPIO0/TMS               | 28  | I/O   | General purpose and multiplexed for JTAG test mode                                                                                                                                                                             |

| GPIO1/TDI               | 29  | I/O   | General purpose and multiplexed for JTAG data input                                                                                                                                                                            |

| GPIO2/TCK               | 30  | I/O   | General purpose and multiplexed for JTAG test clock                                                                                                                                                                            |

| GPIO4/TDO               | 31  | I/O   | General purpose and multiplexed for JTAG data output                                                                                                                                                                           |

| GPIO5/SPISDO            | 18  | I/O   | General purpose and multiplexed serial output data from an SPI device                                                                                                                                                          |

| GPIO6/SPIS_L            | 19  | I/O   | General purpose and multiplexed serial interface enable signal of SPI                                                                                                                                                          |

Table 1-1. Signal-to-Pin Relationships and Descriptions (continued)

| Symbol         | Pin | Type | Description                                                                                                          |

|----------------|-----|------|----------------------------------------------------------------------------------------------------------------------|

| GPIO7/SPISCK   | 20  | I/O  | General purpose and multiplexed serial clock to SPI device                                                           |

| GPIO8/SPISDI   | 21  | I/O  | General purpose and multiplexed serial input data from an SPI device                                                 |

| GPIO9          | 48  | I/O  | General purpose pins                                                                                                 |

| GPIO10         | 49  | I/O  |                                                                                                                      |

| GPIO11         | 12  | I/O  |                                                                                                                      |

| GPIO12/SPIBOOT | 35  | I/O  | If this pin is tied to high at power on, the system will boot from an external SPI Flash instead of the internal ROM |

| GPIO13         | 45  | I/O  | General Purpose Pins                                                                                                 |

| GPIO14         | 44  | I/O  |                                                                                                                      |

| GPIO15         | 36  | I/O  |                                                                                                                      |

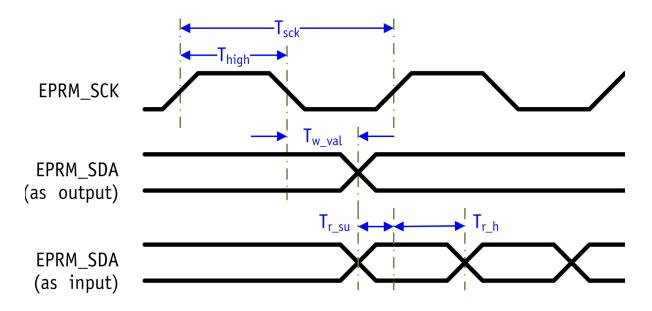

| Serial EEPROM  | 1   | I    |                                                                                                                      |

| GPIO3/EPRM_WP  | 23  | I/O  | Serial EEPROM write protection control output and multiplexed as a general purpose pin                               |

| EPRM_SDA       | 24  | I/O  | Serial EEPROM data                                                                                                   |

| EPRM_SCK       | 25  | О    | Serial EEPROM clock output                                                                                           |

| Symbol             | Pin                                   | Description                                                                          |

|--------------------|---------------------------------------|--------------------------------------------------------------------------------------|

| Power              |                                       |                                                                                      |

| VDD33              | 37, 41                                | Analog 3.3 V power supply for USB PHY                                                |

| VDDP33             | 17, 26, 33, 47                        | Digital 3.3 V power supply                                                           |

| DVDD12             | 11, 22, 27, 42, 43, 46                | Digital 1.2 V power supply                                                           |

| AVDD33_RX          | 1                                     | Analog 3.3 V power supply                                                            |

| AVDD33_XTAL        | 53                                    | Analog 3.3 V power supply                                                            |

| AVDD12_XTAL        | 56                                    | Analog 1.2 V power supply                                                            |

| AVDD12ADC          | 59                                    | Analog 1.2 V power supply                                                            |

| AVDD33_BB_SYNTH    | 60                                    | Analog 3.3 V power supply                                                            |

| AVDD12_BB_SYNTH    | 61                                    | Analog 1.2 V power supply                                                            |

| Ground Pad         |                                       |                                                                                      |

| Exposed Ground Pad | _                                     | Tied to GND (see "Package Dimensions" on page 147)                                   |

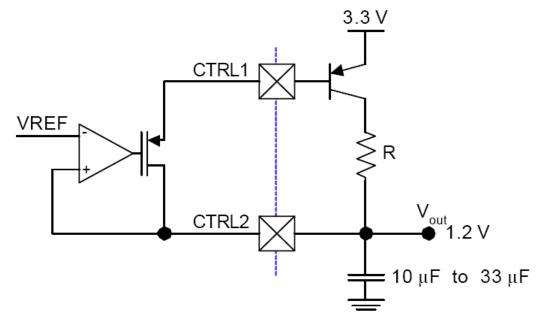

| Control            |                                       |                                                                                      |

| CTRL1              | 58                                    | Used to drive the external PNP device. Connect the base of the external PNP to CTRL1 |

| CTRL2              | 57                                    | Used to drive the LDO output. Connect the collector of the external PNP here         |

| No Connection      |                                       |                                                                                      |

| NC                 | 32, 34, 50, 51, 52, 63, 64,<br>65, 66 | No connect                                                                           |

| Reserved           | 1                                     |                                                                                      |

| RES                | 5,8                                   | Reserved, can be left open or optionally connected to AVDD33                         |

# 2. Functional Description

#### 2.1 Overview

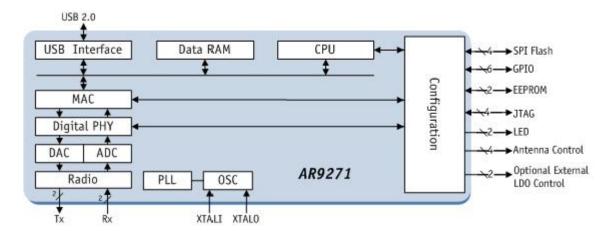

The AR9271 consists of five major functional blocks: CPU, USB 2.0, MAC, digital PHY, and radio.

The IEEE 802.11 MAC functionality is partitioned between the host and the AR9271. IEEE 802.11 MAC data service is provided by the MAC of the AR9271, while the host software, with the aid of the AR9271 MAC, controls Tx and Rx queue processing.

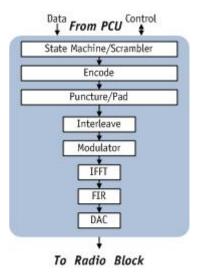

The baseband digital processing functions are implemented by the digital PHY of the AR9271. The radio frequency (RF) and baseband analog processing are provided by the integrated radio. The physical layer (PHY) is partitioned between the baseband processor and the radio. The configuration block, Data RAM, PLL, ADC, DAC, EEPROM interface, JTAG, antenna control, LED and GPIO complete the AR9271 functionality. See Figure 2-1.

Figure 2-1. Functional Block Diagram of the AR9281

#### 2.1.1 Configuration Block

The configuration block provides control, status, and configuration, for each major functional block. This block contains registers accessed by other blocks and by the host using the USB interface. See "Register Descriptions" on page 37 for more information.

#### 2.1.2 AR9271 Address MAP

Internal registers of the various functional blocks and the AR9271 peripheral interface are accessible with the host using the USB interface. These register locations are defined as offset addresses. The combination of the host base address and the offset address allows access to a particular internal register. Table 2-1 lists the offset addresses for the AR9271 internal registers and peripheral interface.

Table 2-1. CPU Block Address Map

| Address                   | Description                   | Usage                               |  |

|---------------------------|-------------------------------|-------------------------------------|--|

| 0x0001_0000 - 0x0001_FFFF | USB Controller PIO Registers  | USB Programmed Input Output         |  |

| 0x0005_0000 - 0x0005_0FFF | Reset/Clock Control Registers | Reset/Clock Control                 |  |

| 0x0005_5000 - 0x0005_5FFF | USB Controller DMA Registers  | USB Rx/Tx DMA Control               |  |

| 0x0005_B000 - 0x0005_BFFF | SPI Control Registers         | Serial Peripheral Interface Control |  |

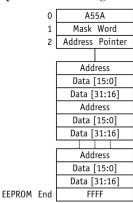

## 2.1.3 Serial EEPROM Interface

The AR9281 provides a serial interface to access an external EEPROM. The EEPROM interface modifies configuration space registers and configuration- and vendor-specific information.

The off-chip EEPROM can be:

A 4-Kb device, organized as 256 entries of 16 bits each (256x16)

The hardware automatically detects the EEPROM size. The EEPROM addressing is 16 bits wide, with each 16-bit EEPROM mapped into the AR9281's register space. Each 32-bit aligned address corresponds to a unique EEPROM location. Because the host interface supports 32-bit register accesses and ignores the two least significant address bits, the address offset provided by the host interface corresponds to four times the EEPROM location.

At reset, some USB configuration registers load from the EEPROM while others are programmed by the host or initialized by AR9281 hardware. To ensure that the EEPROM contents are valid, a 16-bit word at address offset 0x2000 is checked. If the values do not match 0xA55A, the EEPROM contents are ignored and the default values loaded. More information is provided in "Host Interface Registers" on page 93.

#### 2.1.4 EEPROM Auto-Sizing Mechanism

The first procedure after reset is to read the offset address 0x2000 to check for the content 0xA55A. The EEPROM physical presence, programmed state, and size are determined automatically. If the offset address 0x2000 contents do not match the 0xA55A value for any supported EEPROM sizes, the AR9281 assumes the EEPROM is not present on the PCB, or is present but not programmed. In either case, the logic uses the default values as described in "Serial EEPROM Interface".

# 2.1.5 EEPROM Read/Write Protection Mechanism

The EEPROM contains a 16-bit word protect mask value at address location 0x2010 that prevents software from accessing certain regions. The mask is 16 bits wide and contains eight sub-masks that are 2 bits wide.

The sub-mask can have four values that determine the access types permitted to the associated protection region:

- 00: Read/write access allowed

- 01: Write-only access allowed

- 10: Read-only access allowed

- 11: No access allowed

#### 2.2 Reset

The RST\_L pin controls the AR9281 chip reset. The AR9281 host interface receives one reset signal as below:

RST\_L pin Controls the AR9281 power reset

In addition, the RTC\_RESET register provides software control of warm reset for the MAC/baseband and PCU blocks. See the register "RTC Reset and Force Sleep and Force Wakeup (RTC\_RESET)" on page 105.

#### 2.3 GPIO

The AR9281 provides sixteen configurable bidirectional general purpose I/O ports. Each GPIO can be independently configured as input or output using the GPIO control register. Information presented at the GPIO inputs and outputs can be read from the register H\_GPIO\_IN\_OUT (see "GPIO Input and Output (H\_GPIO\_IN\_OUT)" on page 98).

#### 2.4 LED

The AR9281 provides GPIO pins to configure for LED output. Control for LED output is provided by the MAC\_LED register (see "MAC Interface Registers" on page 108).

#### 2.5 USB Host Interface

This section provides a summary of the AR9281 USB interface. This interface is compliant with the USB 2.0 standard. It functions as the host interface for the AR9281, providing data and command transfer between the host software, the MAC, and the configuration registers. For details, refer to the USB 2.0 standards specifications.

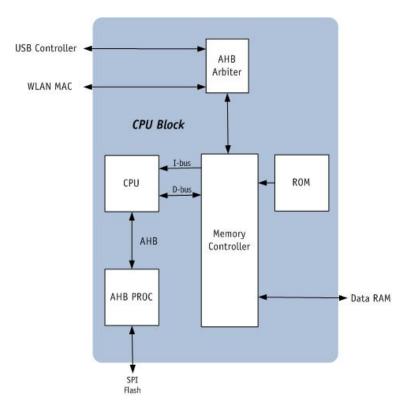

#### 2.6 The CPU Block

The CPU Block includes five major parts: CPU, Memory Controller, AHB Arbiter, the internal memory and the AHB process. The CPU Block controls the data path from the host to the WLAN and vice versa. The CPU Block also

includes controlling the external SPI flash. See Figure 2-2 for a visual description of the CPU block.

Figure 2-2. CPU Block

#### 2.6.1 The CPU

The AR9271 uses an embedded CPU (117 MHz) which has three IO ports for data access. The I-bus is the channel used to get the program code from the ROM or the RAM. The D-bus is used to access data in the RAM. The AHB port provides the channel to access the SPI flash and controls access to the MAC registers.

#### 2.6.2 Memory Controller and the AHB Arbiter

The Memory Controller module provides the channel for bus masters to access the memories within the AR9271. The internal ROM can be accessed by the CPU only, and the RAM can be accessed by the CPU, MAC DMA and the USB DMA. The AHB arbiter provides arbitration for these three masters. The Priority changes and determined by round-robin scheduling.

#### 2.6.3 Internal Memories

The AR9271 has two internal memories, the ROM (24 KB) and the RAM (160 KB). The ROM provides the boot up sequence and various control mechanisms. The RAM is used to store part of the program code and all data packets for transmission and receiving.

#### 2.6.4 The AHB Proc

The AHB Proc is a channel for the CPU to access the external flash. The CPU also accesses the MAC registers through the AHB Proc.

# 3. Medium Access Control (MAC)

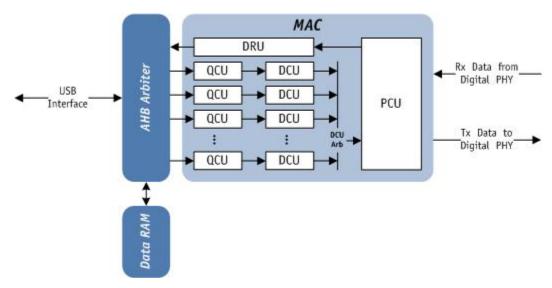

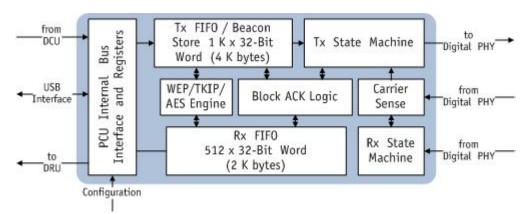

The MAC consists of the following major functional blocks: 10 queue control units (QCUs), 10 distributed coordination function

(DCF) control units (DCUs), a single DMA Rx unit (DRU), and a single protocol control unit (PCU). See Figure 3-1.

Figure 3-1. MAC Block Diagram

#### 3.1 Overview

The MAC block supports full bus-mastering descriptor-based scatter/gather DMA. Frame transmission begins with the QCUs. QCUs manage the DMA of frame data from the host through the USB interface, and determine when a frame is available for transmission.

Each QCU targets exactly one DCU. Ready frames are passed from a QCU to its targeted DCU. The DCU manages the enhanced distributed coordination function (EDCF) channel access procedure on behalf of the QCUs associated with it.

Functionality of the MAC block includes:

- Tx frame data transfer from the host to the radio block using the USB interface

- Rx frame data transfer from the radio block to host using the USB interface

- Register access to all AR9281 registers

- Interrupt generation and reporting

- Sleep-mode (power-down) sequencing

- Miscellaneous error and status reporting functions

Once the DCU gains access to the channel, it passes the frame to the PCU, which encrypts the frame and sends it to the baseband logic. The PCU handles both processing responses to the transmitted frame, and reporting the transmission attempt results to the DCU.

Frame reception begins in the PCU, which receives the incoming frame bitstream from the digital PHY. The PCU decrypts the frame and passes it to the DRU, which manages Rx descriptors and writes the incoming frame data and status to the host memory through the USB interface.

#### 3.2 Descriptor

The MAC is responsible for transferring frames between the host memory (accessed using the USB interface) and the AR9281. For all normal frame transmit/receive activity, the host provides a series of descriptors to the MAC, and the MAC then parses the descriptors and performs the required set of data transfers.

# 3.3 Descriptor Format

The transmit (Tx) descriptor format contains twenty-four 32-bit words and the receive (Rx) descriptor thirteen 32-bit words (see Table 3-1).

The first two words of the descriptor point to the next descriptor in the linked list and to the data buffer associated with the descriptor. Other words carry additional control information that affects how the MAC processes the frame and its data.

A descriptor is required to be aligned on a 32-bit boundary in host memory, although best performance is achieved if the descriptor is aligned on a cache-line boundary. The MAC uses the final two words to report status information back to the host. See:

| Table     | Description                               |

|-----------|-------------------------------------------|

| Table 3-1 | DMA descriptor format                     |

| Table 3-2 | Tx control descriptor format (words 2–13) |

| Table 3-3 | Tx status descriptors<br>(words 14–23)    |

| Table 3-4 | Rx control descriptor (words 2–3)         |

| Table 3-5 | Rx status descriptor<br>(words 4–12)      |

Table 3-1. DMA Descriptor Format

| Word                    | Bits | Field Name                                       | Description                                                                                                                                                                                                                                                                                                                                                      |

|-------------------------|------|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                       | 31:0 | link_ptr                                         | Link pointer. Contains the address of the next descriptor to be used; must be 32-bit aligned (bits [1:0] must be 0)                                                                                                                                                                                                                                              |

| 1                       | 31:0 | buf_ptr                                          | Data buffer pointer. Contains the starting address of the data buffer associated with this descriptor. A Tx data buffer can begin at any byte address. A Rx data buffer must be aligned on a 32-bit boundary in host memory, although best performance is achieved if the Rx data buffer is cache-line aligned.  (Cache-line size varies from system to system.) |

| 2–13 (Tx)<br>2–3 (Rx)   | 31:0 | Host-to-<br>DMA engine<br>control<br>information | Additional control information is passed from host to DMA engine. The format of these words varies depending on whether the descriptor is being used to Tx a frame from host to PCU, or Rx a frame from PCU to host. (See Table 3-2 on page 19, and Table 3-4 on page 29 for details.)                                                                           |

| 14–23 (Tx)<br>4–12 (Rx) | 31:0 | DMA<br>completion<br>status<br>information       | Status information reported by the DMA engine when it has finished processing a descriptor. As with the control information, the format of the status information differs between Tx and Rx descriptors. (See Table 3-3 on page 25, and Table 3-5 on page 29 for details.)                                                                                       |

The Tx descriptor format for words 2 through 13 is described in Table 3-2.

Table 3-2. Tx Control Descriptor Format (Words 2-13)

| Word                | Bits  | Field Name       | Description                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|---------------------|-------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 2                   | 11:0  | frame_length     | Frame length Specifies the length, in bytes, of the entire MAC frame, including the frame check sequence (FCS), initialization vector (IV), and integrity check value (ICV) fields.                                                                                                                                                                                                 |  |  |

|                     | 12    | vmf              | Virtual more fragment If this bit is set, bursting is enabled for this frame. If no burst is in progress, it initiates a CTS-protected burst if cts_enable is set. If a previous burst is in progress, it ignores the cts_enable bit and assumes the burst is protected.                                                                                                            |  |  |

|                     | 13    | RES              | Reserved                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|                     | 14    | low_rx_chain     | When set to 1, indicates that the Rx chain mask switches to low power mode after transmitting this frame                                                                                                                                                                                                                                                                            |  |  |

|                     | 15    | clear_retry      | Setting this bit disables the retry bit from being set in the Tx header on a frame retry                                                                                                                                                                                                                                                                                            |  |  |

|                     | 21:16 | tpc_0            | Tx power control for series 0 These bits pass unchanged to the baseband, where they are used to control the transmit power for the frame.                                                                                                                                                                                                                                           |  |  |

|                     | 22    | rts_enable       | Request to send (RTS) enable. At most, one of the "rts_enable" and "cts_enable" bits may be set; it is illegal to set both.                                                                                                                                                                                                                                                         |  |  |

|                     |       |                  | set PCU transmits the frame using the RTS/CTS protocol clear PCU transmits the frame using the contention/backoff protocol                                                                                                                                                                                                                                                          |  |  |

|                     | 23    | veol             | Virtual end-of-list flag  When set, indicates that the QCU should act as though the descriptor had a NULL LinkPtr, even if the LinkPtr is not NULL. Must be valid in the final descriptor of a frame and must be clear for all other descriptors of the frame.                                                                                                                      |  |  |

|                     | 24    | clear_dest_mask  | Clear destination mask bit flag If set, instructs the PCU and DCU to clear the destination mask bit at the index specified by the DestIdx field.                                                                                                                                                                                                                                    |  |  |

|                     | 28:25 | RES              | Reserved                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|                     | 29    | int_req          | Interrupt request flag Set to one by the driver to request that the DMA engine generate an interrupt upon completion of the frame to which this descriptor belongs.  Note that this field must be valid and identical for all descriptors of the frame; that is, all descriptors for the frame must have this flag set, or all descriptors for the frame must have this flag clear. |  |  |

| 30 dest_index_valid |       | dest_index_valid | Destination index valid flag Specifies whether the contents of the DestIdx field are valid.                                                                                                                                                                                                                                                                                         |  |  |

|                     | 31    | cts_enable       | Proceed frame with CTS flag  If set, the PCU first sends a CTS before sending the frame described by the descriptor. Used for 802.11g and Atheros XR frames to quiet legacy stations before sending a frame the legacy stations cannot interpret (even at the PHY level). At most, one of the "rts_enable" and "cts_enable" bits may be set; it is illegal to set both bits.        |  |  |

Table 3-2. Tx Control Descriptor Format (Words 2–13) (continued)

| Word | Bits  | Field Name   | Description                                                                                                                                                                                                                                                                                                             |