### **AS1108**

## 4-Digit LED Display Driver

## 1 General Description

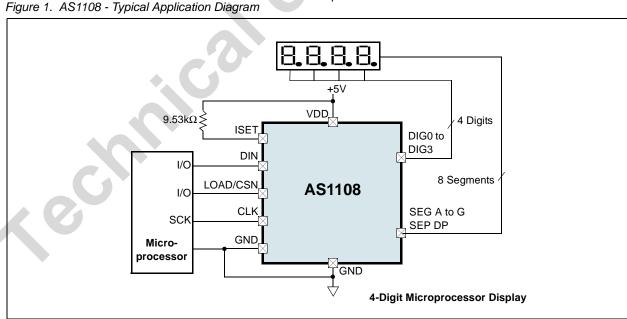

The AS1108 is a compact display driver for 7-segment numeric displays of up to 4 digits. The device can be programmed via SPI, QSPI, and Microwire as well as a conventional 4-wire serial interface.

The device includes an integrated BCD code-B/HEX decoder, multiplex scan circuitry, segment and display drivers, and a 32-bit memory. Internal memory stores the LED settings, eliminating the need for continuous device reprogramming.

Every segment can be individually addressed and updated separately. Only one external resistor (RSET) is required to set the current through the LED display. LED brightness can be controlled by analog or digital means. The device can be programmed to use the internal code-B/HEX decoder to display numeric digits or to directly address each segment.

The AS1108 features an extremely low shutdown current of typically  $3\mu A$ , and an operational current of less than  $500\mu A$ . The number of digits can be programmed, the device can be reset by software, and an external clock is also supported. Additionally, segment blinking can be synchronized across multiple drivers.

The AS1108 provides several test modes for easy application debugging.

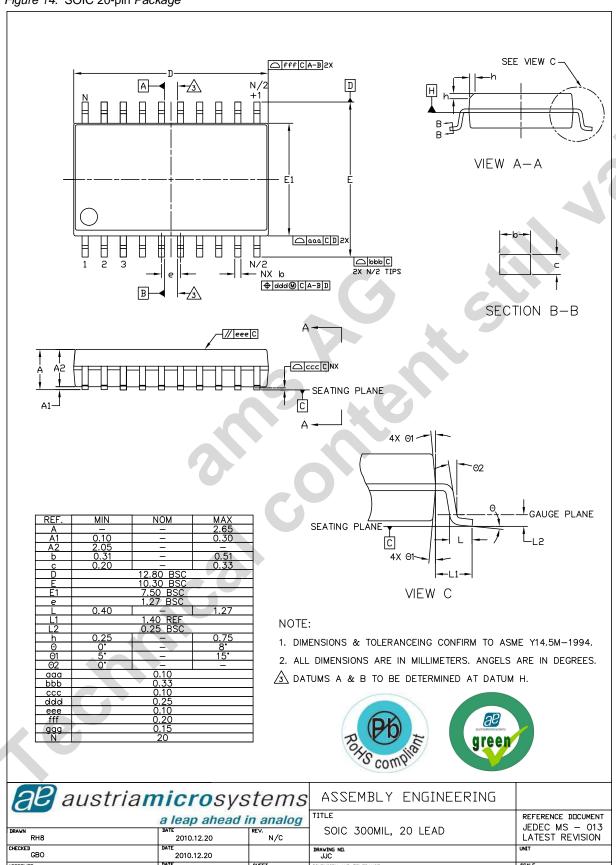

The device is available in a SOIC 20-pin package.

## 2 Key Features

- 10MHz SPI-, QSPI-, Microwire-Compatible Serial I/O

- Individual LED Segment Control

- Segment Blinking Control (can be synchronized across multiple drivers)

- Hexadecimal- or BCD-Code/No-Decode Digit Selection

- 3µA Low-Power Shutdown Current (typ; data retained)

- Extremely Low Operating Current 0.5mA in Open-Loop

- Digital and Analog Brightness Control

- Display Blanked on Power-Up

- Drive Common-Cathode LED Displays

- Supply Voltage Range: +2.7 to +5.5V

- Software Reset

- Optional External Clock

- SOIC 20-pin package

# 3 Applications

The AS1108 is ideal for bar-graph displays, instrumentpanel meters, LED matrix displays, dot matrix displays, set-top boxes, white goods, professional audio equipment, medical equipment, industrial controllers and panel meters.

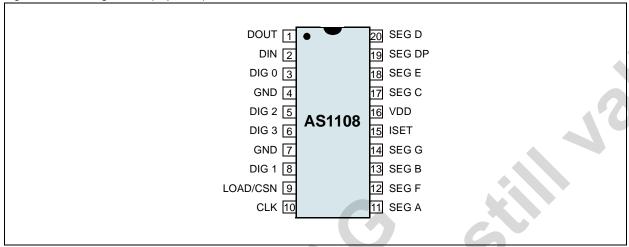

## 4 Pinout

## **Pin Assignments**

Figure 2. Pin Assignments (Top View)

### **Pin Descriptions**

Table 1. Pin Descriptions

| Pin Number                        | Pin Name               | Description                                                                                                                                                                                                                                                              |

|-----------------------------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                 | DOUT                   | Serial-Data Output. The data into pin DIN is valid at pin DOUT 16.5 clock cycles later. This pin is used to daisy-chain several AS1108 devices and is never high-impedance.                                                                                              |

| 2                                 | DIN                    | <b>Serial-Data Input</b> . Data is loaded into the internal 16-bit shift register on the rising edge of pin CLK.                                                                                                                                                         |

| 3, 5, 6, 8                        | DIG 0:DIG 3            | <b>Digit Drive Lines</b> . 4 four-digit drive lines that sink current from the display common cathode. The AS1108 pulls the digit outputs to VDD when turned off.                                                                                                        |

| 4, 7                              | GND                    | Ground. Both GND pins must be connected.                                                                                                                                                                                                                                 |

| 9                                 | LOAD/CSN               | Load-Data Input. The last 16 bits of serial data are latched on the rising edge of this pin.  Chip-Select Input (AS1108 SPI-enabled only). Serial data is loaded into the                                                                                                |

| y                                 | LOAD/CSIV              | shift register while this pin is low. The last 16 bits of serial data are latched on the rising edge of this pin.                                                                                                                                                        |

| 10                                | CLK                    | Serial-Clock Input. 10MHz maximum rate. Data is shifted into the internal shift register on the rising edge of this pin. Data is clocked out of DOUT on the falling edge of this pin. On the AS1108 SPI-enabled, the CLK input is active only while pin LOAD/CSN is low. |

| 11, 12, 13, 14,<br>17, 18, 19, 20 | SEG A:SEG G,<br>SEG DP | Seven Segment and Decimal Point Drive Lines. 8 seven-segment drives and decimal point drive that source current to the display. When a segment driver is turned off it is pulled to GND.                                                                                 |

| 15                                | ISET                   | <b>Set Segment Current</b> . Connect to VDD through RSET to set the peak segment current (see Selecting RSET Resistor Value and Using External Drivers on page 14).                                                                                                      |

| 16                                | VDD                    | Positive Supply Voltage. Connect to +2.7 to +5.5V supply.                                                                                                                                                                                                                |

# 5 Absolute Maximum Ratings

Stresses beyond those listed in Table 2 may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in Section 6 Electrical Characteristics on page 4 is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Table 2. Absolute Maximum Ratings

| Parameter                                 | Min  | Max                   | Units | Notes                                                                                                                                                                                                                                                                                        |

|-------------------------------------------|------|-----------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Electrical Parameters                     |      |                       |       |                                                                                                                                                                                                                                                                                              |

| VDD to GND                                | -0.3 | 7                     | V     |                                                                                                                                                                                                                                                                                              |

| All other pins to GND                     | -0.3 | VDD + 0.3<br>(max 7V) | V     | 10                                                                                                                                                                                                                                                                                           |

| Current                                   | •    |                       |       |                                                                                                                                                                                                                                                                                              |

| DIG 0:DIG 3 Sink Current                  |      | 500                   | mA    |                                                                                                                                                                                                                                                                                              |

| SEG A:SEG G, SEG DP                       |      | 100                   | mA    |                                                                                                                                                                                                                                                                                              |

| Latch-Up Immunity                         |      | ±200                  | mA    | All pins except AS1108 pin 11: ±180 mA<br>Norm: JEDEC 78                                                                                                                                                                                                                                     |

| Electrostatic Discharge                   |      |                       |       |                                                                                                                                                                                                                                                                                              |

| Digital outputs                           |      | 1000                  | V     | Norm: MIL 883 E method 3015                                                                                                                                                                                                                                                                  |

| All other pins                            |      | 1000                  | ٧     | NOITH. WILL 663 E Method 3015                                                                                                                                                                                                                                                                |

| Continuous Power Dissipation (TA = +85°C) |      |                       |       |                                                                                                                                                                                                                                                                                              |

| Wide SOIC                                 | G    | 941                   | mW    | Derate 11.8mW/°C<br>above +70°C                                                                                                                                                                                                                                                              |

| Temperature Ranges and Storage Conditions |      |                       | YK    |                                                                                                                                                                                                                                                                                              |

| Storage Temperature Range                 | -55  | +150                  | °C    |                                                                                                                                                                                                                                                                                              |

| Package Body Temperature (Wide SOIC)      |      | +260                  | °C    | The reflow peak soldering temperature (body temperature) specified is in accordance with IPC/<br>JEDEC J-STD-020 "Moisture/Reflow Sensitivity<br>Classification for Non-Hermetic Solid State Surface<br>Mount Devices".  The lead finish for Pb-free leaded packages is matte tin (100% Sn). |

| Humidity                                  | 5    | 85                    | %     | Non-condensing                                                                                                                                                                                                                                                                               |

| Moisture Sensitive Level                  |      | 3                     |       | Represents a max. floor life time of 168h                                                                                                                                                                                                                                                    |

## **6 Electrical Characteristics**

VDD = 2.7V to 5.5V, RSET = 9.53 $k\Omega \pm 1\%$ , TAMB = TMIN to TMAX (unless otherwise specified). All limits are guaranteed. The parameters with min and max values are guaranteed with production tests or SQC (Statistical Qualification Control) methods.

Table 3. Electrical Characteristics

| Parameter                                                       | Symbol     | Conditions                                        | Min  | Тур  | Max  | Unit |

|-----------------------------------------------------------------|------------|---------------------------------------------------|------|------|------|------|

| Operating Temperature Range                                     | Тамв       |                                                   | 0    |      | +70  | C.   |

| Operating Supply Voltage                                        | VDD        |                                                   | 2.7  | 5.0  | 5.5  | V    |

| Shutdown Supply Current                                         | IDDSD      | All digital inputs at VDD or GND,<br>TAMB = +25°C |      |      | 10   | μΑ   |

|                                                                 |            | RSET = open circuit.                              |      |      | 1    |      |

| Operating Supply Current                                        | IDD        | All segments and decimal point on; ISEG = -40mA.  |      | 330  | 4    | mA   |

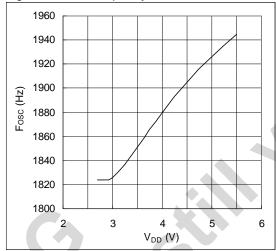

| Display Scan Rate                                               | fosc       | 4 digits scanned                                  | 1000 | 1600 | 2600 | Hz   |

| Digit Drive Sink Current                                        | Idigit     | Vout = 0.65V                                      | 320  |      |      | mA   |

| Segment Drive Source Current                                    | ISEG       | VDD = 5.0V, VOUT = (VDD -1V)                      | -30  | -40  | -45  | mA   |

| Segment Drive Current Matching                                  | ΔISEG      |                                                   |      | 3.0  |      | %    |

| Digit Drive Source Current                                      | Idigit     | Digit off, $VDIGIT = (VDD - 0.3V)$                | -2   |      |      | mA   |

| Segment Drive Sink Current                                      | Iseg       | Segment off, VSEG = 0.3V                          | 5    |      |      | mA   |

| Slow Segment Blink Period (ON phase, Internal Oscillator)       | tslowblink |                                                   | 0.64 | 1    | 1.65 | s    |

| Fast Segment Blink Period (ON phase, Internal Oscillator)       | tFASTBLINK |                                                   | 0.32 | 0.5  | 0.83 | S    |

| Fast or Slow Segment Blink Duty<br>Cycle (Guaranteed by design) |            |                                                   | 49.9 | 50   | 50.1 | %    |

Table 4. Logic Inputs/Outputs Characteristics

| Parameter                        | Symbol         | Conditions                                | Min       | Тур | Max | Unit |

|----------------------------------|----------------|-------------------------------------------|-----------|-----|-----|------|

| Input Current DIN, CLK, LOAD/CSN | IIH, IIL       | VIN = 0V or VDD                           | -1        |     | 1   | μΑ   |

| Logic High Input Voltage         | VIH            |                                           | 0.7 x VDD |     |     | V    |

| Logic Low Input Voltage          | VIL            | VDD = 5.0V ± 10%                          |           |     | 0.8 | V    |

| Logic Low Input Voltage          | VIL            | VDD = 3.0V ± 10%                          |           |     | 0.6 | v    |

| Output High Voltage              | Voн            | DOUT, ISOURCE = -1mA,<br>VDD = 5.0V ± 10% | VDD - 1   |     |     | V    |

| Output Flight Voltage            | VOIT           | DOUT, ISOURCE = -1mA,<br>VDD = 3.0V ± 10% | VDD - 0.5 |     |     | V    |

| Output Low Voltage               | Vol            | DOUT, ISINK = 1.6mA                       |           |     | 0.4 | V    |

| Hysteresis Voltage               | $\Delta V_{I}$ | DIN, CLK, LOAD/CSN                        |           | 1   |     | V    |

Table 5. Timing Characteristics (see Figure 10 on page 8)

| Parameter                                                 | Symbol | Conditions   | Min | Тур | Max  | Unit |

|-----------------------------------------------------------|--------|--------------|-----|-----|------|------|

| CLK Clock Period                                          | tCP    |              | 100 |     |      | ns   |

| CLK Pulse Width High                                      | tch    |              | 50  |     |      | ns   |

| CLK Pulse Width Low                                       | tCL    |              | 50  |     |      | ns   |

| CSMFall-to-CLK Rise Setup Time<br>(AS1108 SPI-programmed) | tcss   |              | 25  |     |      | ns   |

| CLK Rise-to -LOAD/CSN Rise Hold Time                      | tcsh   |              | 0   |     |      | ns   |

| DIN Setup Time                                            | tDS    |              | 25  |     |      | ns   |

| DIN Hold Time                                             | tDH    |              | 0   |     |      | ns   |

| Output Data Propagation Delay                             | tDO    | CLOAD = 50pF |     |     | 25   | ns   |

| LOAD Rising Edge-to-Next Clock Rising Edge                | tldck  |              | 50  |     |      | ns   |

| Minimum LOAD/CSN Pulse High                               | tcsw   |              | 50  |     |      | ns   |

| Data-to-Segment Delay                                     | tDSPD  |              |     |     | 2.25 | ms   |

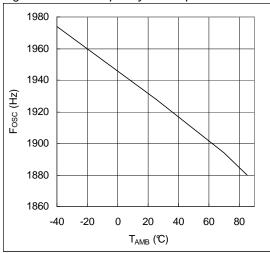

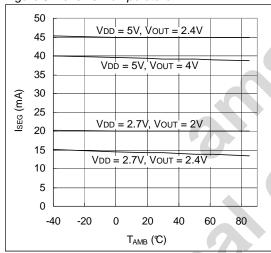

# 7 Typical Operating Characteristics

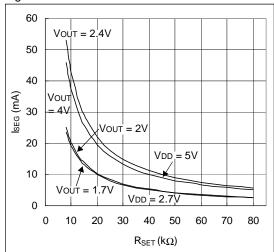

VDD = 5V,  $RSET = 9.53k\Omega$ ,  $TAMB = 25^{\circ}C$  (unless otherwise specified).

Figure 3. Scan Frequency vs. Temperature

Figure 5. ISEG vs. Temperature

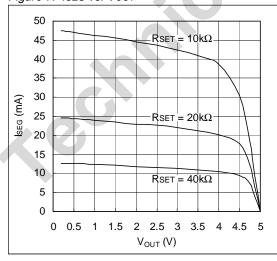

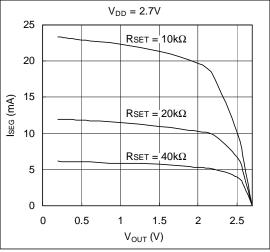

Figure 7. ISEG vs. Vout

Figure 4. Scan Frequency vs. VDD

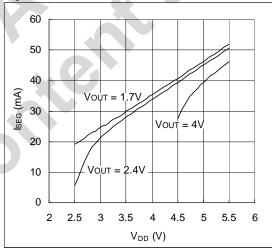

Figure 6. ISEG vs. VDD

Figure 8. ISEG vs. Vout

Figure 9. ISEG vs. RSET

# **8 Detailed Description**

#### **Serial-Addressing Format**

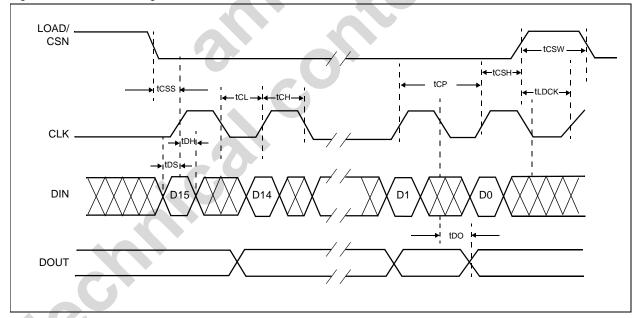

Programming the AS1108 is accomplished by writing to the device's internal registers (see Digit- and Control-Registers on page 9) via the 4-wire serial interface. A programming sequence consists of 16-bit packages as depicted in Table 6.

The data is shifted into the internal 16-bit register with the rising edge of the CLK signal. With the rising edge of the LOAD/CSN signal the data is latched into a digit- or control-register. The LOAD/CSN signal must go high after the 16th rising clock edge.

The LOAD/CSN signal can also come later but this must happen just before the next rising edge of CLK, otherwise the data will be lost. The contents of the internal shift register are applied 16.5 clock cycles later to pin DOUT. The data is clocked out at the falling edge of CLK.

The first 4 bits (D15:D12) are "don't care" settings, bits D11:D8 contain the register address, and bits D7:D0 contain the data. The first bit is D15, the most significant bit (MSB). The exact timing is shown in Figure 10.

Table 6. 16-Bit Serial Data Format

| D15 | D14 | D13 | D12 | D11     | D10     | D9                   | D8       | D7  | D6 | D5 | D4 | D3  | D2 | D1 | D0  |

|-----|-----|-----|-----|---------|---------|----------------------|----------|-----|----|----|----|-----|----|----|-----|

| Χ   | X   | Х   | Х   | Registe | r Addre | ss (see <sup>-</sup> | Table 7) | MSB |    |    | Da | ıta |    | >  | LSB |

#### **Initial Power-Up**

On initial power-up, the AS1108 registers are reset to their default values, the display is blanked, and the device goes into shutdown mode. All registers should be programmed for normal operation at this time.

**Note:** The default settings enable only scanning of one digit; the internal decoder is disabled and the Intensity Control Register (see page 12) is set to the minimum values.

Figure 10. Interface Timing

#### **Shutdown Mode**

The AS1108 features a shutdown mode, consuming only 10µA (max) current. Shutdown mode is entered via a write to the Shutdown Register (see Table 8). At that point, all segment current sources are pulled to ground and all digit drivers are connected to VDD, so that all segments are blanked.

Note: During shutdown mode the Digit-Registers maintain their data.

Shutdown mode can either be used as a means to reduce power consumption or for generating a flashing display (repeatedly entering and leaving shutdown mode). For minimum supply current in shutdown mode, logic input should be at GND or VDD (CMOS logic level).

The device needs typically 250µs to exit shutdown mode, and during shutdown mode the AS1108 is fully programmable. Only the display test mode (see page 11) overrides shutdown mode.

When entering or leaving shutdown mode, the Feature Register is reset to its default values (all 0s) when Shutdown Register bit D7 (page 10) = 0. When bit D7 = 1, the Feature Register is left unchanged when entering or leaving shutdown mode.

**Note:** If the AS1108 is used with an external clock, Shutdown Register bit D7 should be set to 1 when writing to the Shutdown Register.

### **Digit- and Control-Registers**

The AS1108 contains four Digit-Registers and six control-registers, which are listed in Table 7. All registers are selected using a 4-bit address word, and communication is done via the serial interface.

- Digit Registers These registers are realized with an on-chip 32-bit memory. Each digit can be controlled directly without rewriting the whole register contents.

- Control Registers These registers consist of decode mode, display intensity, number of scanned digits, shutdown, display test and features selection registers.

Table 7. Register Address Map

| Register          | HEX Code |         |     | Address |    |    | Dogo |

|-------------------|----------|---------|-----|---------|----|----|------|

| Register          | HEX Code | D15:D12 | D11 | D10     | D9 | D8 | Page |

| No-Op             | 0xX0     | Х       | 0   | 0       | 0  | 0  | 13   |

| Digit 0           | 0xX1     | X       | 0   | 0       | 0  | 1  | N/A  |

| Digit 1           | 0xX2     | X       | 0   | 0       | 1  | 0  | N/A  |

| Digit 2           | 0xX3     | Х       | 0   | 0       | 1  | 1  | N/A  |

| Digit 3           | 0xX4     | Х       | 0   | 1       | 0  | 0  | N/A  |

| Decode-Mode       | 0xX9     | Х       | 1   | 0       | 0  | 1  | 10   |

| Intensity Control | 0xXA     | Х       | 1   | 0       | 1  | 0  | 12   |

| Scan Limit        | 0xXB     | Х       | 1   | 0       | 1  | 1  | 12   |

| Shutdown          | 0xXC     | Х       | 1   | 1       | 0  | 0  | 10   |

| N/A               | 0xXD     | Х       | 1   | 1       | 0  | 1  | N/A  |

| Feature           | 0xXE     | Х       | 1   | 1       | 1  | 0  | 13   |

| Display Test      | 0xXF     | Х       | 1   | 1       | 1  | 1  | 11   |

#### Shutdown Register (0xXC)

The Shutdown Register controls AS1108 shutdown mode (see Shutdown Mode on page 9).

Table 8. Shutdown Register Format (Address (HEX) = 0xXC))

| Mode                                                            | HEX Code | Register Data |    |    |    |    |    |    |    |  |  |

|-----------------------------------------------------------------|----------|---------------|----|----|----|----|----|----|----|--|--|

| Mode                                                            | HEX Code | D7            | D6 | D5 | D4 | D3 | D2 | D1 | D0 |  |  |

| Shutdown Mode,<br>Reset Feature Register to Default Settings    | 0x00     | 0             | Х  | Х  | Х  | Х  | Х  | Х  | 0  |  |  |

| Shutdown Mode, Feature Register Unchanged                       | 0x80     | 1             | Х  | Х  | Х  | Х  | Х  | Χ  | 0  |  |  |

| Normal Operation,<br>Reset Feature Register to Default Settings | 0x01     | 0             | Х  | Х  | Х  | Х  | Х  | Х  | 1  |  |  |

| Normal Operation, Feature Register Unchanged                    | 0x81     | 1             | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | 1  |  |  |

#### Decode Enable Register (0xX9)

The Decode Enable Register sets the decode mode. BCD/HEX decoding (either BCD code – characters 0:9, E, H, L, P, and -, or HEX code – characters 0:9 and A:F) is selected by bit D2 (page 13) of the Feature Register. The Decode Enable Register is used to select the decode mode or no-decode for each digit. Each bit in the Decode Enable Register corresponds to its respective display digit (i.e., bit D0 corresponds to digit 0, bit D1 corresponds to digit 1 and so on). Table 10 lists some examples of the possible settings for the Decode Enable Register bits.

Note: A logic high enables decoding and a logic low bypasses the decoder altogether.

When decode mode is used, the decoder looks only at the lower-nibble (bits D3:D0) of the data in the Digit-Registers, disregarding bits D6:D4. Bit D7 sets the decimal point (SEG DP) independent of the decoder and is positive logic (bit D7 = 1 turns the decimal point on). Table 10 lists the code-B font; Table 11 lists the HEX font.

When no-decode mode is selected, data bits D7:D0 of the Digit-Registers correspond to the segment lines of the AS1108. Table 12 shows the 1:1 pairing of each data bit and the appropriate segment line.

Table 9. Decode Enable Register Format (Address (HEX) = 0xX9))

| Decode Mode                                             | HEX Code | Register Data |    |    |    |    |    |    |    |  |  |

|---------------------------------------------------------|----------|---------------|----|----|----|----|----|----|----|--|--|

| Decode Mode                                             | HEX Code | D7            | D6 | D5 | D4 | D3 | D2 | D1 | D0 |  |  |

| No decode for digits 3:0                                | 0x00     | Χ             | Χ  | Χ  | Χ  | 0  | 0  | 0  | 0  |  |  |

| Code-B/HEX decode for digit 0. No decode for digits 3:1 | 0x01     | Х             | Х  | Х  | Х  | 0  | 0  | 0  | 1  |  |  |

| Code-B/HEX decode for digits 3:0                        | 0xFF     | Х             | Х  | Х  | Х  | 1  | 1  | 1  | 1  |  |  |

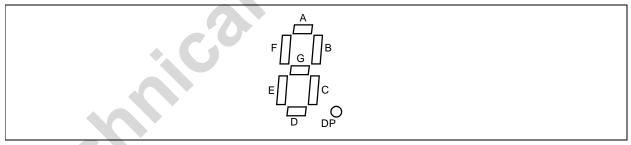

Figure 11. Standard 7-Segment LED Intensity Control and Inter-Digit Blanking

Table 10. Code-B Font

| 7-Segment              |                 |       | Regist | ter Da | ta |    |                 | On Segments = 1 |   |   |   |   |   |   |  |

|------------------------|-----------------|-------|--------|--------|----|----|-----------------|-----------------|---|---|---|---|---|---|--|

| 7-Segment<br>Character | D7 <sup>†</sup> | D6:D4 | D3     | D2     | D1 | D0 | DP <sup>†</sup> | Α               | В | С | D | Е | F | G |  |

| 0                      |                 | Х     | 0      | 0      | 0  | 0  |                 | 1               | 1 | 1 | 1 | 1 | 1 | 0 |  |

| 1                      |                 | Χ     | 0      | 0      | 0  | 1  |                 | 0               | 1 | 1 | 0 | 0 | 0 | 0 |  |

| 2                      |                 | Χ     | 0      | 0      | 1  | 0  |                 | 1               | 1 | 0 | 1 | 1 | 0 | 1 |  |

| 3                      |                 | Х     | 0      | 0      | 1  | 1  |                 | 1               | 1 | 1 | 1 | 0 | 0 | 1 |  |

| 4                      |                 | Χ     | 0      | 1      | 0  | 0  |                 | 0               | 1 | 1 | 0 | 0 | 1 | 1 |  |

| 5                      |                 | Χ     | 0      | 1      | 0  | 1  |                 | 1               | 0 | 1 | 1 | 0 | 1 | 1 |  |

Table 10. Code-B Font (Continued)

| 7-Segment              |                 |       |    |    |    | On S | egmen           | ts = 1 |   |   |   |   |   |   |

|------------------------|-----------------|-------|----|----|----|------|-----------------|--------|---|---|---|---|---|---|

| 7-Segment<br>Character | D7 <sup>†</sup> | D6:D4 | D3 | D2 | D1 | D0   | DP <sup>†</sup> | Α      | В | С | D | Е | F | G |

| 6                      |                 | Χ     | 0  | 1  | 1  | 0    |                 | 1      | 0 | 1 | 1 | 1 | 1 | 1 |

| 7                      |                 | X     | 0  | 1  | 1  | 1    |                 | 1      | 1 | 1 | 0 | 0 | 0 | 0 |

| 8                      |                 | X     | 1  | 0  | 0  | 0    |                 | 1      | 1 | 1 | 1 | 1 | 1 | 1 |

| 9                      |                 | Χ     | 1  | 0  | 0  | 1    |                 | 1      | 1 | 1 | 1 | 0 | 1 | 1 |

| -                      |                 | X     | 1  | 0  | 1  | 0    |                 | 0      | 0 | 0 | 0 | 0 | 0 | 1 |

| E                      |                 | Χ     | 1  | 0  | 1  | 1    |                 | 1      | 0 | 0 | 1 | 1 | 1 | 1 |

| Н                      |                 | Χ     | 1  | 1  | 0  | 0    |                 | 0      | 1 | 1 | 0 | 1 | 1 | 1 |

| L                      |                 | Χ     | 1  | 1  | 0  | 1    |                 | 0      | 0 | 0 | 1 | 1 | 1 | 0 |

| Р                      |                 | Χ     | 1  | 1  | 1  | 0    |                 | 1      | 1 | 0 | 0 | 1 | 1 | 1 |

| Blank                  |                 | Χ     | 1  | 1  | 1  | 1    |                 | 0      | 0 | 0 | 0 | 0 | 0 | 0 |

$<sup>^{\</sup>dagger}$  The decimal point is enabled by setting bit D7 = 1.

Table 11. HEX Font

| 7-Segment |                 |       | Regi | ster Da | nta |    |                 |   |   | On Se | egmer | ts = 1 |   |   |

|-----------|-----------------|-------|------|---------|-----|----|-----------------|---|---|-------|-------|--------|---|---|

| Character | D7 <sup>†</sup> | D6:D4 | D3   | D2      | D1  | D0 | DP <sup>†</sup> | Α | В | С     | D     | E      | F | G |

| 0         |                 | Χ     | 0    | 0       | 0   | 0  |                 | 1 | 1 | 1     | 1     | 1      | 1 | 0 |

| 1         |                 | Χ     | 0    | 0       | 0   | 1  |                 | 0 | 1 | 1     | 0     | 0      | 0 | 0 |

| 2         |                 | Χ     | 0    | 0       | 1   | 0  |                 | 1 | 1 | 0     | 1     | 1      | 0 | 1 |

| 3         |                 | Χ     | 0    | 0       | 1   | 1  |                 | 1 | 1 | 1     | 1     | 0      | 0 | 1 |

| 4         |                 | Χ     | 0    | 1       | 0   | 0  | 4               | 0 | 1 | 1     | 0     | 0      | 1 | 1 |

| 5         |                 | Χ     | 0    | 1       | 0   | 1  |                 | 1 | 0 | 1     | 1     | 0      | 1 | 1 |

| 6         |                 | Χ     | 0    | 1       | 1   | 0  |                 | 1 | 0 | 1     | 1     | 1      | 1 | 1 |

| 7         |                 | Χ     | 0    | 1       | 1   | 1  |                 | 1 | 1 | 1     | 0     | 0      | 0 | 0 |

| 8         |                 | Χ     | 1    | 0       | 0   | 0  |                 | 1 | 1 | 1     | 1     | 1      | 1 | 1 |

| 9         |                 | X     | 1    | 0       | 0   | 1  |                 | 1 | 1 | 1     | 1     | 0      | 1 | 1 |

| A         |                 | X     | 1    | 0       | 1   | 0  |                 | 1 | 1 | 1     | 0     | 1      | 1 | 1 |

| b         |                 | X     | 1    | 0       | 1   | 1  |                 | 0 | 0 | 1     | 1     | 1      | 1 | 1 |

| С         |                 | Χ     | 1    | 1       | 0   | 0  |                 | 1 | 0 | 0     | 1     | 1      | 1 | 0 |

| d         |                 | Χ     | 1    | 1       | 0   | 1  |                 | 0 | 1 | 1     | 1     | 1      | 0 | 1 |

| E         |                 | Χ     | 1    | 1       | 1   | 0  |                 | 1 | 0 | 0     | 1     | 1      | 1 | 1 |

| F         |                 | Χ     | 1    | 1       | 1   | 1  |                 | 1 | 0 | 0     | 0     | 1      | 1 | 1 |

$<sup>^{\</sup>dagger}$  The decimal point is enabled by setting bit D7 = 1.

Table 12. No-Decode Mode Data Bits and Corresponding Segment Lines

|                            | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|----------------------------|----|----|----|----|----|----|----|----|

| Corresponding Segment Line | DP | Α  | В  | С  | D  | Е  | F  | G  |

#### **Display-Test Register (0xXF)**

The AS1108 can operate in two modes: normal mode and display test mode. In display test mode all LEDs are switched on at maximum brightness (duty cycle is 15/16). The device remains in display-test mode until the Display-Test Register is set for normal operation.

Note: All settings of the Digit- and Control-Registers are maintained.

Table 13. Display-Test Register Format (Address (HEX) = 0xXF))

| Mode              | Register Data |    |    |    |    |    |    |    |

|-------------------|---------------|----|----|----|----|----|----|----|

| Wiode             | D7            | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| Normal Operation  | Х             | Х  | Х  | Х  | Х  | Х  | Х  | 0  |

| Display Test Mode | Х             | Х  | Χ  | Х  | Х  | Х  | Χ  | 1  |

#### Intensity Control Register (0xXA)

The brightness of the display can be controlled by digital means using the Intensity Control Register and by analog means using RSET (see Selecting RSET Resistor Value and Using External Drivers on page 14).

Display brightness is controlled by an integrated pulse-width modulator which is controlled by the lower-nibble of the Intensity Control Register. The modulator scales the average segment-current in 16 steps from a maximum of 31/32 down to 1/32 of the peak current set by RSET.

Table 14. Intensity Register Format (Address (HEX) = 0xXA))

| Duty Cycle     | HEX Code  |    |    |    | Regist | er Data |    |    |    |

|----------------|-----------|----|----|----|--------|---------|----|----|----|

| AS1108         | TILX COUE | D7 | D6 | D5 | D4     | D3      | D2 | D1 | D0 |

| 1/32 (min on)  | 0xX0      | Х  | Х  | Х  | Х      | 0       | 0  | 0  | 0  |

| 3/32           | 0xX1      | Х  | Х  | Х  | Х      | 0       | 0  | 0  | 1  |

| 5/32           | 0xX2      | Х  | Х  | Х  | Х      | 0       | 0  | 1  | 0  |

| 7/32           | 0xX3      | Х  | Х  | Х  | Х      | 0       | 0  | 1  | 1  |

| 9/32           | 0xX4      | Х  | Х  | Х  | Х      | 0       | 1  | 0  | 0  |

| 11/32          | 0xX5      | Х  | Х  | Х  | Х      | 0       | 1  | 0  | 1  |

| 13/32          | 0xX6      | Х  | Х  | Х  | Х      | 0       | 1  | 1  | 0  |

| 15/32          | 0xX7      | Х  | Х  | X  | Х      | 0       | 1  | 1  | 1  |

| 17/32          | 0xX8      | Х  | X  | X  | Х      | 1       | 0  | 0  | 0  |

| 19/32          | 0xX9      | Х  | Х  | X  | Х      | 1       | 0  | 0  | 1  |

| 21/32          | 0xXA      | Х  | X  | X  | X      | 1       | 0  | 1  | 0  |

| 23/32          | 0xXB      | Х  | X  | X  | X      | 1       | 0  | 1  | 1  |

| 25/32          | 0xXC      | Х  | X  | Х  | X      | 1       | 1  | 0  | 0  |

| 27/32          | 0xXD      | X  | X  | Х  | X      | 1       | 1  | 0  | 1  |

| 29/32          | 0xXE      | X  | X  | Х  | X      | 1       | 1  | 1  | 0  |

| 31/32 (max on) | 0xXF      | X  | Х  | X  | X      | 1       | 1  | 1  | 1  |

#### Scan-Limit Register (0x0B)

The Scan-Limit Register controls which of the digits are to be displayed. When all 4 digits are to be displayed, the update frequency is typically 1600Hz. If the number of digits displayed is reduced, the update frequency is increased. The frequency can be calculated using 8fOSC/N, where N is the number of digits. Since the number of displayed digits influences the brightness, RSET should be adjusted accordingly. Table 16 lists the maximum allowed current when fewer than 4 digits are used.

Note: To avoid differences in brightness this register should not be used to blank parts of the display (leading zeros).

Table 15. Scan-Limit Register Format (Address (HEX) = 0xXB))

| Scan Limit                          | HEX Code | Register Data |    |    |    |    |    |    |    |

|-------------------------------------|----------|---------------|----|----|----|----|----|----|----|

| Scar Limit                          | HEX Code | D7            | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| Display digit 0 only (see Table 16) | 0xX0     | Х             | Х  | Х  | Х  | Х  | 0  | 0  | 0  |

| Display digits 0:1 (see Table 16)   | 0xX1     | Х             | Х  | Х  | Х  | X  | 0  | 0  | 1  |

| Display digits 0:2 (see Table 16)   | 0xX2     | Х             | Х  | Х  | Х  | X  | 0  | 1  | 0  |

| Display digits 0:3                  | 0xX3     | Х             | Х  | Х  | Х  | Х  | 0  | 1  | 1  |

Table 16. Maximum Segment Current for 1-, 2-, or 3-Digit Displays

| Number of Digits Displayed | Maximum Segment Current (mA) |

|----------------------------|------------------------------|

| 1                          | 10                           |

| 2                          | 20                           |

| 3                          | 30                           |

#### Feature Register (0xXE)

The Feature Register is used for switching the device into external clock mode, applying an external reset, selecting code-B or HEX decoding, enabling or disabling blinking, enabling or disabling the SPI-compatible interface, setting the blinking rate, and resetting the blink timing.

**Note:** At power-up the Feature Register is initialized to 0.

Table 17. Feature Register Summary

| D7              | D6   | D5                 | D4       | D3     | D2         | D1      | D0     |

|-----------------|------|--------------------|----------|--------|------------|---------|--------|

| blink_<br>start | sync | blink_<br>freq_sel | blink_en | spi_en | decode_sel | reg_res | clk_en |

Table 18. Feature Register Bit Descriptions (Address (HEX) = 0xXE))

|     | Addr: 0xXE     | Feature R |             |                                                                                                                                                                                                                                                                  |

|-----|----------------|-----------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| •   | Addi. UXXL     | Enables a | nd disables | various device features.                                                                                                                                                                                                                                         |

| Bit | Bit Name       | Default   | Access      | Bit Description                                                                                                                                                                                                                                                  |

| D0  | clk_en         | 0         | R/W         | External clock select.  0 = Internal oscillator is used for system clock.  1 = Pin CLK of the serial interface operates as system clock input.                                                                                                                   |

| D1  | reg_res        | 0         | R/W         | Resets all control registers except the Feature Register.  0 = Reset Disabled. Normal operation.  1 = All control registers are reset to default state (except the Feature Register) identically after power-up.  Note: The Digit Registers maintain their data. |

| D2  | decode_sel     | 0         | R/W         | Selects display decoding.  0 = Enable Code-B decoding (see Table 10 on page 10).  1 = Enable HEX decoding (see Table 11 on page 11).                                                                                                                             |

| D3  | spi_en         | 0         | R/W         | Enables the SPI-compatible interface.  0 = Disable SPI-compatible interface.  1 = Enable the SPI-compatible interface.                                                                                                                                           |

| D4  | blink_en       | 0         | R/W         | Enables blinking.  0 = Disable blinking.  1 = Enable blinking.                                                                                                                                                                                                   |

| D5  | blink_freq_sel | 0         | R/W         | Sets blink with low frequency (with the internal oscillator enabled):  0 = Blink period typically is 1 second (0.5s on, 0.5s off).  1 = Blink period is 2 seconds (1s on, 1s off).                                                                               |

| D6  | sync           | 0         | R/W         | Synchronizes blinking on the rising edge of pin LOAD/CSN. The multiplex and blink timing counter is cleared on the rising edge of pin LOAD/CSN. By setting this bit in multiple AS1108 devices, the blink timing can be synchronized across all the devices.     |

| D7  | blink_start    | 0         | R/W         | Start Blinking with display enabled phase. When bit D4 (blink_en) is set, bit D7 determines how blinking starts.  0 = Blinking starts with the display turned off.  1 = Blinking starts with the display turned on.                                              |

### No-Op Register (0xX0)

The No-Op Register is used when multiple AS1108 devices are cascaded in order to support displays with more than 4 digits. The cascading must be done in such a way that all DOUT pins are connected to DIN of the next AS1108 (see Figure 12 on page 16). The LOAD/CSN and CLK signals are connected to all devices.

For example, if five devices are cascaded, in order to perform a write operation to the fifth device, the write-command must be followed by four no-operation commands. When the LOAD/CSN signal goes high, all shift registers are latched. The first four devices will receive no-operation commands and only the fifth device will receive the intended operation command, and subsequently update its register.

# 9 Typical Application

### **Supply Bypassing and Wiring**

In order to achieve optimal performance the AS1108 should be placed very close to the LED display to minimize effects of electromagnetic interference and wiring inductance.

Furthermore, a 10µF electrolytic and a 0.1µF ceramic capacitor should be connected between pins VDD and GND to avoid power supply ripple (see Figure 12 on page 16).

Note: Both GND pins must be connected to ground.

#### Selecting RSET Resistor Value and Using External Drivers

Brightness of the display segments is controlled via RSET. The current that flows between VDD and ISET defines the current that flows through the LEDs.

Segment current is about 200 times the current in ISET. Typical values for RSET for different segment currents, operating voltages, and LED voltage drop (VLED) are given in Tables 19 - 23. The maximum current the AS1108 can drive is 40mA. If higher currents are needed, external drivers must be used, in which case it is no longer necessary that the device drive high currents.

In cases where the device drives only a few digits, Table 16 specifies the maximum currents, and RSET must be set accordingly.

**Note:** The display brightness can also be logically controlled (see Selecting RSET Resistor Value and Using External Drivers on page 14).

Table 19. RSET vs. Segment Current and LED Forward Voltage, VDD = 2.7V

| ISEG (mA)   | VLE    | D(V)   |

|-------------|--------|--------|

| ISEG (IIIA) | 1.5    | 2.0    |

| 40          | 5kΩ    | 4.4kΩ  |

| 30          | 6.9kΩ  | 5.9kΩ  |

| 20          | 10.7kΩ | 9.6kΩ  |

| 10          | 22.2kΩ | 20.7kΩ |

Table 20. RSET vs. Segment Current and LED Forward Voltage, VDD = 3.3V

| ISEG (mA)   |        | VLED(V)          |        |

|-------------|--------|------------------|--------|

| ISLG (IIIA) | 1.5    | 2.0              | 2.5    |

| 40          | 6.7kΩ  | $6.4$ k $\Omega$ | 5.7kΩ  |

| 30          | 9.1kΩ  | 8.8kΩ            | 8.1kΩ  |

| 20          | 13.9kΩ | 13.3kΩ           | 12.6kΩ |

| 10          | 28.8kΩ | 27.7kΩ           | 26kΩ   |

Table 21. RSET vs. Segment Current and LED Forward Voltage, VDD = 3.6V

| ISEG (mA)   | VLED(V)          |       |        |        |  |  |  |

|-------------|------------------|-------|--------|--------|--|--|--|

| ISEG (IIIA) | 1.5              | 2.0   | 2.5    | 3.0    |  |  |  |

| 40          | $7.5$ k $\Omega$ | 7.2kΩ | 6.6kΩ  | 5.5kΩ  |  |  |  |

| 30          | 10.18kΩ          | 9.8kΩ | 9.2kΩ  | 7.5kΩ  |  |  |  |

| 20          | 15.6kΩ           | 15kΩ  | 14.3kΩ | 13kΩ   |  |  |  |

| 10          | 31.9kΩ           | 31kΩ  | 29.5kΩ | 27.3kΩ |  |  |  |

Table 22. RSET vs. Segment Current and LED Forward Voltage, VDD = 4.0V

| ISEG (mA)   | VLED(V) |        |        |       |       |  |  |

|-------------|---------|--------|--------|-------|-------|--|--|

| ISLG (IIIA) | 1.5     | 2.0    | 2.5    | 3.0   | 3.5   |  |  |

| 40          | 8.6kΩ   | 8.3kΩ  | 7.9kΩ  | 7.6kΩ | 5.2kΩ |  |  |

| 30          | 11.6kΩ  | 11.2kΩ | 10.8kΩ | 9.9kΩ | 7.8kΩ |  |  |

Table 22. RSET vs. Segment Current and LED Forward Voltage, VDD = 4.0V (Continued)

| ISEG (mA)   |         |        | VLED(V) |        |        |

|-------------|---------|--------|---------|--------|--------|

| ISLG (IIIA) | 1.5     | 2.0    | 2.5     | 3.0    | 3.5    |

| 20          | 17.7kΩ  | 17.3kΩ | 16.6kΩ  | 15.6kΩ | 13.6kΩ |

| 10          | 36.89kΩ | 35.7kΩ | 34.5kΩ  | 32.5kΩ | 29.1kΩ |

Table 23. RSET vs. Segment Current and LED Forward Voltage, VDD = 5.0V

| ISEG (mA) | VLED (V) |         |         |         |        |        |  |

|-----------|----------|---------|---------|---------|--------|--------|--|

|           | 1.5      | 2.0     | 2.5     | 3.0     | 3.5    | 4.0    |  |

| 40        | 11.35kΩ  | 11.12kΩ | 10.84kΩ | 10.49kΩ | 10.2kΩ | 9.9kΩ  |  |

| 30        | 15.4kΩ   | 15.1kΩ  | 14.7kΩ  | 14.4kΩ  | 13.6kΩ | 13.1kΩ |  |

| 20        | 23.6kΩ   | 23.1kΩ  | 22.6kΩ  | 22kΩ    | 21.1kΩ | 20.2kΩ |  |

| 10        | 48.9kΩ   | 47.8kΩ  | 46.9kΩ  | 45.4kΩ  | 43.8kΩ | 42kΩ   |  |

Table 24. Package Thermal Data

| Package      | Thermal Resistance (ΘJA) |  |  |

|--------------|--------------------------|--|--|

| 20 Wide SOIC | +85℃/W                   |  |  |

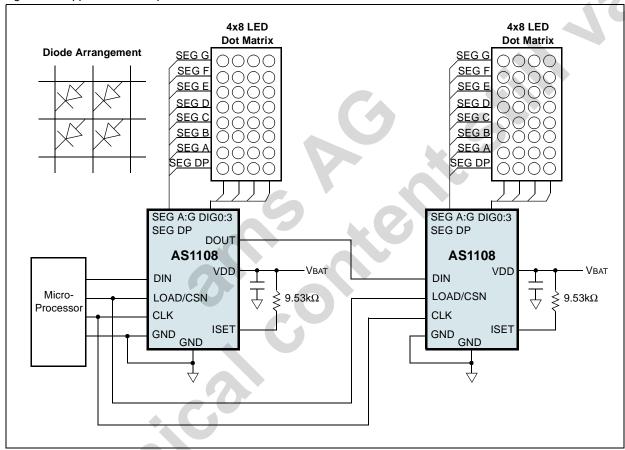

#### 4x8 LED Dot Matrix Driver

The application example in Figure 12 shows the AS1108 as a 4x8 LED dot matrix driver.

The LED columns have common cathodes and are connected to the DIG0:3 outputs. The rows are connected to the segment drivers. Each of the 32 LEDs can be addressed separately. The columns are selected via the digits as listed in Table 7 on page 9.

The Decode Enable Register (see page 10) must be set to '00000000' as described in Table 9 on page 10. Single LEDs in a column can be addressed as described in Table 12 on page 11, where bit D0 corresponds to segment G and bit D7 corresponds to segment DP.

Note: For a multiple-digit dot matrix, multiple AS1108 devices must be cascaded.

Figure 12. Application Example as LED Dot Matrix Driver

### **Cascading Drivers**

If more than 4 digits or 32 LEDs are needed, it is recommended to use the AS1106/AS1107, although several AS1108 devices can be cascaded.

The example in Figure 4 drives 2 dot matrix digits using a 4-wire microprocessor interface. All Scan-Limit Registers should be set to the same value so that one display will not appear brighter than the other.

For example, to display 6 digits, set both Scan-Limit Registers to display 3 digits so that both displays have a 1/3 duty cycle per digit. If 5 digits are needed, set both Scan-Limit Registers to display 3 digits and leave one digit unconnected. Otherwise, if one driver is set to display 3 digits and the other to display 2 digits one display will appear brighter because its duty cycle per digit will be 1/2 and the other display's duty cycle will be 1/3.

**Note:** Refer to No-Op Register (0xX0) on page 13 for additional information.

# 10 Package Drawings and Markings

Figure 13. SOIC 20-pin Marking

Table 25. Packaging Code YYWWRZZ

| YY                                  | WW                 | Q                | ZZ                              |

|-------------------------------------|--------------------|------------------|---------------------------------|

| last two digits of the current year | manufacturing week | plant identifier | free choice / traceability code |

Figure 14. SOIC 20-pin Package

MKR

2010.12.20

IMENSION AND TOLERANCE

NOT IN SCALE

# 11 Ordering Information

The AS1108 is available as the standard products shown in Table 26.

Table 26. Ordering Information

| Ordering Code | Marking  | Description                | Temperature Range | Delivery Form | Package     |

|---------------|----------|----------------------------|-------------------|---------------|-------------|

| AS1108WL      | AS1108WL | 4-Digit LED Display Driver | 0 to +70°C        | Tubes         | SOIC 20-pin |

| AS1108WL-T    | AS1108WL | 4-Digit LED Display Driver | 0 to +70°C        | Tape and Reel | SOIC 20-pin |

**Note:** All products are RoHS compliant and austriamicrosystems green.

Buy our products or get free samples online at ICdirect: http://www.austriamicrosystems.com/ICdirect

Technical Support is found at http://www.austriamicrosystems.com/Technical-Support

For further information and requests, please contact us mailto:sales@austriamicrosystems.com or find your local distributor at http://www.austriamicrosystems.com/distributor

### Copyrights

Copyright © 1997-2012, austriamicrosystems AG, Tobelbaderstrasse 30, 8141 Unterpremstaetten, Austria-Europe. Trademarks Registered ®. All rights reserved. The material herein may not be reproduced, adapted, merged, translated, stored, or used without the prior written consent of the copyright owner.

All products and companies mentioned are trademarks or registered trademarks of their respective companies.

#### **Disclaimer**

Devices sold by austriamicrosystems AG are covered by the warranty and patent indemnification provisions appearing in its Term of Sale. austriamicrosystems AG makes no warranty, express, statutory, implied, or by description regarding the information set forth herein or regarding the freedom of the described devices from patent infringement. austriamicrosystems AG reserves the right to change specifications and prices at any time and without notice. Therefore, prior to designing this product into a system, it is necessary to check with austriamicrosystems AG for current information. This product is intended for use in normal commercial applications. Applications requiring extended temperature range, unusual environmental requirements, or high reliability applications, such as military, medical life-support or life-sustaining equipment are specifically not recommended without additional processing by austriamicrosystems AG for each application. For shipments of less than 100 parts the manufacturing flow might show deviations from the standard production flow, such as test flow or test location.

The information furnished here by austriamicrosystems AG is believed to be correct and accurate. However, austriamicrosystems AG shall not be liable to recipient or any third party for any damages, including but not limited to personal injury, property damage, loss of profits, loss of use, interruption of business or indirect, special, incidental or consequential damages, of any kind, in connection with or arising out of the furnishing, performance or use of the technical data herein. No obligation or liability to recipient or any third party shall arise or flow out of austriamicrosystems AG rendering of technical or other services.

#### **Contact Information**

Headquarters

austriamicrosystems AG Tobelbaderstrasse 30 A-8141 Unterpremstaetten, Austria

Tel: +43 (0) 3136 500 0 Fax: +43 (0) 3136 525 01

For Sales Offices, Distributors and Representatives, please visit:

http://www.austriamicrosystems.com/contact