# AS1228

8.5-28V Controller for Isolated and Non-Isolated DC-DC Power Conversion

# **GENERAL DESCRIPTION**

The Akros Silicon AS1228 Single Chip Controller provides DC-DC Power Conversion for isolated and non-isolated power conversion applications over a wide input voltage range of 8.5-28 VDC. The current-mode controller architecture provides fast loop response, high efficiency, and low no-load power configurable for flyback, forward or buck topology power designs.

## **Features**

- 8.5V to 28V Input Voltage

- High Efficiency Design Capable, 90% typical

- Low No-Load Power for Energy Star and EUP/CoC Compliant Designs

- Programmable PWM Frequency, 100-500 KHz

- o Programmable Soft Start

- o Over Temperature Protection

- Industrial Temperature Range, -40° to +85°C

- RoHS compliant 5x5 mm 20 lead QFN and Chip Scale Packaging (contact Akros for CSP details)

## **Typical Applications**

- Consumer 12V, 24V Input Power Conversion (WiFi Access Points, Ethernet Switches, Set Top Boxes, DVR, Printers)

- o Enterprise Router, Switch and Server Blades

- Isolated and Non-Isolated IBA Power Conversion

- Flyback, Forward and Buck Power Designs

## **Typical Non-Isolated High Side Buck Application**

# **TABLE OF CONTENTS**

| GENERAL DESCRIPTION                            | 1  |

|------------------------------------------------|----|

| TABLE OF CONTENTS                              | 2  |

| FIGURES                                        | 2  |

| TABLES                                         | 2  |

| PIN ASSIGNMENTS AND DESCRIPTIONS               | 3  |

| TEST SPECIFICATIONS                            | 4  |

| APPLICATION INFORMATION                        | 8  |

| PHYSICAL DIMENSIONS                            |    |

| CONTACT INFORMATION                            |    |

| IMPORTANT NOTICES                              |    |

| Legal Notice                                   | 11 |

| Reference Design Policy                        |    |

| Reference Design Policy<br>Life Support Policy |    |

| Substance Compliance                           |    |

# **FIGURES**

| Figure 1 - AS1228 Pin Assignments                           | 3    |

|-------------------------------------------------------------|------|

| Figure 2 - AS1228 Top-Level Block Diagram                   |      |

| Figure 3 - Typical VBIAS from VIN Design                    |      |

| Figure 4 - Typical Isolated Synchronous Flyback Application | 8    |

| Figure 5 - Typical Non-Isolated High Side Buck Application  | 8    |

| Figure 6 - AS1228 PCB Footprint (top view)                  | 9    |

| Figure 7 – AS1228 Physical Dimensions                       | . 10 |

| 5                                                           | -    |

# **TABLES**

| Table 1 - AS1228 Pin Descriptions                     | 3 |

|-------------------------------------------------------|---|

| Table 2 - Absolute Maximum Ratings                    | 4 |

| Table 3 - Normal Operating Conditions                 | 4 |

| Table 4 - DC-DC Controller Electrical Characteristics |   |

| Table 5 - Thermal Characteristics                     |   |

| Table 6 - PWM Switching Frequency Selection           | 7 |

| Table 7 - Typical VBIAS External Component Values     |   |

|                                                       |   |

| Status:       | Preliminary Datasheet |

|---------------|-----------------------|

| Revision:     | Version 0.25          |

| Release Date: | September 27, 2010    |

*Advance Datasheet*: Document contains design specifications for initial product development.

*Preliminary Datasheet*: Document contains preliminary data and will be revised at a later date.

*Final Datasheet*: Document contains specifications on a product that is in final release.

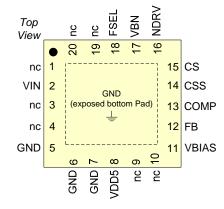

# PIN ASSIGNMENTS AND DESCRIPTIONS

## Figure 1 - AS1228 Pin Assignments

## Table 1 - AS1228 Pin Descriptions

| Pin                                                                | <b>I/O</b> <sup>1</sup> | Name  | Description                                                                     |  |  |  |

|--------------------------------------------------------------------|-------------------------|-------|---------------------------------------------------------------------------------|--|--|--|

| 2                                                                  | Р                       | VIN   | Voltage input.                                                                  |  |  |  |

| 5                                                                  | А                       | GND   | Must be connected to exposed bottom side pad ground (GND).                      |  |  |  |

| 6                                                                  | А                       | GND   | Must be connected to exposed bottom side pad ground (GND).                      |  |  |  |

| 7                                                                  | А                       | GND   | Must be connected to exposed bottom side pad ground (GND).                      |  |  |  |

| 8                                                                  | 0                       | VDD5  | Internal 5 volts bus decoupling point.                                          |  |  |  |

| 11                                                                 | А                       | VBIAS | Voltage bias input.                                                             |  |  |  |

| 12                                                                 | А                       | FB    | DC-DC Controller feedback point.                                                |  |  |  |

| 13                                                                 | А                       | COMP  | DC-DC Controller error amplifier compensation network connection.               |  |  |  |

| 14                                                                 | А                       | CSS   | DC-DC Controller soft-start capacitor connection point.                         |  |  |  |

| 15                                                                 | А                       | CS 🔷  | DC-DC Controller peak-current sense input (low side).                           |  |  |  |

| 16                                                                 | 0                       | NDRV  | DC-DC Controller N-MOSFET gate drive.                                           |  |  |  |

| 17                                                                 | 0                       | VBN   | DC-DC Controller low-side supply decoupling.                                    |  |  |  |

| 18                                                                 | Ι                       | FSEL  | Frequency Select. This pin sets the switching frequency of the DC-DC converter. |  |  |  |

| Pad                                                                | Ρ                       | GND   | Device ground connection (exposed bottom side Pad).                             |  |  |  |

| 1, 3, 4, 9,<br>10, 19, 20                                          | -                       | nc    | No connection. Must be left floating.                                           |  |  |  |

| <sup>1</sup> Key: I = Input O = Output A = Analog signal P = Power |                         |       |                                                                                 |  |  |  |

# **TEST SPECIFICATIONS**

Unless otherwise noted Test Specifications apply over the full -40°C to 85°C operating temperature range.

#### Table 2 - Absolute Maximum Ratings

| Description                                                       | Max Value <sup>1</sup> | Units |

|-------------------------------------------------------------------|------------------------|-------|

| High-voltage pin (VIN)<br>Under Transient conditions <sup>4</sup> | 100                    | Volts |

| High-voltage pin (VIN)<br>Steady-state with internal Surge Clamp  | 60                     | Volts |

| VDD5; VBIAS; FB; COMP; CSS; CS; NDRV;<br>VBN; FSEL                | 6                      | Volts |

| ESD Ratings                                                       |                        |       |

| Human body model <sup>2</sup>                                     | 2                      | KV    |

| ESD charged device model                                          | 500                    | V     |

| ESD machine model                                                 | 200                    | V     |

| System level (contact/air) at RJ-45 <sup>3</sup>                  | 8/15                   | KV    |

| Temperature                                                       |                        |       |

| Storage temperature                                               | 165                    | °C    |

| Junction temperature                                              | 150                    | °C    |

<sup>1</sup> Absolute maximum ratings are limits beyond which damage to the device may occur.

<sup>2</sup> The human body model is as described in JESD22-A114.

<sup>3</sup> System ESD testing done per IEC61000-4-2.

<sup>4</sup> Transient conditions like system startup and other noise conditions. Device must not be exposed to sustained over-voltage condition at this level.

#### Table 3 - Normal Operating Conditions

| Description                 | Min  | Typical <sup>1</sup> | Мах | Unit | Conditions |

|-----------------------------|------|----------------------|-----|------|------------|

| VIN                         | 8.5V |                      | 28V |      |            |

| Operating temperature range | -40  |                      | +85 | °C   |            |

<sup>1</sup> Typical specification; not 100% tested. Performance guaranteed by design and/or other correlation methods.

#### Table 4 - DC-DC Controller Electrical Characteristics

| Description                     | Min | Typical <sup>1</sup> | Max | Units | Conditions                                       |

|---------------------------------|-----|----------------------|-----|-------|--------------------------------------------------|

| Operating current (at VIN)      |     |                      | TBD | mA    | VIN = TBD, FOSC = TBD                            |

| FOSC                            | 80  | 100                  | 120 |       | Rosc=178kΩ                                       |

| (DC-DC switching                | 200 | 225                  | 250 | KHz   | Rosc=100kΩ                                       |

| frequency)                      | 315 | 350                  | 385 |       | Rosc=53.6kΩ                                      |

| frequency)                      | 450 | 500                  | 550 |       | Rosc=36.8kΩ                                      |

| FOSC temperature<br>coefficient |     | 0.12                 |     | %/C   |                                                  |

| NDRV ROUT                       |     | 1.2                  | 3   | Ω     | Output drive resistance                          |

| NDRV voltage                    |     | 4.7                  |     |       | NDRV voltage follows VBN<br>power supply voltage |

| Description                                        | Min  | Typical <sup>1</sup> | Max  | Units    | Conditions                                 |

|----------------------------------------------------|------|----------------------|------|----------|--------------------------------------------|

| Gate drive dynamic<br>response<br>NDRV TR, TF      |      | 2.2<br>2             |      | ns<br>ns | 10% - 90% with CLOAD = 1 nF                |

| Max. NDRV duty cycle                               |      | 80                   |      | %        | Measured at 350KHz                         |

| Min. NDRV duty cycle                               |      | 6                    | 10   | %        | Measured at 350KHz                         |

| VBN                                                |      | 4.7                  |      | V        | Internal supply voltage; sets VOH of NDRV. |

| Error amplifier reference voltage                  | 1.45 | 1.5                  | 1.55 | V        | Compared to input of the FB pin            |

| VPK, peak current sense<br>threshold voltage at CS | 500  | 600                  | 700  | mV       | IPEAK=VPK/RSENSE                           |

| Soft start ramp time                               |      | 2                    |      | ms       | Conditions: CSS=100nF                      |

| COMP source current                                |      | 80                   |      | μA       | FB = 0V, COMP = 0V                         |

| COMP sink current                                  |      | 80                   |      | μA       | FB = 5V, COMP = 5V                         |

| Open loop voltage gain<br>(Error amplifier)        |      | 80                   |      | dB       |                                            |

| Small signal unity-gain<br>bandwidth               |      | 5                    |      | MHz      | COMP connected to FB.                      |

| FB leakage (source or sink)                        |      | 1                    |      | μA       |                                            |

| VBIAS pin voltage                                  | 5.4  | 5.6                  | 5.8  | V        |                                            |

| VBIAS current                                      |      | 75                   |      | μA       | VBIAS voltage = 5.6V                       |

$^1$  Typical specifications are not 100% tested. Performance guaranteed by design and/or other correlation methods.

## Table 5 - Thermal Characteristics

| Description                                            | Min | Typical <sup>1</sup> | Мах | Units | Conditions                                                                         |

|--------------------------------------------------------|-----|----------------------|-----|-------|------------------------------------------------------------------------------------|

| Thermal shutdown temperature                           |     | 165                  |     | °C    | Above this Temp., the AS1228 is disabled.                                          |

| Thermal shutdown hysteresis                            | 5   | 40                   |     | °C    | Temperature change required<br>to restore full operation after<br>thermal shutdown |

| Max. on-die operating<br>temperature                   |     |                      | 140 | °C    | Maximum recommended<br>operating temperature for<br>normal operation               |

| Thermal Resistance, Junction to Ambient, $\theta_{JA}$ |     | 31                   |     | °C/W  | 20 lead QFN package                                                                |

| Thermal Resistance, Junction to Case, $\theta_{JC}$    |     | 3.4                  |     | °C/W  | 20 lead QFN package                                                                |

<sup>1</sup> Typical specifications are not 100% tested. Performance guaranteed by design and/or other correlation methods.

# FUNCTIONAL DESCRIPTION

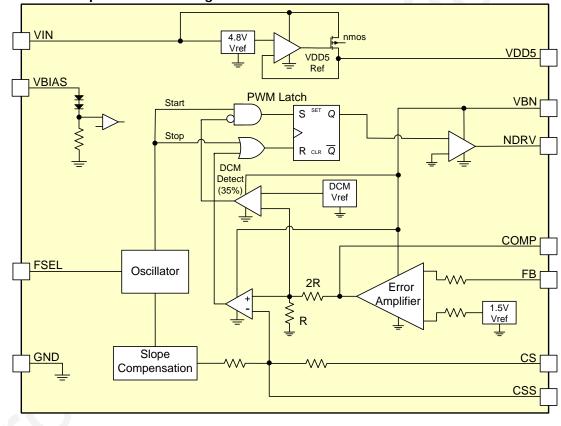

## AS1228 Overview

The AS1228 DC-DC architecture is that of a current-mode controller, configurable with external components to fly-back, forward or buck topologies. Both non-isolated and isolated application topologies are supported.

The integrated DC-DC controller includes programmable soft start. Once input power is applied within the device VIN range, the DC-DC controller starts up. The controller provides a gate control signal, NDRV, for an external switching MOSFET and uses an external resistor to sense primary current in the transformer. It also provides an 80% duty cycle (max) programmable PWM switching frequency and a true voltage-output error amplifier.

As part of a full system level solution to control EMI, the device reduces switching noise by shaping the FET driver waveforms. Ground bounce is also reduced by minimizing dV/dt switching noise.

#### Figure 2 - AS1228 Top-Level Block Diagram

#### **Programmable PWM Frequency**

The FSEL pin allows the DC-DC converter switching frequency to be set externally. Placing a resistor between FSEL and GND sets the internal oscillator's frequency. Table 6 identifies resistor values for some commonly used switching frequencies.

| Table 0 - I will Switching Frequency Selection | Table 6 - PWM Switching Freque | ncy Selection |

|------------------------------------------------|--------------------------------|---------------|

|------------------------------------------------|--------------------------------|---------------|

| Switching Frequency<br>(KHz) | FSEL Resistor<br>(KΩ, 1%) |

|------------------------------|---------------------------|

| 100                          | 178                       |

| 225                          | 100                       |

| 350                          | 53.6                      |

| 500                          | 36.8                      |

#### **Current-Limit/Current Sense**

The DC/DC controller provides cycle-by-cycle current limiting, to ensure that transformer primary current limits are not exceeded. The maximum average current in the transformer primary is nominally set by internal duty-cycle limits.

#### **Low Load Current Operation**

If a low output power condition is detected the DC-DC Controller is put into a discontinuous current operation (DCM) mode.

#### **Compensation and Feedback**

For isolated applications, loop compensation and output voltage feedback is generally provided by an opto-isolator circuit, and the Feedback pin (FB) is tied to ground. In these applications, the COMP pin is pulled up to approximately 4.8V by an internal current source. This pull-up can be the termination for an opto-isolator, or, an additional resistor can be used in parallel.

For non-isolated applications, a resistive divider network, connected directly to the FB pin, senses the output voltage. The internal error amplifier is connected to a 1.5V reference voltage and the control loop will servo the FB pin to this voltage. A capacitive/resistive network connected to the COMP pin provides loop compensation.

#### Soft-Start Current Limit

Internal circuitry automatically ramps up the inrush current by limiting the maximum current allowed in the transformer primary magnetizing inductance per clock cycle. The amount of time required to perform a soft start cycle is determined by the CSS capacitor. A value of 330nF provides approximately 7ms of soft startup ramp time.

## **Thermal Limit / Protection**

The AS1228 provides internal thermal protection by monitoring die temperature and reducing maximum current or disconnecting power as needed to prevent pre-set thermal limits from being exceeded. Two-stage thermal current limiting is implemented, which reduces the operating current limit by 50% when the die temperature reaches 145°C, and disables the power MOSFET switch above 165°C. Normal current limits in both cases are re-applied when the die temperature returns below 125°C.

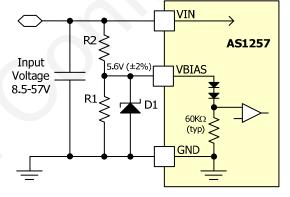

#### **Deriving VBIAS from VIN**

A VBIAS input (5.6V,  $\pm 2\%$ ) is required for device operation. Figure 3 shows a typical external component design using the VIN power source to create VBIAS.

#### Figure 3 - Typical VBIAS from VIN Design

An appropriate ratio of R1 and R2 resistors should be used to ensure proper operation across all supply voltages. Though single values of R1 and R2 can be used across the whole local supply voltage range of 8.5V to 28V, if the application has a narrower input voltage range then the resistor values can be adjusted to minimize power consumption. See Table 7 for some typical external component values.

# Table 7 - Typical VBIAS External ComponentValues

| Local Voltage<br>Range (V) | R2<br>(ΚΩ) | R1<br>(ΚΩ) |

|----------------------------|------------|------------|

| 8.5-28                     | 2.74       | 4.02       |

| 20-28                      | 11.3       | 4.02       |

| D1: 5.6V Zener (±2%, max)  |            |            |

# **APPLICATION INFORMATION**

For detailed applications documentation please refer to the separate Akros application note #TBD, the AS12xx Design and Layout Guide.

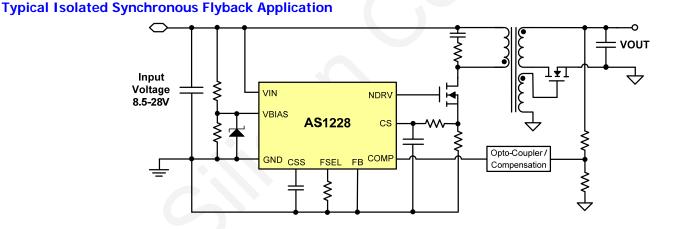

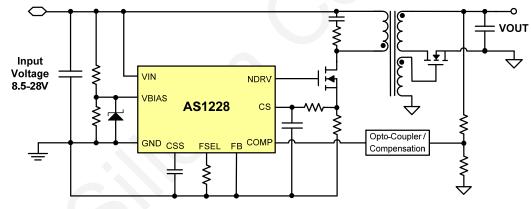

### **Isolated DC-DC Topologies**

The DC-DC controller can be configured in several different isolated power topologies.

Flyback topology is chosen when a minimum number of external components is desired, or, there is a large step-down and the output voltage is < 7V. The Forward mode is chosen when lower switching noise is desired.

Either of these isolated topologies can be designed for synchronous or non-synchronous operation based on system requirements. A typical highefficiency Isolated Synchronous Flyback design is shown in Figure 4.

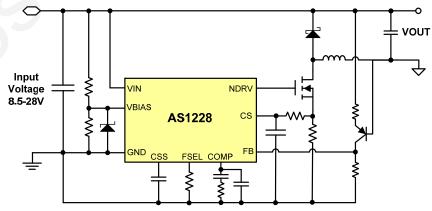

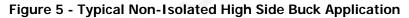

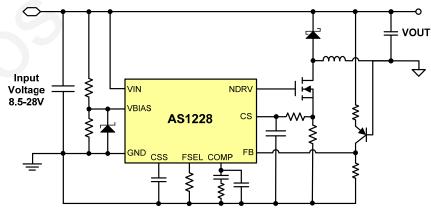

## **Non-Isolated Topologies**

A Buck topology is used in non-isolated applications, which uses an inductor for energy storage instead of a transformer.

Buck designs typically have the smallest overall board component footprint.

Figure 5 shows a typical non-synchronous high side Buck converter design. Since the FB voltage is input power ground referenced, the feedback signal must be level-shifted back down to the input power ground. This is accomplished by the PNP transistor and associated resistors.

## THERMAL DE-RATING AND BOARD LAYOUT CONSIDERATIONS

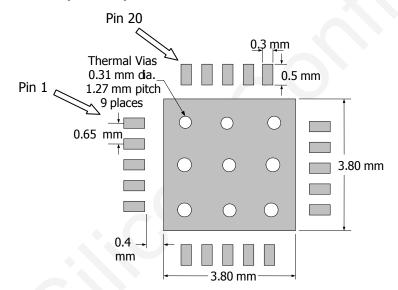

The AS1228 is capable of operation to 85 °C (ambient) without forced cooling. A thermal pad on the underside of the package dissipates generated heat.

If the PCB landing pattern is properly designed, the QFN package should exhibit a thermal resistance of  $\Theta_{JA}=31^{\circ}C/W$ . For adequate heat dissipation, the board layout must include a ground pad which provides both the ground connection and dissipates the heat energy produced in the chip. Thermal vias are used to draw heat away from the QFN package and transfer it to the backside of the system PCB.

The recommended PCB layout for the AS1228 is shown in Figure 6.

#### Figure 6 - AS1228 PCB Footprint (top view)

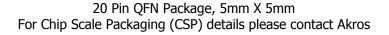

# **PHYSICAL DIMENSIONS**

#### Figure 7 – AS1228 Physical Dimensions

- 1. Controlling dimensions in mm.

- 2. Dimension tolerances are  $\pm 0.1$  (angular tolerance  $\pm 3^{\circ}$ ) unless otherwise specified.

- 3. All dimensions and tolerances conform to ANSI 14.5M-1994.

- 4. Co-planarity applies to exposed pad as well as the terminals.

- $\sqrt{5}$  Pin 1 location may be identified by either a mold or marked feature.

- 6. JEDEC reference MO-220.

# **CONTACT INFORMATION**

Akros Silicon, Inc. 275 Turn Pike Drive Folsom, CA. 95630 USA Tel: (916) 351-8100 Fax: (916) 351-8102 Email inquiries: <u>marcom@AkrosSilicon.com</u> Website: www.AkrosSilicon.com

## **IMPORTANT NOTICES**

#### LEGAL NOTICE

Copyright  $\bigcirc$  2010 Akros Silicon<sup>TM</sup>. All rights reserved. Other names, brands and trademarks are the property of others. Akros Silicon<sup>TM</sup> assumes no responsibility or liability for information contained in this document. Akros reserves the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or services without notice. The information contained herein is believed to be accurate and reliable at the time of printing.

#### **REFERENCE DESIGN POLICY**

This document is provided as a design reference and Akros Silicon assumes no responsibility or liability for the information contained in this document. Akros reserves the right to make corrections, modifications, enhancements, improvements and other changes to this reference design documentation without notice.

Reference designs are created using Akros Silicon's published specifications as well as the published specifications of other device manufacturers. This information may not be current at the time the reference design is built. Akros Silicon and/or its licensors do not warrant the accuracy or completeness of the specifications or any information contained therein.

Akros does not warrant that the designs are production worthy. Customer should completely validate and test the design implementation to confirm the system functionality for the end use application.

Akros Silicon provides its customers with limited product warranties, according to the standard Akros Silicon terms and conditions.

For the most current product information visit us at <u>www.AkrosSilicon.com</u>

#### LIFE SUPPORT POLICY

LIFE SUPPORT: AKROS' PRODUCTS ARE NOT DESIGNED, INTENDED, OR AUTHORIZED FOR USE AS COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS. NO WARRANTY, EXPRESS OR IMPLIED, IS MADE FOR THIS USE. AUTHORIZATION FOR SUCH USE SHALL NOT BE GIVEN BY AKROS, AND THE PRODUCTS SHALL NOT BE USED IN SUCH DEVICES OR SYSTEMS, EXCEPT UPON THE WRITTEN APPROVAL OF THE PRESIDENT OF AKROS FOLLOWING A DETERMINATION BY AKROS THAT SUCH USE IS FEASIBLE. SUCH APPROVAL MAY BE WITHHELD FOR ANY OR NO REASON.

"Life support devices or systems" are devices or systems which (1) are intended for surgical implant into the human body, (2) support or sustain human life, or (3) monitor critical bodily functions including, but not limited to, cardiac, respirator, and neurological functions, and whose failure to perform can be reasonably expected to result in a significant bodily injury to the user. A "critical component" is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### SUBSTANCE COMPLIANCE

With respect to any representation by Akros Silicon that its products are compliant with RoHS, Akros Silicon complies with the Restriction of the use of Hazardous Substances Standard ("RoHS"), which is more formally known as Directive 2002/95/EC of the European Parliament and of the Council of 27 January 2003 on the restriction of the use of certain hazardous substances in electrical and electronic equipment. To the best of our knowledge the information is true and correct as of the date of the original publication of the information. Akros Silicon bears no responsibility to update such statements.