# AS1312

Ultra Low Quiescent Current, Hysteretic DC-DC Step-up Converter

## **General Description**

The AS1312 is an ultra low IQ hysteretic step-up DC-DC converter.

The AS1312 achieves an efficiency of up to 94% and is designed to operate from a +0.7V to +5.0V supply, the output voltage is fixed in 50mV steps from +2.5V to 5.0V.

In order to save power the AS1312 features a shutdown mode, where it draws less than 100nA. In shutdown mode the battery is not connected to the output.

If the input voltage exceeds the output voltage the device is in a feedthrough mode and the input is directly connected to the output voltage.

In light load operation, the device enters a sleep mode when most of the internal operating blocks are turned off in order to save power. This mode is active approximately  $50\mu s$  after a current pulse provided that the output is in regulation.

The AS1312 also offers an adjustable low battery detection. If the battery voltage decreases below a threshold defined by two external resistors on pin LBI, the LBO output is pulled to logic low. LBO is working as Power-OK when LBI is connected to GND.

The AS1312 is available in a 8-pin (2x2) TDFN and a 0.4mm pitch 8-pin WL-CSP package.

Ordering Information and Content Guide appear at end of datasheet.

## **Key Benefits & Features**

The benefits and features of AS1312, Ultra Low Quiescent Current, Hysteretic DC-DC Step-up Converter are listed below:

Figure 1: Added Value of Using AS1312

| Benefits                                             | Features                                                                                                   |

|------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| Ideal for single Li-Ion battery powered applications | Wide Input Voltage Range (0.7V to 5.0V)<br>Feedthrough mode when V <sub>IN</sub> > V <sub>OUT</sub>        |

| Extended battery life                                | High Efficiency up to 94%                                                                                  |

| Less Power Consumption                               | Low Quiescent Current of typ. 1uA<br>Low Shutdown Current of less than 100nA                               |

| Supports a variety of end applications               | Fixed output voltage range (2.5V to 5.0V)<br>Peak Output Current of 200mA<br>Output Disconnect in shutdown |

| Benefits                                   | Features                                                |

|--------------------------------------------|---------------------------------------------------------|

| Over – temperature protection and shutdown | Integrated temperature monitoring                       |

| Early power-fail warning                   | Low battery detection                                   |

| Cost effective, small package              | 8-pin WL-CSP with 0.4mm pitch<br>8-pin TDFN (2mm x 2mm) |

# Applications

The AS1312 is an ideal solution for:

- Handheld devices

- Battery powered products

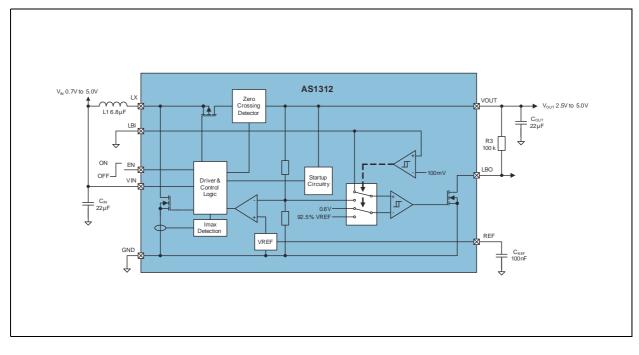

## **Block Diagram**

The functional blocks of this device for reference are shown below:

Figure 2: AS1312 Block Diagram

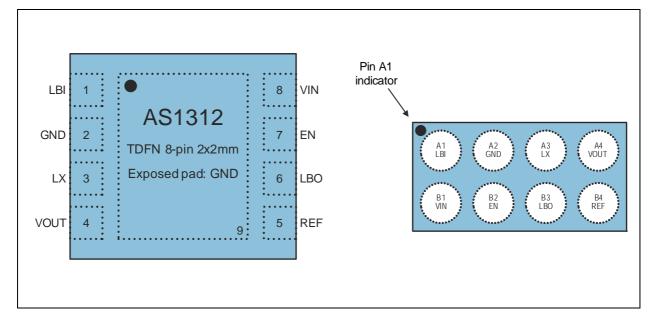

# Pin Assignments

Figure 3: Pinout (Top View)

#### Figure 4: Pin Description

| Pin Nu | mber | Pin Name | Description                                                                                                                                        |

|--------|------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| WL-CSP | TDFN | Fin Name | Description                                                                                                                                        |

| A1     | 1    | LBI      | <b>Low Battery Comparator Input</b> . 0.6V Threshold. May not be left floating. If connected to GND, LBO is working as Power Output OK.            |

| A2     | 2    | GND      | Ground                                                                                                                                             |

| A3     | 3    | LX       | External Inductor Connector.                                                                                                                       |

| A4     | 4    | VOUT     | <b>Output Voltage.</b> Decouple VOUT with a ceramic capacitor as close as possible to VOUT and <b>GND</b> .                                        |

| B4     | 5    | REF      | <b>Reference Pin.</b> Connect a 100nF ceramic capacitor to this pin.                                                                               |

| B3     | 6    | LBO      | Low Battery Comparator Output. Open-drain output.                                                                                                  |

| B2     | 7    | EN       | <b>Enable Pin</b> . Logic controlled shutdown input.<br>1 = Normal operation;<br>0 = Shutdown; shutdown current <100nA.                            |

| B1     | 8    | VIN      | <b>Battery Voltage Input.</b> Decouple VIN with a ceramic capacitor as close as possible to VIN and GND.                                           |

| -      | 9    | NC       | <b>Exposed Pad.</b> This pad is not connected internally. Can be left floating or connect to <b>GND</b> to achieve an optimal thermal performance. |

## Absolute Maximum Ratings

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in Electrical Characteristics is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### Figure 5: Absolute Maximum Ratings

| Parameter                      |                                               | Min        | Max  | Unit          | Comments |                                                                                                           |  |  |

|--------------------------------|-----------------------------------------------|------------|------|---------------|----------|-----------------------------------------------------------------------------------------------------------|--|--|

|                                |                                               |            |      | Electrical Pa | aramete  | rs                                                                                                        |  |  |

|                                | VIN, VOUT, EN, LBI,<br>GND                    | LBO to     | -0.3 | 7             | v        |                                                                                                           |  |  |

|                                | LX, REF to GND                                |            | -0.3 | Vout + 0.3    | V        |                                                                                                           |  |  |

|                                | Input Current<br>(latch-up immunit            | y)         | -100 | 100           | mA       | Norm: JEDEC 78                                                                                            |  |  |

|                                | Electrostatic Discharge                       |            |      |               |          |                                                                                                           |  |  |

|                                | Electrostatic Discharge HBM ±2                |            |      | ±2            | kV       | Norm: MIL 883 E method 3015                                                                               |  |  |

|                                | Temperature Ranges and Storage Conditions     |            |      |               |          |                                                                                                           |  |  |

| θ <sub>JA</sub> <sup>(1)</sup> | Thermal                                       | WL-CSP     |      | 97<br>60      |          |                                                                                                           |  |  |

| OJA                            | Resistance                                    | TDFN       |      |               |          |                                                                                                           |  |  |

| T <sub>AMB</sub>               | Operating Temper                              | ature      | -40  | 85            | °C       |                                                                                                           |  |  |

| T,                             | Junction                                      | WL-CSP     |      | 125           | ∘⊂       |                                                                                                           |  |  |

| ('<br>                         | Temperature                                   | TDFN       |      | 150           | ∘⊂       |                                                                                                           |  |  |

|                                | Storage Temperatu                             | Iro Pango  | -55  | 150           | °C       | for 8-pin (2x2) TDFN                                                                                      |  |  |

|                                | Storage remperato                             | ire nalige | -55  | 125           | °C       | for 8-pin WL-CSP                                                                                          |  |  |

|                                |                                               | WL-CSP     |      |               |          | Norm IPC/JEDEC J-STD-020 <sup>(2)</sup>                                                                   |  |  |

| T <sub>BODY</sub>              | T <sub>BODY</sub> Package Body<br>Temperature | TDFN       |      | 260           | °C       | Norm IPC/JEDEC J-STD-020 <sup>(2)</sup><br>The lead for Pb-free leaded packages is<br>matte tin (100% Sn) |  |  |

|                                | Humidity non-con                              | densing    | 5    | 85            | %        |                                                                                                           |  |  |

| Parameter         |        | Min | Мах | Unit | Comments                                |

|-------------------|--------|-----|-----|------|-----------------------------------------|

| Moisture          | WL-CSP | 1   |     |      | Represents an unlimited floor life time |

| Sensitivity Level | TDFN   |     | •   |      | Represents an unlimited floor life time |

#### Note(s) and/or Footnote(s):

1. Junction-to-ambient thermal resistance is very dependent on application and board-layout. In situations where high maximum power dissipation exists, special attention must be paid to thermal dissipation during board design.

2. The reflow peak soldering temperature (body temperature) is specified according IPC/JEDEC J-STD-020 "Moisture/Reflow Sensitivity Classification for Nonhermetic Solid State Surface Mount Devices"

## **Electrical Characteristics**

All limits are guaranteed. The parameters with Min and Max values are guaranteed by production tests or SQC (Statistical Quality Control) methods.

VIN = 1.5V,  $C1 = C2 = 22\mu F$ , CREF = 100nF, Typical values are at TAMB = 25°C. Unless otherwise specified. All limits are guaranteed. The parameters with min and max values are guaranteed with production tests or SQC (Statistical Quality Control) methods.

Figure 6: Electrical Characteristics

| Symbol | Parameter                             | Conditions                                                                    | Min | Тур  | Max | Unit |

|--------|---------------------------------------|-------------------------------------------------------------------------------|-----|------|-----|------|

|        |                                       | Input                                                                         |     |      |     |      |

| Vin    | Input Voltage Range                   |                                                                               | 0.7 |      | 5.0 | V    |

|        | Minimum Startup Voltage               | TAMB = 25°C                                                                   |     | 0.9  |     | V    |

|        |                                       | Regulation                                                                    |     |      |     |      |

| Vout   | Output Voltage Range                  |                                                                               | 2.5 |      | 5.0 | V    |

|        |                                       | ILOAD = 0mA to 10mA,<br>TAMB = 25°C                                           | -2  |      | 2   | %    |

|        | Output Voltage Tolerance              | ILOAD = 0mA to 10mA                                                           | -4  |      | 4   | %    |

|        |                                       | $ILOAD = 0mA \text{ to } 30mA,$ $TAMB = -20^{\circ}C \text{ to } 60^{\circ}C$ | -2  |      | 2   | %    |

|        | Vout Lockout Threshold <sup>(1)</sup> | Rising Edge                                                                   |     | 2.45 |     | V    |

|        |                                       | Operating Current                                                             |     |      |     |      |

| IQ     | Quiescent Current VIN                 | Vout = $1.02x$ Voutnom,<br>REF = $0.99x$ Voutnom,<br>Tamb = $25^{\circ}$ C    |     |      | 100 | nA   |

|        | Quiescent Current Vout                | VOUT = 5V, No load,<br>TAMB = 25°C                                            | 0.7 | 1    | 1.3 | μΑ   |

| Iqshdn | Shutdown Current                      | Тамв = 25°C                                                                   |     |      | 100 | nA   |

| Symbol           | Parameter                                                | Conditions                                                    | Min  | Тур  | Max  | Unit |

|------------------|----------------------------------------------------------|---------------------------------------------------------------|------|------|------|------|

|                  | I                                                        | Switches                                                      |      |      |      |      |

| Ron              | NMOS                                                     | Vout = 5V                                                     |      | 0.4  |      | Ω    |

| NON              | PMOS                                                     |                                                               |      | 0.45 |      | Ω    |

|                  | NMOS maximum on-time                                     |                                                               | 3.3  | 4.0  | 4.6  | μs   |

| IPEAK            | Peak current limit                                       |                                                               |      | 400  |      | mA   |

|                  | Zero crossing current                                    |                                                               | 5    | 20   | 35   | mA   |

|                  |                                                          | Enable, Reference                                             |      |      |      |      |

| VENH             | EN input voltage 'high'                                  |                                                               | 0.7  |      |      | V    |

| VENL             | EN input voltage 'low'                                   |                                                               |      |      | 0.1  | V    |

| I <sub>EN</sub>  | EN input bias current                                    | N input bias current EN = 5V, TAMB = 25°C                     |      |      | 100  | nA   |

| I <sub>REF</sub> | REF input bias currentREF = 0.99xVoutnom,<br>TAMB = 25°C |                                                               |      |      | 100  | nA   |

|                  |                                                          | Low Battery & Power-OK                                        |      |      |      |      |

| $V_{\text{LBI}}$ | LBI threshold                                            | Falling edge                                                  | 0.57 | 0.6  | 0.63 | V    |

|                  | LBI hysteresis                                           |                                                               |      | 25   |      | mV   |

| I <sub>LBI</sub> | LBI leakage current                                      | LBI $\leq$ VIN or VOUT (which ever<br>is higher), TAMB = 25°C |      |      | 100  | nA   |

| V <sub>LBO</sub> | LBO voltage low <sup>(2)</sup>                           | Ilbo = 1mA                                                    |      | 5    | 20   | mV   |

| I <sub>LBO</sub> | LBO leakage current                                      | TAMB = 25°C                                                   |      |      | 100  | nA   |

|                  | Power-OK threshold                                       | LBI = 0V, Falling Edge                                        | 87   | 91   | 95   | %    |

|                  |                                                          | Thermal Protection                                            | •    |      |      |      |

|                  | Thermal shutdown <sup>(3)</sup>                          | 10°C Hysteresis                                               |      | 150  |      | °C   |

Caution: Do not apply full load current until the device output > 2.5V

#### Note(s) and/or Footnote(s):

1. The regulator is in startup mode until this voltage is reached.

2. LBO goes low in startup mode as well as during normal operation if,

(i) The voltage at the LBI pin is lower than LBI threshold.

(ii) The voltage at the LBI pin is below 0.1V (connected to GND) and VOUT is below 92.5% of its nominal value.

3. Further switching is inhibited.

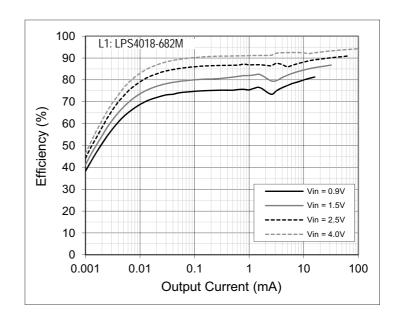

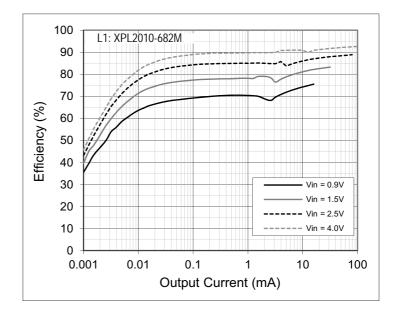

# Typical Operating Characteristics

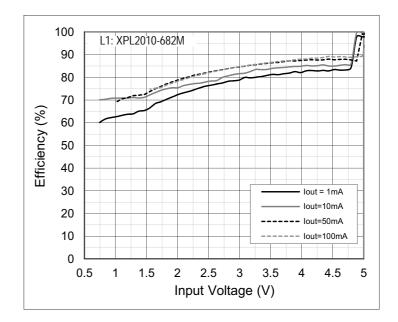

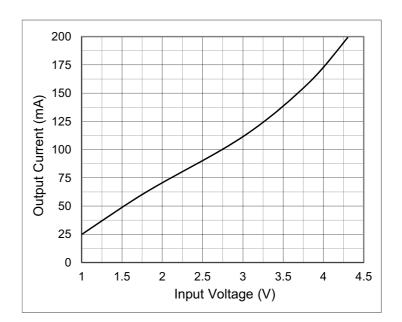

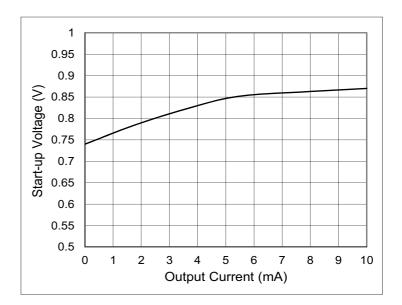

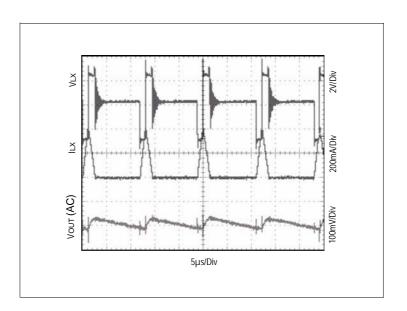

VOUT = 5.0V, TAMB = 25°C, unless otherwise specified.

Figure 7: Efficiency vs. Output Current

Figure 8: Efficiency vs. Output Current

Figure 9: Efficiency vs. Input Voltage

Figure 10: Maximum Output Current vs. Input Voltage

Figure 11: Start-up Voltage vs. Output Current

Figure 12: Output Voltage Ripple;  $V_{IN}$ = 2V,  $R_{load}$ = 100 $\Omega$

# **Detailed Description**

## **Hysteretic Boost Converter**

Hysteretic boost converters are so called because comparators are the active elements used to determine on-off timing via current and voltage measurements. There is no continuously operating fixed oscillator, providing an independent timing reference. As a result, a hysteretic or comparator based converter has a very low quiescent current. In addition, because there is no fixed timing reference, the operating frequency is determined by external component (inductor and capacitors) and also the loading on the output.

Ripple at the output is an essential operating component. A power cycle is initiated when the output regulated voltage drops below the nominal value of VOUT (0.99 x VOUT).

Inductor current is monitored by the control loop, ensuring that operation is always dis-continuous.

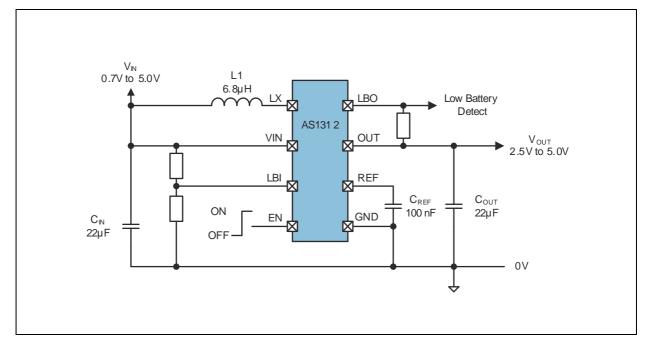

The application circuit shown in Figure 15 will support many requirements. However, further optimization may be useful, and the following is offered as a guide to changing the passive components to more closely match the end requirement.

### Input Loop Timing

The input loop consists of the source dc supply, the input capacitor, the main inductor, and the N-channel power switch. The on timing of the N-channel switch is determined by a peak current measurement or a maximum on time. In the AS1312, peak current is 400mA (typ) and maximum on time is 4.2µs (typ). Peak current measurement ensures that the on time varies as the input voltage varies. This imparts line regulation to the converter.

The fixed on-time measurement is something of a safety feature to ensure that the power switch is never permanently on. The fixed on-time is independent of input voltage changes. As a result, no line regulation exists.

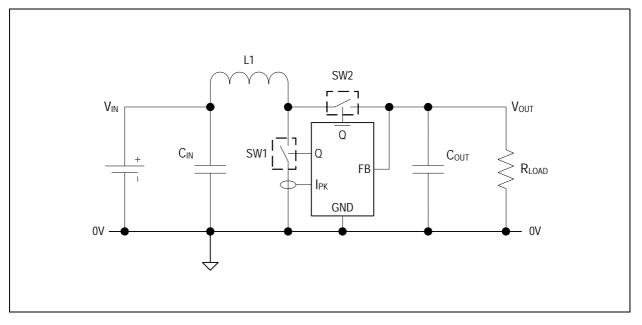

#### Figure 13: Simplified Boost DCDC Architecture

On time of the power switch (Faraday's Law) is given by:

(EQ1)

$$T_{ON} = \frac{LI_{PK}}{V_{IN} - (I_{PK}R_{SW1} + I_{PK}R_{L1})}$$

sec [volts, amps, ohms, Henry]

Applying Min and Max values and neglecting the resistive voltage drop across L1 and SW1;

$$(EQ2) \quad T_{ON\_MIN} = \frac{L_{MIN}I_{PK\_MIN}}{V_{IN\_MAX}}$$

(EQ3)

$$T_{ON\_MAX} = \frac{L_{MAX}I_{PK\_MAX}}{V_{IN\_MIN}}$$

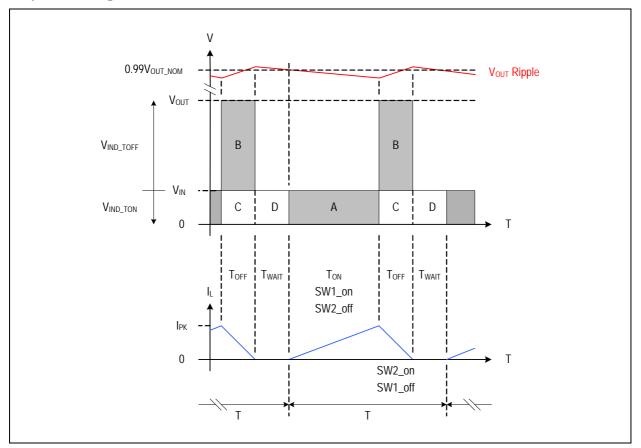

#### Figure 14: Simplified Voltage and Current Waveforms

Another important relationship is the "volt-seconds" law. Expressed as following:

$(EQ4) V_{ON}T_{ON} = V_{OFF}T_{OFF}$

Voltages are those measured across the inductor during each time segment. Figure 14 shows this graphically with the shaded segments marked "A & B". Re-arranging (EQ 4):

$$(EQ5) \quad \frac{T_{ON}}{T_{OFF}} = \frac{V_{OUT} - V_{IN}}{V_{IN}}$$

The time segment called T<sub>WAIT</sub> in Figure 14 is a measure of the "hold-up" time of the output capacitor. While the output voltage is above the threshold (0.99xVout), the output is assumed to be in regulation and no further switching occurs.

### Inductor Choice Example

For the AS1312 V<sub>IN\_MIN</sub> = 0.9V, V<sub>OUT\_MAX</sub> = 3.3V, (EQ 5) gives  $T_{ON}$ =2.66 $T_{OFF}$ .

Let the maximum operating on-time = 1 $\mu$ s. Note that this is shorter than the minimum limit on-time of 3.6 $\mu$ s. Therefore from (EQ 5), T<sub>OFF</sub> = 0.376 $\mu$ s. Using (EQ 3), L<sub>MAX</sub> is obtained:

$L_{MAX} = 1.875 \mu$ H. The nearest preferred value is 2.2 $\mu$ H.

This value provides the maximum energy storage for the chosen fixed on-time limit at the minimum VIN.

Energy stored during the on time is given by:

(EQ6)

$$E = 0.5L(I_{PK})^2$$

Joules (Region A in Figure 14)

If the overall time period  $(T_{ON} + T_{OFF})$  is T, the power taken from the input is:

(EQ7)

$$P_{IN} = \frac{0.5L(I_{PK})^2}{T}$$

Watts

Assume output power is 0.8  $\mathrm{P}_{\mathrm{IN}}$  to establish an initial value of operating period T.

$T_{WAIT}$  is determined by the time taken for the output voltage to fall to 0.99xV<sub>OUT</sub>. The longer the wait time, the lower will be the supply current of the converter. Longer wait times require increased output capacitance. Choose  $T_{WAIT} = 10\%$  T as a minimum starting point for maximum energy transfer. For very low power load applications, choose  $T_{WAIT} \ge 50\%$  T.

### **Output Loop Timing**

The output loop consists of the main inductor, P-channel synchronous switch (or diode if fitted), output capacitor and load. When the input loop is interrupted, the voltage on the LX pin rises (Lenz's Law). At the same time a comparator enables the synchronous switch, and energy stored in the inductor is transferred to the output capacitor and load. Inductor peak current supports the load and replenishes the charge lost from the output capacitor. The magnitude of the current from the inductor is monitored, and as it approaches zero, the synchronous switch is turned off. No switching action continues until the output voltage falls below the output reference point (0.99 x VOUT).

Output power is composed of the dc component (Region C in Figure 14):

$$(EQ8) \quad \mathsf{P}_{\mathsf{REGION}_{\mathsf{C}}} = V_{IN} \frac{I_{PK}}{2} \frac{T_{OFF}}{T}$$

Output power is also composed of the inductor component (Region B in Figure 14), neglecting efficiency loss:

$$(EQ9) \quad \mathsf{P}_{\mathsf{REGION}_{\mathsf{B}}} = \frac{0.5L(I_{PK})^2}{T}$$

Total power delivered to the load is the sum of (EQ 8) and (EQ 9):

(EQ10)

$$P_{TOTAL} = V_{IN} \frac{I_{PK}}{2} \frac{T_{OFF}}{T} + \frac{0.5L(I_{PK})^2}{T}$$

From (EQ 3) (using nominal values) peak current is given by:

$$(EQ11) \quad I_{PK} = \frac{T_{ON}V_{IN}}{L}$$

Substituting (EQ 11) into (EQ 10) and re-arranging:

(EQ12)

$$P_{TOTAL} = \frac{V_{IN}^2 T_{ON}}{2TL} (0.9T)$$

0.9T incorporates a wait time  $T_{WAIT} = 10\% T$

Output power in terms of regulated output voltage and load resistance is:

$$(EQ13) \quad P_{OUT} = \frac{V^2_{OUT}}{R_{LOAD}}$$

Combining (EQ 12) and (EQ 13):

(EQ14)

$$\frac{V_{OUT}^2}{R_{LOAD}} = \frac{V_{IN}^2 T_{ON}}{2TL} (0.9T) \eta$$

Symbol  $\eta$  reflects total energy loss between input and output and is approximately 0.8 for these calculations. Use (EQ 14) to plot duty cycle (T<sub>ON</sub>/T) changes for various output loadings and changes to VIN.

### Input Capacitor Selection

The input capacitor supports the triangular current during the on-time of the power switch, and maintains a broadly constant input voltage during this time. The capacitance value is obtained from choosing a ripple voltage during the on-time of the power switch. Additionally, ripple voltage is generated by the equivalent series resistance (ESR) of the capacitor. For worst case, use maximum peak current values from the datasheet.

$$(EQ15) \quad C_{IN} = \frac{I_{PEAK}T_{ON}}{V_{RIPPLE}}$$

Using  $T_{ON}$  = 1µs, and  $I_{PEAK}$  = 400mA (typ), and  $V_{RIPPLE}$  = 50mV, EQ 15 yields:

$CIN = 8.0 \mu F$

Nearest preferred would be 10µF.

$$(EQ16) \quad V_{PK\_RIPPLE\_ESR} = I_{PK}R_{ESR}$$

Typically, the ripple due to ESR is not dominant. ESR for the recommended capacitors (Murata GMR), ESR =  $5m\Omega$  to  $10m\Omega$ . For the AS1312, maximum peak current is 400mA. Ripple due to ESR is 2.0mV to 4.0mV.

Ripple at the input propagates through the common supply connections, and if too high in value can cause problems elsewhere in the system. The input capacitance is an important component to get right.

### **Output Capacitor Selection**

The output capacitor supports the triangular current during the off-time of the power switch (inductor discharge period), and also the load current during the wait time (Region D in Figure 14) and on-time (Region A in Figure 14) of the power switch.

(EQ17)

$$C_{OUT} = \frac{I_{LOAD}(T_{ON} + T_{WAIT})}{(1 - 0.99)V_{OUT_NOM}}$$

**Note(s):** There is also a ripple component due to the equivalent series resistance (ESR) of the capacitor.

#### Summary

#### **User Application Defines:**

VINmin, VINmax, VOUTmin, VOUTmax, I<sub>LOAD</sub>min, I<sub>LOAD</sub>max

#### **Inductor Selection:**

Select Max on-time =  $0.5\mu s$  to  $3\mu s$  for AS1312. Use (EQ 3) to calculate inductor value.

Use (EQ 5) to determine off-time.

Use (EQ 6) to check that power delivery matches load requirements assume 70% conversion efficiency.

Use (EQ 13) to find overall timing period value of T at min  $V_{\rm IN}$  and max  $V_{\rm OUT}$  for maximum load conditions.

#### Input Capacitor Selection:

Choose a ripple value and use (EQ 14) to find the value.

#### **Output Capacitor Selection:**

Determine  $T_{WAIT}$  via (EQ 6) or (EQ 13), and use (EQ 16) to find the value.

# **Application Information**

The AS1312 is available with fixed output voltages from 2.5V to 5.0V in 50mV steps.

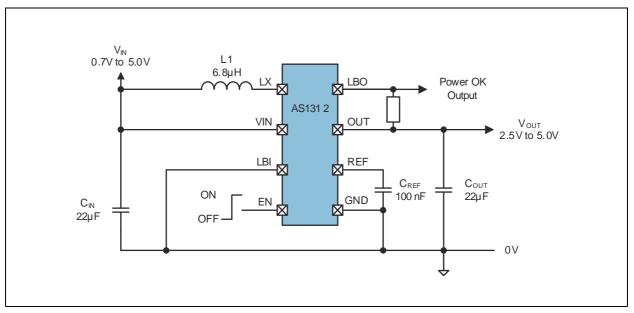

Figure 15: Typical Application Diagram

### **AS1312 Features**

#### Shutdown

The part is in shutdown mode while the voltage at pin EN is below 0.1V and is active when the voltage is higher than 0.7V.

**Note(s):** EN can be driven above VIN or VOUT, as long as it is limited to less than 5.0V.

#### **Output Disconnect**

During shutdown VOUT is going to 0V and no current from the input source is running through the device.

### Feedthrough Mode

If the input voltage is higher than the output voltage (and the AS1312 is enabled) the supply voltage is connected to the load through the device. To guarantee a proper function of the AS1312 it is not allowed that the supply exceeds the maximum allowed input voltage (5.0V).

In this feedthrough mode the quiescent current is 35µA (typ.). The device goes back into step-up mode when the output voltage is 4% (typ.) below VOUTNOM.

### Power-OK and Low-Battery-Detect Functionality

LBO goes low in startup mode as well as during normal operation if:

- The voltage at the LBI pin is below LBI threshold (0.6V). This can be used to monitor the battery voltage.

- LBI pin is connected to GND and VOUT is below 92.5% of its nominal value. LBO works as a power-OK signal in this case.

The LBI pin can be connected to a resistive-divider to monitor a particular definable voltage and compare it with a 0.6V internal reference. If LBI is connected to GND an internal resistive-divider is activated and connected to the output. Therefore, the Power-OK functionality can be realized with no additional external components.

The Power-OK feature is not active during shutdown and provides a power-on-reset function that can operate down to VIN = 0.7V. A capacitor to GND may be added to generate a power-on-reset delay. To obtain a logic-level output, connect a pull-up resistor R3 from pin LBO to pin VOUT. Larger values for this resistor will help to minimize current consumption; a 100k $\Omega$  resistor is perfect for most applications see Figure 17.

For the circuit shown in the left of Figure 16, the input bias current into LBI is very low, permitting large-value resistor-divider networks while maintaining accuracy. Place the resistor-divider network as close to the device as possible. Use a defined resistor for R2 and then calculate R1 as:

$$(EQ18) \quad R_1 = R_2 \cdot \left(\frac{V_{IN}}{V_{LBI}} - 1\right)$$

Where: VLB<sub>I</sub> is 0.6V

#### Figure 17: Typical Application with LBO Working as Power-OK

### Thermal Shutdown

To prevent the AS1312 from short-term misuse and overload conditions the chip includes a thermal overload protection. To block the normal operation mode all further switching is inhibited for output voltage above VOUT lockout threshold. The device is in thermal shutdown when the junction temperature exceeds 150°C. To resume the normal operation the temperature has to drop below 140°C.

A good thermal path has to be provided to dissipate the heat generated within the package. Otherwise it's not possible to operate the AS1312 at its usable maximal power. To dissipate as much heat as possible from the package into a copper plane with as much area as possible, it's recommended to use multiple vias in the printed circuit board. It's also recommended to solder the Exposed Pad (pin 9) to the GND plane.

**Note(s):** Continuing operation in thermal overload conditions may damage the device and is considered bad practice.

## **Component Selection**

Only four components are required to complete the design of the step-up converter. The low peak currents of the AS1312 allow the use of low value, low profile inductors and tiny external ceramic capacitors.

### **Inductor Selection**

For best efficiency, choose an inductor with high frequency core material, such as ferrite, to reduce core losses. The inductor should have low DCR (DC resistance) to reduce the  $l^2R$  losses, and must be able to handle the peak inductor current without saturating. A 6.8µH inductor with a > 500mA current rating and < 500m $\Omega$  DCR is recommended.

Figure 18: Recommended Inductors

| Part Number      | L     | DCR    | Current<br>Rating | Size in mm<br>(L/W/T) | Manufacturer                              |

|------------------|-------|--------|-------------------|-----------------------|-------------------------------------------|

| ELLVEG6R8N       | 6.8uH | 0.35Ω  | 0.58A             | 3x3x1                 |                                           |

| ELLVFG6R8MC      | 6.8uH | 0.23Ω  | 0.6A              | 3x3x1.2               | Panasonic<br>www.industrial.panasonic.com |

| ELLVGG6R8N       | 6.8uH | 0.23Ω  | 1A                | 3x3x1.5               |                                           |

| LQH3NPN6R8MM0    | 6.8uH | 0.24Ω  | 1A                | 3x3x1.4               |                                           |

| LQH3NPN6R8NM0    | 6.8uH | 0.24Ω  | 1A                | 3x3x1.4               |                                           |

| LQH3NPN6R8MJ0    | 6.8uH | 0.252Ω | 0.85A             | 3x3x1.1               | Murata<br>www.murata.com                  |

| LQH3NPN6R8NJ0    | 6.8uH | 0.252Ω | 0.85A             | 3x3x1.1               |                                           |

| LQH3NPN6R8MMR    | 6.8uH | 0.186Ω | 1.25A             | 3x3x1.1               |                                           |

| VLS2012ET-6R8M   | 6.8uH | 0.498  | 0.57A             | 2x2x1.2               |                                           |

| VLS252015ET-6R8M | 6.8uH | 0.48   | 0.85A             | 2.5x2x1.5             |                                           |

| VLS3010ET-6R8M   | 6.8uH | 0.312  | 0.69A             | 3x3x1                 | TDK<br>www.tdk.com                        |

| VLS3012ET-6R8M   | 6.8uH | 0.228  | 0.81A             | 3x3x1.2               |                                           |

| VLS3015ET-6R8M   | 6.8uH | 0.216  | 0.92A             | 3x3x1.5               |                                           |

| LPS4018-682ML    | 6.8uH | 0.15   | 1.2A              | 4x4x1.7               | Coilcraft<br>www.coilcraft.com            |

## **Capacitor Selection**

The convertor requires three capacitors. Ceramic X5R or X7R types will minimize ESL and ESR while maintaining capacitance at rated voltage over temperature. The VIN capacitor should be  $22\mu$ F. The VOUT capacitor should be between  $22\mu$ F and  $47\mu$ F. A larger output capacitor should be used if lower peak to peak output voltage ripple is desired. A larger output capacitor will also improve load regulation on VOUT. See table below for a list of capacitors for input and output capacitor selection.

Figure 19: Recommended Input and Output Capacitors

| Part Number         | С    | TC<br>Code | Rated<br>Voltage | Size in mm<br>(L/W/T) | Manufacturer       |  |

|---------------------|------|------------|------------------|-----------------------|--------------------|--|

| GRM21BR60J226ME39L  | 22uF | X5R        | 6.3V             | 2x1.25x1.25           | Murata             |  |

| GRM31CR61A226ME19L  | 22uF | X5R        | 10V              | 3.2x1.6x1.6           | www.murata.com     |  |

| 12066D226KAT_A      | 22uF | X5R        | 6.3V             | 3.2x1.6x1.78          |                    |  |

| 1210ZD226KAT_A      | 22uF | X5R        | 10V              | 3.2x1.6x1.78          | AVX<br>www.avx.com |  |

| 1210YD226KAT_A      | 22uF | X5R        | 16V              | 3.2x1.6x1.78          |                    |  |

| C2012X5R0J226K/1.25 | 22uF | X5R        | 6.3V             | 2x1.2x1.25            |                    |  |

| C2012X5R1A226K/1.25 | 22uF | X5R        | 10V              | 2x1.2x1.25            | TDK<br>www.tdk.com |  |

| C2012X5R1C226K      | 22uF | X5R        | 16V              | 2x1.2x1.25            |                    |  |

On the pin REF a 100nF capacitor with an Insulation resistance >1G $\Omega$  is recommended.

Figure 20: Recommended Capacitors for REF

| Part Number       | С     | TC<br>Code | Insulation<br>Resistance | Rated<br>Voltage | Dimensions<br>(L/W/T) | Manufacturer             |

|-------------------|-------|------------|--------------------------|------------------|-----------------------|--------------------------|

| GRM188R71C104KA01 | 100nF | X7R        | >5GΩ                     | 16V              | 0603, T=0.8mm         | Murata<br>www.murata.com |

### **Layout Considerations**

Relatively high peak currents of 400mA (typ) circulate during normal operation of the AS1312. Long printed circuit tracks can generate additional ripple and noise that mask correct operation and prove difficult to "de-bug" during production testing. Referring to Figure 15, the input loop formed by C1, VIN and GND pins should be minimized. Similarly, the output loop formed by C2, VOUT and GND should also be minimized. Ideally both loops should connect to GND in a "star" fashion. Finally, it is important to return CREF to the GND pin directly.

# Package Drawings & Markings

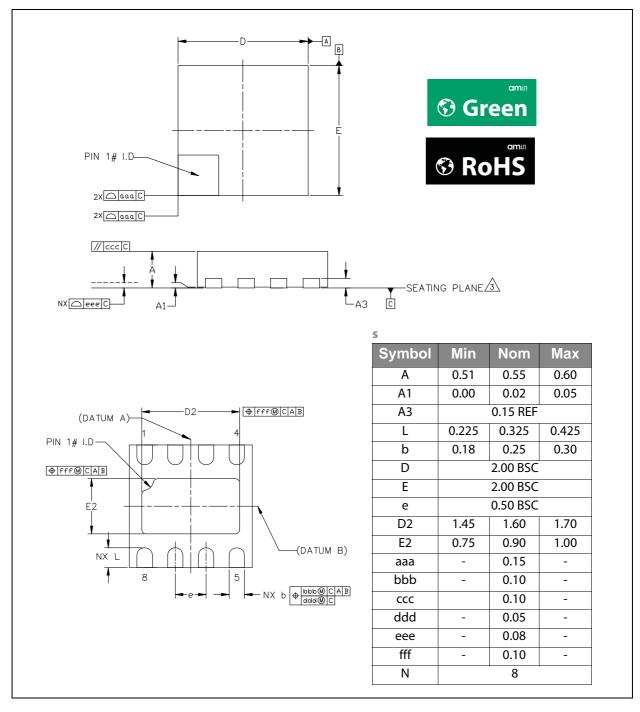

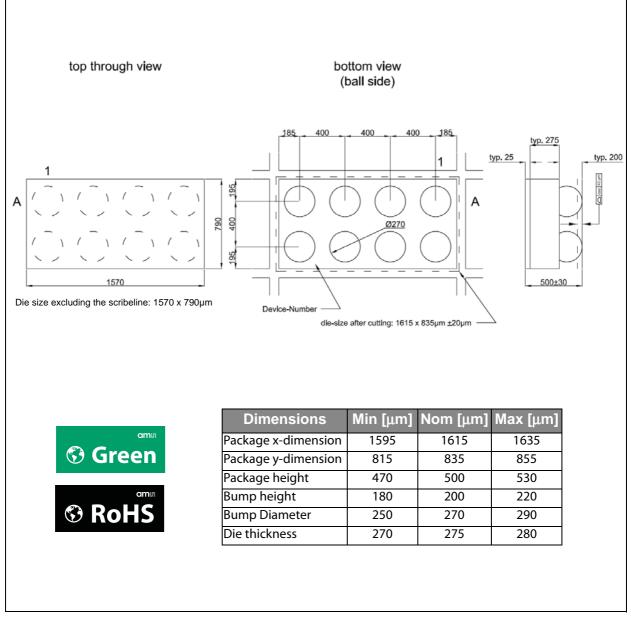

The device is available in a 8-pin (2x2) TDFN and 8-pin WL-CSP package.

Figure 21: 8-pin (2x2) TDFN Marking

Figure 22: 8-pin WL-CSP Marking

#### Figure 23: Packaging Code

| ХХХ                | хххх                 | YY      |

|--------------------|----------------------|---------|

| Tracecode for TDFN | Tracecode for WL-CSP | Marking |

#### Figure 24: 8-pin (2x2) TDFN Drawings and Dimensions

#### Note(s) and/or Footnote(s):

- 1. Dimensioning & tolerancing conform to ASME Y14.5M-1994.

- 2. All dimensions are in millimeters. Angles are in degrees.

- 3. Coplanarity applies to the exposed heat slug as well as the terminal.

- 4. Radius on terminal is optional.

- 5. N is the total number of terminals.

# Figure 25:

8-pin WL-CSP Drawings and Dimensions

#### Note(s) and/or Footnote(s):

- 1. ccc Coplanarity.

- 2. All dimensions are in  $\mu m.$

- 3. "Bottom view" and "top trough view" values indicate the die dimensions without scribe lines. The "die size after cutting" values gives the package dimensions with tolerance.

# **Ordering & Contact Information** The device is available as the standard products listed below.

Figure 26: Ordering Information

| Ordering Code         | Marking | V <sub>OUT</sub> | Description                  | Delivery Form | Package          |

|-----------------------|---------|------------------|------------------------------|---------------|------------------|

| AS1312-BTDT-50        | BE      | 5.0V             |                              | Tape and Reel | 8-pin (2x2) TDFN |

| AS1312-BTDT-33        | BX      | 3.3V             |                              | Tape and Reel | 8-pin (2x2) TDFN |

| AS1312-BTDT-30        | BY      | 3.0V             | Ultra Low                    | Tape and Reel | 8-pin (2x2) TDFN |

| AS1312-BTDM-27        | C1      | 2.7V             | Quiescent                    | Tape and Reel | 8-pin (2x2) TDFN |

| AS1312-BWLT-50        | BF      | 5.0V             | Current,<br>Hysteretic DC-DC | Tape and Reel | 8-pin WL-CSP     |

| AS1312-BWLT-45        | BQ      | 4.5V             | Step-up Converter            | Tape and Reel | 8-pin WL-CSP     |

| AS1312-BWLT-33        | CO      | 3.3V             |                              | Tape and Reel | 8-pin WL-CSP     |

| AS1312 <sup>(1)</sup> | tbd     | хх               |                              | Tape and Reel | tbd              |

#### Note(s) and/or Footnote(s):

1. Non-standard devices from 2.5V to 5.0V are available in 50mV steps.

The above figure shows the ordering codes for Tape & Reel deliveries (suffix **T** in the ordering code). It is also possible to have all the variants on mini reels, when the ordering codes are AS1312-BTDM-xx or AS1312-BWLM (where suffix **M** stands for mini reel). The components are the same in both reel sizes.

Buy our products or get free samples online at: www.ams.com/ICdirect

Technical Support is available at: www.ams.com/Technical-Support

Provide feedback about this document at: www.ams.com/Document-Feedback

For further information and requests, e-mail us at: ams\_sales@ams.com

For sales offices, distributors and representatives, please visit: www.ams.com/contact

#### Headquarters

ams AG Tobelbaderstrasse 30 8141 Unterpremstaetten Austria, Europe

Tel: +43 (0) 3136 500 0

Website: www.ams.com

# RoHS Compliant & ams Green Statement

**RoHS:** The term RoHS compliant means that ams AG products fully comply with current RoHS directives. Our semiconductor products do not contain any chemicals for all 6 substance categories, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, RoHS compliant products are suitable for use in specified lead-free processes.

**ams Green (RoHS compliant and no Sb/Br):** ams Green defines that in addition to RoHS compliance, our products are free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material).

**Important Information:** The information provided in this statement represents ams AG knowledge and belief as of the date that it is provided. ams AG bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. ams AG has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. ams AG and ams AG suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

## **Copyrights & Disclaimer**

Copyright ams AG, Tobelbader Strasse 30, 8141 Unterpremstaetten, Austria-Europe. Trademarks Registered. All rights reserved. The material herein may not be reproduced, adapted, merged, translated, stored, or used without the prior written consent of the copyright owner.

Devices sold by ams AG are covered by the warranty and patent indemnification provisions appearing in its General Terms of Trade. ams AG makes no warranty, express, statutory, implied, or by description regarding the information set forth herein. ams AG reserves the right to change specifications and prices at any time and without notice. Therefore, prior to designing this product into a system, it is necessary to check with ams AG for current information. This product is intended for use in commercial applications. Applications requiring extended temperature range, unusual environmental requirements, or high reliability applications, such as military, medical life-support or life-sustaining equipment are specifically not recommended without additional processing by ams AG for each application. This product is provided by ams AG "AS IS" and any express or implied warranties, including, but not limited to the implied warranties of merchantability and fitness for a particular purpose are disclaimed.

ams AG shall not be liable to recipient or any third party for any damages, including but not limited to personal injury, property damage, loss of profits, loss of use, interruption of business or indirect, special, incidental or consequential damages, of any kind, in connection with or arising out of the furnishing, performance or use of the technical data herein. No obligation or liability to recipient or any third party shall arise or flow out of ams AG rendering of technical or other services.

## **Document Status**

| Document Status          | Product Status  | Definition                                                                                                                                                                                                                                                                     |

|--------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Product Preview          | Pre-Development | Information in this datasheet is based on product ideas in<br>the planning phase of development. All specifications are<br>design goals without any warranty and are subject to<br>change without notice                                                                       |

| Preliminary Datasheet    | Pre-Production  | Information in this datasheet is based on products in the<br>design, validation or qualification phase of development.<br>The performance and parameters shown in this document<br>are preliminary without any warranty and are subject to<br>change without notice            |

| Datasheet                | Production      | Information in this datasheet is based on products in<br>ramp-up to full production or full production which<br>conform to specifications in accordance with the terms of<br>ams AG standard warranty as given in the General Terms of<br>Trade                                |

| Datasheet (discontinued) | Discontinued    | Information in this datasheet is based on products which<br>conform to specifications in accordance with the terms of<br>ams AG standard warranty as given in the General Terms of<br>Trade, but these products have been superseded and<br>should not be used for new designs |

# **Revision Information**

| Changes from 1-16 (2014-Sep-01) to current revision 1-18 (2014-Dec-15) | Page |

|------------------------------------------------------------------------|------|

| Updated Package Drawings & Markings section                            |      |

#### Note(s) and/or Footnote(s):

1. Page and figure numbers for the previous version may differ from page and figure numbers in the current revision.

2. Correction of typographical errors is not explicitly mentioned.

### **Content Guide**

#### 1 General Description

- 1 Key Benefits & Features

- 2 Applications

- 2 Block Diagram

- 3 Pin Assignments

- 4 Absolute Maximum Ratings

- 5 Electrical Characteristics

- 7 Typical Operating Characteristics

#### 10 Detailed Description

- 10 Hysteretic Boost Converter

- 10 Input Loop Timing

- 13 Inductor Choice Example

- 14 Output Loop Timing

- 15 Input Capacitor Selection

- 16 Output Capacitor Selection

- 16 Summary

#### 17 Application Information

- 17 AS1312 Features

- 17 Shutdown

- 17 Output Disconnect

- 17 Feedthrough Mode

- 18 Power-OK and Low-Battery-Detect Functionality

- 19 Thermal Shutdown

- 20 Component Selection

- 20 Inductor Selection

- 21 Capacitor Selection

- 21 Layout Considerations

- 22 Package Drawings & Markings

- 25 Ordering & Contact Information

- 26 RoHS Compliant & ams Green Statement

- 27 Copyrights & Disclaimer

- 28 Document Status

- 29 Revision Information