# AS1851A/31A — Digital Power PoE PD Controllers w/HV Isolation & Synchronous DC-DC Converter

#### **GENERAL DESCRIPTION**

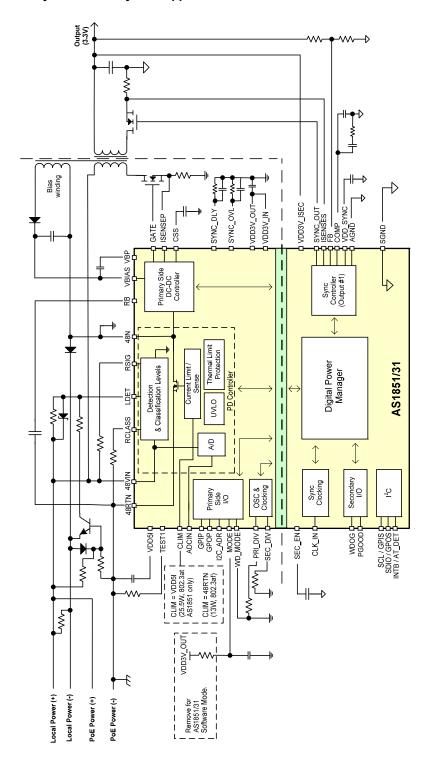

The AS1851A and AS1831A devices each integrate Akros  $GreenEdge^{TM}$  High Voltage Isolation technology with Power-over-Ethernet (PoE) PD and Synchronous DC-DC power conversion technology.

The AS1851A includes a 13W/25W (Type 1 and Type 2) IEEE®802.3af/at compliant PD integrated with high-voltage isolation and a digital power Synchronous DC-DC converter.

The AS1831A includes a 13W (Type 1) IEEE®802.3af/at compliant PD integrated with high-voltage isolation and a digital power Synchronous DC-DC converter.

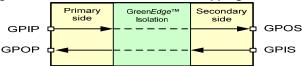

In addition to enabling digital PoE power conversion, Akros  $GreenEdge^{TM}$  isolation enables direct digital management of both isolated Primary power and Secondary system power for real time end-to-end Green Power application capabilities.

#### TYPICAL APPLICATIONS

- Voice-over-IP (VoIP) phones

- Wireless LAN & WiMAX access points (WAP)

- Pan, Tilt, Zoom (PTZ) Cameras, IP cameras

- Thin-client and notebook computers

- Fiber-to-the-home (FTTH) terminals

- Point-of-sale (PoS) terminals, RFID readers

#### ORDERING INFORMATION

The AS1851A and AS1831A pin-compatible devices are available in 64-lead QFN Reduction of Hazardous Substance (RoHS) compliant packages.

| Part #   | Type 1<br>PD | Type 2<br>PD | Hardware<br>Mode | Software<br>Mode | Pwr In<br>(W) |

|----------|--------------|--------------|------------------|------------------|---------------|

| AS1851A* | х            | Х            | Х                | Х                | 13/30         |

| AS1831A* | х            |              | Х                | Х                | 13            |

<sup>\*</sup> Industrial Temperature Range, -40°C to 85°C

#### **FEATURES**

#### **Digitally Isolated Programmable Power**

#### **PoE PD Controller**

- Type 1 and Type 2 IEEE<sup>®</sup> 802.3af & 802.3at Compliant PD (AS1851A), Type 1 only (AS1831A)

- Automatic PoE-Plus (Type 2) detection in HW and I<sup>2</sup>C Modes (AS1851A only)

- Low Resistance PD Power FET Switch (0.5Ω typical)

#### **Primary-Side DC-DC Controller**

- High-efficiency DC-DC Controller with Digital Optimization

- Primary-Secondary High-voltage integrated Digital Isolation

- Programmable Primary Clock Frequency Local-power operation Down to 9.5V

#### Secondary-Side Sync Power Output

- Synchronous Controller with programmable power-FET timing for high efficiency at both light and full load

- Programmable PWM Frequencies synched to External Clock

#### **Power Management**

- Hardware programmable start-up power sequencing

- Primary-side power monitoring & control from Secondary-side

- Individual output Power-Good management

- Voltage margining for each output

- Primary GPIO/ADC controlled via Secondary GPIO or I<sup>2</sup>C

- 5V μC-compatible with interrupt on alarm services

- Programmable watchdog timer

#### **EMC Compliance and Protection**

- Slew-rate-controlled power drivers

- External PWM sync clock option

- Optional spread-spectrum clocking, SW controlled

- Over-current, Under/Over-voltage and Short-circuit Protection

- High-temperature warning and shutdown

- Meets IEC 61000-4-2/3/4/5/6, IEC60747, IEC 60950, DIN EN60747-5-2 (VDE0884), & UL1577 requirements for EMC compliance and basic isolation to 2120 VDC (1500 VRMS)

- 100V Process for PoE transient voltage robustness

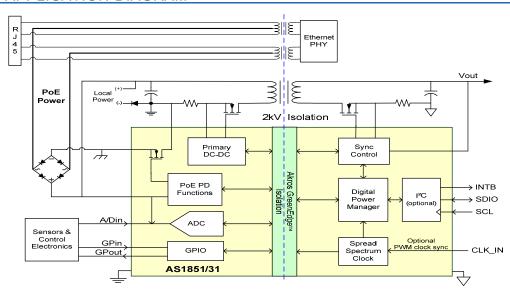

#### SIMPLIFIED APPLICATION DIAGRAM

## **TABLE OF CONTENTS**

| GENERAL DESCRIPTION                               |      |

|---------------------------------------------------|------|

| TYPICAL APPLICATIONS                              | 1    |

| ORDERING INFORMATION                              |      |

| FEATURES                                          | 1    |

| DIGITALLY ISOLATED PROGRAMMABLE POWER             | 1    |

| POE PD CONTROLLER                                 |      |

| PRIMARY-SIDE DC-DC CONTROLLER                     |      |

| SECONDARY-SIDE SYNC POWER OUTPUT                  |      |

| POWER MANAGEMENT                                  |      |

| EMC COMPLIANCE AND PROTECTION                     | 1    |

| SIMPLIFIED APPLICATION DIAGRAM                    | 1    |

| PIN ASSIGNMENTS AND DESCRIPTIONS                  |      |

| TEST SPECIFICATIONS                               |      |

| FUNCTIONAL DESCRIPTION                            |      |

| ISOLATION                                         |      |

| PD CONTROLLER                                     |      |

| PD POWER MOSFET                                   |      |

| UNDER-VOLTAGE LOCKOUT (UVLO)                      |      |

| POE CURRENT LIMIT/CURRENT SENSE                   | . 10 |

|                                                   |      |

| OVER-TEMPERATURE PROTECTION                       |      |

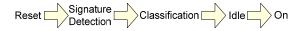

| PD OPERATING STATES                               | . 15 |

| AT DETECTION OPERATION (AS1851A ONLY)             |      |

| LOCAL POWER SOURCE                                | . 16 |

| PWM CLOCK FREQUENCY CONFIGURATION                 | . 17 |

| EXTERNAL CLOCK SOURCE (CLK_IN)                    | . 17 |

| EMI PERFORMANCE CONTROL                           |      |

| POWER OUTPUT                                      |      |

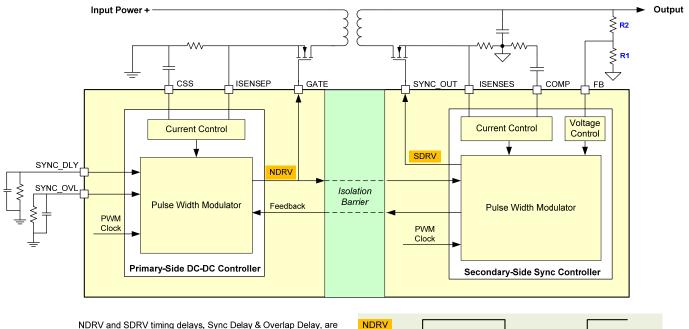

| PRIMARY-SIDE DC-DC CONTROLLER                     | . 18 |

| SOFT-START INRUSH CURRENT LIMIT                   |      |

| CURRENT-LIMIT AND CURRENT SENSE                   |      |

| SECONDARY-SIDE SYNC CONTROLLER                    |      |

| COMPENSATION AND LOOP FEEDBACK                    |      |

| LOW-LOAD CURRENT OPERATION - DCM                  |      |

| OVER-VOLTAGE PROTECTION                           | . 19 |

| RF & EMI FILTERING                                | . 19 |

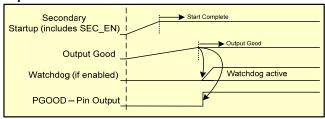

| HARDWARE MODE OPERATION                           | . 20 |

| DEVICE INITIALIZATION & HARDWARE MODE SELECTION   |      |

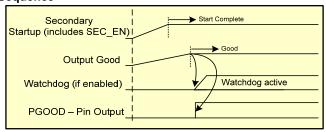

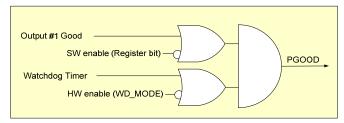

| HW MODE POWER MONITORING (PGOOD)                  | . 20 |

| HW MODE WATCHDOG TIMER                            |      |

| WATCHDOG CONFIGURATION                            |      |

| WATCHDOG SERVICE                                  |      |

| WATCHDOG TIMEOUT                                  |      |

| IF THE WATCHDOG TIMES OUT, THE FOLLOWING OCCUR:   |      |

| HW MODE GENERAL-PURPOSE I/O OPERATION             | . 20 |

| SOFTWARE MODE OPERATION                           |      |

| DEVICE INITIALIZATION AND SOFTWARE MODE SELECTION |      |

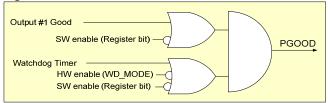

| SW MODE POWER STATUS MONITORING (PGOOD)           |      |

| HISTORY REGISTER                                  |      |

| PD VOLTAGE AND CURRENT MEASUREMENTS               |      |

| PD OVER-CURRENT ALARM THRESHOLD                   |      |

| SW MODE POWER MARGINING                           |      |

| OVV INIODE I OVVETA IVIALOUININO                  | . 44 |

| SW MODE EMI PERFORMANCE CONTROL                                                                       |    |

|-------------------------------------------------------------------------------------------------------|----|

| PWM CLOCKS - PRBS RANDOMIZATION                                                                       | 22 |

| PWM CLOCKS - FRACTIONAL-N                                                                             |    |

| SW MODE GENERAL-PURPOSE I/O & ADC                                                                     |    |

| GENERAL-PURPOSE I/O PINS                                                                              |    |

| GENERAL-PURPOSE ADC (ADCIN PIN)                                                                       | 22 |

| SW MODE WATCHDOG TIMER OPERATION                                                                      | 22 |

| WATCHDOG TIMER OPERATION                                                                              |    |

| SW MODE INTERRUPT OPERATION                                                                           |    |

| INTERRUPT MASKING                                                                                     |    |

| INTERRUPT STATUS                                                                                      |    |

| I2C INTERFACE                                                                                         |    |

| START/STOP TIMING                                                                                     |    |

| DATA TIMING                                                                                           |    |

| ACKNOWLEDGE (ACK)                                                                                     |    |

| DEVICE ADDRESS CONFIGURATION                                                                          |    |

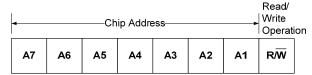

| DEVICE ADDRESS/OPERATION WORD                                                                         |    |

| REGISTER ADDRESS WORD                                                                                 |    |

| DATA WORD                                                                                             |    |

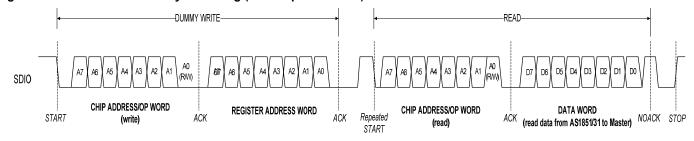

| WRITE CYCLE                                                                                           |    |

| READ CYCLE                                                                                            |    |

| POWER OVER ETHERNET OVERVIEW                                                                          |    |

| POWER OVER ETHERNET OVERVIEW POWER FEED ALTERNATIVES FOR 10/100/1000M ETHERNET SYSTEMS                |    |

| POE+: THE NEXT GENERATION                                                                             |    |

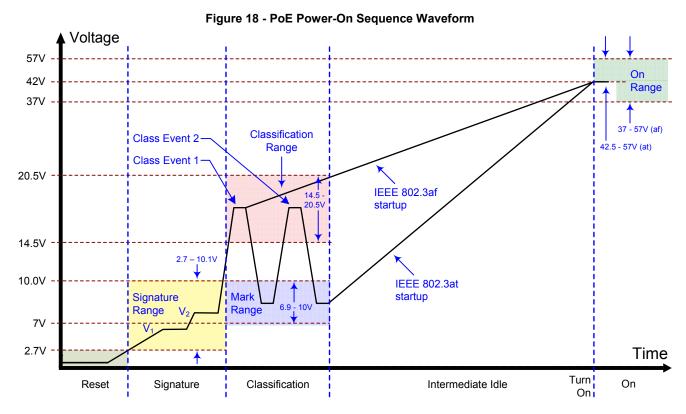

| POE POWER-ON SEQUENCE                                                                                 |    |

| PACKAGE SPECIFICATIONS                                                                                |    |

| CONTACT INFORMATION                                                                                   |    |

| IMPORTANT NOTICES                                                                                     |    |

| LEGAL NOTICE                                                                                          |    |

| REFERENCE DESIGN POLICY                                                                               |    |

| LIFE SUPPORT POLICY                                                                                   |    |

| SUBSTANCE COMPLIANCE                                                                                  |    |

| FIGURES                                                                                               |    |

| FIGURES                                                                                               |    |

| Figure 1 - AS1851A/31A Pin Assignments                                                                |    |

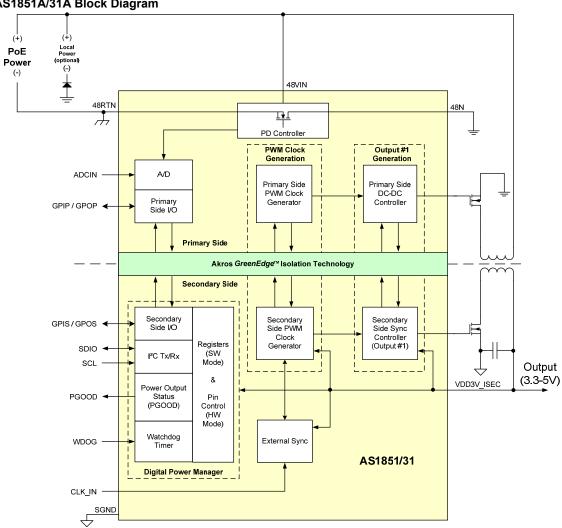

| Figure 2 - AS1851A/31A Block Diagram                                                                  |    |

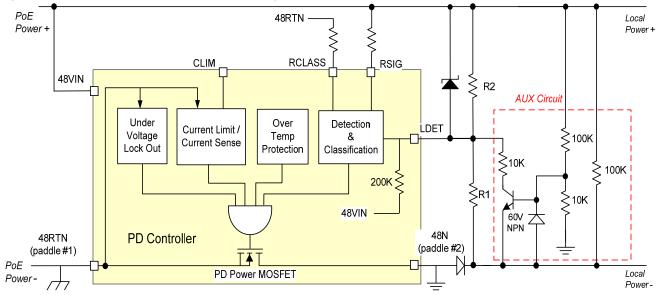

| Figure 3 - AS1851A/31A PD Controller Block Diagram                                                    |    |

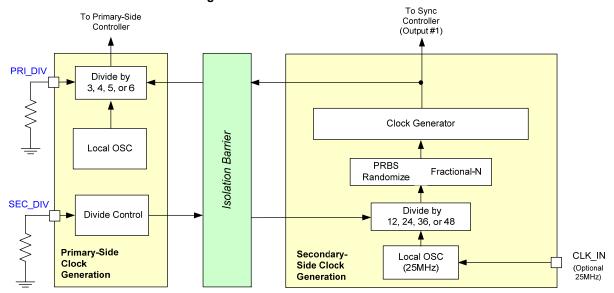

| Figure 4 - PWM Clock Generation Block Diagram                                                         |    |

| Figure 5 - Power Output Block Diagram                                                                 |    |

| Figure 6 - Hardware Mode Secondary Power-On Sequence                                                  |    |

| Figure 7 - Hardware Mode PGOOD Generation                                                             |    |

| Figure 8 - Hardware Mode GPIO Pin Mapping                                                             |    |

| Figure 9 – Software Mode Secondary Power-On Sequence                                                  |    |

| Figure 10 - Software Mode PGOOD Generation                                                            |    |

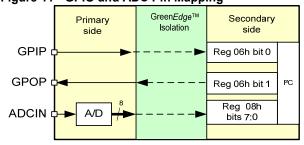

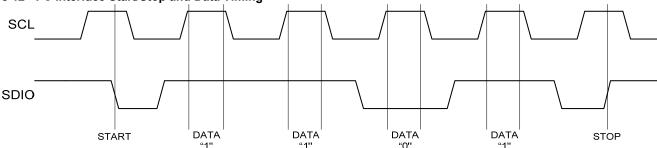

| Figure 11 - GPIO and ADC Pin MappingFigure 12 - I <sup>2</sup> C Interface Start/Stop and Data Timing | 22 |

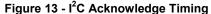

| Figure 13 - I <sup>2</sup> C Acknowledge Timing                                                       | 24 |

| Figure 14 - Device Address/Operation Word                                                             |    |

|                                                                                                       |    |

| Figure 15 - I <sup>2</sup> C Interface Write Cycle Timing                            | 26 |

|--------------------------------------------------------------------------------------|----|

| Figure 16 - I <sup>2</sup> C Interface Read Cycle Timing (with Repeated Start)       | 26 |

| Figure 17 - IEEE <sup>®</sup> Std. 802.3af Power Feeding Schemes                     | 35 |

| Figure 18 - PoE Power-On Sequence Waveform                                           |    |

| Figure 19 - Typical Isolated Synchronous Flyback Application                         |    |

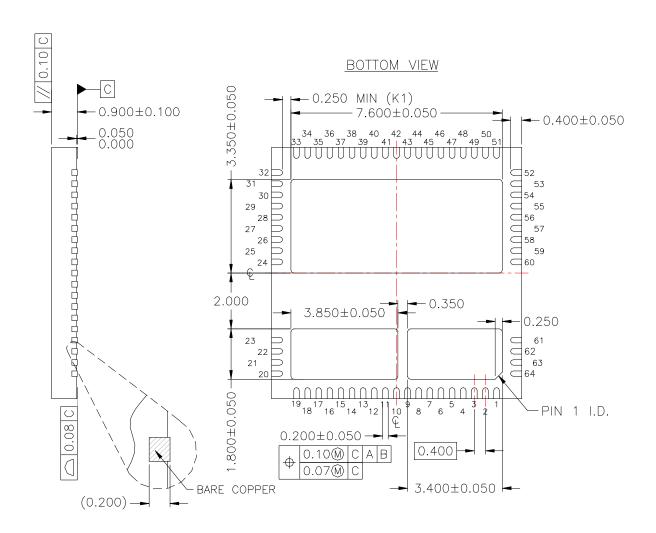

| Figure 20 - 64-Pin QFN Dimensions                                                    | 38 |

|                                                                                      |    |

| TABLES                                                                               |    |

| Table 1 - AS1851A/31A Signal Descriptions - Primary Side                             |    |

| Table 2 - AS1851A/31A Signal Descriptions - Secondary Side                           | 8  |

| Table 3 - Absolute Maximum Ratings                                                   |    |

| Table 4 - Normal Operating Conditions                                                |    |

| Table 5 - PD Section Electrical Characteristics                                      |    |

| Table 6 - Primary Side Digital, I/O, and A/D Electrical Characteristics              | 10 |

| Table 7 - Primary Side DC-DC Controller Electrical Characteristics                   |    |

| Table 8 - Secondary Side Sync Controller (Output) Electrical Characteristics         |    |

| Table 9 - Secondary Side Digital I/O and I <sup>2</sup> C Electrical Characteristics |    |

| Table 10 - Thermal Protection Electrical Characteristics                             |    |

| Table 11 - Isolation Electrical Characteristics                                      |    |

| Table 12 - Classification Map                                                        |    |

| Table 13 - AT_DET and LDET Operation                                                 | 17 |

| Table 14 - Typical LDET External Resistor Design                                     |    |

| Table 15 - PWM Clock Rate Configuration                                              |    |

| Table 16 - Sync & Overlap Delay Timing Limit                                         |    |

| Table 17 - SYNC_DLY & SYNC_OVL Resistor Calculation Example                          |    |

| Table 18 - AS1851A/31A Device Address Configuration                                  |    |

| Table 19 - AS1851A/31A Register Address Word                                         |    |

| Table 20 - AS1851A/31A Register and Bit Summary                                      |    |

| Table 21 - Alarms and Power Status (Read-Only) - 00h                                 |    |

| Table 22 - Interrupt Mask (R/W) - 01h                                                |    |

| Table 23 - Interrupt Status (Read-Only) - 02h                                        |    |

| Table 24 - PGOOD Voltage Masks (R/W) - 03h                                           |    |

| Table 25 - Watchdog Enable, Mask, Service (R/W) - 04h                                |    |

| Table 26 - PGOOD & Watchdog History (R/W) - 05h                                      | 30 |

| Table 27 - Device Control and I/O Status (R/W) - 06h                                 |    |

| Table 28 - Watchdog Timeout (R/W) - 07h                                              |    |

| Table 29 - ADCIN Voltage (Read-Only) - 08h                                           |    |

| Table 30 - ADCIN Alarm Threshold (R/W) - 09h                                         |    |

| Table 31 - PD Status and System Clock Control (R/W) - 0Ah                            |    |

| Table 32 - PD Voltage (Read-Only) - 0Bh                                              |    |

| Table 33 - PD Current (Read-Only) - 0Ch                                              |    |

| Table 34 - PD Over-Current Alarm Threshold (R/W) - 0Dh                               |    |

| Table 35 - Output Margin Control (R/W) - 0Eh                                         |    |

| Table 36 - Reserved - 0Fh                                                            |    |

| Table 37 - PoE Design Framework Summary                                              | 34 |

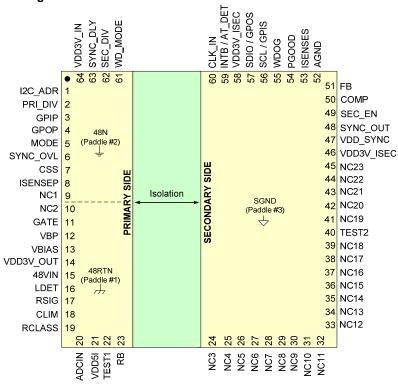

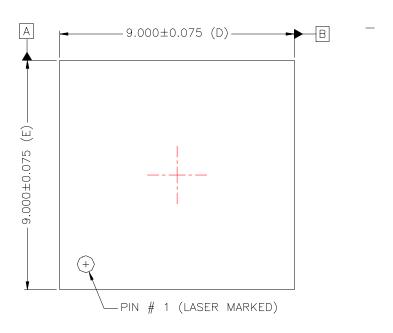

#### PIN ASSIGNMENTS AND DESCRIPTIONS

Figure 1 - AS1851A/31A Pin Assignments

Table 1 - AS1851A/31A Signal Descriptions - Primary Side

| Pin<br><b>Primary</b> - | Name<br>Side: PD Cont | roller | Description                                                                                                                                                                                                                                                                                                           |

|-------------------------|-----------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15                      | 48VIN                 | Р      | AS1851A/31A startup power input.                                                                                                                                                                                                                                                                                      |

| Paddle<br>#1            | 48RTN                 | Р      | Input power return. One of three bottom side device connections, 48RTN (Paddle #1) is connected to the internal PD Power MOSFET source. 48RTN is connected to 48N (Paddle #2) via this internal inrush current limiting power MOSFET.                                                                                 |

| Paddle<br>#2            | 48N                   | Р      | Primary-side Transformer power return. One of three bottom side device connections, 48N (Paddle #2) provides the power return for the DC-DC controller transformer primary. 48N is connected to the internal PD Power MOSFET drain. 48N is connected to 48RTN via this internal inrush current limiting power MOSFET. |

| 16                      | LDET                  | D, I   | Local Power Enable Input. Enables use of local power for the DC-DC controller and disables PD functions. When activated this disables the PoE PD signature capability that normally uses the RSIG signature resistor.                                                                                                 |

|                         |                       |        | Refer to Figure 3 for a typical LDET circuit configuration and Table 14 for resistor values. If Local power detection is not required, connect LDET to 48VIN. Note that LDET must NOT be tied to 48RTN.                                                                                                               |

|                         |                       |        | In Software mode, the LDET status can be read from the PD Status & Control Register.                                                                                                                                                                                                                                  |

| 19     | RCLASS             | Α        | PoE Classification Resistor. See Table 12 for resistor value. Connect the classification resistor between this input and the 48RTN (Paddle #1). The resistor is automatically disconnected after a valid PD classification.                                                                                         |

|--------|--------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17     | RSIG               | A, I     | PoE Signature Resistor. Connect a 26.7KΩ signature resistor from RSIG to 48VIN. This resistor is automatically disconnected after a valid PD detection.                                                                                                                                                             |

| 18     | CLIM               | I        | Sets internal PD Power MOSFET current limit in PoE operation mode; should be pulled either High (VDD5I) or Low (48RTN). In Local Mode (LDET active), CLIM is not used.  For AS1851A:  High = VDD5I = ILIM_AT (see Electrical Characteristics)  Low = 48RTN = ILIM_AF (see Electrical Characteristics)               |

|        |                    |          | For AS1831A:  Must be Low = 48RTN = ILIM_AF (see Electrical Characteristics)                                                                                                                                                                                                                                        |

| Primar | y-Side: Common     | Power P  | ins                                                                                                                                                                                                                                                                                                                 |

| 12     | VBP                | Р        | Internal bias node, decouple with an external capacitor to VBIAS.                                                                                                                                                                                                                                                   |

| 13     | VBIAS              | Р        | Bias voltage input (typically from a power transformer winding).                                                                                                                                                                                                                                                    |

| 14     | VDD3V_OUT          | Р        | Primary-side supply voltage source (3.3 volts). This supply can be used for additional external circuits on the primary side that are referenced to 48N, see Electrical Characteristics for supply limits.                                                                                                          |

| 64     | VDD3V IN           | Р        | Primary-side input supply voltage (3.3 volts) normally connected to VDD3_OUT.                                                                                                                                                                                                                                       |

| 21     | VDD5I              | Р        | Low power node that can be used to supply 48RTN referenced devices, see Electrical                                                                                                                                                                                                                                  |

|        |                    |          | Characteristics for supply limits. Must be decoupled with an external capacitor.                                                                                                                                                                                                                                    |

| 23     | RB                 | I, PU    | PD Controller state machine Power-on-Reset, connect to 48RTN with external capacitor.                                                                                                                                                                                                                               |

| Primar | y-Side: DC-DC Co   | ntroller |                                                                                                                                                                                                                                                                                                                     |

| 7      | CSS                | Α        | Primary-side PWM Soft Start input, decouple to 48N with an external capacitor.                                                                                                                                                                                                                                      |

| 11     | GATE               | Α        | Primary-side external Power FET gate drive.                                                                                                                                                                                                                                                                         |

| 8      | ISENSEP            | Α        | Current sense input, also used to set Primary PWM current limit (with external resistor).                                                                                                                                                                                                                           |

| 63     | SYNC_DLY           | Α        | Along with SYNC_OVL this signal sets Primary and Secondary-side primary sync delay timing for the Output. Connecting a resistor to ground (48N) from this input will optimize output efficiency for a given PD power level or Sync Power-FET choice. See Table 17 for resistor value selection and other details.   |

| 6      | SYNC_OVL           | Α        | Along with SYNC_DLY this signal sets Primary and Secondary-side primary sync overlap timing for the Output. Connecting a resistor to ground (48N) from this input will optimize output efficiency for a given PD power level or Sync Power-FET choice. See Table 17 for resistor value selection and other details. |

| Primar | y-Side: Clock Divi | iders    |                                                                                                                                                                                                                                                                                                                     |

| 2      | PRI_DIV            | A, I     | Primary PWM frequency divider input. Connect an external resistor (5%) from this input to ground to set the Primary PWM clock divider. Used in either internal or external (if the CLK_IN input is active) clocking operation.                                                                                      |

|        |                    |          | Note that the Primary PWM clocking rate is a function of both PRI_DIV and SEC_DIV divider ratios.                                                                                                                                                                                                                   |

| 62     | SEC_DIV            | A, I     | Secondary PWM frequency divider input. Connect an external resistor (5%) from this input to ground to set the Secondary PWM clock divider for either internal or external (if the CLK_IN input is active) PWM clocking operation.                                                                                   |

|        |                    |          | Note that the Secondary PWM clocking rate is a function of this SEC_DIV divider ratio. See                                                                                                                                                                                                                          |

|        |                    |          | PWM Clock Generation description for details.                                                                                                                                                                                                                                                                       |

|        | y-Side: Inputs & C |          |                                                                                                                                                                                                                                                                                                                     |

| 3      | GPIP               | I, PU    | General purpose digital input on primary side, referenced to 48N. See GPIO operation.                                                                                                                                                                                                                               |

| 4      | GPOP               | 0        | General purpose digital output on primary side, referenced to 48N. See GPIO operation.                                                                                                                                                                                                                              |

|        |                    |          |                                                                                                                                                                                                                                                                                                                     |

## AS1851A/31A

| 20    | ADCIN<br>I2C_ADR  | A, I<br>A, I | General purpose ADC input, referenced to 48RTN.  Sets the AS1851A/31A I <sup>2</sup> C device address. One of 8 possible Device addresses is configured by connecting a resistor on this input to ground (48N). As a result of the chosen resistor, 3 bits of available addressing for the device are configured. See Table 18 for resistor values and other details.                                                                                                                                                                                                                                    |

|-------|-------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 61    | WD_MODE           | I            | Watchdog Timer mode. Enables/disables watchdog timer and sets timer period, operation also varies with MODE input setup.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       |                   |              | For Hardware Mode Operation:  WD_MODE = Low (connect to 48N): watchdog off.  WD_MODE = Capacitor to 48N: A 1 second timeout generates a PGOOD output transition.  WD_MODE = High (connect to VDD3V_OUT): A 32 second timeout generates a PGOOD output transition.                                                                                                                                                                                                                                                                                                                                        |

|       |                   |              | For Software Mode Operation:  WD_MODE = Low (connect to 48N): watchdog off.  WD_MODE = Capacitor to 48N: Power-on enables watchdog usage and counter starts (at max count) after PGOOD indicates good power. Use the Watchdog Timeout Register to change timeout count. Watchdog servicing is via Hardware or I <sup>2</sup> C commands.  WD_MODE = High (connect to VDD3V_OUT): Power-on enables watchdog usage but waits for software to enable before starting. Use Watchdog Timeout Register for timeout length (reset to max). Watchdog servicing is via Hardware pin or I <sup>2</sup> C commands. |

| 5     | MODE              | 1            | The MODE pin selects the device operation mode at power-on.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       |                   |              | For Hardware Mode Operation:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|       |                   |              | <ul> <li>Mode 1 = Reset mode</li> <li>Mode 1 is selected by holding the MODE pin Low (MODE to 48N).</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       |                   |              | <ul> <li>Mode 2 = HW Operating Mode</li> <li>Mode 2 is selected with a pull-up resistor (17.8KΩ max) from MODE to VDD3V_OUT plus a required power-on reset capacitor from MODE to 48N.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                        |

|       |                   |              | For Software Mode Operation:  - Mode 1 = Reset mode  - Mode 1 is selected by helding the MODE pin Law (MODE to 19N)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|       |                   |              | <ul> <li>Mode 1 is selected by holding the MODE pin Low (MODE to 48N).</li> <li>Mode 2 = SW Operating Mode with I<sup>2</sup>C device address per I2C_ADR pin setting</li> <li>Mode 2 is selected with a required power-on reset capacitor from MODE to 48N.</li> </ul>                                                                                                                                                                                                                                                                                                                                  |

|       | Side: Miscellaneo | us           | M (1) (1) (1) (1) (1) (1) (1) (1) (1) (1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 9, 10 | TEST1<br>NC1, NC2 |              | Must be pulled down to 48RTN with a resistor $(4.7K\Omega-100K\Omega)$ .<br>No User Connection. Must be floated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ə, IU | NOT, NOZ          |              | NO OSEI COMBECTION. MUST DE MORTEU.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

$^1$  I = Input, O = Output, I/O = Bidirectional, PU = Internal pull-up, PD = Internal pull-down, P = Power, A = Analog, D = Digital, OD = Open drain

| <b>Fable 2 - <i>F</i></b><br>Pin                            | AS1851A/31A Signa<br>Name                   | al Descript<br>I/O¹ | tions - Secondary Side Description                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

|-------------------------------------------------------------|---------------------------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|                                                             | ry-Side: Common                             |                     |                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| 46, 58                                                      | VDD3V_ISEC                                  | Р                   | Secondary-side 3.3V power inputs. Sourced from Vout (if Vout=3.3V), or other external supply.                                                                                                                                                                                                              |  |  |  |  |  |  |

| Paddle<br>#3                                                | SGND                                        | Р                   | Secondary-side ground connection. One of three bottom side device connections, SGND (Paddle #3) is the Secondary-side ground connection.                                                                                                                                                                   |  |  |  |  |  |  |

| Secondary-Side: Synchronous Rectification Controller (Vout) |                                             |                     |                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| 47                                                          | VDD_SYNC                                    | Α                   | Sync FET power decoupling node. Decouple with an external capacitor, VDD_SYNC to SGND. This node is nominally 5V.                                                                                                                                                                                          |  |  |  |  |  |  |

| 51                                                          | FB                                          | A                   | Controller voltage feedback input.                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| 53                                                          | ISENSES                                     | A                   | Controller secondary-side sync switches node current sense. Sensed signal is used to control the external secondary-side power FET, making it an efficient power diode.                                                                                                                                    |  |  |  |  |  |  |

| 50                                                          | COMP                                        | A                   | Controller compensation network connection.                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| 48                                                          | SYNC_OUT                                    | A                   | Controller sync gate drive output. Used for secondary-side synchronization in conjunction with the primary-side controller.                                                                                                                                                                                |  |  |  |  |  |  |

| 52                                                          | AGND                                        | Р                   | Controller secondary-side sense ground, used for both differential feedback and differential current sensing. Should be routed differentially, as the pairs of FB & AGND and ISENSES & AGND.                                                                                                               |  |  |  |  |  |  |

| Seconda                                                     | ry-Side: I <sup>2</sup> C Interfa           | ce (or I/O i        | in Hardware Mode)                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| 57                                                          | SDIO / GPOS                                 | ÓD                  | SDIO in Software mode, used for I <sup>2</sup> C bi-directional data input/output. GPOS in Hardware mode, this output reflects the GPIP pin state (from the primary side).                                                                                                                                 |  |  |  |  |  |  |

| 56                                                          | SCL / GPIS                                  | 1/1                 | SCL in Software mode, used as the I <sup>2</sup> C clock input. GPIS in Hardware mode is an input that drives the GPOP pin state (on the primary-side).                                                                                                                                                    |  |  |  |  |  |  |

| 59                                                          | INTB / AT_DET                               | OD                  | INTB in Software Mode. The I <sup>2</sup> C interface interrupts output, active low. The open drain output allows user defined voltage output high level.                                                                                                                                                  |  |  |  |  |  |  |

|                                                             |                                             |                     | AT_DET in Hardware Mode. It is the PoE+ (802.3at) PSE detect indication output. A High level output indicates connection to either a Type 2 PSE or to a Local Power supply. The output is open drain, active High. If a Type 1 PSE is connected, the output of AT_DET remains in the inactive state (Low). |  |  |  |  |  |  |

| Seconda                                                     | ry Side: Inputs & C                         | Outputs             |                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| 60                                                          | CLK_IN                                      | İ, PU               | DC coupled optional clock input for timing of Primary and Secondary DC-DC regulators & controllers if synchronizing to an external time source is desired. Nominally sourced from the local Ethernet master clock.                                                                                         |  |  |  |  |  |  |

| 54                                                          | PGOOD                                       | OD                  | Logical "AND" of global power good & watchdog status.                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

|                                                             |                                             |                     | High = All enabled voltages (#1 with any or all of #2, #3, and #4) are within voltage spec and there is presently no watchdog timeout. Low = one or more of enabled voltages out of spec, or, the watchdog has timed out.                                                                                  |  |  |  |  |  |  |

|                                                             |                                             |                     | Note that PGOOD operation is different for Hardware and Software modes of operation (selected by the MODE input). For Hardware mode PGOOD operation details see HW Mode Power Monitoring (PGOOD). For Software mode PGOOD operation details see SW Mode Power Status Monitoring (PGOOD).                   |  |  |  |  |  |  |

| 55                                                          | WDOG                                        | I                   | Watchdog timer input, used for hardware reset of the watchdog timer (if enabled). Serviced with a transition of either polarity.                                                                                                                                                                           |  |  |  |  |  |  |

| Seconda                                                     | ry Side: Miscellane                         |                     |                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| 49                                                          | SEC_EN                                      | I, PU               | Secondary-side Enable. A capacitor on this input to SGND is required.                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| 40                                                          | TEST2                                       |                     | Must be pulled down to SGND with a resistor (100K $\Omega$ ).                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| Pins 24-<br>39, 41-<br>45                                   | NC3-NC18,<br>NC19-23                        |                     | No User Connection. Must be floated.                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

|                                                             | O = Output, I/O = Bg, $D = Digital, OD = B$ |                     | PU = Internal pull-up, PD = Internal pull-down, P = Power,                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| TEST SPECIFICATIONS                                                                            |                                    |      |

|------------------------------------------------------------------------------------------------|------------------------------------|------|

| Table 3 - Absolute Maximum Ratings                                                             |                                    |      |

| Parameter                                                                                      | Max                                | Unit |

| 48VIN, 48N, RSIG: to 48RTN                                                                     | 100 1                              | V    |

| 48VIN: to 48N                                                                                  | 100 1                              | V    |

| 48VIN, 48N, RSIG: to 48RTN (under steady-state conditions)                                     | 60 <sup>2</sup>                    | V    |

| 48VIN: to 48N (under steady-state conditions)                                                  | 60 <sup>2</sup>                    | V    |

| GATE, VBIAS, VBP: to 48N                                                                       | 20                                 | V    |

| LDET: to 48VIN                                                                                 | no more than 6V less<br>than 48VIN | V    |

| RCLASS, CLIM, RB, VDD5I: to 48RTN                                                              | 6                                  | V    |

| ADCIN to 48RTN                                                                                 | 4                                  | V    |

| VDD3V_OUT, VDD3V_IN: to 48N                                                                    | 4                                  | V    |

| ISENSEP, CSS, SYNC_DLY, SYNC_OVL, MODE, GPIP, GPOP, PRI_DIV, I2C_ADR, SEC_DIV, WD_MODE: to 48N | 4                                  | V    |

| VBOOST: to SGND                                                                                | 12                                 | V    |

| CLK_IN, ISENSES, SEC_EN, COMP, AGND, PGOOD, VDD3V_ISEC: to SGND                                | 4                                  | V    |

| FB, VDD_SYNC, SYNC_OUT, INTB/AT_DET, SCL/GPIS, SDIO/GPOS, WDOG: to SGND                        | 6                                  | V    |

| ESD Rating, Human body model (per JESD22-A114)                                                 | 2                                  | kV   |

| ESD charged device model                                                                       | 500                                | V    |

| ESD machine model                                                                              | 200                                | V    |

| ESD System level (contact/air) at RJ-45 (per IEC61000-4-2)                                     | 8/15                               | kV   |

| Storage Temperature                                                                            | 165                                | °C   |

| Operating Junction Temperature                                                                 | 125                                | °C   |

<sup>&</sup>lt;sup>1</sup> The AS1851A/31A has a fast internal surge clamp for transient conditions such as system startup and other noise conditions; the device must not be exposed to sustained over-voltage condition at this level.

Unless otherwise noted all Test Specifications apply over the full -40°C to 85°C operating temperature range.

#### **Table 4 - Normal Operating Conditions**

| Parameter                                                     | Min  | Typ <sup>1</sup> | Max | Unit | Conditions                                                 |

|---------------------------------------------------------------|------|------------------|-----|------|------------------------------------------------------------|

| VIN_AF                                                        | 37   | 48               | 57  | V    | Measured at the Network Interface                          |

| VIN_AT                                                        | 42.5 | 48               | 57  | V    | Measured at the Network Interface                          |

| VAUX (optional local power)                                   | 9.5  |                  | 57  | V    | Measured at 48VIN for full VLDET range (referenced to 48N) |

| Thermal Resistance, Junction to Case, $\theta_{\text{JC}}$    |      | 5                |     | °C/W | Operating Junction Temperature 125°C, max                  |

| Thermal Resistance, Junction to Ambient, $\theta_{\text{JA}}$ |      | 20               |     | °C/W | Operating Junction Temperature 125°C, max                  |

| Operating temperature range                                   | -40  |                  | 85  | °C   |                                                            |

<sup>&</sup>lt;sup>1</sup> Typical specification not 100% tested. Performance guaranteed by design and/or other correlation methods.

<sup>&</sup>lt;sup>2</sup> Under steady state conditions; higher voltage level is acceptable under transient conditions.

| Table 5 - PD Sec | tion Electrical Characteristics                          |      |      |      |      |                                                                                                                           |

|------------------|----------------------------------------------------------|------|------|------|------|---------------------------------------------------------------------------------------------------------------------------|

| Symbol           | Parameter                                                | Min  | Typ¹ | Max  | Unit | Conditions <sup>2</sup>                                                                                                   |

| IINRUSH_AF       | Inrush current limit - AF PD                             |      | 120  |      | mΑ   | 13W                                                                                                                       |

| IINRUSH_AT       | Inrush current limit - AT PD                             |      | 240  |      | mΑ   | 30W                                                                                                                       |

| ILIM_AF          | PoE current limit - AF PD                                | 350  | 400  | 500  | mΑ   | 13W, CLIM = 48RTN                                                                                                         |

| ILIM_AT          | PoE current limit - AT PD                                | 720  | 750  | 1000 | mΑ   | 30W, CLIM = VDD5I                                                                                                         |

| RDS_ON           | PD Power MOSFET Switch on Resistance                     |      | 0.5  | 0.9  | Ω    | As measured between 48RTN and 48N with source of 48V and 200ma current.                                                   |

| VRESET_MIN       | Minimum reset voltage level                              |      |      | 2.81 | V    | Measured at the Network Interface <sup>2</sup> .                                                                          |

| VSIGMIN          | Minimum Signature voltage                                |      |      | 2.7  | V    | Measured at the Network Interface <sup>2</sup> .                                                                          |

| VSIGMAX          | Maximum Signature voltage                                | 10.1 |      |      | V    | Measured at the Network Interface <sup>2</sup> .                                                                          |

| VCLASSMIN        | Minimum Classification voltage                           |      |      | 14.5 | V    | In classification, the AS1851A/31A sinks current as defined in Table 12, measured at the Network Interface <sup>2</sup> . |

| VCLASSMAX        | Maximum Classification voltage                           | 20.5 |      |      | V    | In classification, the AS1851A/31A sinks current as defined in Table 12, measured at the Network Interface <sup>2</sup> . |

| VMARKMIN         | Min Mark Event voltage                                   |      | 5.2  | 6.90 | V    | Measured at the Network Interface <sup>2</sup> .                                                                          |

| VMARKMAX         | Max Mark Event voltage                                   | 10   |      |      | V    | Measured at the Network Interface <sup>2</sup> .                                                                          |

| IMARK            | Mark Event current                                       | 0.5  | 2.1  | 4    | mΑ   | Measured at the Network Interface <sup>2</sup> .                                                                          |

| VCLASSRSET       | Classification Reset threshold                           | 2.81 | 5.2  | 6.90 | V    | Measured at the Network Interface <sup>2</sup> .                                                                          |

| VACT             | Full power activation UVLO threshold, voltage rising     |      | 37   | 42   | V    | Measured at the Network Interface <sup>2</sup> .                                                                          |

| VDEACT           | Full power de-activation UVLO threshold, voltage falling | 30   |      |      | V    | Measured at the Network Interface <sup>2</sup> .                                                                          |

<sup>&</sup>lt;sup>1</sup> Typical values at: Ta = 25°C, Vin = 48VDC. Typical specifications not 100% tested. Performance guaranteed by design and/or other correlation methods.

Table 6 - Primary Side Digital, I/O, and A/D Electrical Characteristics

| Symbol     | Parameter                                           | Min | Typ <sup>1</sup> | Max             | Unit | Conditions                                                                                                |

|------------|-----------------------------------------------------|-----|------------------|-----------------|------|-----------------------------------------------------------------------------------------------------------|

| VDD3V_OUT  | Voltage from internally generated 3V source.        | 3.0 | 3.3              | 3               | V    | Decouple VDD3V_OUT with 4.7µF cap. Referenced to 48N.                                                     |

| IVDD3V_OUT | Current output from internally generated 3V source. |     |                  | 5               | mA   | Decouple VDD3V_OUT with 4.7µF cap. Referenced to 48N.                                                     |

| VDD3V_IN   | 3V primary side voltage inputs.                     | 3.0 | 3.3              | 3               | V    | Supplied by VDD3_OUT, Referenced to 48N.                                                                  |

| VDD5I      | Voltage from internally generated 5V node.          | 4.0 | 5                | 6.0             | V    | Decouple with 1.5µF cap, referenced to 48RTN.                                                             |

| IVDD5I     | Current output from internally generated 5V node.   |     |                  | 5               | mA   | Decouple with 1.5µF cap, referenced to 48RTN.                                                             |

| VHGPOP     | GPOP voltage output – high                          | 3.0 |                  |                 | V    | Current at GPOP = 1.0 mA (VDD3V_IN=3.3V, referenced to 48N).                                              |

| VLGPOP     | GPOP voltage output – low                           |     |                  | 0.4             | V    | Current at GPOP = -1.0 mA (VDD3V_IN=3.3V, referenced to 48N).                                             |

| VHGPIP     | GPIP voltage input - high                           | 2.0 |                  |                 | V    | (VDD3V_IN=3.3V, referenced to 48N).                                                                       |

| VLGPIP     | GPIP voltage input - low                            |     |                  | 8.0             | V    | (VDD3V_IN=3.3V, referenced to 48N).                                                                       |

| TGPIO      | Primary side GPIO pin latency to register update.   |     |                  | 10 <sup>2</sup> | ms   | Independent of I <sup>2</sup> C clock speed. Pin I/O is automatic to and from I <sup>2</sup> C registers. |

| TADCIN     | ADCIN pin latency to register update.               |     |                  | 10 <sup>2</sup> | ms   | Independent of I <sup>2</sup> C clock speed. Pin I/O is automatic to and from I <sup>2</sup> C registers. |

| VADCIN     | ADCIN voltage range                                 | 0   |                  | 2.5             | V    | Referenced to 48RTN.                                                                                      |

<sup>&</sup>lt;sup>2</sup> All measurements at the Network Interface are before the PD diodes (assuming a 1.2V drop across the PD diodes).

| RADCIN   | ADCIN resolution             | 8                | bits | Referenced to 48RTN. |

|----------|------------------------------|------------------|------|----------------------|

| ADCERROR | ADCIN total unadjusted error | $\pm TBD^3$      | LSB  | Referenced to 48RTN. |

| ILADCIN  | ADCIN input leakage current  | 100 <sup>2</sup> | nΑ   | Referenced to 48RTN. |

| CADCIN   | ADCIN input capacitance      | $0.3^{2}$        | pF   | Referenced to 48RTN. |

<sup>&</sup>lt;sup>1</sup> Typical values at: Ta = 25°C, Vin = 48VDC. Typical specifications not 100% tested. Performance guaranteed by design and/or other correlation

Table 7 - Primary Side DC-DC Controller Electrical Characteristics

| Table 7 - Primary Side DC-DC Controller Electrical Characteristics |                                                          |                 |                  |                 |      |                                                                         |  |  |

|--------------------------------------------------------------------|----------------------------------------------------------|-----------------|------------------|-----------------|------|-------------------------------------------------------------------------|--|--|

| Symbol                                                             | Parameter                                                | Min             | Typ <sup>1</sup> | Max             | Unit | Conditions                                                              |  |  |

| VIN_AF                                                             | Type 1 PD input voltage                                  | 37              | 48               | 57              | V    | Measured at the Network Interface                                       |  |  |

| VIN_AT                                                             | Type 2 PD input voltage                                  | 42.5            | 48               | 57              | V    | Measured at the Network Interface                                       |  |  |

| VAUX                                                               | Input Voltage, Local Power Mode                          | 9.5             |                  | 57              | V    | Measured at 48VIN (referenced to 48N) over full VLDET range             |  |  |

| VLDET_ON                                                           | Local input voltage threshold for Local Power Mode - ON  | 48VIN<br>-2.4V  |                  |                 | V    | See Table 3 for Absolute Maximum Rating for LDET (referenced to 48VIN). |  |  |

| VLDET_OFF                                                          | Local input voltage threshold for Local Power Mode - OFF | _               |                  | 48VIN<br>-1.2V  | V    |                                                                         |  |  |

| VBIAS                                                              | External bias source voltage                             | 8 <sup>2</sup>  |                  | 14 <sup>2</sup> | V    | Sets VOH of GATE.                                                       |  |  |

| FPWM1L                                                             | Low end of Primary PWM switching frequency range         |                 | 104              |                 | KHz  | Set by external resistors on PRI_DIV and SEC_DIV pins see Table 15.     |  |  |

| FPWM1H                                                             | High end of Primary PWM switching frequency range        |                 | 512              |                 | KHz  | Set by external resistors on PRI_DIV and SEC_DIV pins see Table 15.     |  |  |

| FOSC1                                                              | PWM1 clock frequency accuracy                            | -20             |                  | +20             | %    | See Table 15 for frequency.                                             |  |  |

| FPWM1T                                                             | PWM switching frequency temperature coefficient          |                 | 0.12             |                 | %/C° | Refer to Table 15 for PWM Frequency.                                    |  |  |

| RH_GATE                                                            | GATE drive impedance                                     |                 | 6                |                 | Ω    | High side output drive resistance, Source.                              |  |  |

| RL_GATE                                                            | GATE drive impedance                                     |                 | 6                |                 | Ω    | Low side output drive resistance, Sink.                                 |  |  |

| VPK1P                                                              | Peak current sense threshold voltage at ISENSEP          |                 | 395              |                 | mV   | lpeak = VPK1P / RISENSEP.                                               |  |  |

| DMAX1                                                              | Primary PWM Maximum duty cycle                           | 80 <sup>3</sup> |                  |                 | %    |                                                                         |  |  |

| DMIN1                                                              | Primary PWM Minimum duty cycle                           |                 |                  | 10 <sup>3</sup> | %    |                                                                         |  |  |

<sup>&</sup>lt;sup>1</sup> Typical values at: Ta = 25°C, Vin = 48VDC. Typical specifications not 100% tested. Performance guaranteed by design and/or other correlation methods.

Table 8 - Secondary Side Sync Controller (Output) Flectrical Characteristics

| Symbol    | Parameter                                     | Min  | Typ <sup>1</sup> | Max            | Unit | Conditions                   |

|-----------|-----------------------------------------------|------|------------------|----------------|------|------------------------------|

| VSYNC_OUT | SYNC_OUT voltage                              | 4.5  | 5                | 6              | V    |                              |

| RH_SYNC   | SYNC_OUT<br>Source Impedance<br>VDD_SYNC = 5V |      |                  | 2.5            | Ω    | Source                       |

| RL_SYNC   | SYNC_OUT Source Impedance VDD_SYNC = 5V       |      |                  | 2.5            | Ω    | Sink                         |

| VMR       | Output voltage margining range                |      | ±5               |                | %    | Software mode, see Table 35. |

| VREF      | FB voltage reference                          | 0.98 | 1.0              | 1.02           | V    |                              |

| ILEA      | Error amp leakage                             |      |                  | 1 <sup>2</sup> | μΑ   |                              |

| Gm        | Feedback Transconductance (Siemens)           | 150  | 225              | 350            | μS   |                              |

<sup>&</sup>lt;sup>1</sup> Typical values at: Ta = 25°C, Vin = 48VDC. Typical specifications not 100% tested. Performance guaranteed by design and/or other correlation methods.

<sup>&</sup>lt;sup>2</sup> Guaranteed by design. Not tested in production. <sup>3</sup> Includes offset, full-scale, and linearity.

Guaranteed by characterization. Not tested in production.

<sup>&</sup>lt;sup>3</sup> Guaranteed by design. Not tested in production.

Guaranteed by design. Not tested in production

| Table 9 - Secondary Side Digital I/O and I <sup>2</sup> C Electrical Characteristics |                                                               |                  |      |                 |      |                                                                                      |  |

|--------------------------------------------------------------------------------------|---------------------------------------------------------------|------------------|------|-----------------|------|--------------------------------------------------------------------------------------|--|

| Symbol                                                                               | Parameter                                                     | Min              | Typ¹ | Max             | Unit | Conditions                                                                           |  |

| VDD3V_ISEC                                                                           | Secondary Side Power Supply Input Voltage                     | 3.0              | 3.3  | 3               | V    | Sourced from Vout (if 3.3V) or other external supply                                 |  |

| FCLK_IN                                                                              | External Clock Input<br>Frequency                             | 23.75            | 25   | 26.25           | MHz  | ,                                                                                    |  |

| VCLK_IN_HI                                                                           | CLK_IN input voltage<br>threshold - high                      | 2.0              |      |                 | V    |                                                                                      |  |

| VCLK_IN_LOW                                                                          | CLK_IN input voltage threshold - low                          |                  |      | 0.8             | V    |                                                                                      |  |

| IOINTB                                                                               | INTB/AT_DET open drain current drive                          | 1                |      |                 | mA   | With $V_{PULL-UP}$ = TBD and $R_{PULL-UP}$ = TBDK $\Omega$ , $V_{INTB}$ (typ) = TBD  |  |

| IOPG                                                                                 | PGOOD open drain current drive                                | 1                |      |                 | mA   | With $V_{PULL-UP}$ = TBD and $R_{PULL-UP}$ = TBDK $\Omega$ , $V_{PGOOD}$ (typ) = TBD |  |

| TPGOOD                                                                               | PGOOD minimum pulse output (High-Low-High)                    | 10 <sup>2</sup>  |      |                 | ms   | , , , , , , , , , , , , , , , , , , ,                                                |  |

| TWDOG                                                                                | Watchdog minimum reset pulse width (WDOG pin)                 | 100 <sup>2</sup> |      |                 | ns   |                                                                                      |  |

| VHGPOS                                                                               | GPOS voltage output – high (referenced to SGND)               | 3.0              |      |                 | V    | Current at GPOS = 1.0 mA<br>(VDD3V_ISEC=3.3V, referenced to<br>SGND)                 |  |

| VLGPOS                                                                               | GPOS voltage output – low (referenced to SGND)                |                  |      | 0.4             | V    | Current at GPOS = -1.0 mA<br>(VDD3V_ISEC=3.3V, referenced to<br>SGND)                |  |

| VHGPIS                                                                               | GPIS voltage input – high (referenced to SGND)                | 2.0              |      |                 | V    | (referenced to SGND)                                                                 |  |

| VLGPIS                                                                               | GPIS voltage input – low (referenced to SGND)                 |                  |      | 8.0             | V    | (referenced to SGND)                                                                 |  |

| FSCL                                                                                 | I <sup>2</sup> C Clock Frequency                              | 10               |      | 400             | KHz  | 5V tolerant input                                                                    |  |

| VIH                                                                                  | I <sup>2</sup> C HIGH level input voltage                     | 1.4              |      |                 | V    | 5V tolerant input                                                                    |  |