# **AS3955**

# **NFC Forum Compliant Dynamic Tag**

# **General Description**

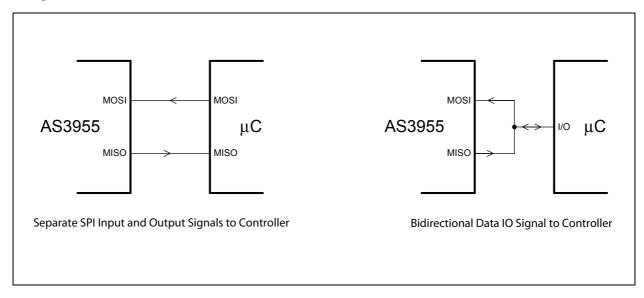

AS3955 NFC Dynamic Tag IC is the ultimate solution to easily add NFC functionality to electronic devices. Thanks to a high sensitivity ISO14443A frontend and high integrated resonance capacitor, AS3955 offers standalone NFC passive tag functionality in a small footprint. Fast system integration and high speed data transfer are guaranteed by the available SPI and I<sup>2</sup>C interfaces and by the optimized protocols (Tunneling Mode and Extended Mode), allowing bidirectional communication between the device microcontroller and an external NFC compliant device or ISO14443A reader device (PCD).

AS3955 is able to operate fully powered by the RF field, without any external supply. This, combined with an advanced energy harvesting feature, greatly increases battery life time or even allows battery-less designs.

AS3955 is used with an appropriate antenna coil connected to the terminals LC1 and LC2, and behaves as a standard passive ISO 14443A tag (PICC). After the anti-collision protocol stage, based on configuration, AS3955 can operate as a standalone NFC Forum Type 2 Tag or, when tunneling mode is activated, as a bridge between the PCD and the microcontroller, e.g. to emulate a custom or standard ISO14443A Level 3 or Level 4 PICC or a NFC Forum tag. A configurable wake-up signal notifies the microcontroller on ongoing RF activities, in order to minimize overall power consumption.

AS3955 includes an embedded EEPROM memory that can be accessed from the PCD through the RF link or from the microcontroller through the SPI or I<sup>2</sup>C interfaces. Part or all memory can be protected by a 32-bit password, or permanently locked.

AS3955 supports ISO 14443A up to Level 4 and is designed according to EMVCo requirements, to enable the emulation of contactless smart cards or NFC Forum compliant Type 2 or Type 4 Tags.

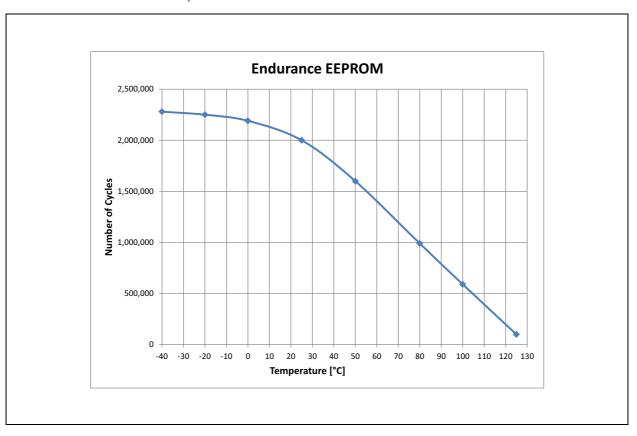

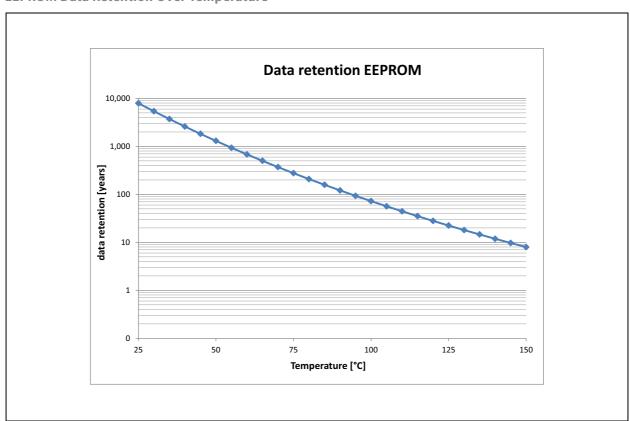

AS3955 is designed for high reliability, and can operate in a wide power supply range from 1.65V to 5.5V, in a wide temperature range from -40 °C to 125 °C. EEPROM memory reaches automotive grade quality with endurance of 100,000 cycles and data retention of 10 years at 125 °C.

Ordering Information and Content Guide appear at end of datasheet.

# **Key Benefits & Features**

The benefits and features of AS3955, NFC Forum compliant Dynamic Tag are listed below:

Figure 1: Added Value of Using AS3955

| Benefits                                                                                                | Features                                                                                                           |

|---------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| NFC Forum compliance for full interoperability                                                          | <ul><li>Type 2 Tag standalone functionality</li><li>Type 4 Tag emulation with external MCU</li></ul>               |

| <ul><li>NFC Forum compliance</li><li>ISO 14443A compliance up to Level 4</li></ul>                      | <ul> <li>Operating frequency at 13.56 MHz</li> <li>Bit rate at 106 kbps</li> <li>7-byte UID</li> </ul>             |

| Choice of memory size based on application                                                              | <ul> <li>2 kbit EEPROM (216 bytes of user data) or</li> <li>4 kbit EEPROM (472 bytes of user data)</li> </ul>      |

| Allows zero-power standby                                                                               | Configurable passive wake-up interrupt                                                                             |

| Enables long battery life time, or battery-less designs                                                 | Energy harvesting to supply up to 5mA @ 4.5V (regulated)                                                           |

| Allows fast antenna prototyping (ISO antenna classes 1 to 6)                                            | 45 pF integrated resonant capacitor                                                                                |

| Design flexibility, easy integration. Fits<br>requirements for various embedded applications            | <ul> <li>3/4-wire SPI slave interface up to 5 Mbps</li> <li>I<sup>2</sup>C slave interface up to 1 Mbps</li> </ul> |

| Design flexibility, easy integration                                                                    | Programmable I <sup>2</sup> C address                                                                              |

| Fits supply requirements for various applications, including industrial                                 | Wide interface supply range (1.65V to 5.5V)                                                                        |

| Support for multiple applications, and storage of sensitive data                                        | 32-bit password memory protection                                                                                  |

| High performance and robust data<br>communication, allows custom protocols to be<br>implemented         | Tunneling and Extended modes for MCU communication                                                                 |

| Consistent NFC behavior of battery supplied devices in e.g. pairing applications                        | Silent mode (MCU power status detection),<br>configurable between 1.42V and 3.65V                                  |

| Possibility to disable RF communication                                                                 | Configurable Chip Kill mode                                                                                        |

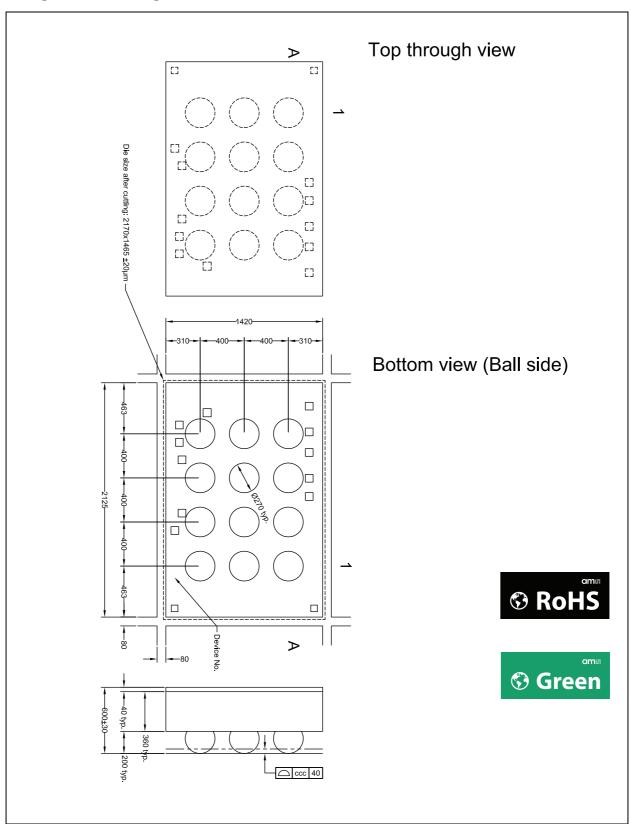

| Small outline, compatibility to common inlay and<br>card manufacturing lines, surface-mount<br>assembly | <ul><li>Sawn wafer</li><li>WL-CSP package</li><li>10-pin MLPD 3x3mm package</li></ul>                              |

Page 2ams DatasheetDocument Feedback[v1-01] 2015-Apr-29

# **Applications**

AS3955 is suited to a wide range of applications, including

- NFC connection handover (Bluetooth™, Bluetooth Low Energy, Wi-Fi pairing)

- Equipment setup, service and configuration

- Firmware upgrades

- · Activity and status logging

- Wireless authentication (e.g. access control to buildings and equipment)

#### **Typical Markets:**

- EMV payment cards

- Consumer electronics, wearables and smart clothing

- · Home appliances

- Automotive

- Industrial equipment and building automation

- · Remote sensing

- Gaming

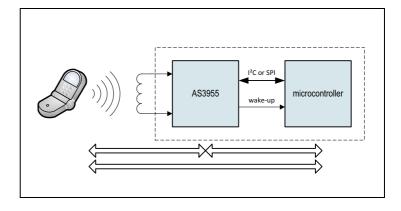

A typical system diagram is depicted in Figure 2.

At the presence of a 13.56 MHz field generated by a NFC device, AS3955 powers up, notifies the microcontroller through a wake-up signal and handles the tag activation sequence. Depending on configuration, several operations are then possible:

- AS3955 exchanges with the NFC device NDEF data stored in the internal EEPROM

- The microcontroller exchanges with the NFC device NDEF data stored in external memory

- The microcontroller exchanges data with AS3955. This

operation can be performed concurrently with

communication over the RF link, or also in absence of RF

power, in presence of an external supply.

Figure 2: Typical System Diagram

ams Datasheet Page 3

[v1-01] 2015-Apr-29 Document Feedback

This built-in flexibility makes it ideal for a number of applications requiring non-volatile memory to be accessed when the system is not powered, e.g.:

- personalization data is programmed by the NFC device (even in case SPI / I<sup>2</sup>C is not powered) and it is later read by microcontroller through SPI / I<sup>2</sup>C interface

- Log data is stored periodically by the microcontroller and can then be read by the NFC device even when the microcontroller is not powered

- A NDEF message is regularly modified by the microcontroller (e.g. Bluetooth pin code, or Wi-Fi key, or dynamic URL) and it is later read by a NFC device.

# **Block Diagram**

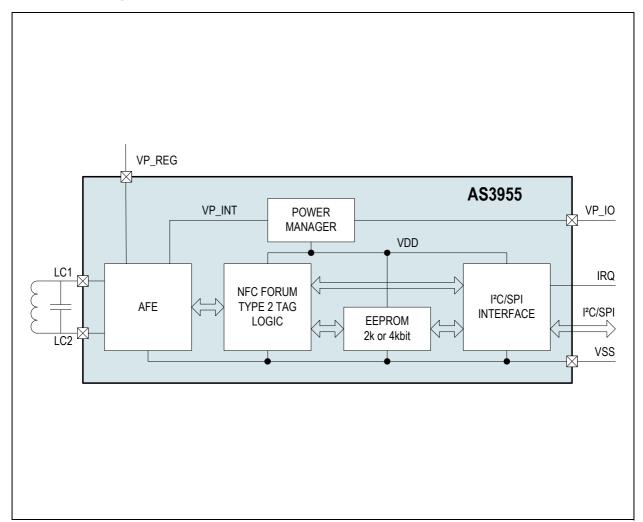

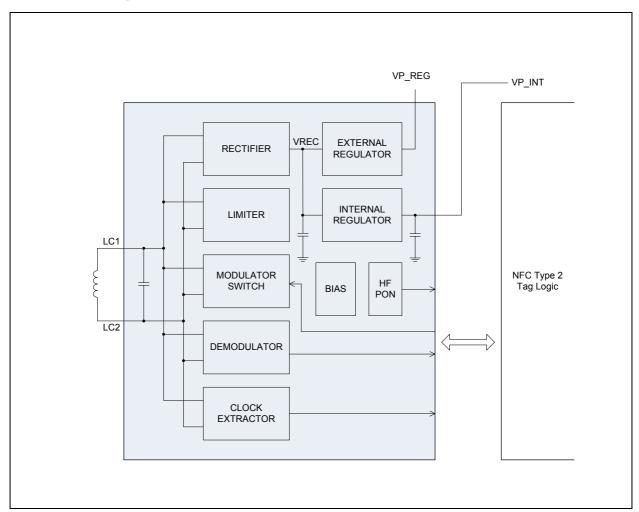

The functional blocks of this device for reference are shown below:

Figure 3: AS3955 Block Diagram

Page 4ams DatasheetDocument Feedback[v1-01] 2015-Apr-29

AS3955 is composed of NFC-A Analog Front End (AFE), NFC Type 2 Tag Logic, EEPROM, SPI / I<sup>2</sup>C Interface and Power Supply Manager Block (Power Manager).

The AFE is connected to an external tag coil which forms, together with integrated resonant capacitor, a LC tank resonating with the external electromagnetic field frequency of 13.56 MHz. The AFE has built-in rectifier and regulators. The output of the internal regulator (VP\_INT) is used to supply the AFE and also the Logic and EEPROM (through Power Supply Manager). A regulator output VP\_REG is available on a pin to supply external circuitry by harvesting energy from the RF field.

The Power Manager is controlling the power supply of Logic and EEPROM. The two blocks can be supplied either from VP\_INT or from VP\_IO (SPI / I<sup>2</sup>C power supply) depending on the power mode of the chip. AS3955 offers a power mode where VP\_IO supply is switched to VP\_INT whenever the RF field is present. VP IO is typically used when some activity is started over the SPI / I<sup>2</sup>C and the VP\_INT is too low to be used as a power supply.

The Logic is responsible for handling the anti-collision sequence, when acting as NFC Type 2 Tag, and other data transfer. The interface logic contains also a 32-byte buffer for block transmission between NFC device and AS3955.

The EEPROM is used to store the UID, configuration and control bits, and user data which can be accessed also via the SPI / I<sup>2</sup>C.

ams Datasheet Page 5 **Document Feedback**

# **Pin Assignments**

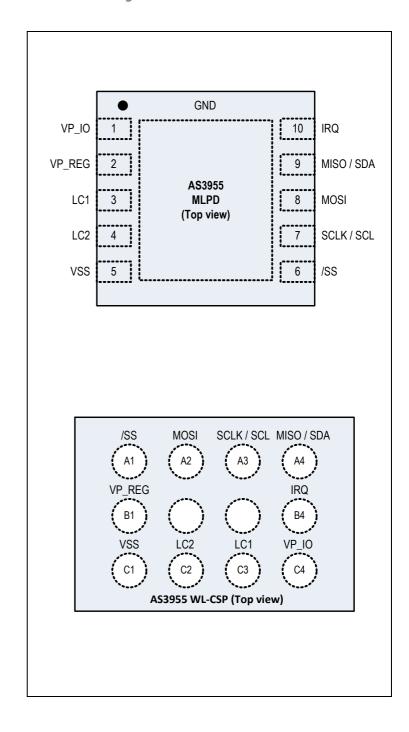

Figure 4: AS3955 Pin Assignment

# **Pin Description**

Figure 5: Pin Description

| 10-pin<br>MLPD | 10-pin<br>WL-CSP | Die | Pin Name   | Pin Type                        | Description                                                 |

|----------------|------------------|-----|------------|---------------------------------|-------------------------------------------------------------|

| NA             | NA               | 1   | meas       | Analog I/O                      | Analog test pin (1)                                         |

| 1              | C4               | 2   | VP_IO      | Supply Pad                      | Positive supply of the interface / IC                       |

| 2              | B1               | 3   | VP_REG     | Analog<br>Output                | Regulator output                                            |

| 3              | C3               | 4   | LC1        | Analog I/O                      | Connection to tag coil                                      |

| 4              | C2               | 5   | LC2        | Analog I/O                      | Connection to tag coil                                      |

| 5              | C1               | 6   | VSS        | Supply Pad                      | Ground, die substrate potential                             |

| 6              | A1               | 9   | /SS        | Digital                         | SPI enable (active low) / I <sup>2</sup> C interface enable |

| 7              | А3               | 10  | SCLK / SCL | Input                           | SPI / I <sup>2</sup> C clock                                |

| 8              | A2               | 11  | MOSI       |                                 | SPI data input                                              |

| 9              | A4               | 12  | MISO / SDA | Digital<br>Output /<br>Tristate | SPI data output / I <sup>2</sup> C data line                |

| 10             | B4               | 13  | IRQ        | Digital<br>Output               | Interrupt request output (active high)                      |

# Note(s) and/or Footnote(s):

1. Pin  $\it meas$  is not bonded in MLPD package. It is only used during wafer sort test.

# **Absolute Maximum Ratings**

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated under Operating Conditions is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Figure 6: Absolute Maximum Ratings

| Symbol                | Parameter                                   | Min         | Max        | Unit    | Comments                                                                                                                                                                                                                                                                                            |  |  |

|-----------------------|---------------------------------------------|-------------|------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Electrical Parameters |                                             |             |            |         |                                                                                                                                                                                                                                                                                                     |  |  |

| VDD                   | DC supply voltage                           | -0.5        | 6.5        | V       |                                                                                                                                                                                                                                                                                                     |  |  |

| V <sub>in</sub>       | Input pin voltage except LC1 and LC2        | -0.5        | 6.5        | V       |                                                                                                                                                                                                                                                                                                     |  |  |

|                       | Input pin voltage pins LC1 and LC2          | -0.5        | 6.5        | V       |                                                                                                                                                                                                                                                                                                     |  |  |

|                       | Peak current induced on pins<br>LC1 and LC2 |             | 100        | mA      |                                                                                                                                                                                                                                                                                                     |  |  |

| I <sub>scr</sub>      | Input current (latch-up immunity)           | -100        | 100        | mA      | Norm: Jedec 78                                                                                                                                                                                                                                                                                      |  |  |

|                       | El                                          | ectrostatio | Discharge  | •       |                                                                                                                                                                                                                                                                                                     |  |  |

| ESD <sub>HBM</sub>    | Electrostatic Discharge HBM                 | ±2          |            | kV      | Norm: MIL 883 E method 3015<br>(Human Body Model)                                                                                                                                                                                                                                                   |  |  |

| ESD <sub>CDM</sub>    | ESD – Machine and Charged<br>Device Models  | ±500        |            | ٧       |                                                                                                                                                                                                                                                                                                     |  |  |

|                       | Temperature                                 | Ranges a    | nd Storage | Conditi | ons                                                                                                                                                                                                                                                                                                 |  |  |

| T <sub>strg</sub>     | Storage temperature                         | -55         | 150        | °C      |                                                                                                                                                                                                                                                                                                     |  |  |

| T <sub>body</sub>     | Package body temperature                    |             | 260        | °C      | Norm: IPC/JEDEC J-STD-020. The reflow peak soldering temperature (body temperature) is specified according IPC/JEDEC J-STD-020 "Moisture/Reflow Sensitivity Classification for Non-hermetic Solid State Surface Mount Devices." The lead finish for Pb-free leaded packages is matte tin (100% Sn). |  |  |

| RH <sub>NC</sub>      | Relative Humidity<br>non-condensing         | 5           | 85         | %       |                                                                                                                                                                                                                                                                                                     |  |  |

| MSL                   | Moisture Sensitivity Level                  | 3           |            |         | Represents a max. floor life time of 168h                                                                                                                                                                                                                                                           |  |  |

Page 8ams DatasheetDocument Feedback[v1-01] 2015-Apr-29

# **Electrical Characteristics**

All limits are guaranteed. The parameters with min and max values are guaranteed with production tests or SQC (Statistical Quality Control) methods.

# **Operating Conditions**

All in this specification defined tolerances for external components need to be assured over the whole operation conditions range and also over lifetime.

Figure 7: Electrical Characteristics

| Symbol             | Parameter            | Min  | Max | Unit | Notes                                |

|--------------------|----------------------|------|-----|------|--------------------------------------|

| I <sub>lim</sub>   | Limiter current      |      | 30  | mA   |                                      |

| V <sub>VP_IO</sub> | SPI power supply     | 1.65 | 5.5 | V    | When logic powered from RF interface |

| V <sub>VP_IO</sub> | SPI power supply     | 1.65 | 5.5 | V    | When logic powered from VP_IO        |

| T <sub>junc</sub>  | Junction temperature | -40  | 125 | °C   |                                      |

# DC/AC Characteristics for Digital Inputs and Outputs

Figure 8: CMOS Inputs

| Symbol            | Parameter                | Min          | Тур | Max          | Unit | Note   |

|-------------------|--------------------------|--------------|-----|--------------|------|--------|

| V <sub>IH</sub>   | High level input voltage | 0.7 * VDD_IO |     |              | V    |        |

| V <sub>IL</sub>   | Low level input voltage  |              |     | 0.3 * VDD_IO | V    |        |

| I <sub>LEAK</sub> | Input leakage current    |              |     | 10           | μΑ   | @125°C |

#### Note(s) and/or Footnote(s):

1. Valid for input pins /SS, MOSI and SCLK  $\,$

ams Datasheet Page 9

[v1-01] 2015-Apr-29

Document Feedback

Figure 9: CMOS Outputs

| Symbol | Parameter                        | Min              | Тур | Max              | Unit | Note         |

|--------|----------------------------------|------------------|-----|------------------|------|--------------|

| VOH    | High level output voltage        | 0.85 *<br>VDD_IO |     |                  | V    | Isource=1mA  |

| VOL    | Low level output voltage         |                  |     | 0.15 *<br>VDD_IO | V    | VP_IO = 5V   |

| RO     | Output Resistance                |                  | 200 | 400              | Ω    |              |

| RPD    | Pull-down resistance pad<br>MISO |                  | 10  |                  | kΩ   | see note (1) |

#### Note(s) and/or Footnote(s): Valid for output pins MISO and IRQ

# **Electrical Specifications**

Figure 10: Electrical Specifications

| Symbol              | Parameter                         | Min     | Тур        | Max | Unit   | Note                                                                     |

|---------------------|-----------------------------------|---------|------------|-----|--------|--------------------------------------------------------------------------|

| I <sub>SB_SPI</sub> | Stand by consumption on VP_IO     |         | 100        |     | nA     |                                                                          |

| V <sub>LIM</sub>    | Limiter Voltage                   |         | 5.2        | 5.5 | V      | I <sub>LC</sub> =30mA (DC) <sup>(1)</sup>                                |

| I <sub>S</sub>      | Supply current                    |         | 350        |     | μΑ     | see note (2)                                                             |

| V <sub>HF_PON</sub> | HF_PON threshold<br>(rising VREG) |         | 1.6<br>2.3 |     | V      | see note (3)                                                             |

| V <sub>POR_HY</sub> | HF_PON hysteresis                 |         | 0.8        |     | V      |                                                                          |

| V <sub>MOD</sub>    | Modulator ON voltage drop         |         | 1.2<br>2.6 |     | >      | I <sub>LC</sub> =1mA <sup>(1)</sup> I <sub>LC</sub> =30mA <sup>(1)</sup> |

| C <sub>RES</sub>    | Resonance Capacitor               |         | 45         |     | pF     |                                                                          |

| EE <sub>EN</sub>    | EEPROM endurance                  | 100 000 |            |     | cycles | @ 125°C <sup>(4)</sup>                                                   |

| EE <sub>RET</sub>   | EEPROM retention                  | 10      |            |     | years  | @ 125°C <sup>(5)</sup>                                                   |

### Note(s) and/or Footnote(s):VP\_IO=1.8V, Temperature 25°C unless noted otherwise

Page 10ams DatasheetDocument Feedback[v1-01] 2015-Apr-29

<sup>1.</sup> Pull down can be enabled while MISO output is in tristate. The activation is controlled by register setting.

<sup>1.</sup>  $\rm I_{LC}$  is the current flowing through LC1 and LC2 pins

<sup>2.</sup> Internal supply current measured over VP\_IO pin, by forcing internal digital supply to 2.0V, and applying 13.56 MHz alternative pulses with amplitude 3.0Vpp to LC1 and LC2.

<sup>3. 1.6</sup>V is set in Power Mode 2 only.

<sup>4.</sup> See Figure 11.

<sup>5.</sup> See Figure 12.

Figure 11: EEPROM Endurance Over Temperature

Figure 12: EEPROM Data Retention Over Temperature

ams Datasheet [v1-01] 2015-Apr-29

# **Detailed Description**

# Analog Frontend (AFE)

The AFE is connected to external tag coil, which together with the integrated resonant capacitor forms an LC tank resonating at the external electromagnetic field frequency (13.56 MHz). Figure 13 depicts the main AFE building blocks.

Figure 13: PICC AFE Block Diagram

**Rectifier** extracts DC power supply from the AC voltage induced on coil terminals.

**Limiter** limits the maximum voltage on coil terminals to protect AFE from destruction. At voltages that exceed limiter voltage it starts to absorb current (acts as some sort of shunt regulator).

**Modulator Switch** is used for communication the NFC tag to a NFC device. When switched on it will draw current from coil terminals. This mechanism is called load modulation. Variation of current in the modulator switch (ON and OFF state) is seen as modulation by the NFC device.

Page 12

Document Feedback

[v1-01] 2015-Apr-29

**Demodulator** is used for communication NFC device to NFC tag. It detects AM modulation of the NFC device magnetic field. The demodulator is designed to accept modulation according to NFC-A specifications ([NFC Analog] [NFC Digital]).

**Clock Extractor** extracts a digital clock signal from the PCD carrier field frequency which is used as clock signal by logic blocks.

**HF\_PON** enables operation of the AFE and the logic when the supply voltage is sufficiently high. A buffer capacitor and HF\_PON hysteresis guarantee that there is no reset during NFC device modulation.

**Internal Regulator** provides regulated voltage VP\_INT to the AFE and in most cases also to EEPROM and logic blocks. Typical regulated voltage VP\_INT is 2.0V. A buffer capacitor is also integrated.

**External Regulator** provides regulated voltage on external pin VP\_REG where it can be used to supply some external circuitry. The regulated voltage and output resistance can be adjusted using EEPROM settings. Appropriate external buffer capacitor is needed in case VP\_REG is used in the application. Current which may be provided depends on reader field strength, antenna size and Q factor, but it is limited to maximum 5mA.

**Bias** provides bias currents and reference voltages to AFE analog blocks.

## **Power Management**

AS3955 power management comprises of four different modes to fit requirements of different applications. AS3955 supports two power sources, whose activation depends on the selected power mode.

#### **Power Mode 0**

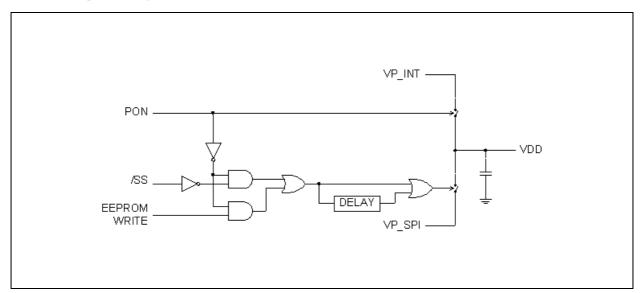

In this power mode, the Power Manager is controlling the supply of the PICC Logic, EEPROM and SPI / I<sup>2</sup>C Interface (VDD). Its inputs are VP\_INT (rectified and regulated supply extracted from RF field) and the VP\_IO (supplied by external battery).

In standby mode, when AS3955 is not in the RF field (the condition is that rectified supply voltage is below HF\_PON threshold) and the SPI /  $I^2C$  is not active (/SS is high), the VDD supply is disconnected. The only current consumption in this state is leakage on VP\_IO, mainly due to level shifters and SPI /  $I^2C$  pins.

When AS3955 is placed in a RF field, VDD is connected to VP\_INT. This happens once the VP\_INT level is above the HF\_PON threshold.

ams Datasheet Page 13

[v1-01] 2015-Apr-29 Document Feedback

VP\_IO is connected to VDD only when AS3955 is not in the RF field (rectified supply voltage is below HF\_PON threshold) and the SPI / I<sup>2</sup>C interface is activated by pulling /SS signal low. The switch to VP\_IO is controlled by /SS signal. The deactivation is delayed by 0.7ms minimum, so that the switch shall stay closed in case of shorter times between successive SPI / I<sup>2</sup>C activations. The switch is also closed during EEPROM writes activated over SPI / I<sup>2</sup>C.

At activation of the switch, the time between the falling edge of the /SS signal and rising edge of SCLK shall be at least 300  $\mu s$  to allow charging of internal VDD buffer capacitor, expiration of POR signal and to perform a complete IC initialization. Please note that the only SPI /  $I^2C$  operations, which are allowed in this mode, are read and write of EEPROM and registers.

If the RF filed is lost during operation and the external system (MCU) is supplied over battery and /SS is low then power manager will automatically connect the VDD to VP IO.

To enable low power mode where tag consumes less than 1uA at room temperature following conditions must be met:

- SPI interface configured

- All SPI interface input lines (including /SS) must be set to high

- All SPI output lines must be open

Figure 14: Power Manager Concept

Page 14

Document Feedback

[v1-01] 2015-Apr-29

#### Power Mode 1

AS3955 is fully supplied by RF field. AS3955 checks if Extended or Tunneling mode are enabled. In this case, VP\_REG supplies the system (SPI / I<sup>2</sup>C pads, pull-ups, MCU), otherwise energy harvesting is turned off and VP\_REG is set in tristate.

Such power mode can be used in battery-less systems where the system is fully powered by the RF field. In such configuration, the VP\_REG output pin for energy harvesting and VP\_IO input supply shall be externally connected. Battery, even when present, will not be involved.

If this power mode is enabled and neither tunneling nor extended mode are enabled, *rreg* value from IC Configuration Register 1 will be forced to zero. This will disable energy harvesting.

#### Power Mode 2

In this case, the external supply is used to provide power to digital blocks, EEPROM, SPI /  $I^2C$  pads and MCU. External supply VP\_REG is not used. Since this mode can be enabled only after initialization of the chip, the /SS line must be either permanently set to low or pulled low for short time (400µs) to complete the initialization.

This mode is specifically designed to operate with AS392x products (**ams**' Active Boost). In this mode, the HF\_PON threshold of the chip will be decreased so that it will operate with external voltage on LC pin in the range of 2.7-3.6Vpp.

If this mode is enabled, AS3955 will not be turned off as long as there is an external supply present.

#### **Power Mode 3**

In this case the external supply shall be used to provide power to digital blocks, EEPROM, SPI / I<sup>2</sup>C pads and MCU. External supply VP\_REG is not used. Since this mode can be enabled only after initialization of the chip, the /SS line must be either permanently set to low or pulled low for short time to complete the initialization.

In this mode, the HF\_PON threshold of the chip is set so that it will operate with external voltage on LC pin in the range of 4.1-5Vpp.

If this mode is enabled, AS3955 will not be turned off as long as there is an external power present.

#### **Interface Arbitration**

Concurrent access to AS3955 internal EEPROM from RF or SPI / I<sup>2</sup>C requires arbitration, to resolve conflicts or undesired behaviour.

AS3955 implements two arbitration modes, which can be set in Configuration Byte IC\_CFG0.

ams Datasheet Page 15

[v1-01] 2015-Apr-29 Document Feedback

#### **Arbitration Mode 0**

AS3955 arbitrates EEPROM write accesses according to first-come-first-serve principle.

- In case no write access is currently ongoing, both RF and SPI / I<sup>2</sup>C interfaces are allowed to write into EEPROM.

- In case a write request comes over RF, while SPI / I<sup>2</sup>C is writing, AS3955 will return a NAK.

- In case a write request comes over SPI / I<sup>2</sup>C while RF is writing, AS3955 will trigger a l\_err\_acc interrupt (see Figure 92).

#### **Arbitration Mode 1**

AS3955 gives always priority to RF accesses. In this mode, AS3955 behaves over RF as a pure contactless tag.

- In case SPI / I<sup>2</sup>C is performing a EEPROM write while the RF field is turned on, the write operation is interrupted to allow the initialization of the RF communication

- In case the RF field is already on and SPI / I<sup>2</sup>C performs a

write to EEPROM and a READ or WRITE command is

received via RF, the write operation of SPI / I<sup>2</sup>C is

interrupted so that the RF operation can be performed

In both cases, a *I\_err\_acc* interrupt (see Figure 92) will be triggered.

Please note that the interruption of an EEPROM write may result in an undefined or "weak" state for the cell being programmed, and a second successful write attempt is suggested.

#### **Energy Harvesting**

AS3955 has energy harvesting capability. The regulated voltage output pin for energy harvesting is VP\_REG. The energy harvesting is enabled only in Power Mode 1 and 2. The output voltage and resistance can be set by Configuration Byte IC\_CFG1. The energy harvesting can be disabled by setting the output resistance register to 0 as shown in Figure 15.

Figure 15:

Output Resistance Settings

| rreg<1:0> | Output Resistance | Comment                              |

|-----------|-------------------|--------------------------------------|

| 00b       | X                 | Disabled – output pin is in tristate |

| 01b       | 100Ω              |                                      |

| 10b       | 50Ω               |                                      |

| 11b       | 25Ω               |                                      |

Figure 15 shows settings of the regulated voltage output. The output can be set between 1.8V and 4.5V in 100mV step.

Page 16

Document Feedback

[v1-01] 2015-Apr-29

Figure 16:

Regulated Voltage Output Settings

| vreg<4:0>        | Output Voltage      | Abs. Accuracy                  |

|------------------|---------------------|--------------------------------|

| 00000b           | 1.8V                | ±115mV                         |

| 00001b<br>:<br>: | Step 100mV<br>±20mV | Linearly increasing over range |

| 11011b           | 4.5V                | ±225mV                         |

#### Silent Mode

The Silent mode enables detection of the power status of a circuit whose supply (Vdd) is connected to VP\_IO pin. If this mode is enabled and the voltage measured on pin VP\_IO is below the configured threshold value, the RF part of AS3955 will be disabled, and the IC will not be responsive to incoming commands. Silent mode settings can be performed by using Configuration Byte IC\_CFGO.

This feature overcomes a potentially inconsistent behavior in a battery powered system, where a passive NFC tag can always communicate with a NFC device, also in case the battery is not sufficiently charged to supply the rest of the system. A typical example is when the NFC tag is used for Bluetooth pairing: AS3955 would trigger a pairing procedure only in case the system is fully operational by monitoring the supply voltage.

#### **Memory Protection**

AS3955 internal memory can be protected from unauthorized access by enabling password authentication. A 32-bit password can be set to protect the full user memory, or part of it, to allow the creation of a public data and a private data area. Password protection can be applied for read and write accesses.

Password authentication is performed through a standard WRITE command to the Authentication Password block. A maximum of 7 negative attempts are permitted before the chip is locked. Once authenticated, the user can modify the password.

Password protection applies to RF communication only.

Further information on how to handle password authentication can be found in Authentication Password, Configuration Byte AUTH\_CFG, Configuration Byte AUTH\_CNT and Configuration Byte AUTH\_LIM.

ams Datasheet Page 17

[v1-01] 2015-Apr-29 Document Feedback

# Passive Wake-Up

AS3955 is able to operate NFC tag operations standalone and fully powered by the RF field. The connected MCU can remain is standby/sleep mode as long as its intervention is not required by the application, in order to save power. AS3955 can be configured to notify the MCU through a wake-up interrupt.

A number of triggering events can be selected, e.g.:

- Power up

- SELECTED state entered

- Reception of SLP\_REQ command

- NFC device has updated memory content

For a complete interrupt source list, please refer to the section Interrupt Registers.

# **Chip Kill**

Some applications require that the RF link is active only under certain conditions, e.g. during device configuration only in a controlled environment like a production facility.

AS3955 can be configured by the MCU in order to restrict the NFC device access to the system. By setting the Configuration Byte CHIP\_KILL in EEPROM, the MCU can disable access to SPI/I<sup>2</sup>C from the RF link (i.e. Tunneling and Extended mode are permanently disabled), or even disable RF communication completely. In the latter case, AS3955 will not respond to incoming RF commands.

This configuration can be modified only by the MCU through  $SPI/I^2C$  interfaces.

Page 18

Document Feedback

[v1-01] 2015-Apr-29

# **NFC Tag Functionality**

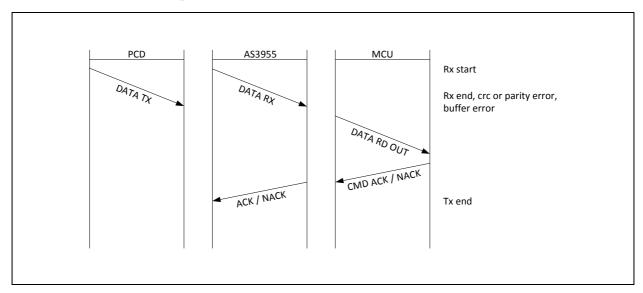

# **Communication Principle**

AS3955 autonomously executes complete NFC-A anti-collision communication sequence, during which the 7-byte UID is used ([NFC Analog] [NFC Digital]). After anti-collision, the NFC tag is brought into SELECTED state where read and write commands can be processed. The NFC tag will accept only read and write command issued to the address space actually available in AS3955 EEPROM. Any attempt to access an address outside the internal memory address space will be rejected. This default behavior of the NFC tag can be modified by enabling Tunneling or Extended mode.

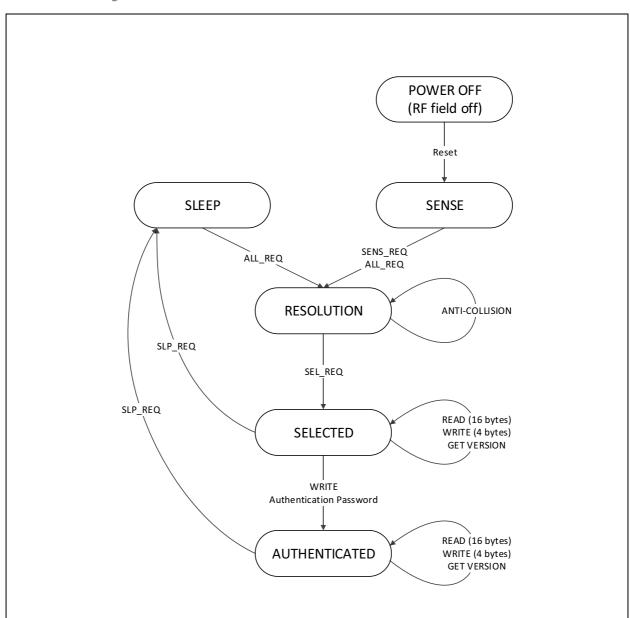

A simplified AS3955 state diagram is shown in Figure 17.

Figure 17: AS3955 State Diagram

ams Datasheet Page 19

[v1-01] 2015-Apr-29 Document Feedback

#### **SENSE State**

After a power-on reset (POR), AS3955 switches to the SENSE state. This state is exited when a SENS\_REQ or an ALL\_REQ command is received from the NFC device. Any other data received while in this state is interpreted as an error and AS3955 remains in SENSE state.

When in SELECTED or AUTHENTICATED state, a correctly executed SLP\_REQ command will modify the default waiting state from SENSE to SLEEP state. SLEEP state can be exited when an ALL\_REQ command is received.

#### **SLEEP State**

Together with SENSE state, SLEEP state is the other waiting state for AS3955. SLEEP state can be entered upon reception of a SLP\_REQ command. The distinction between SENSE and SLEEP state is made necessary to discriminate selected and not yet selected tags.

AS3955 can only exit this state upon reception of an ALL\_REQ command. Any other command received in this state is interpreted as an error and AS3955 state remains unchanged.

#### **RESOLUTION State**

In RESOLUTION state, the NFC device is resolving the tag UID. Since AS3955 has a double size UID, the RESOLUTION state actually comprises of two sub-states, where the anti-collision procedure is carried out in Cascade Level 1 and 2. Please refer to [ISO18092] for further information.

#### **SELECTED State**

All memory operations are operated in SELECTED state.

Upon reception of a SLP\_REQ command, SELECTED state is exited and AS3955 transits to SLEEP state. Any other command received when the device is in this state is interpreted as an error. Depending on its previous state, AS3955 returns to either SENSE or SLEEP state.

Upon reception of a SECTOR SELECT command, AS3955 returns a NAK and transits to SENSE or SLEEP state, depending on its previous state.

AS3955 transits to the AUTHENTICATED state after successful password verification, using a standard WRITE command to a dedicated memory address (see Authentication Password). The number of permitted failed authentications is set to 7, after which AS3955 transits to LOCKED sub-state (not shown in the picture). When LOCKED state is entered, only the MCU can bring AS3955 back to SENSE state by resetting the authentication counter (Configuration Byte AUTH\_CNT) back to 0 and issue a Set Default, or Go To Sense, or Go To Sleep command.

When in LOCKED sub-state, all memory operations are only allowed in the memory area not password protected, as defined by the configuration byte Configuration Byte AUTH\_LIM.

Page 20

Document Feedback

[v1-01] 2015-Apr-29

Upon reception of a SLP\_REQ command, SELECTED state is exited and AS3955 transits to SLEEP state.

Any other command received when the device is in this state is interpreted as an error and, depending on its previous state, AS3955 returns to either SENSE or SLEEP state.

#### **AUTHENTICATED State**

In this state, all operations on memory blocks, which are configured as password verification protected, can be performed.

Upon reception of a SECTOR SELECT command, AS3955 returns a NAK and transits to SENSE or SLEEP state, depending on its previous state.

IUpon reception of a SLP\_REQ command, AUTHENTICATED state is exited and AS3955 transits to SLEEP state.

Any other command received when the device is in this state is interpreted as an error and, depending on its previous state, AS3955 returns to either SENSE state or SLEEP state.

# NFC Forum Type 2 Tag Support

NFC Forum NFC-A commands ALL\_REQ, SENS\_REQ, SDD\_REQ, SEL\_REQ, SLP\_REQ are required for anti-collision. Commands READ and WRITE are used for internal memory access. If NFC device issues a SECTOR SELECT command, AS3955 shall always reply with NAK.

Figure 18: NFC-A vs ISO14443 Terminology

| NFC-A Term           | ISO14443 Term |  |  |  |  |

|----------------------|---------------|--|--|--|--|

| States               |               |  |  |  |  |

| SENSE                | IDLE          |  |  |  |  |

| SLEEP                | HALT          |  |  |  |  |

| RESOLUTION           | READY         |  |  |  |  |

| SELECTED             | ACTIVE        |  |  |  |  |

| Commands / Responses |               |  |  |  |  |

| SENS_REQ             | REQA          |  |  |  |  |

| ALL_REQ              | WUPA          |  |  |  |  |

| SENS_RES             | ATQA          |  |  |  |  |

| SSD_REQ              | AC            |  |  |  |  |

| SEL_REQ              | SELECT        |  |  |  |  |

| SLP_REQ              | HLTA          |  |  |  |  |

ams Datasheet Page 21

[v1-01] 2015-Apr-29 Document Feedback

# **UID Coding**

Anti-collision procedure is based on the Unique Identification Number (UID). AS3955 supports double size UID (7 bytes). First three bytes of the UID are hardwired inputs to the PICC Logic (uid<23:0>). The last 4 bytes of the UID are stored in EEPROM UID block.

# First UID Byte (uid0)

The first byte of UID is Manufacturer ID according to [ISO7816-6]. It is coded on bits *uid*<7:0>. **ams** IC Manufacturer ID is 3Fh.

## Second UID Byte (uid1)

The second byte of UID (uid<15:8>) is reserved for **ams**' chip type (IC Type). Every **ams**' RFID tag IC has its own chip type assigned. AS3955 IC type is 14h.

#### Third UID Byte (uid2)

The third byte of UID (uid<23:16>) is set to 00h.

#### Figure 19:

**Coding of First Three UID Bytes**

| UID Byte | Value (Hex) |

|----------|-------------|

| uid0     | 3F          |

| uid1     | 14          |

| uid2     | 00          |

# Last Four UID Bytes (uid3-uid6)

The last 4 bytes of UID are read from EEPROM (UID block) and pre-programmed during IC production. Those 4 bytes are unique, and cannot be modified.

Figure 20:

**Last Four UID Bytes**

| UID Byte | UID Block Bits |

|----------|----------------|

| uid3     | b7-b0          |

| uid4     | b15-b8         |

| uid5     | b23-b16        |

| uid6     | b31-b24        |

Page 22ams DatasheetDocument Feedback[v1-01] 2015-Apr-29

# Coding of SENS\_RES, SEL\_REQ, ACK and NACK

Several bits in certain responses are defined as don't-care in the NFC-A standard [NFC Digital], some others are defined by optional choices in standard protocol. This chapter defines how these bits are actually set in AS3955.

#### SENS\_RES Response

SENS\_RES is a response on ALL\_REQ and SENS\_REQ commands. The SENS\_RES is defined by Configuration Bytes SENSR1 and SENSR2 stored in EEPROM.

Figure 21: **Coding of SENS RES Response**

| b15 | b14    | b13 | b12 | b11 | b10 | b9 | b8 | b7 | b6 | b5  | b4  | b3 | b2 | b1 | b0 |

|-----|--------|-----|-----|-----|-----|----|----|----|----|-----|-----|----|----|----|----|

|     | SENSR2 |     |     |     |     |    |    |    |    | SEN | SR1 |    |    |    |    |

#### SEL\_RES Response, Cascade Level 1 and 2

SEL\_RES is the response to SEL\_REQ command. Since AS3955 UID is double sized, SEL\_RES responses for Cascade Level 1 and Cascade Level 2 are defined. SEL\_RES on Cascade Level 1 and 2 is defined with Configuration Byte SELR except for cascade bit 3. The response on Cascade Level 2 is also configured by *selr\_b6\_inv* bit which, when set, inverts cascade bit 6 in SEL\_RES response on Cascade Level 2 (see IC\_CFG2).

Figure 22: **SEL\_RES CL1 Coding**

| b8<br>MSB    | b7 | b6 | b5 | b4 | b3           | b2 | b1<br>LSB                         | Description |

|--------------|----|----|----|----|--------------|----|-----------------------------------|-------------|

| sel_res<7:3> |    |    |    | 1  | sel_res<1:0> |    | Cascade bit set: UID not complete |             |

Figure 23: **SEL\_RES CL2 Coding**

| b8<br>MSB    | b7 | b6             | b5           | b4 | b3 | b2           | b1<br>LSB | Description          |

|--------------|----|----------------|--------------|----|----|--------------|-----------|----------------------|

| sel_res<7:6> |    | sel_res<5>     | sel_res<4:3> |    | 0  | sel_res<1:0> |           | selr_b6_inv set to 0 |

|              |    | NOT sel_res<5> |              |    | O  |              |           | selr_b6_inv set to 1 |

# Note(s) and/or Footnote(s):

1. According to [ISO14443-3], all bits except b3 are "don't care" for Cascade Level 1, and all bits except b6 and b3 are "don't care" for  $Cascade\ Level\ 2.\ Bit\ b6\ in\ CL2\ indicates\ whether\ the\ tag\ is\ compliant\ to\ [ISO14443]\ or\ not\ (resp.\ b6=1\ and\ b6=0).\ In\ case\ of\ applications$ requiring EMVCo compliance, bit b6 in Cascade Level 1 shall be set as bit b6 in Cascade Level 2 ([EMVCO-1]).

ams Datasheet Page 23

#### **ACK Response**

The ACK response of AS3955 is a 4-bit value Ah.

# **NACK Response**

The AS3955 uses all four combinations of NAK values. The usage of various NAK values is explained in section Error Handling.

# Access to UID, SENS\_RES and SEL\_REQ During Anti-Collision

UID block, SENSR1, SENSR2 and SELR bytes are stored in a buffer. The purpose of storing these data into the buffer is faster access to the data and UID verification during the anti-collision procedure. Buffer access over SPI / I<sup>2</sup>C is locked until NFC tag enters SELECTED state.

#### **Get Version Command**

In addition to standard NFC tag commands, AS3955 supports a custom Get Version command. This command consists of 8 bits and shall be transmitted only in standalone and Extended mode when the tag is SELECTED state. The command code and the tag response are shown resp. in Figure 24 and Figure 25.

Figure 24: Coding of Get Version Command

| b8 | b7 | b6 | b5 | b4 | b3 | b2 | b1 |

|----|----|----|----|----|----|----|----|

| 0  | 1  | 1  | 0  | 0  | 0  | 0  | 0  |

Page 24ams DatasheetDocument Feedback[v1-01] 2015-Apr-29

Figure 25:

Response to Get Version Command

| Byte No. | Descr                 |            | Comment |              |

|----------|-----------------------|------------|---------|--------------|

| 0        | Fixed Header          | 00         | h       |              |

| 1        | Vendor Id             | 3F         | h       | ams AG       |

| 2        | Product Type          | 14         | h       | AS395x       |

| 3        | Product Subtype       | 01h        |         | AS3955       |

| 4        | Major Product Version | 01         | h       | 1            |

| 5        | Minor Product Version | 00         | h       | V0           |

| 6        | Storage Size          | 15h 17h    |         | see note (1) |

| 7        | Supported Features    | 01h or 02h |         | see note (2) |

#### Note(s) and/or Footnote(s):Notes:

- 1. The most significant 7 bits of the storage size byte are interpreted as an unsigned integer value *n*. As a result, it codes the total available user memory size as 2<sup>n</sup>. If the least significant bit is 0b, the user memory size is exactly 2<sup>n</sup>. If the least significant bit is 1b, the user memory size is between 2<sup>n</sup> and 2<sup>n+1</sup>.

- The user memory is the memory available for user data (Capability Container and lock bits are excluded)

- 2. The figure below is maintained consistently across the whole AS395x family, where Get Version command is supported.

Figure 26: Get Version Response, Byte 7

| Get Version |                                                                                                    |  |  |  |  |  |  |  |

|-------------|----------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Byte No. 7  | Description                                                                                        |  |  |  |  |  |  |  |

| b7          |                                                                                                    |  |  |  |  |  |  |  |

| b6          | 00000b: ISO14443A Level 3 supported, max<br>baudrate 106 kbps, Tunneling and                       |  |  |  |  |  |  |  |

| b5          | Extended mode present, Password protection available, energy                                       |  |  |  |  |  |  |  |

| b4          | harvesting available<br>Others: RFU                                                                |  |  |  |  |  |  |  |

| b3          |                                                                                                    |  |  |  |  |  |  |  |

| b2          | 000b: No wired interface available                                                                 |  |  |  |  |  |  |  |

| b1          | 001b: SPI slave, passive wake-up available 010b: I <sup>2</sup> C slave, passive wake-up available |  |  |  |  |  |  |  |

| b0          | o rob. i C siave, passive wake-up available                                                        |  |  |  |  |  |  |  |

ams Datasheet Page 25

[v1-01] 2015-Apr-29 Document Feedback

# **Memory Organization**

AS3955 contains an embedded EEPROM module which can be accessed via RF or SPI /  $I^2$ C interface. EEPROM contains 4096 bits (512 bytes) organized in 128 blocks of 4 bytes each. Blocks in EEPROM are numbered from 00h to 7Fh. Bits in a block are numbered from 0 to 31.

Most of the EEPROM is NFC Type 2 Tag user data area (472 bytes). The position of the dynamic lock bits is fixed at the end of NFC Type 2 Tag user data area (blocks 7Ah and 7Bh). The configuration bits which define AS3955 operating options are stored in blocks 01h, 7Ch, 7Dh, 7Eh, 7Fh. Housekeeping information is stored in block 00h. 4kbit EEPROM organization is shown in Figure 27.

AS3955 is also available in 2kbit version. In this case the data area is reduced to 216 byte. AS3955 internal user memory implements static and dynamic lock bits according to NFC Forum Type 2 Tag standard. Configuration and lock bits, as well as the full 2kbit EEPROM organization, are shown in Figure 28.

#### **4kbit EEPROM Organization**

Numbers of dynamic lock bits:

- Data area size in bytes:

4\*(127 3) 7 17 = 472 bytes

- Number of dynamic lock bits:

(472 48) / 8 = 53 bits (53 bits)

Page 26

Document Feedback

[v1-01] 2015-Apr-29

Figure 27: 4kbit EEPROM Organization

|                      |            | Е          | Byte Number           | in Block   |                         |        |

|----------------------|------------|------------|-----------------------|------------|-------------------------|--------|

| Block                | 0          | 1          | 2                     | 3          | Description             | Access |

| 00h                  | UID0       | UID1       | UID2                  | UID3       | UID / Internal          | RO     |

| 01h                  | FAB_CFG0   | FAB_CFG1   | FAB_CFG2              | FAB_CFG3   | Fabrication data        | RO     |

| 02h                  | Internal 8 | Internal 9 | Lock 0                | Lock 1     | Internal / Lock         | ОТР    |

| 03h                  | CC 0       | CC 1       | CC 2                  | CC 3       | CC                      | ОТР    |

| 04h                  | Data 0     | Data 1     | Data 2                | Data 3     | Data                    | RW     |

| 05h                  | Data 4     | Data 5     | Data 6                | Data 7     | Data                    | RW     |

| 06h                  | Data 8     | Data 9     | Data 10               | Data 11    | Data                    | RW     |

| 07h<br>:<br>:<br>79h |            |            |                       |            | Data                    | RW     |

| 7Ah                  | Lock 2     | Lock 3     | Lock 4                | Lock 5     | Lock                    | ОТР    |

| 7Bh                  | Lock 6     | Lock 7     | Lock 8 <sup>(1)</sup> | Reserved 0 | Lock / Reserved         | ОТР    |

| 7Ch                  | RFP0       | RFP1       | RFP2                  | RFP3       | Authentication password | RW     |

| 7Dh                  | CHIP_KILL  | AUTH_CNT   | AUTH_LIM              | AUTH_CFG   | Authentication settings | RW     |

| 7Eh                  | SENSR1     | SENSR2     | SELR                  | IC_CFG0    | Config. block 0         | RW     |

| 7Fh                  | IC_CFG1    | IC_CFG2    | MIRQ_0                | MIRQ_1     | Config. block 1         | RW     |

#### Note(s) and/or Footnote(s):

1. Bits that are not used should be set to 0.

Access properties:

RO: Read only, writing to this word is not possible

RW: Reading and writing to this word is possible

OTP: One time programmable. A bit of this word once set to 1 cannot be set back to 0.

ams DatasheetPage 27[v1-01] 2015-Apr-29Document Feedback

# **2kbit EEPROM Organization**

Numbers of dynamic lock bits:

- Data area size in bytes:

4\*(63 3) 3 21 = 216 bytes

- Number of dynamic lock bits:

(200 48) / 8 = 21 bits (21 bits)

Figure 28: 2kbit EEPROM Organization

|          | Byte Number in Block |            |            |            |                         |        |  |  |  |  |  |

|----------|----------------------|------------|------------|------------|-------------------------|--------|--|--|--|--|--|

| Block    | 0                    | 1          | 2          | 3          | Description             | Access |  |  |  |  |  |

|          | Byte number in block |            |            |            |                         |        |  |  |  |  |  |

| Block    | 0                    | 1          | 2          | 3          | Description             | Access |  |  |  |  |  |

| 00h      | UID0                 | UID1       | UID2       | UID3       | UID / Internal          | RO     |  |  |  |  |  |

| 01h      | FAB_CFG0             | FAB_CFG1   | FAB_CFG2   | FAB_CFG3   | Fabrication data        | RO     |  |  |  |  |  |

| 02h      | Internal 8           | Internal 9 | Lock 0     | Lock 1     | Internal / Lock         | ОТР    |  |  |  |  |  |

| 03h      | CC 0                 | CC 1       | CC 2       | CC 3       | CC                      | ОТР    |  |  |  |  |  |

| 04h      | Data 0               | Data 1     | Data 2     | Data 3     | Data                    | RW     |  |  |  |  |  |

| 05h      | Data 4               | Data 5     | Data 6     | Data 7     | Data                    | RW     |  |  |  |  |  |

| 06h      | Data 8               | Data 9     | Data 10    | Data 11    | Data                    | RW     |  |  |  |  |  |

| 07h<br>: |                      |            |            |            | 5                       | 5111   |  |  |  |  |  |

| :<br>39h |                      |            |            |            | Data                    | RW     |  |  |  |  |  |

| 3Ah      | Lock 2               | Lock 3     | Lock 4     | Lock 5     | Lock                    | ОТР    |  |  |  |  |  |

| 3Bh      | Lock 6               | Lock 7     | Lock 8 (1) | Reserved 0 | Lock / Reserved         | ОТР    |  |  |  |  |  |

| 3Ch      | RFP0                 | RFP1       | RFP2       | RFP3       | Authentication password | RW     |  |  |  |  |  |

| 3Dh      | CHIP_KILL            | AUTH_CNT   | AUTH_LIM   | AUTH_CFG   | Authentication settings | RW     |  |  |  |  |  |

| 3Eh      | SENSR1               | SENSR2     | SELR       | IC_CFG0    | Config. block 0         | RW     |  |  |  |  |  |

| 3Fh      | IC_CFG1              | IC_CFG2    | MIRQ_0     | MIRQ_1     | Config. block 1         | RW     |  |  |  |  |  |

#### Note(s) and/or Footnote(s):

1. Bits that are not used should be set to 0.

Access properties:

RO: Read only, writing to this word is not possible

RW: Reading and writing to this word is possible

OTP: One time programmable. A bit of this word once set to 1 cannot be set back to 0.

Page 28ams DatasheetDocument Feedback[v1-01] 2015-Apr-29

# **UID Bytes**

The UID block contains four LSB bytes of the 7-byte UID which is used during anti-collision and selection process. Every IC is programmed by a unique number during fabrication process at **ams**. See UID Coding about details on UID.

This block stores some IC manufacturer data which is programmed and locked during fabrication process at **ams**.

UID is treated as IC internal configuration, and is permanently locked during IC production.

# **Fabrication Data**

Fabrication data are used to set internal configuration and trimming values. They are treated as IC internal configuration.

Fabrication Data FAB\_CFG0

Figure 29: Fabrication Data FAB\_CFG0

| Conf. Bit | Name | Default | Function               | Note |

|-----------|------|---------|------------------------|------|

| b7        |      | 0       |                        |      |

| b6        |      | 0       |                        |      |

| b5        |      | 0       |                        |      |

| b4        |      | 0       | Internal configuration |      |

| b3        |      | 0       | Internal configuration |      |

| b2        | b2   |         |                        |      |

| b1        |      | 0       |                        |      |

| b0        |      | 0       |                        |      |

#### Note(s) and/or Footnote(s):

1. This byte can be set only during production.

ams Datasheet Page 29

[v1-01] 2015-Apr-29 Document Feedback

# Fabrication Data FAB\_CFG1

Figure 30: Fabrication Data FAB\_CFG1

| Conf. Bit | Name    | Default | Function                                   | Note |

|-----------|---------|---------|--------------------------------------------|------|

| b7        | fdel<3> | 0       |                                            |      |

| b6        | fdel<2> | 0       | PCD to PICC frame delay time compensation; |      |

| b5        | fdel<1> | 0       | frame compensation defined as fdel*1/fc    |      |

| b4        | fdel<0> | 0       |                                            |      |

| b3        | osct<1> | 0       | Oscillator trimming bits                   |      |

| b2        | osct<0> | 0       | Oscillator trimining bits                  |      |

| b1        | decc<1> | 0       | Decoder compensation register              |      |

| b0        | decc<0> | 0       | Decoder compensation register              |      |

#### Note(s) and/or Footnote(s):

1. This byte can be set only during production.

The *fdel* bits define frame delay time (FDT) adjustment and represent a time compensation in number of clocks of carrier frequency. The *osct* bits are trimming bits for the internal oscillator.

Fabrication Data FAB\_CFG2

Figure 31: Fabrication Data FAB\_CFG2

| Conf. Bit | Name      | Default | Function                                                                   | Note |

|-----------|-----------|---------|----------------------------------------------------------------------------|------|

| b7        | test_mode | 0       |                                                                            |      |

| b6        | mod_r     | 0       | 1: decreased modulator switch resistance                                   |      |

| b5        | miso_pd2  | 0       | 1: pull down on MISO, when \SS is low and MISO is not driven by the AS3955 |      |

| b4        | miso_pd1  | 0       | 1: pull down on MISO when \SS is high                                      |      |

| b3        | rfu       | 0       |                                                                            |      |

| b2        | rfu       | 0       |                                                                            |      |

| b1        | rfu       | 0       |                                                                            |      |

| b0        | rfu       | 0       |                                                                            |      |

#### Note(s) and/or Footnote(s):

1. This byte can be set only during production.

Page 30ams DatasheetDocument Feedback[v1-01] 2015-Apr-29

#### Fabrication Data FAB CFG3

Figure 32: **Fabrication Data FAB\_CFG3**

| Conf. Bit | Name       | Default | Function                    | Note |

|-----------|------------|---------|-----------------------------|------|

| b7        | uid_crc<7> |         |                             |      |

| b6        | uid_crc<6> |         |                             |      |

| b5        | uid_crc<5> |         |                             |      |

| b4        | uid_crc<4> |         | CRC value calculated on UID |      |

| b3        | uid_crc<3> |         | CRC value calculated on UID |      |

| b2        | uid_crc<2> |         |                             |      |

| b1        | uid_crc<1> |         |                             |      |

| b0        | uid_crc<0> |         |                             |      |

#### Note(s) and/or Footnote(s):

1. This byte can be set only during production.

# **Reserved Bytes**

The reserved bytes belong to reserved memory areas.

#### **OTP Blocks**

Write and Read Lock blocks are OTP (One Time Programmable). This means that once they are set to 1, they cannot be set back to 0. Since setting OTP bits is an irreversible operation, it is strongly recommended to perform this operation in controlled environment.

#### **Lock Bits**

The bits of byte 2 and 3 of block 02h represent the field-programmable read-only locking mechanism called "static lock bytes". They are called static because their position in memory is fixed.

When data memory is larger than 16 blocks (64 bytes), also "dynamic lock bytes" are required. They are located starting at address 7Ah (4kbit version) and address 3Ah (2kbit version). Block lock granularity is 1 block per bit for the first 16 blocks, 2 blocks per bit for the remaining blocks.

Lock bits are OTP, i.e. setting bits to 1b is an irreversible operation. Bits at 0b can be set to 1b through a WRITE operation, the result being a bit-wise OR with the current value.

ams Datasheet Page 31 **Document Feedback**

Lock bits apply only to RF interface, as SPI / I<sup>2</sup>C interface has unlimited access to user data area.

- Lock 0 byte locks 8 blocks starting from address 00h where lock bit 0 locks block on address 00h

- Lock 1 byte locks 8 blocks starting from address 08h where lock bit 0 locks block on address 08h

- Lock 2 byte locks 16 blocks starting from address 10h where lock bit 0 locks block on address 10h and 11h

- Lock 3 byte locks 16 blocks starting from address 20h where lock bit 0 locks block on address 20h and 21h

- Lock 4 byte locks 16 blocks starting from address 30h where lock bit 0 locks block on address 30h and 31h

- Lock 5 byte locks 16 blocks starting from address 40h where lock bit 0 locks block on address 40h and 41h

- Lock 6 byte locks 16 blocks starting from address 50h where lock bit 0 locks block on address 50h and 51h

- Lock 7 byte locks 16 blocks starting from address 60h where lock bit 0 locks block on address 60h and 61h

- Lock 8 byte locks 16 blocks starting from address 70h where lock bit 0 locks block on address 70h and 71h

Figure 33: Example of Lock Bits

| Lock 0 byte |             |     |     |     |             | Lock 1 byte |     |     |     |     |     |     |     |     |     |

|-------------|-------------|-----|-----|-----|-------------|-------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| b7          | b6          | b5  | b4  | b3  | b2          | b1          | b0  | b7  | b6  | b5  | b4  | b3  | b2  | b1  | b0  |

|             | locks block |     |     |     | locks block |             |     |     |     |     |     |     |     |     |     |

| 07h         | 06h         | 05h | 04h | 03h | 02h         | 01h         | 00h | 0Fh | 0Eh | 0Dh | 0Ch | 0Bh | 0Ah | 09h | 08h |

#### **Capability Container**

Block 03h in AS3955 EEPROM contains the Capability Container (CC), pre-programmed during IC production according to NFC Forum Type 2 Tag specifications [T2T]. CC bits are OTP, i.e. setting bits to 1b is an irreversible operation. Bits at 0b can be set to 1b through a WRITE operation, the result being a bit-wise OR with the current value.

Figure 34 and Figure 35 show the Capability Container content at delivery.

Figure 34: CC Content at Delivery (4kbit Option)

|               | Byte number in block |     |     |     |  |  |  |

|---------------|----------------------|-----|-----|-----|--|--|--|

| Block address | 0                    | 1   | 2   | 3   |  |  |  |

| 03h           | E1h                  | 10h | 3Bh | 00h |  |  |  |

Page 32ams DatasheetDocument Feedback[v1-01] 2015-Apr-29

### Figure 35: CC Content at Delivery (2kbit Option)

|               | Byte number in block |     |     |     |  |

|---------------|----------------------|-----|-----|-----|--|

| Block address | 0                    | 1   | 2   | 3   |  |

| 03h           | E1h                  | 10h | 1Bh | 00h |  |

# **Configuration Bytes**

The Configuration bytes are used to define AS3955 operating options. AS3955 is delivered by **ams** with default settings.

#### **Authentication Password**

The Authentication password block (bytes RFP0, RFP1, RFP2, and RFP3) contains the 32-bit password. This password is used for authentication over RF side. The NFC tag is set into AUTHENTICATED state when a write command is issued via the RF to write password address with the data that has same content as the data stored in Authentication password block. If the NFC tries to authenticate with a wrong password, AS3955 shall not respond and returns into SENSE / SLEEP state and the value of the AUTH CNT is decreased.

The password can be overwritten via RF only in AUTHENTICATED state and can always be set via SPI / I<sup>2</sup>C. Configuration register AUTH\_CFG defines access rights controlled by the password. The RF password can't be read via

The authentication for read or write is required only to the memory portion defined by AUTH\_LIM. The chip is no longer in AUTHENTICATED state when the tag leaves SELECTED state.

An attempt to read the password block will return zeroes. The authentication does not override permissions set by the lock bits. Authentication also does not restrict access over SPI / I<sup>2</sup>C in any way.

Authentication can be configured using configuration bits in AUTH\_CFG and AUTH\_LIM bytes.

ams Datasheet Page 33 **Document Feedback**

#### Configuration Byte CHIP\_KILL

Figure 36: Configuration Byte CHIP\_KILL

| Conf. Bit | Name        | Default | Function                                    | Note |

|-----------|-------------|---------|---------------------------------------------|------|

| b7        | chip_kill_2 | 0       | 1: Tunneling and Extended mode are disabled |      |

| b6        | chip_kill_1 | 0       | 1: RF communication part is disabled        |      |

| b5        | rfu         | 0       |                                             |      |

| b4        | rfu         | 0       |                                             |      |

| b3        | rfu         | 0       |                                             |      |

| b2        | rfu         | 0       |                                             |      |

| b1        | rfu         | 0       |                                             |      |

| b0        | rfu         | 0       |                                             |      |

#### Note(s) and/or Footnote(s):

1. This byte can always be accessed for read and write via the SPI / I<sup>2</sup>C and can't be accessed for read and write from the RF side.

By setting CHIP\_KILL byte the RF communication part of the chip or Tunneling and Extended mode will be disabled permanently. At its initial state, the CHIP\_KILL byte is set to value 00h. The value of this byte can be changed via SPI / I<sup>2</sup>C. If bit b6 is set to value 1, the RF part of the chip shall be disabled and AS3955 will not respond to any command received from a NFC device. By setting bit b7 to 1, Tunneling and Extended mode will be disabled.

Page 34 ams Datasheet [v1-01] 2015-Apr-29

#### Configuration Byte AUTH\_CNT

Figure 37: **Configuration Byte AUTH\_CNT**

| Conf. Bit | Name         | Default | Function                 | Note |

|-----------|--------------|---------|--------------------------|------|

| b7        | rfu          | 0       |                          |      |

| b6        | auth_cnt2<2> | 1       |                          |      |

| b5        | auth_cnt2<1> | 1       | Authentication counter 2 |      |

| b4        | auth_cnt2<0> | 1       |                          |      |

| b3        | rfu          | 0       |                          |      |

| b2        | auth_cnt1<2> | 1       |                          |      |

| b1        | auth_cnt1<1> | 1       | Authentication counter 1 |      |

| b0        | auth_cnt1<0> | 1       |                          |      |

#### Note(s) and/or Footnote(s):

1. This byte can always be accessed for read and write via the SPI /  $I^2C$  and can't be accessed for read and write from the RF side.

This byte indicates the number of allowed unsuccessful authentication attempts over RF available before disabling the chip. The byte consists of two separate counters where the second counter is a copy of the first counter.

These counters are updated at each failed authentication. At each successful authentication, counters are reset to 7 and, at each unsuccessful authentication attempt, counters are decreased by one. If the value of the counters reaches 0, the chip will be permanently locked and cannot be authenticated any longer over the RF field. The chip will also be locked in case the two counter values don't match. The lock can always be cleared via SPI / I<sup>2</sup>C interface.

ams Datasheet Page 35 Document Feedback

#### Configuration Byte AUTH\_LIM

Figure 38: Configuration Byte AUTH\_LIM

| Conf. Bit | Name          | Default | Function                                                                          | Note |

|-----------|---------------|---------|-----------------------------------------------------------------------------------|------|

| b7        | auth_lim<7>   | 1       |                                                                                   |      |

| b6        | auth_lim<6>   | 1       |                                                                                   |      |

| b5        | auth_lim<5>   | 1       | AUTH_LIM defines the block address above which password verification is required. |      |

| b4        | auth_lim<4>   | 1       |                                                                                   |      |

| b3        | auth_lim<3>   | 1       |                                                                                   |      |

| b2        | auth_lim<2>   | 1       |                                                                                   |      |

| b1        | auth_lim<1>   | 1       |                                                                                   |      |

| b0        | auth_lim<0> 1 |         |                                                                                   |      |

#### Note(s) and/or Footnote(s):

1. This byte can always be accessed for read and write via SPI / I<sup>2</sup>C and can be accessed for read and write from the RF side if chip is in AUTHENTICATED state and configuration bit *auth\_set* is 1.

AUTH\_LIM defines the block address above which password verification is required. Valid address range for the AUTH\_LIM byte is from 00h to FFh. If AUTH\_LIM is set to a block address higher than the last block of the EEPROM address space, the password protection is effectively disabled. Addresses above the limit are protected for read / write depending on <code>auth\_r</code> and <code>auth\_w</code> values. If no bits are set, password protection is disabled.

If the NFC device tries to access protected blocks without authenticating first, then:

- If only protected blocks are accessed, AS3955 will not respond

- If protected and unprotected blocks are accessed<sup>1</sup>, AS3955 will return actual stored values only for the unprotected portion, and zeroes for the protected portion.

Page 36

Document Feedback

[v1-01] 2015-Apr-29

<sup>1.</sup> This can occur, for instance, with a READ command crossing the border between protected and unprotected memory.

## Configuration Byte AUTH\_CFG

Figure 39: **Configuration Byte AUTH\_CFG**

| Conf. Bit | Name      | Default | Function                               | Note |

|-----------|-----------|---------|----------------------------------------|------|

| b7        | rfu       | 0       |                                        |      |

| b6        | rfu       | 0       |                                        |      |

| b5        | rfu       | 0       |                                        |      |

| b4        | rfu       | 0       |                                        |      |

| b3        | rfu       | 0       |                                        |      |

| b2        | rfu       | 0       |                                        |      |

| b1        | auth_w<1> | 0       | Authentication is required for writing |      |

| b0        | auth_r<0> | 0       | Authentication is required for reading |      |

#### Note(s) and/or Footnote(s):

1. This byte can always be accessed for read and write via SPI /  $I^2C$  and can be accessed for read and write from the RF side if chip is in AUTHENTICATED state and configuration bit *auth\_set* is 1.

> Bits *auth\_w* and *auth\_r* define for which operations the authentication is needed. If a lock bit is set for a certain block, then write cannot be performed even if IC is in AUTHENTICATED state. This means that lock bits overrule authentication.

**Configuration Byte SENSR1**

Figure 40: **Configuration Byte SENSR1**

| Conf. Bit | Name         | Default | Function                             | Note |

|-----------|--------------|---------|--------------------------------------|------|

| b7        | sens_res<15> | 0       |                                      |      |

| b6        | sens_res<14> | 0       |                                      |      |

| b5        | sens_res<13> | 0       |                                      |      |

| b4        | sens_res<12> | 0       | SENS_RES response byte 2 on SENS_REQ |      |

| b3        | sens_res<11> | 0       | SENS_NES response byte 2 on SENS_NEQ |      |

| b2        | sens_res<10> | 0       |                                      |      |

| b1        | sens_res<9>  | 0       |                                      |      |

| b0        | sens_res<8>  | 0       |                                      |      |

## Note(s) and/or Footnote(s):

1. This byte can always be accessed for read and write via SPI /  $I^2C$  and can be accessed for read and write from the RF side if  $rfcfg\_en$ is set to 1.

ams Datasheet Page 37

# **Configuration Byte SENSR2**

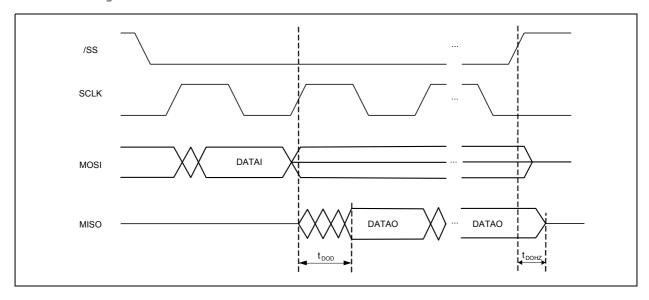

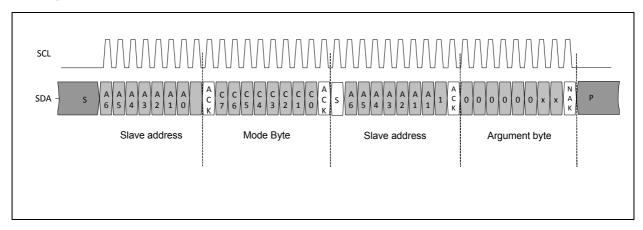

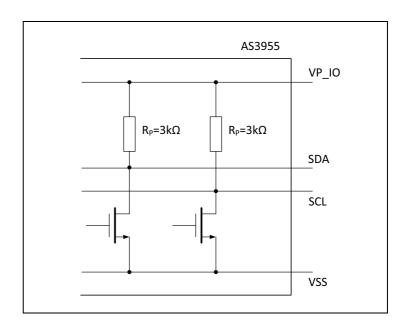

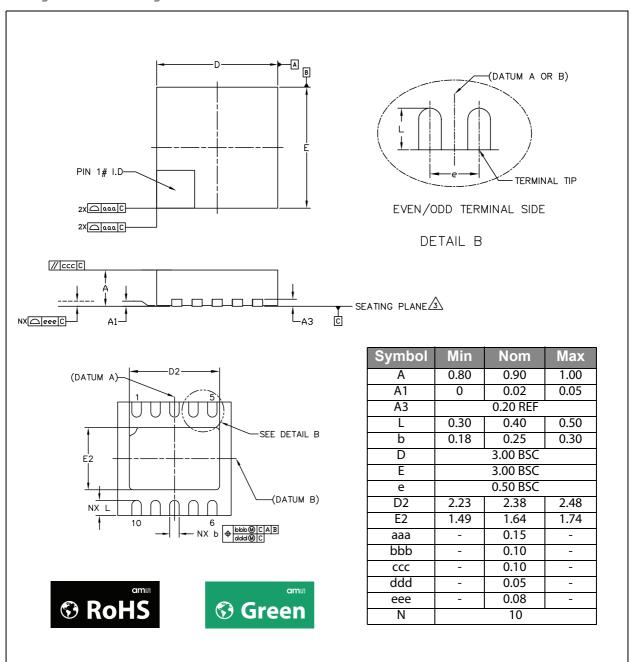

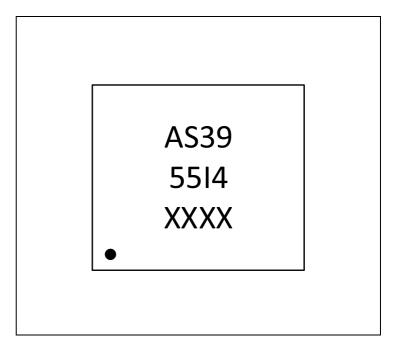

Figure 41: **Configuration Byte SENSR2**