### **Datasheet**

DS000667

# **AS7421**

**64-Channel Hyperspectral NIR Sensor**

v2-00 • 2022-Oct-13

# **Content Guide**

| 1                                      | General Description 3                               |

|----------------------------------------|-----------------------------------------------------|

| 1.1<br>1.2<br>1.3                      | Key Benefits & Features3Applications4Block Diagram4 |

| 2                                      | Ordering Information5                               |

| 3                                      | Pin Assignment 6                                    |

| 3.1<br>3.2                             | Pin Diagram6 Pin Description6                       |

| 4                                      | Absolute Maximum Ratings 8                          |

| 5                                      | Electrical Characteristics9                         |

| 6                                      | Typical Operating Characteristics14                 |

| 7                                      | Functional Description 16                           |

| 7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6 | Device Architecture                                 |

| 8                                      | Device and System Calibration 21                    |

| 9                               | I <sup>2</sup> C Interface                                                                                                           | 23             |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 9.1<br>9.2<br>9.3<br>9.4<br>9.5 | I <sup>2</sup> C Address I <sup>2</sup> C Write Transaction I <sup>2</sup> C Read Transaction Timing Characteristics Timing Diagrams | 23<br>24<br>24 |

| 10                              | Register Description                                                                                                                 | 26             |

| 10.1<br>10.2                    | Register Overview Detailed Register Description                                                                                      |                |

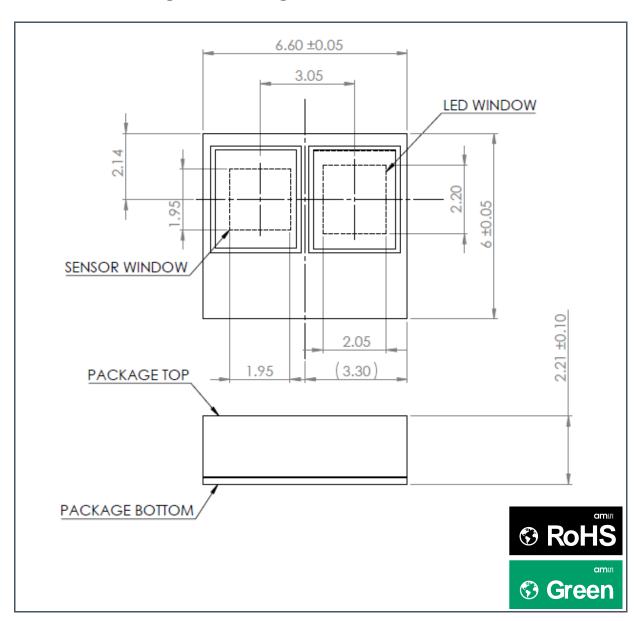

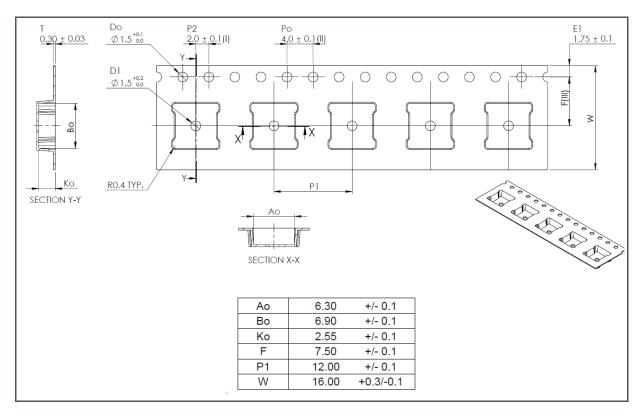

| 11                              | Package Drawings & Marking                                                                                                           | gs 45          |

| 11.1                            | Package Drawings                                                                                                                     | 45             |

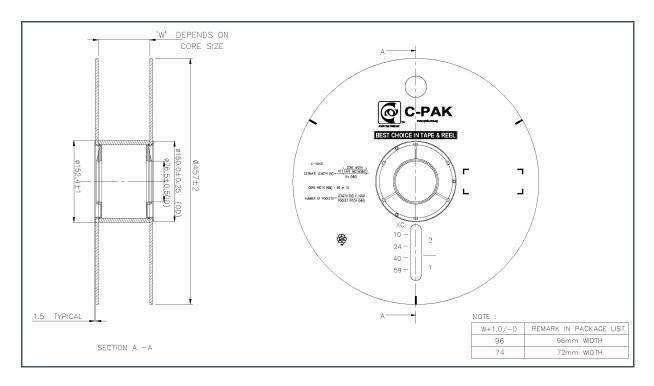

| 12                              | Tape & Reel Information                                                                                                              | 48             |

| 13                              | Soldering & Storage Informa                                                                                                          | tion 50        |

| 14                              | Revision Information                                                                                                                 | 51             |

| 15                              | I egal Information                                                                                                                   | 52             |

# 1 General Description

AS7421 is a 64-channel near infrared digital spectrometer for spectral identification and spectral footprint analysis used in consumer devices. The spectral response of the sensor is defined in the wavelengths from approximately 750 nm to 1050 nm and the channels are equally distributed over the mentioned range. Once a spectral measurement is started, all 64 channels are processed automatically by 16 parallel sampling ADCs with four consecutive integration cycles.

AS7421 integrates Fabry-Perot filters into standard CMOS silicon via nano-optic deposited interference filter technology and its package provides a built in aperture and micro optics to control the light entering the sensor array. In addition, the module provides a near infrared (NIR) light source and an integrated LED driver to control it.

Control and spectral data access is implemented through a serial I<sup>2</sup>C interface. A GPIO and an interrupt signal are available to start/synchronize the spectral measurement as well as minimize I<sup>2</sup>C traffic.

### 1.1 Key Benefits & Features

The benefits and features of AS7421, 64-Channel Hyperspectral NIR Sensor, are listed below:

Figure 1: Added Value of Using AS7421

| Benefits                                                                                       | Features                                                                                                                             |

|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| Miniaturized reflectance/absorbance spectral analysis and material identification in NIR range | 61 individual and 4 special purpose spectral channels with a FWHM of typical 10 nm 16-bit full scale resolution per spectral channel |

| Fast measurement time                                                                          | 16 parallel sampling ADCs with individual gain settings                                                                              |

| - ast measurement time                                                                         | 256 ms to obtain measurement data for all 64 channels                                                                                |

|                                                                                                | Integrated 64-channel sensor with on-chip Fabry-Perot filters                                                                        |

| High module integration and low BOM                                                            | Integrated NIR light source (LED) to cover 750 - 1050 nm range                                                                       |

|                                                                                                | Integrated programmable LED driver                                                                                                   |

|                                                                                                | Integrated optics to limit AOI on sensor                                                                                             |

|                                                                                                | 3.3 V VDD operation                                                                                                                  |

| Low power consumption and minimum I <sup>2</sup> C traffic                                     | Configurable sleep mode                                                                                                              |

|                                                                                                | Interrupt-driven device                                                                                                              |

| Synchronization of spectral measurement                                                        | Configurable GPIO to trigger/sync spectral measurements                                                                              |

| Benefits                                                          | Features                                                                                                                                              |

|-------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| Full calibration augment package available for                    | Calibration library support which includes data post-processing of spectral raw data                                                                  |

| Full calibration support package available for sensor integration | Data output options: raw data, absorbance spectra, 1 <sup>st</sup> derivative of absorbance spectra, 2 <sup>nd</sup> derivative of absorbance spectra |

# 1.2 Applications

- Spectral material identification of goods and fabrics

- Moisture measurements in industrial or agricultural environments

- Brix and dry matter measurements of fruits (fruit ripeness)

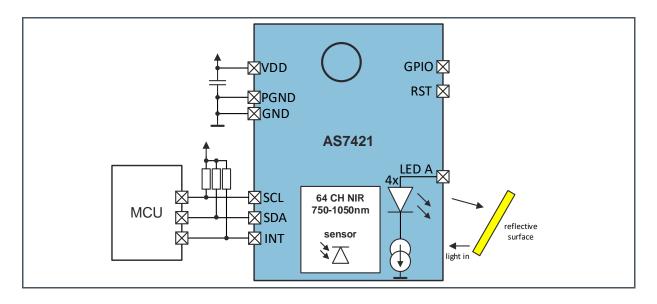

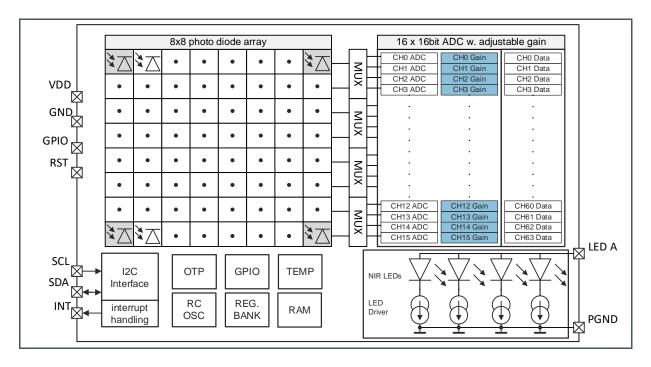

## 1.3 Block Diagram

The functional blocks of this device are shown below:

Figure 2: Functional Blocks of AS7421

# 2 Ordering Information

| Ordering Code | Package | Marking | Delivery Form | Delivery Quantity |

|---------------|---------|---------|---------------|-------------------|

| AS7421-ZLGT   | OLGA-10 | AS7421  | Tape & Reel   | 2000 pcs/reel     |

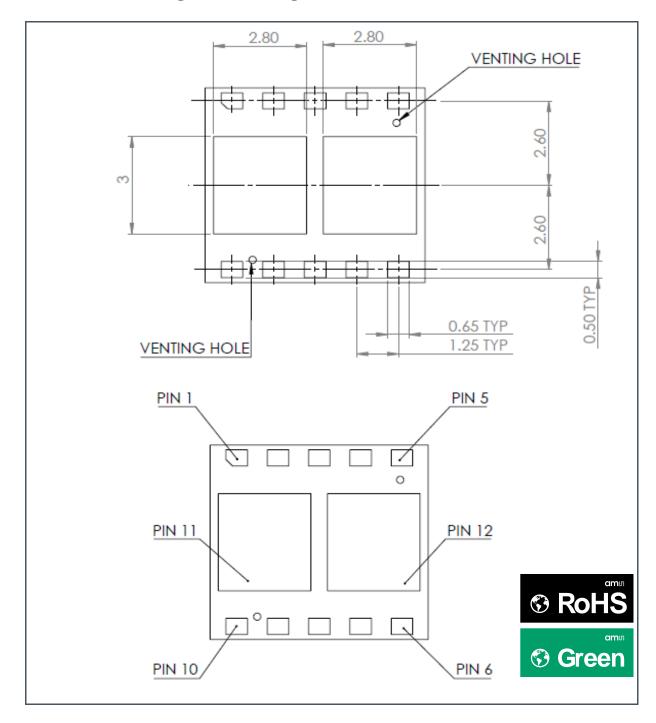

# 3 Pin Assignment

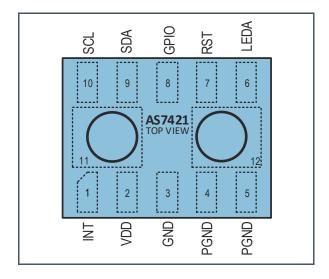

## 3.1 Pin Diagram

Figure 3: Pin Assignment of AS7421 (TOP VIEW)

### 3.2 Pin Description

Figure 4: Pin Description of AS7421

| Pin Name | Pin Type <sup>(1)</sup>               | Description                                                                           |

|----------|---------------------------------------|---------------------------------------------------------------------------------------|

| INT      | DO_OD                                 | Interrupt. Open drain output. Connect pull up resistor to 1.8 V or 3.3 V. Active low. |

| VDD      | Р                                     | Positive supply terminal.                                                             |

| GND      | Р                                     | Ground. All voltages referenced to GND.                                               |

| PGND     | Р                                     | Ground. All voltages referenced to GND.                                               |

| PGND     | A_I                                   | Ground. All voltages referenced to GND.                                               |

| LED A    | A_I                                   | Supply voltage for NIR LEDs anode.                                                    |

| RST      | DI                                    | Reset input with internal pull down resistor. Active high.                            |

| GPIO     | D_I/O                                 | General purpose input/output.                                                         |

|          | INT  VDD  GND  PGND  PGND  LED A  RST | INT DO_OD  VDD P  GND P  PGND P  PGND A_I  LED A A_I  RST DI                          |

| Pin Number | Pin Name | Pin Type <sup>(1)</sup> | Description                                                                                                     |

|------------|----------|-------------------------|-----------------------------------------------------------------------------------------------------------------|

| 9          | SDA      | D_I/O                   | Serial Interface data signal line for I <sup>2</sup> C interface.  Connect pull up resistor to 1.8 V or 3.3 V.  |

| 10         | SCL      | DI                      | Serial Interface clock signal line for I <sup>2</sup> C interface.  Connect pull up resistor to 1.8 V or 3.3 V. |

| 11         | GND      | Р                       | Exposed pad, connect to GND with thermal vias.                                                                  |

| 12         | LED A    | A_I                     | Exposed pad, connect to LED A.                                                                                  |

(1) Explanation of abbreviations:

DI Digital Input

D\_I/O Digital Input/Output

DO\_OD Digital Output, open drain

P Power pin A\_I Analog input

# **Absolute Maximum Ratings**

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated under "Electrical Conditions" is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

**Absolute Maximum Ratings of AS7421**

| Symbol                             | Parameter                                  | Min  | Max     | Unit | Comments                             |

|------------------------------------|--------------------------------------------|------|---------|------|--------------------------------------|

| Electrical Pa                      | arameters                                  |      |         |      |                                      |

| V <sub>DD</sub> / V <sub>GND</sub> | Supply voltage to ground                   | -0.3 | 3.6     | V    | Applicable for pin VDD               |

| $V_{LEDA}$                         | LEDA voltage to ground                     | -0.3 | 3.6     | V    | Applicable for pin LEDA              |

| $V_{DIG\_MAX}$                     | Digital pins                               | -0.3 | VDD+0.3 | V    | Applicable for pins SCL, SDA and INT |

| I <sub>SCR</sub>                   | Input current (latch-up immunity)          | ±    | 100     | mA   | JESD78E                              |

| Continuous                         | Power Dissipation (T <sub>A</sub> = 70 °C) |      |         |      |                                      |

| P <sub>T</sub>                     | Continuous power dissipation               |      | 1.4     | W    | Including LEDs and sensor            |

| Electrostation                     | : Discharge                                |      |         |      |                                      |

| ESD <sub>HBM</sub>                 | Electrostatic discharge HBM                | ±    | 2000    | V    | JS-001-2017                          |

| ESD <sub>CDM</sub>                 | Electrostatic discharge CDM                | ±    | 500     | V    | JS-002-2014                          |

| Temperature                        | Ranges and Storage Conditions              |      |         |      |                                      |

| T <sub>A</sub>                     | Ambient temperature                        | -30  | +85     | °C   |                                      |

| R <sub>THJA</sub>                  | Junction to ambient thermal resistance     |      | 85      | K/W  | Depending on actual PCB layout. (2)  |

| T <sub>STRG</sub>                  | Storage temperature range                  | -40  | +85     | °C   |                                      |

| T <sub>BODY</sub>                  | Package body temperature                   |      | 260     | °C   | IPC/JEDEC J-STD-020 <sup>(1)</sup>   |

| R <sub>HNC</sub>                   | Relative humidity (non-condensing)         | 5    | 85      | %    |                                      |

| MSL                                | Moisture sensitivity level                 |      | 3       |      | Maximum floor life time of 168h      |

The reflow peak soldering temperature (body temperature) is specified according to IPC/JEDEC J-STD-020 "Moisture/Reflow Sensitivity Classification for Nonhermetic Solid State Surface Mount Devices." The lead finish for Pbfree leaded packages is "Matte Tin" (100 % Sn).

Value defined for PCB using 5x5mm copper area on bottom side of PCB. Thermal vias used to connect exposed pad (2) from TOP layer with bottom layer. Contact ams OSRAM for guidelines on thermal management.

# **5** Electrical Characteristics

All limits are guaranteed. The parameters with Min and Max values are guaranteed with production tests or SQC (Statistical Quality Control) methods. All voltages with respect to GND/PGND. Device parameters are guaranteed at  $V_{DD}=3.3~V$  and  $T_A=25~C$  unless otherwise noted.

Figure 6: Electrical Characteristics of AS7421

| Symbol                    | Parameter                                           | Conditions                                                                   | Min  | Тур | Max    | Unit |

|---------------------------|-----------------------------------------------------|------------------------------------------------------------------------------|------|-----|--------|------|

| $V_{DD}$                  | Supply voltage                                      |                                                                              | 3    | 3.3 | 3.6    | V    |

| $V_{LEDA}$                | LED supply voltage                                  | ILED = 75 mA                                                                 |      | 2.8 | 3.0(1) | V    |

| f <sub>OSC</sub>          | Oscillator frequency                                |                                                                              |      | 8   |        | MHz  |

| T <sub>A</sub>            | Operating free-air temperature                      |                                                                              | -30  | 25  | 60     | °C   |

| TJ                        | Operating junction temperature                      |                                                                              | -30  | 25  | 65     | °C   |

| T <sub>OVTEMP</sub>       | Overtemperature shutdown                            |                                                                              |      | 150 | 165    | °C   |

| Power Consu               | mption                                              |                                                                              |      |     |        |      |

|                           |                                                     | $V_{DD}$ = 3.3 V; $T_A$ = 25°C<br>Active mode <sup>(2)</sup>                 |      | 2.5 | 5      | mA   |

| I <sub>DD</sub>           | Supply current                                      | V <sub>DD</sub> = 3.3 V; T <sub>A</sub> = 25 °C<br>Idle mode <sup>(3)</sup>  |      | 400 |        | μA   |

|                           |                                                     | V <sub>DD</sub> = 3.3 V; T <sub>A</sub> = 25 °C<br>Sleep mode <sup>(4)</sup> |      | 2   | 4      | μΑ   |

| Digital Pins              |                                                     |                                                                              |      |     |        |      |

| V <sub>IH</sub>           | SCL, SDA input high voltage                         |                                                                              | 1.26 |     |        | V    |

| V <sub>IL</sub>           | SCL, SDA input low voltage                          |                                                                              |      |     | 0.54   | V    |

| V <sub>OL</sub>           | INT, SDA output low voltage                         | 6 mA sink current                                                            |      |     | 0.4    | V    |

| Cı                        | Input pin capacitance                               |                                                                              |      |     | 10     | pF   |

| I <sub>leak</sub>         | Leakage current into<br>SCL, SDA, INT,<br>GPIO pins |                                                                              |      |     | 1.5    | μA   |

| LED Driver                |                                                     |                                                                              |      |     |        |      |

| I <sub>LED_ACCURACY</sub> | Absolute ILED accuracy                              | ILED = $50 \text{ mA}$<br>T <sub>A</sub> = $25^{\circ}\text{C}$              | -30  |     | +30    | %    |

| V <sub>COMP</sub>         | Compliance voltage of current sink                  | ILED = 75 mA                                                                 |      |     | 500    | mV   |

| LED                       |                                                     |                                                                              |      |     |        |      |

| $V_{f\_LED1}$             | Forward voltage                                     | I <sub>F</sub> = 25 mA                                                       |      | 2.0 |        | V    |

| Symbol              | Parameter       | Conditions             | Min | Тур  | Max | Unit |

|---------------------|-----------------|------------------------|-----|------|-----|------|

| $V_{f\_LED2}$       | Forward voltage | $I_F = 25 \text{ mA}$  |     | 1.6  |     | V    |

| $V_{f\_LED3}$       | Forward voltage | $I_F = 25 \text{ mA}$  |     | 1.25 |     | V    |

| $V_{f\_LED4}$       | Forward voltage | $I_F = 25 \text{ mA}$  |     | 1.25 |     | V    |

| $\lambda_{p\_LED1}$ | Peak wavelength | $I_F = 25 \text{ mA}$  |     | 760  |     | nm   |

| $\lambda_{p\_LED2}$ | Peak wavelength | $I_F = 25 \text{ mA}$  |     | 830  |     | nm   |

| $\lambda_{p\_LED3}$ | Peak wavelength | I <sub>F</sub> = 25 mA |     | 950  |     | nm   |

| $\lambda_{p\_LED4}$ | Peak wavelength | I <sub>F</sub> = 25 mA |     | 1040 |     | nm   |

- (1) VDD must be applied before VLEDA during power on. VLEDA must always be smaller or equal than VDD+0.3 V.

- (2) Active state occurs during ongoing spectral measurement AEN = "1" and power consumption defined without LED current.

- (3) Idle state occurs when PON = "1" and all functions are disabled.

- (4) Sleep state occurs when PON = "0" and no active I<sup>2</sup>C communication.

Figure 7:

Optical Characteristics of AS7421, Integration Time = 65.5 ms (unless otherwise noted)

| Symbol                | Parameter                                        | Conditions                                                | Min | Тур                  | Max | Unit   |

|-----------------------|--------------------------------------------------|-----------------------------------------------------------|-----|----------------------|-----|--------|

| FWHM                  | Full width half maximum of filter <sup>(8)</sup> |                                                           |     | 10                   |     | nm     |

| $\lambda_{\text{s}}$  | Peak Wavelength<br>Separation                    |                                                           |     | 5                    |     | nm     |

| dark                  | Dark ADC count value                             | Ee = 0 μW/cm²<br>AGAIN: 128x<br>Integration time: 65.5 ms |     |                      | 5   | counts |

|                       |                                                  | AGAIN: 1x                                                 |     | 1                    |     |        |

|                       |                                                  | AGAIN: 2x                                                 |     | 2                    |     | _      |

|                       |                                                  | AGAIN: 4x                                                 |     | 4                    |     | _      |

|                       | Optical gain ratios, relative to 1x gain setting | AGAIN: 8x                                                 |     | 8                    |     | _      |

| Gain ratio            |                                                  | AGAIN: 16x                                                |     | 16                   |     |        |

|                       |                                                  | AGAIN: 32x                                                |     | 32                   |     | _      |

|                       |                                                  | AGAIN: 64x                                                |     | 64                   |     | _      |

|                       |                                                  | AGAIN: 128x                                               |     | 128                  |     | _      |

|                       |                                                  | AGAIN: 256x                                               |     | 256                  |     | _      |

| SNR <sub>SYSTEM</sub> | Signal to noise ratio of optical system (1) (2)  | Range: 750 nm – 1050 nm                                   | 500 |                      |     |        |

| ImSR                  | Intra-module spectral repeatability (1) (3)      | Range: 750 nm – 1050 nm                                   |     |                      | 0.5 | %      |

| IMSR                  | Inter-module spectral repeatability (1) (4)      | Range: 750 nm – 1050 nm                                   |     |                      | 5   | %      |

| W <sub>acc</sub>      | Wavelength accuracy (1) (7)                      |                                                           |     |                      | 5   | nm     |

| t <sub>int</sub>      | Integration time (5)                             |                                                           | 0.5 | 65.5                 | 256 | ms     |

| t <sub>64CH</sub>     | Measurement time for all 64 channel (6)          |                                                           |     | 4 x t <sub>int</sub> |     | ms     |

| f                     | Field of view of single photo diode              |                                                           | -10 |                      | 10  | deg    |

- (1) Parameter not tested in final test but guaranteed by design and validation.

- Verified with raw spectral data collected with reflectance standard sample (RSS) with reflectance of 99% (white diffusive target). Average and standard deviation is calculated for each channel ( $\lambda_{CH}$ ) for 10 measurements. SNR<sub>SYSTEM</sub> =  $\mu(\lambda_{CH})$  /  $\sigma(\lambda_{CH})$ .

- (3) Verified with raw spectral data collected with reflectance standard sample (RSS, 10 measurements per channel) with reflectance of 99% (white diffusive target) and wavelength calibration standard zenith polymer (WCS, 100 measurements per channel).

- (4) Verified with raw spectral data collected with reflectance standard sample (RSS, 10 measurements per channel for 10 devices) with reflectance of 99% (white diffusive target) and wavelength calibration standard zenith polymer (WCS, 100 measurements per channel for 10 devices).

- (5) 65.5 ms integration time to achieve 16-bit count value (depending on amount of light reflected to sensor)

- (6) 4 integration cycles are done automatically to process all 64 channels.

- (7) Verified after full sensor calibration. Raw spectral data recorded for each channel with wavelength calibration standard zenith polymer (WCS, 10 measurements per channel).

- (8) Parameter verified with collimated light at 0° AOI (angle of incidence).

Figure 8: Typical Irradiance Responsivity of AS7421, Integration Time = 65.5 ms (unless otherwise noted)

| Symbol              | Parameter               | Conditions                                    | Min | Тур | Max | Unit              |

|---------------------|-------------------------|-----------------------------------------------|-----|-----|-----|-------------------|

| R <sub>e_PD0</sub>  | Irradiance responsivity | AGAIN: 64x; λ <sub>p</sub> : 830 nm           |     | 406 |     | counts / (µW/cm²) |

| R <sub>e_PD1</sub>  | Irradiance responsivity | AGAIN: $64x$ ; $\lambda_p$ : 750 nm           |     | 431 |     | counts / (µW/cm²) |

| R <sub>e_PD2</sub>  | Irradiance responsivity | AGAIN: $64x$ ; $\lambda_p$ : 790 nm           |     | 409 |     | counts / (µW/cm²) |

| R <sub>e_PD3</sub>  | Irradiance responsivity | AGAIN: 64x; λ <sub>p</sub> : 870 nm           |     | 296 |     | counts / (µW/cm²) |

| R <sub>e_PD4</sub>  | Irradiance responsivity | AGAIN: $64x$ ; $\lambda_p$ : $940 \text{ nm}$ |     | 190 |     | counts / (µW/cm²) |

| R <sub>e_PD5</sub>  | Irradiance responsivity | AGAIN: $64x$ ; $\lambda_p$ : $980 \text{ nm}$ |     | 112 |     | counts / (µW/cm²) |

| R <sub>e_PD6</sub>  | Irradiance responsivity | AGAIN: 128x; $\lambda_p$ : 1020 nm            |     | 105 |     | counts / (µW/cm²) |

| R <sub>e_PD7</sub>  | Irradiance responsivity | AGAIN: $64x$ ; $\lambda_p$ : $830 \text{ nm}$ |     | 385 |     | counts / (µW/cm²) |

| R <sub>e_PD8</sub>  | Irradiance responsivity | AGAIN: $64x$ ; $\lambda_p$ : $760 \text{ nm}$ |     | 394 |     | counts / (µW/cm²) |

| R <sub>e_PD9</sub>  | Irradiance responsivity | AGAIN: $64x$ ; $\lambda_p$ : $800 \text{ nm}$ |     | 422 |     | counts / (µW/cm²) |

| R <sub>e_PD10</sub> | Irradiance responsivity | AGAIN: $64x$ ; $\lambda_p$ : $840 \text{ nm}$ |     | 385 |     | counts / (µW/cm²) |

| R <sub>e_PD11</sub> | Irradiance responsivity | AGAIN: $64x$ ; $\lambda_p$ : $880 \text{ nm}$ |     | 344 |     | counts / (µW/cm²) |

| R <sub>e_PD12</sub> | Irradiance responsivity | AGAIN: $64x$ ; $\lambda_p$ : $930 \text{ nm}$ |     | 235 |     | counts / (µW/cm²) |

| R <sub>e_PD13</sub> | Irradiance responsivity | AGAIN: $64x$ ; $\lambda_p$ : 970 nm           |     | 151 |     | counts / (µW/cm²) |

| R <sub>e_PD14</sub> | Irradiance responsivity | AGAIN: 128x; $\lambda_p$ : 1010 nm            |     | 148 |     | counts / (µW/cm²) |

| R <sub>e_PD15</sub> | Irradiance responsivity | AGAIN: 128x; $\lambda_p$ : 1050 nm            |     | 61  |     | counts / (µW/cm²) |

| R <sub>e_PD16</sub> | Irradiance responsivity | AGAIN: 64x; λ <sub>p</sub> : 770 nm           |     | 398 |     | counts / (µW/cm²) |

| R <sub>e_PD17</sub> | Irradiance responsivity | AGAIN: 64x; λ <sub>p</sub> : 810 nm           |     | 416 |     | counts / (µW/cm²) |

| R <sub>e_PD18</sub> | Irradiance responsivity | AGAIN: 64x; λ <sub>p</sub> : 850 nm           |     | 390 |     | counts / (µW/cm²) |

| R <sub>e_PD19</sub> | Irradiance responsivity | AGAIN: 64x; λ <sub>p</sub> : 890 nm           |     | 367 |     | counts / (µW/cm²) |

| R <sub>e_PD20</sub> | Irradiance responsivity | AGAIN: 64x; λ <sub>p</sub> : 920 nm           |     | 253 |     | counts / (µW/cm²) |

| R <sub>e_PD21</sub> | Irradiance responsivity | AGAIN: 64x; λ <sub>p</sub> : 960 nm           |     | 166 |     | counts / (µW/cm²) |

| R <sub>e_PD22</sub> | Irradiance responsivity | AGAIN: 128x; $\lambda_p$ : 1000 nm            |     | 180 |     | counts / (µW/cm²) |

| R <sub>e_PD23</sub> | Irradiance responsivity | AGAIN: 128x; $\lambda_p$ : 1040 nm            |     | 74  |     | counts / (µW/cm²) |

| R <sub>e_PD24</sub> | Irradiance responsivity | AGAIN: $64x$ ; $\lambda_p$ : $780 \text{ nm}$ |     | 398 |     | counts / (µW/cm²) |

| R <sub>e_PD25</sub> | Irradiance responsivity | AGAIN: $64x$ ; $\lambda_p$ : $820 \text{ nm}$ |     | 411 |     | counts / (µW/cm²) |

| R <sub>e_PD26</sub> | Irradiance responsivity | AGAIN: $64x$ ; $\lambda_p$ : $860 \text{ nm}$ |     | 405 |     | counts / (µW/cm²) |

| R <sub>e_PD27</sub> | Irradiance responsivity | AGAIN: $64x$ ; $\lambda_p$ : 900 nm           |     | 363 |     | counts / (µW/cm²) |

| R <sub>e_PD28</sub> | Irradiance responsivity | AGAIN: $64x$ ; $\lambda_p$ : $910 \text{ nm}$ |     | 286 |     | counts / (µW/cm²) |

| R <sub>e_PD29</sub> | Irradiance responsivity | AGAIN: 64x; λ <sub>p</sub> : 950 nm           |     | 189 |     | counts / (µW/cm²) |

| R <sub>e_PD30</sub> | Irradiance responsivity | AGAIN: 128x; $\lambda_p$ : 990 nm             |     | 206 |     | counts / (µW/cm²) |

| R <sub>e_PD31</sub> | Irradiance responsivity | AGAIN: 128x; $\lambda_p$ : 1030 nm            |     | 92  |     | counts / (µW/cm²) |

| R <sub>e_PD32</sub> | Irradiance responsivity | AGAIN: 64x; λ <sub>p</sub> : 775 nm           |     | 401 |     | counts / (µW/cm²) |

| R <sub>e_PD33</sub> | Irradiance responsivity | AGAIN: 64x; λ <sub>p</sub> : 815 nm           |     | 430 |     | counts / (µW/cm²) |

| R <sub>e_PD34</sub> | Irradiance responsivity | AGAIN: 64x; λ <sub>p</sub> : 855 nm           |     | 401 |     | counts / (µW/cm²) |

| R <sub>e_PD35</sub> | Irradiance responsivity | AGAIN: 64x; λ <sub>p</sub> : 895 nm           |     | 370 |     | counts / (µW/cm²) |

| R <sub>e_PD36</sub> | Irradiance responsivity | AGAIN: 64x; λ <sub>p</sub> : 905 nm           |     | 304 |     | counts / (µW/cm²) |

| R <sub>e_PD37</sub> | Irradiance responsivity | AGAIN: 64x; λ <sub>p</sub> : 945 nm           |     | 209 |     | counts / (µW/cm²) |

| R <sub>e_PD38</sub> | Irradiance responsivity | AGAIN: 128x; $\lambda_p$ : 985 nm     | 225 | counts / (µW/cm²) |

|---------------------|-------------------------|---------------------------------------|-----|-------------------|

| R <sub>e_PD39</sub> | Irradiance responsivity | AGAIN: 128x; λ <sub>p</sub> : 1025 nm | 104 | counts / (µW/cm²) |

| R <sub>e_PD40</sub> | Irradiance responsivity | AGAIN: 64x; λ <sub>p</sub> : 765 nm   | 397 | counts / (µW/cm²) |

| R <sub>e_PD41</sub> | Irradiance responsivity | AGAIN: 64x; λ <sub>p</sub> : 805 nm   | 418 | counts / (µW/cm²) |

| R <sub>e_PD42</sub> | Irradiance responsivity | AGAIN: 64x; λ <sub>p</sub> : 845 nm   | 371 | counts / (µW/cm²) |

| R <sub>e_PD43</sub> | Irradiance responsivity | AGAIN: 64x; λ <sub>p</sub> : 885 nm   | 354 | counts / (µW/cm²) |

| R <sub>e_PD44</sub> | Irradiance responsivity | AGAIN: 64x; λ <sub>p</sub> : 915 nm   | 269 | counts / (µW/cm²) |

| R <sub>e_PD45</sub> | Irradiance responsivity | AGAIN: 64x; λ <sub>p</sub> : 955 nm   | 177 | counts / (µW/cm²) |

| R <sub>e_PD46</sub> | Irradiance responsivity | AGAIN: 128x; λ <sub>p</sub> : 995 nm  | 203 | counts / (µW/cm²) |

| R <sub>e_PD47</sub> | Irradiance responsivity | AGAIN: 128x; λ <sub>p</sub> : 1035 nm | 90  | counts / (µW/cm²) |

| R <sub>e_PD48</sub> | Irradiance responsivity | AGAIN: 64x; λ <sub>p</sub> : 755 nm   | 375 | counts / (µW/cm²) |

| R <sub>e_PD49</sub> | Irradiance responsivity | AGAIN: 64x; λ <sub>p</sub> : 795 nm   | 401 | counts / (µW/cm²) |

| R <sub>e_PD50</sub> | Irradiance responsivity | AGAIN: 64x; λ <sub>p</sub> : 835 nm   | 387 | counts / (µW/cm²) |

| R <sub>e_PD51</sub> | Irradiance responsivity | AGAIN: 64x; λ <sub>p</sub> : 875 nm   | 320 | counts / (µW/cm²) |

| R <sub>e_PD52</sub> | Irradiance responsivity | AGAIN: 64x; λ <sub>p</sub> : 926 nm   | 239 | counts / (µW/cm²) |

| R <sub>e_PD53</sub> | Irradiance responsivity | AGAIN: 64x; λ <sub>p</sub> : 965 nm   | 163 | counts / (µW/cm²) |

| R <sub>e_PD54</sub> | Irradiance responsivity | AGAIN: 128x; λ <sub>p</sub> : 1005 nm | 169 | counts / (µW/cm²) |

| R <sub>e_PD55</sub> | Irradiance responsivity | AGAIN: 128x; λ <sub>p</sub> : 1045 nm | 74  | counts / (µW/cm²) |

| R <sub>e_PD56</sub> | Irradiance responsivity | AGAIN: 64x; λ <sub>p</sub> : 830 nm   | 403 | counts / (µW/cm²) |

| R <sub>e_PD57</sub> | Irradiance responsivity | AGAIN: 64x; λ <sub>p</sub> : 785 nm   | 413 | counts / (µW/cm²) |

| R <sub>e_PD58</sub> | Irradiance responsivity | AGAIN: 64x; λ <sub>p</sub> : 825 nm   | 327 | counts / (µW/cm²) |

| R <sub>e_PD59</sub> | Irradiance responsivity | AGAIN: 64x; λ <sub>p</sub> : 865 nm   | 214 | counts / (µW/cm²) |

| R <sub>e_PD60</sub> | Irradiance responsivity | AGAIN: 64x; λ <sub>p</sub> : 935 nm   | 214 | counts / (µW/cm²) |

| R <sub>e_PD61</sub> | Irradiance responsivity | AGAIN: 64x; λ <sub>p</sub> : 975 nm   | 143 | counts / (µW/cm²) |

| R <sub>e_PD62</sub> | Irradiance responsivity | AGAIN: 128x; λ <sub>p</sub> : 1015 nm | 134 | counts / (µW/cm²) |

| R <sub>e_PD63</sub> | Irradiance responsivity | AGAIN: 64x; λ <sub>p</sub> : 830 nm   | 426 | counts / (µW/cm²) |

|                     |                         |                                       |     |                   |

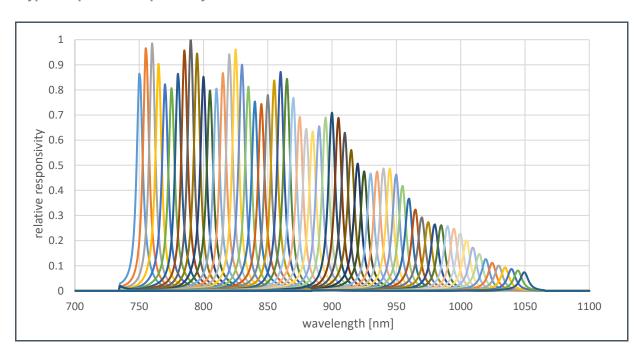

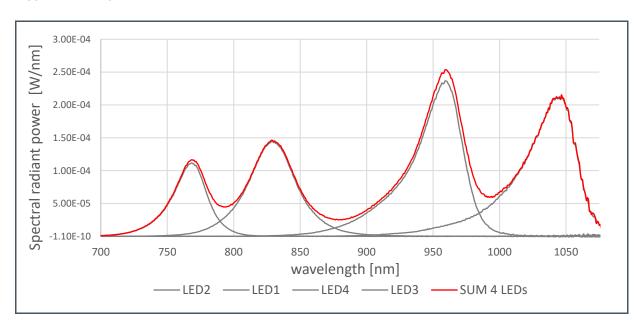

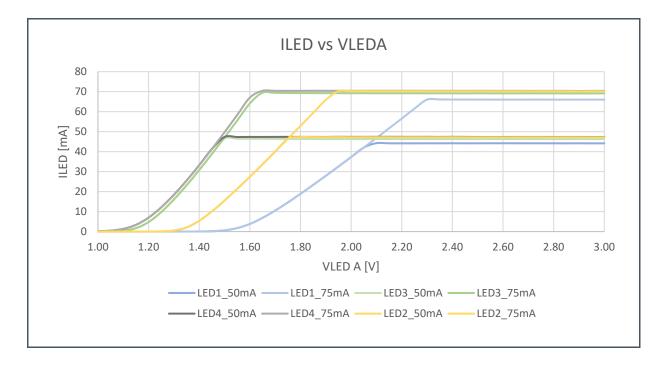

# **6 Typical Operating Characteristics**

Figure 9: Typical Spectral Responsivity of Sensor

Figure 10:

Typical LED Spectral Emission at 50 mA LED Current

Figure 11:

Typical LED Forward Voltage vs. LED Current

# 7 Functional Description

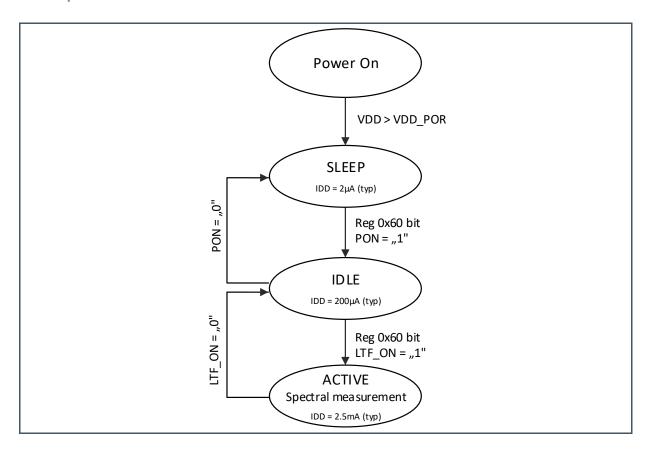

Upon power-up (POR), the device initializes. It is required that VDD is applied and settled 10 ms before the supply voltage of the NIR light source is applied (VLED\_A). During power down VLED\_A needs to be turned off 10 ms prior VDD.

During initialization, the device cannot accept I<sup>2</sup>C transactions. All communication with the device must be delayed and all outputs from the device must be ignored including interrupts. After initialization, the device enters the SLEEP state. In this operational state, the internal oscillator and other circuitry are not active, resulting in ultra-low power consumption. If an I<sup>2</sup>C transaction occurs during this state, the I<sup>2</sup>C core wakes up temporarily to service the communication. Once the Power ON bit, "PON", is enabled, the device enters the IDLE state in which the internal oscillator and attendant circuitry are active, but power consumption remains low. Whenever the spectral measurement is enabled (LTF\_ON = "1") the device enters the ACTIVE state. If the spectral measurement is disabled (LTF\_ON = "0") the device returns to the IDLE state. The figure below describes a simplified state diagram and the typical supply currents in each state. The power consumption in ACTIVE state does not include the power consumption to drive the NIR LEDs.

Figure 12: Start Up Flow-Chart

#### 7.1 Device Architecture

The device features 64 photo diodes (8 x 8 array) with on-chip Fabry-Perot filters. 61 photodiodes have an individual spectral response in the wavelength range from 750 nm - 1050 nm. The four corner photodiodes (indicated in the block diagram below with grey shading) share the same filter response of 830 nm. Sixteen dedicated 16-bit ADCs with adjustable gain and integration time are available and can be configured with the serial interface. The gain of each ADC can be adjusted independently. Once a spectral measurement is started, the device automatically runs four full integration cycles to obtain spectral data of all 64 channels. The spectral data (128 bytes) is stored on chip and can be read out using the I<sup>2</sup>C interface burst mode after the four cycles have been finished.

The GPIO can be used to trigger and synchronize a spectral measurement with an external MCU or as additional interrupt output. The pin RST acts as reset input and is active high.

Figure 13: Simplified Block Diagram of AS7421

### 7.2 Sensor Array

The device features an 8 x 8-photodiode array – each photo diode has its own filter with a dedicated response. The pitch between each photo-diode is 200  $\mu$ m. Four photodiodes (corner) share the same wavelength response.

Figure 14: Photodiode Array

| -      | +         |     |     | 160 | Ͻμm |     |      |           |

|--------|-----------|-----|-----|-----|-----|-----|------|-----------|

| †      | 830<br>nm | 750 | 790 | 870 | 940 | 980 | 1020 | 830<br>nm |

|        | 760       | 800 | 840 | 880 | 930 | 970 | 1010 | 1050      |

|        | 770       | 810 | 850 | 890 | 920 | 960 | 1000 | 1040      |

| E H    | 780       | 820 | 860 | 900 | 910 | 950 | 990  | 1030      |

| 1600µш | 775       | 815 | 855 | 895 | 905 | 945 | 985  | 1025      |

|        | 765       | 805 | 845 | 885 | 915 | 955 | 995  | 1035      |

|        | 755       | 795 | 835 | 875 | 925 | 965 | 1005 | 1045      |

|        | 830<br>nm | 785 | 825 | 865 | 935 | 975 | 1015 | 830<br>nm |

### 7.3 SMUX Configuration

The device integrates a multiplexer (SMUX). With the SMUX, it is possible to map all available photo diodes to one of four pre-defined ADCs. In total sixteen ADCs are available for data processing. After power up of the device the SMUX needs to be configured and the configuration data is stored in the RAM. ams OSRAM provides reference codes and an application note on how to configure the SMUX.

### 7.4 ADC Gain Configuration

The gain of each modulator (ADC) can be adjusted individually. Eight configuration steps are available, from AGAIN "0" (gain factor 1x) to AGAIN "8" which equals a gain ration of 256x. ams OSRAM provides reference codes and an application note on how to configure the AGAIN values of AS7421.

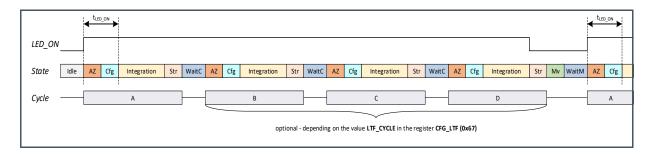

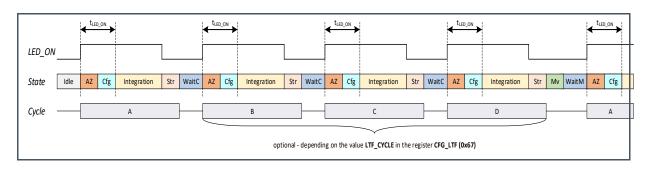

# 7.5 Typical Measurement Cycle

Figure 15:

Measurement Cycle with LED\_WAIT\_OFF = "1"

Figure 16:

Measurement Cycle with LED\_WAIT\_OFF = "0"

Figure 17:

Measurement State Explanation

| _ |             |                     |                                                                                                                                                            |

|---|-------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | AZ          | AutoZero            | Offset compensation of ADCs                                                                                                                                |

|   | Cfg         | Configuration       | Set the ASETUP and SMUX values for the integration cycle                                                                                                   |

|   | Integration | Integration cycle   | Programable with register LTF_ITIME (0x61 – 0x63)                                                                                                          |

|   | Str         | Store               | Store the 16 x 16bit ADC data in the internal RAM                                                                                                          |

|   | Mv          | Move                | Provision of a new memory area in the internal RAM for the next measurement                                                                                |

|   | WaitC       | Wait Cycle          | Waiting time between integration cycles within a measurement (can optionally be switched on or off) Programable with registers LTF_WTIME (0x64 – 0x67)     |

|   | WaitM       | Wait<br>Measurement | Waiting time between the provision of a new memory area and the automatic start of the next measurement Programable with registers LTF_WTIME (0x64 – 0x67) |

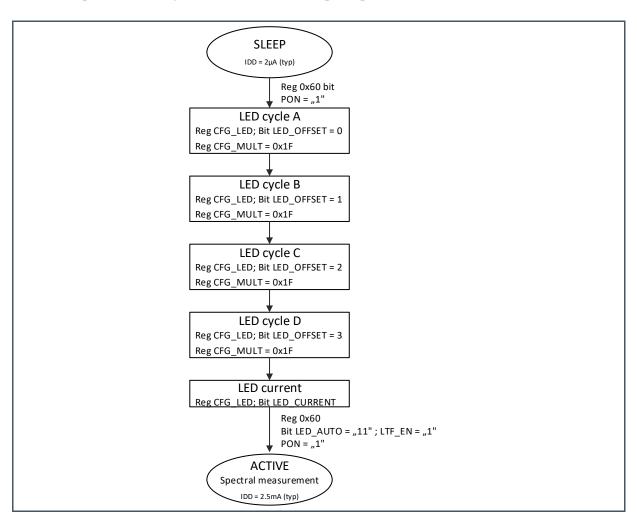

#### 7.6 LED Driver

Four current sinks are provided to drive the 4 integrated NIR LEDs with a programmable constant current of 50 mA or 75 mA per channel. If a measurement is done with 4 x 75 mA ILED the next measurement can be started after a timeout of 10 seconds.

The LED driver can be configured with the register CFG\_LED. With the bits "LED\_AUTO" in register 0x60 it is possible that the LED driver is configured in such a way that during two consecutive spectral measurements the LEDs are turned on in the first and turned off in the second measurement or vice versa. The example below shows how the device needs to be configured to turn on all LEDs for integration cycle A to D.

Figure 18: LED Configuration Example – All LEDs On During Integration

# 8 Device and System Calibration

AS7421 is a fully integrated spectrometer, including sensor array, light sources, optics, Fabry-Perot interference filter, cover glass, light guide, all integrated into a single package. Factors such as temperature drift of the LEDs, wavelength shift of the filters but also system related influences such as optical stack-up of the final application influence the measurement results and therefore need to be calibrated to provide accurate and repeatable spectral measurements.

Typically a calibration consist of 2 stages, stage 1 is Device Calibration. ams OSRAM is providing a device calibration file for each individual device which is linked to its unique device ID. This Device Calibration file is needed for final System Calibration and can be used by our provided "Calibration Library".

System Calibration is done to compensate influences which are caused by final system optical stack up implementation, such as cross talk from cover glasses or influences from external diffusers within the optical stack-up. The System Calibration file (stage 2) is generated by use of our Calibration Library.

Figure 19: Calibration Stages

| Calibration Stage                           | Addressed Items                                                         | Comment                                                                                                            |  |

|---------------------------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|--|

|                                             | Sensor Array (responsivity)                                             |                                                                                                                    |  |

| Device Calibration                          | Light Sources (SPD)                                                     | Device Calibration file is provided                                                                                |  |

| (Stage 1 Calibration)                       | Temperature Drift of PDs                                                | by ams OSRAM for each individual AS7421 device.                                                                    |  |

|                                             | Filter Performance (PWL)                                                | •                                                                                                                  |  |

| System Calibration<br>(Stage 2 Calibration) | Optical stack of final application such as cover glasses, system optics | In order to generate a system calibration file the Device Calibration file and the calibration library are needed. |  |

ams OSRAM is providing the following supporting tools to enable system calibration at customer applications.

Figure 20: Supporting Tools (SW and Calibration)

| Supporting Tools                      | Function                                          | Version |

|---------------------------------------|---------------------------------------------------|---------|

| AS7421 Calibration Library            | Provides APIs for system calibration.             | 1.4.0   |

| Calibration Library API Documentation | Documentation of available APIs.                  | 1.4.0   |

| AS7421 Chip Library                   | Provide low level access to AS7421 configuration. | 4.0.0   |

| Supporting Tools                    | Function                              | Version |

|-------------------------------------|---------------------------------------|---------|

| Chip Library API Documentation      | Documentation of Chip Library.        | 4.0.0   |

| AS7421 Calibration Application Note | Provides details to calibration flow. | 1.4     |

# 9 I<sup>2</sup>C Interface

The device uses I<sup>2</sup>C serial communication protocol for communication. The device supports 7-bit chip addressing and both standard and full-speed clock frequency modes. Read and Write transactions comply with the standard set by Philips (now NXP). Internal to the device, an 8-bit buffer stores the register address location of the desired byte to read or write. This buffer auto-increments upon each byte transfer and is retained between transaction events (i.e. valid even after the master issues a STOP command and the I<sup>2</sup>C bus is released). During consecutive Read transactions, the future/repeated I<sup>2</sup>C Read transaction may omit the memory address byte normally following the chip address byte; the buffer retains the last register address +1. All 16-bit fields have a latching scheme for reading and writing. In general, it is recommended to use I<sup>2</sup>C bursts whenever possible, especially in this case when accessing two bytes of one logical entity. When reading these fields, the low byte must be read first, and it triggers a 16-bit latch that stores the 16-bit field. The high byte must be read immediately afterwards. When writing to these fields, the low byte must be written first, immediately followed by the high byte. Reading or writing to these registers without following these requirements will cause errors.

#### 9.1 I<sup>2</sup>C Address

Figure 21: AS7421 I<sup>2</sup>C Slave Address

| Device | l <sup>2</sup> C Address |

|--------|--------------------------|

| AS7421 | 0x64                     |

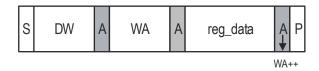

#### 9.2 I<sup>2</sup>C Write Transaction

A Write transaction consists of a START, CHIP-ADDRESSWRITE, REGISTER-ADDRESS WRITE, DATA BYTE(S), and STOP (P). Following each byte (9<sup>th</sup> clock pulse) the slave places an ACKNOWLEDGE/NOT- ACKNOWLEDGE (A/N) on the bus. If the slave transmits N, the master may issue a STOP.

Figure 22: I<sup>2</sup>C Byte Write

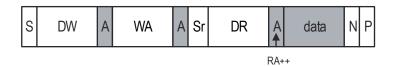

#### 9.3 I<sup>2</sup>C Read Transaction

A Read transaction consists of a START, CHIP-ADDRESSWRITE, REGISTER-ADDRESS, RESTART, CHIP-ADDRESSREAD, DATA BYTE(S), and STOP. Following all but the final byte the master places an ACK on the bus (9<sup>th</sup> clock pulse). Termination of the Read transaction is indicated by a NACK being placed on the bus by the master, followed by STOP.

Figure 23: I<sup>2</sup>C Read

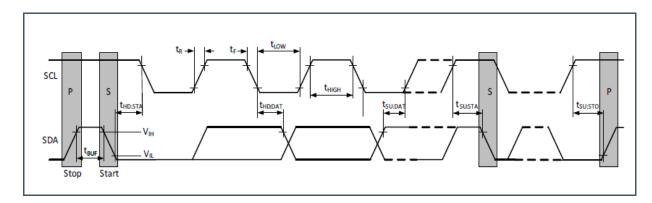

## 9.4 Timing Characteristics

Figure 24: I<sup>2</sup>C Timing Characteristics

| Symbol              | Parameter                                                                                    | Min | Max | Unit |

|---------------------|----------------------------------------------------------------------------------------------|-----|-----|------|

| f <sub>SCL</sub>    | I <sup>2</sup> C clock frequency                                                             |     | 400 | kHz  |

| t <sub>BUF</sub>    | Bus free time between start and stop condition                                               | 1.3 |     | μs   |

| t <sub>HS;STA</sub> | Hold time after (repeated) start condition. After this period, the first clock is generated. | 0.6 |     | μs   |

| t <sub>SU;STA</sub> | Repeated start condition setup time                                                          | 0.6 |     | μs   |

| t <sub>SU;STO</sub> | Stop condition setup time                                                                    | 0.6 |     | μs   |

| t <sub>LOW</sub>    | SCL clock low period                                                                         | 1.3 |     | μs   |

| t <sub>HIGH</sub>   | SCL clock high period                                                                        | 0.6 |     | μs   |

| t <sub>HD;DAT</sub> | Data hold time                                                                               | 60  |     | ns   |

| t <sub>SU;DAT</sub> | Data setup time                                                                              | 100 |     | ns   |

| t <sub>F</sub>      | Clock/data fall time                                                                         |     | 300 | ns   |

| t <sub>R</sub>      | Clock/data rise time                                                                         |     | 300 | ns   |

# 9.5 Timing Diagrams

Figure 25: I<sup>2</sup>C Slave Timing Diagram

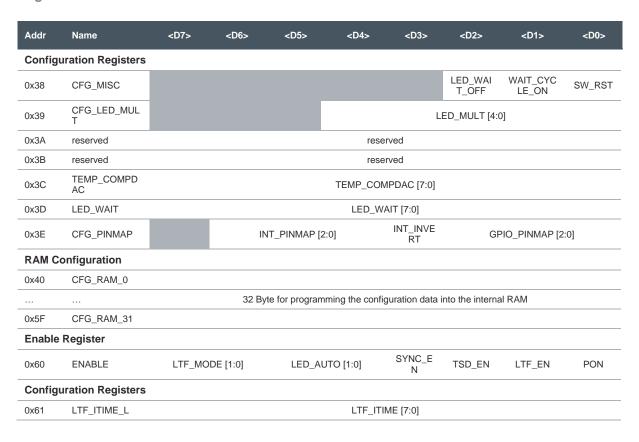

# 10 Register Description

The device is controlled and monitored by registers accessed through the I<sup>2</sup>C serial interface. These registers provide device control functions and can be read to determine device status and acquire device data.

The register set is summarized below. The values of all registers and fields that are listed as reserved (gray) or are not listed must not be changed at any time. Two-byte fields are always latched with the low byte followed by the high byte. The "Name" column illustrates the purpose of each register by highlighting the function associated to each bit. The bits are shown from MSB (D7) to LSB (D0).

Note: After power on reset the following commands have to be written prior accessing other registers:

Write 44h to register 6Fh

Write 20h to register 6Eh

Write 00h to register 6Fh

### 10.1 Register Overview

Figure 26: Register Overview

| Addr    | Name             | <d7></d7>      | <d6></d6>      | <d5></d5>     | <d4></d4>    | <d3></d3>       | <d2></d2>    | <d1></d1>     | <d0></d0>    |

|---------|------------------|----------------|----------------|---------------|--------------|-----------------|--------------|---------------|--------------|

| 0x62    | LTF_ITIME_M      |                |                |               | LTF_ITII     | ME [15:8]       |              |               |              |

| 0x63    | LTF_ITIME_H      |                |                |               | LTF_ITIN     | ЛЕ [23:16]      |              |               |              |

| 0x64    | LTF_WTIME_L      |                |                |               | LTF_WT       | IME [7:0]       |              |               |              |

| 0x65    | LTF_WTIME_M      |                |                |               | LTF_WT       | IME [15:8]      |              |               |              |

| 0x66    | LTF_WTIME_H      |                |                |               | LTF_WTI      | ME [23:16]      |              |               |              |

| 0x67    | CFG_LTF          | TEM            | P_DIODE_SE     | L [2:0]       | LTF_CY(      | CLE [1:0]       |              | CLKMOD [2:0]  |              |

| 0x68    | CFG_LED          | SET_<br>LED_ON | LED_OFF<br>_EN | LED_OF        | FSET [1:0]   |                 | LE           | D_CURRENT [:  | 2:0]         |

| 0x69    | LTF_ICOUNT       |                |                |               | LTF_ICC      | OUNT [7:0]      |              |               |              |

| 0x6A    | CFG_RAM          | REG_BAN<br>K   |                |               |              | R.A             | AM_OFFSET [  | 4:0]          |              |

| 0x6B    | CFG_GPIO         |                |                |               |              | GPIO_IN<br>VERT | GPIO_OE<br>N | GPIO_OUT      | GPIO_IN      |

| 0x6C    | INT_ENABLE       |                |                | EN_DLOS<br>T  | EN_DSAT      | EN_ASA<br>T     | EN_TSD       | EN_AZ         | EN_ADA<br>TA |

| 0x6D    | CFG_AZ           | AZ_ON          | AZ_WT          | IME [1:0]     | AZ_EN        | AZ_CYCL<br>E    | AZ           | Z_ITERATION[2 | 2:0]         |

| Status  |                  |                |                |               |              |                 |              |               |              |

| 0x70    | STATUS_0         |                |                |               |              | DEV_            | ID [5:0]     |               |              |

| 0x71    | STATUS_1         |                |                |               |              |                 |              | REV_ID [2:0]  |              |

| 0x72    | STATUS_2         |                |                |               | LTF_AS       | SAT [7:0]       |              |               |              |

| 0x73    | STATUS_3         |                |                |               | LTF_AS       | AT [15:8]       |              |               |              |

| 0x76    | STATUS_6         |                | TEMP_ASA<br>T  | LTF_READ<br>Y | LTF_BUS<br>Y |                 |              |               |              |

| 0x77    | STATUS_7         | I2C_DAT        | A_PTR[1:0]     | DLOST         | DSAT         | ASAT            | TSD          | AZ            | ADATA        |

| Temp    |                  |                |                |               |              |                 |              |               |              |

| 0x78    | TEMP0_L          |                |                |               | TEMF         | P0 [7:0]        |              |               |              |

| 0x79    | TEMP0_H          |                |                |               | TEMP         | 0 [15:8]        |              |               |              |

| 0x7A    | TEMP1_L          |                |                |               | TEMF         | P1 [7:0]        |              |               |              |

| 0x7B    | TEMP1_H          |                |                |               | TEMP         | 1 [15:8]        |              |               |              |

| 0x7C    | TEMP2_L          |                |                |               | TEMP         | 2 [7:0]         |              |               |              |

| 0x7D    | TEMP2_H          |                |                |               | TEMP         | 2 [15:8]        |              |               |              |

| 0x7E    | TEMP3_L          |                |                |               | TEMP         | 3 [7:0]         |              |               |              |

| 0x7F    | TEMP3_H          |                |                |               | TEMP         | 3 [15:8]        |              |               |              |

| Spectra | al Channel Outpu | t Register     |                |               |              |                 |              |               |              |

| 0x80    |                  |                |                |               | CH0_D/       | ATA [7:0]       |              |               |              |

| 0x81    | - CH0_DATA       |                |                |               |              | TA [15:8]       |              |               |              |

| 0x82    |                  |                |                |               | CH1_D/       | ATA [7:0]       |              |               |              |

| 0x83    | - CH1_DATA       |                |                |               |              | TA [15:8]       |              |               |              |

| 0x84    |                  |                |                |               | CH2_D/       | ATA [7:0]       |              |               |              |

| 0x85    | - CH2_DATA       |                |                |               |              | TA [15:8]       |              |               |              |

| 0x86    |                  |                |                |               |              | ATA [7:0]       |              |               |              |

| 0x87    | - CH3_DATA       |                |                |               |              | TA [15:8]       |              |               |              |

| 0x88    |                  |                |                |               |              | ATA [7:0]       |              |               |              |

| 0x89    | - CH4_DATA       |                |                |               |              | TA [15:8]       |              |               |              |

| 0x8A    | CH5_DATA         |                |                |               |              | ATA [7:0]       |              |               |              |

|         |                  |                |                |               |              |                 |              |               |              |

| Addr | Name          | <d7></d7> | <d6></d6> | <d5></d5> | <d4></d4> | <d3></d3>  | <d2></d2> | <d1></d1> | <d0></d0> |

|------|---------------|-----------|-----------|-----------|-----------|------------|-----------|-----------|-----------|

| 0x8B |               |           |           |           | CH5_DA    | TA [15:8]  |           |           |           |

| 0x8C | 0110 5474     |           |           |           | CH6_DA    | TA [7:0]   |           |           |           |

| 0x8D | - CH6_DATA    |           |           |           | CH6_DA    | TA [15:8]  |           |           |           |

| 0x8E | 015 5474      |           |           |           | CH7_DA    | TA [7:0]   |           |           |           |

| 0x8F | - CH7_DATA    |           |           |           | CH7_DA    | TA [15:8]  |           |           |           |

| 0x90 | 0110 5474     |           |           |           | CH8_DA    | TA [7:0]   |           |           |           |

| 0x91 | - CH8_DATA    |           |           |           | CH8_DA    | TA [15:8]  |           |           |           |

| 0x92 | OUR DATA      |           |           |           | CH9_DA    | TA [7:0]   |           |           |           |

| 0x93 | - CH9_DATA    |           |           |           | CH9_DA    | TA [15:8]  |           |           |           |

| 0x94 | OLIAO DATA    |           |           |           | CH10_D/   | ATA [7:0]  |           |           |           |

| 0x95 | - CH10_DATA   |           |           |           | CH10_DA   | TA [15:8]  |           |           |           |

| 0x96 | CUIA DATA     |           |           |           | CH11_D/   | ATA [7:0]  |           |           |           |

| 0x97 | - CH11_DATA   |           |           |           | CH11_DA   | TA [15:8]  |           |           |           |

| 0x98 | CLIAC DATA    |           |           |           | CH12_D/   | ATA [7:0]  |           |           |           |

| 0x99 | - CH12_DATA   |           |           |           | CH12_DA   | TA [15:8]  |           |           |           |

| 0x9A | CLIAC DATA    |           |           |           | CH13_D/   | ATA [7:0]  |           |           |           |

| 0x9B | - CH13_DATA   |           |           |           | CH13_DA   | TA [15:8]  |           |           |           |

| 0x9C | CUIA DATA     |           |           |           | CH14_D/   | ATA [7:0]  |           |           |           |

| 0x9D | - CH14_DATA   |           |           |           | CH14_DA   | TA [15:8]  |           |           |           |

| 0x9E | CH1E DATA     |           |           |           | CH15_D/   | ATA [7:0]  |           |           |           |

| 0x9F | - CH15_DATA   |           |           |           | CH15_DA   | TA [15:8]  |           |           |           |

| 0xA0 | CH16 DATA     |           |           |           | CH16_D/   | ATA [7:0]  |           |           |           |

| 0xA1 | - CH16_DATA   |           |           |           | CH16_DA   | TA [15:8]  |           |           |           |

| 0xA2 | - CH17_DATA   |           |           |           | CH17_D/   | ATA [7:0]  |           |           |           |

| 0xA3 | - CITI_DATA   |           |           |           | CH17_DA   | TA [15:8]  |           |           |           |

| 0xA4 | - CH18_DATA   |           |           |           | CH18_D/   | ATA [7:0]  |           |           |           |

| 0xA5 | CITIO_DATA    |           |           |           | CH18_DA   | TA [15:8]  |           |           |           |

| 0xA6 | - CH19_DATA   |           |           |           | CH19_D/   | ATA [7:0]  |           |           |           |

| 0xA7 | CITI9_DATA    |           |           |           | CH19_DA   | TA [15:8]  |           |           |           |

| 0xA8 | - CH20_DATA   |           |           |           | CH20_D/   | ATA [7:0]  |           |           |           |

| 0xA9 | 01120_5/11/1  |           |           |           | CH20_DA   | TA [15:8]  |           |           |           |

| 0xAA | - CH21_DATA   |           |           |           | CH21_D/   | ATA [7:0]  |           |           |           |

| 0xAB | OHE I_DATA    |           |           |           | CH21_DA   | TA [15:8]  |           |           |           |

| 0xAC | - CH22_DATA   |           |           |           | CH22_D/   | ATA [7:0]  |           |           |           |

| 0xAD | 5.122_5/(1//  |           |           |           | CH22_DA   | TA [15:8]  |           |           |           |

| 0xAE | - CH23_DATA   |           |           |           | CH23_D/   | ATA [7:0]  |           |           |           |

| 0xAF | 01120_D/(1/A  |           |           |           | CH23_DA   | TA [15:8]  |           |           |           |

| 0xB0 | - CH24_DATA   |           |           |           | CH24_D/   | ATA [7:0]  |           |           |           |

| 0xB1 | 3.12.1_3/(1// |           |           |           | CH24_DA   | ATA [15:8] |           |           |           |

| 0xB2 | - CH25_DATA   |           |           |           | CH25_D/   | ATA [7:0]  |           |           |           |

| 0xB3 | 323_3/\\/     |           |           |           | CH25_DA   | ATA [15:8] |           |           |           |

| 0xB4 | CH26_DATA     |           |           |           | CH26_D/   | ATA [7:0]  |           |           |           |

| 0xB5 |               |           |           |           | CH26_DA   | TA [15:8]  |           |           |           |

| Addr | Name        | <d7></d7> | <d6></d6> | <d5></d5> | <d4></d4> | <d3></d3>  | <d2></d2> | <d1></d1> | <d0></d0> |

|------|-------------|-----------|-----------|-----------|-----------|------------|-----------|-----------|-----------|

| 0xB6 |             |           |           |           | CH27_D    | ATA [7:0]  |           |           |           |

| 0xB7 | - CH27_DATA |           |           |           | CH27_D/   | ATA [15:8] |           |           |           |

| 0xB8 |             |           |           |           | CH28_D    | ATA [7:0]  |           |           |           |

| 0xB9 | - CH28_DATA |           |           |           | CH28_D/   | ATA [15:8] |           |           |           |

| 0xBA |             |           |           |           | CH29_D    | ATA [7:0]  |           |           |           |

| 0xBB | CH29_DATA   |           |           |           | CH29_D/   | ATA [15:8] |           |           |           |

| 0xBC |             |           |           |           | CH30_D    | ATA [7:0]  |           |           |           |

| 0xBD | - CH30_DATA |           |           |           | CH30_D/   | ATA [15:8] |           |           |           |

| 0xBE | OLIGA DATA  |           |           |           | CH31_D    | ATA [7:0]  |           |           |           |

| 0xBF | - CH31_DATA |           |           |           | CH31_D/   | ATA [15:8] |           |           |           |

| 0xC0 | OLIOO DATA  |           |           |           | CH32_D    | ATA [7:0]  |           |           |           |

| 0xC1 | - CH32_DATA |           |           |           | CH32_D/   | ATA [15:8] |           |           |           |

| 0xC2 | CLICO DATA  |           |           |           | CH33_D    | ATA [7:0]  |           |           |           |

| 0xC3 | - CH33_DATA |           |           |           | CH33_D/   | ATA [15:8] |           |           |           |

| 0xC4 | CUOA DATA   |           |           |           | CH34_D    | ATA [7:0]  |           |           |           |

| 0xC5 | - CH34_DATA |           |           |           | CH34_D/   | ATA [15:8] |           |           |           |

| 0xC6 | CLIOF DATA  |           |           |           | CH35_D    | ATA [7:0]  |           |           |           |

| 0xC7 | - CH35_DATA |           |           |           | CH35_D/   | ATA [15:8] |           |           |           |

| 0xC8 | CH36 DATA   |           |           |           | CH36_D    | ATA [7:0]  |           |           |           |

| 0xC9 | - CH36_DATA |           |           |           | CH36_DA   | ATA [15:8] |           |           |           |

| 0xCA | CH37_DATA   |           |           |           | CH37_D    | ATA [7:0]  |           |           |           |

| 0xCB | CH37_DATA   |           |           |           | CH37_D/   | ATA [15:8] |           |           |           |

| 0xCC | - CH38_DATA |           |           |           | CH38_D    | ATA [7:0]  |           |           |           |

| 0xCD | OHOO_DATA   |           |           |           | CH38_D/   | ATA [15:8] |           |           |           |

| 0xCE | - CH39_DATA |           |           |           | CH39_D    | ATA [7:0]  |           |           |           |

| 0xCF |             |           |           |           | CH39_D/   | ATA [15:8] |           |           |           |

| 0xD0 | - CH40_DATA |           |           |           | CH40_D    | ATA [7:0]  |           |           |           |

| 0xD1 |             |           |           |           | CH40_DA   | ATA [15:8] |           |           |           |

| 0xD2 | - CH41_DATA |           |           |           | CH41_D    | ATA [7:0]  |           |           |           |

| 0xD3 |             |           |           |           | CH41_D/   | ATA [15:8] |           |           |           |

| 0xD4 | - CH42_DATA |           |           |           | CH42_D    | ATA [7:0]  |           |           |           |

| 0xD5 |             |           |           |           | CH42_D/   | ATA [15:8] |           |           |           |

| 0xD6 | - CH43_DATA |           |           |           | CH43_D    | ATA [7:0]  |           |           |           |

| 0xD7 |             |           |           |           | CH43_D/   | ATA [15:8] |           |           |           |

| 0xD8 | - CH44_DATA |           |           |           | CH44_D    | ATA [7:0]  |           |           |           |

| 0xD9 |             |           |           |           |           | ATA [15:8] |           |           |           |

| 0xDA | - CH45_DATA |           |           |           | CH45_D    | ATA [7:0]  |           |           |           |

| 0xDB |             |           |           |           | CH45_D/   | ATA [15:8] |           |           |           |

| 0xDC | - CH46_DATA |           |           |           | CH46_D    | ATA [7:0]  |           |           |           |

| 0xDD |             |           |           |           | CH46_DA   | ATA [15:8] |           |           |           |

| 0xDE | - CH47_DATA |           |           |           | CH47_D    | ATA [7:0]  |           |           |           |

| 0xDF |             |           |           |           |           | ATA [15:8] |           |           |           |

| 0xE0 | CH48_DATA   |           |           |           | CH48_D    | ATA [7:0]  |           |           |           |

| 0XE1       CH48_DATA [15:8]         0XE2       CH49_DATA [7:0]         0XE3       CH49_DATA [15:8]         0XE4       CH50_DATA [15:8]         0XE5       CH50_DATA [15:8]         0XE6       CH51_DATA [7:0]         0XE7       CH51_DATA [15:8]         0XE8       CH52_DATA [15:8]         0XE9       CH52_DATA [15:8]         0XEA       CH53_DATA [7:0]         0XEB       CH53_DATA [15:8]         0XEC       CH54_DATA [7:0]         0XED       CH54_DATA [15:8]         0XEE       CH55_DATA [7:0]         0XEE       CH55_DATA [7:0]         0XEF       CH55_DATA [7:0]         0XF0       CH56_DATA [15:8]         0XF0       CH56_DATA [15:8]         0XF1       CH56_DATA [15:8] |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| OXE3         CH49_DATA           OXE4         CH50_DATA [7:0]           OXE5         CH50_DATA [7:0]           OXE6         CH51_DATA [7:0]           OXE7         CH51_DATA [7:0]           OXE8         CH52_DATA [15:8]           OXE9         CH52_DATA [15:8]           OXEA         CH52_DATA [15:8]           OXEB         CH53_DATA [7:0]           OXEC         CH54_DATA [15:8]           OXEC         CH54_DATA [15:8]           OXED         CH54_DATA [15:8]           OXEE         CH55_DATA [7:0]           OXEE         CH55_DATA [15:8]           OXEF         CH55_DATA [15:8]           OXFO         CH56_DATA [15:8]           OXFO         CH56_DATA [15:8]             |  |

| 0XE3         CH49_DATA [15:8]           0XE4         CH50_DATA [7:0]           0XE5         CH50_DATA [15:8]           0XE6         CH51_DATA [7:0]           0XE7         CH51_DATA [15:8]           0XE8         CH52_DATA [15:8]           0XE9         CH52_DATA [15:8]           0XEA         CH53_DATA [7:0]           0XEB         CH53_DATA [15:8]           0XEC         CH54_DATA [7:0]           0XED         CH54_DATA [15:8]           0XEE         CH55_DATA [7:0]           0XEF         CH55_DATA [15:8]           0XF0         CH56_DATA [7:0]           0XF1         CH56_DATA [15:8]                                                                                      |  |

| OXE5         CH50_DATA [15:8]           OXE6         CH51_DATA [7:0]           OXE7         CH51_DATA [15:8]           OXE8         CH52_DATA [15:8]           OXE9         CH52_DATA [7:0]           OXEA         CH53_DATA [7:0]           OXEB         CH53_DATA [15:8]           OXEC         CH54_DATA [7:0]           OXED         CH54_DATA [15:8]           OXEE         CH55_DATA [7:0]           OXEF         CH55_DATA [15:8]           OXF0         CH56_DATA [7:0]           OXF1         CH56_DATA [15:8]                                                                                                                                                                      |  |

| 0xE5         CH50_DATA [15:8]           0xE6         CH51_DATA [7:0]           0xE7         CH51_DATA [15:8]           0xE8         CH52_DATA [7:0]           0xE9         CH52_DATA [15:8]           0xEA         CH53_DATA [7:0]           0xEB         CH53_DATA [15:8]           0xEC         CH54_DATA [7:0]           0xED         CH54_DATA [15:8]           0xEE         CH55_DATA [7:0]           0xEF         CH55_DATA [15:8]           0xF0         CH56_DATA [7:0]           0xF1         CH56_DATA [15:8]                                                                                                                                                                      |  |

| 0xE7         CH51_DATA [15:8]           0xE8         CH52_DATA [7:0]           0xE9         CH52_DATA [15:8]           0xEA         CH52_DATA [15:8]           0xEB         CH53_DATA [7:0]           0xEB         CH53_DATA [15:8]           0xEC         CH54_DATA [7:0]           0xED         CH54_DATA [15:8]           0xEE         CH55_DATA [7:0]           0xEF         CH55_DATA [15:8]           0xF0         CH56_DATA [7:0]           0xF1         CH56_DATA [15:8]                                                                                                                                                                                                             |  |

| 0xE7         CH51_DATA [15:8]           0xE8         CH52_DATA [7:0]           0xE9         CH52_DATA [15:8]           0xEA         CH53_DATA [7:0]           0xEB         CH53_DATA [15:8]           0xEC         CH54_DATA [7:0]           0xED         CH54_DATA [15:8]           0xEE         CH55_DATA [7:0]           0xEF         CH55_DATA [15:8]           0xF0         CH56_DATA [7:0]           0xF1         CH56_DATA [15:8]                                                                                                                                                                                                                                                     |  |

| 0xE9         CH52_DATA [15:8]           0xEA         CH53_DATA [7:0]           0xEB         CH53_DATA [15:8]           0xEC         CH54_DATA [7:0]           0xED         CH54_DATA [15:8]           0xEE         CH55_DATA [7:0]           0xEF         CH55_DATA [15:8]           0xF0         CH56_DATA [7:0]           0xF1         CH56_DATA [15:8]                                                                                                                                                                                                                                                                                                                                    |  |

| 0xE9         CH52_DATA [15:8]           0xEA         CH53_DATA [7:0]           0xEB         CH53_DATA [15:8]           0xEC         CH54_DATA [7:0]           0xED         CH54_DATA [15:8]           0xEE         CH55_DATA [7:0]           0xEF         CH55_DATA [15:8]           0xF0         CH56_DATA [7:0]           0xF1         CH56_DATA [15:8]                                                                                                                                                                                                                                                                                                                                    |  |