## **AS8506C**

## **Battery Cell Monitor and Balancer IC**

#### **General Description**

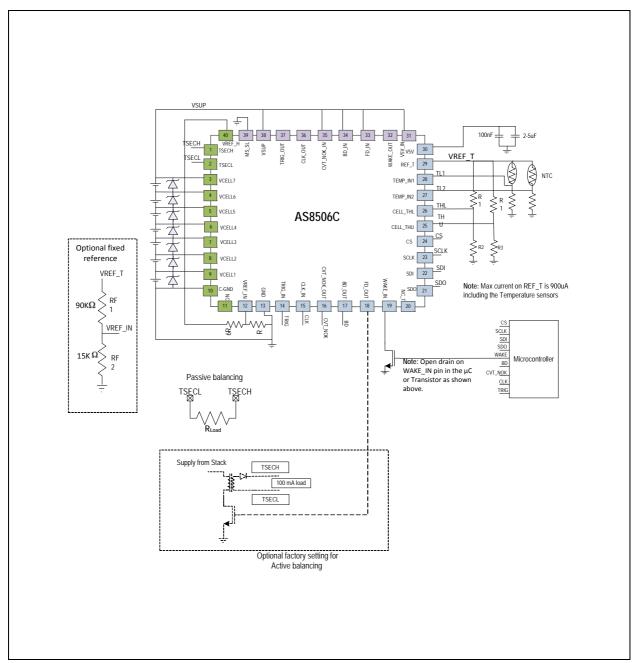

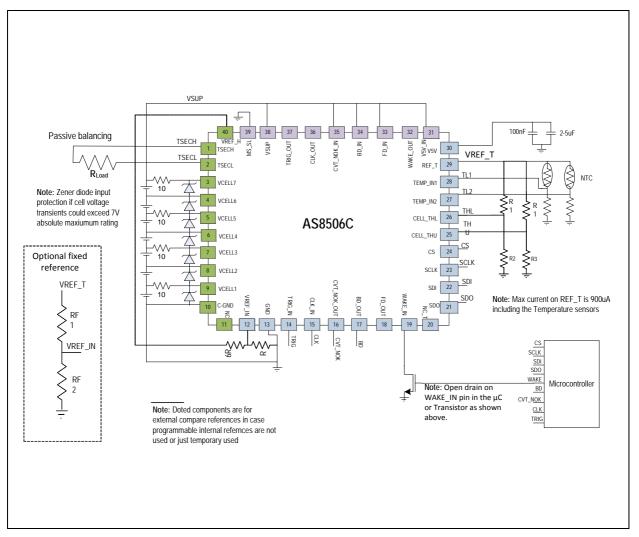

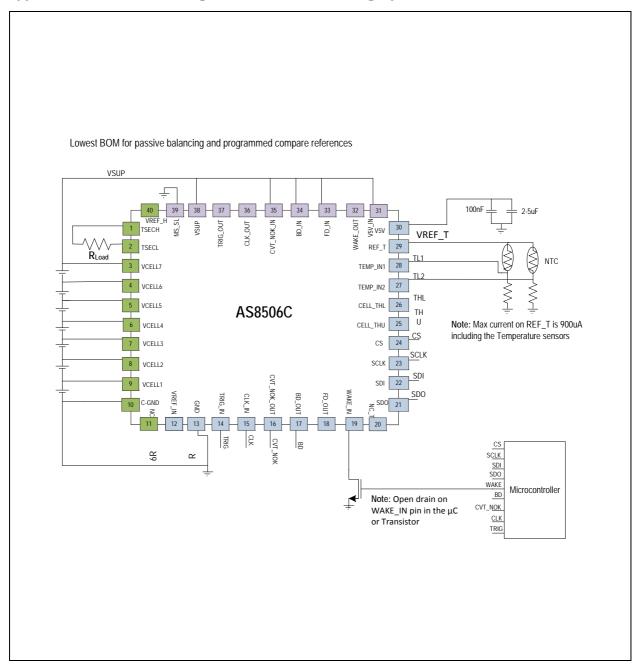

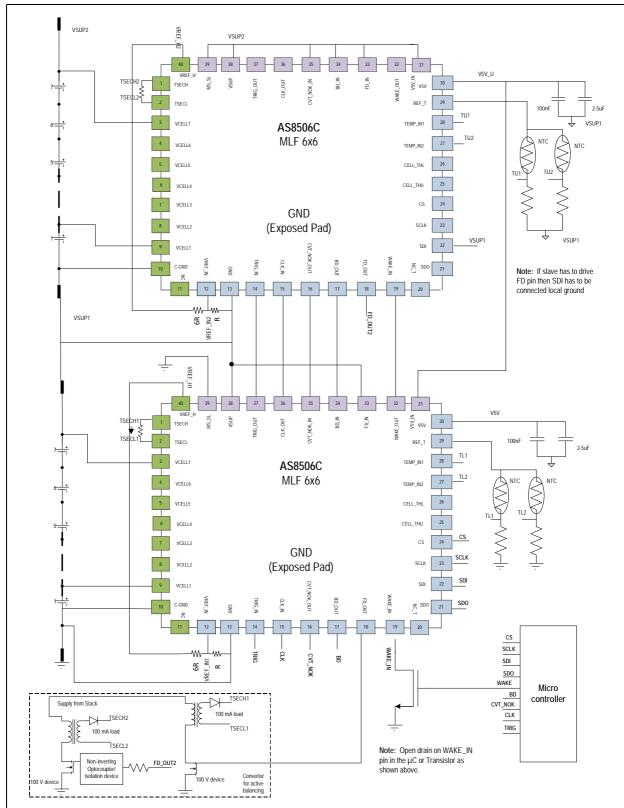

The AS8506C is a battery management IC dedicated to support cell voltage measurement, monitoring, cell balancing and temperature measurement functions in Li-lon battery stacks for industrial/consumer/PV battery applications.

Ambient temperature range is from -40°C to +85°C.

It features cell voltage diagnosis with externally adjustable upper and lower cell voltage limits, fast cell voltage capture on request through 12-bit SAR ADC, passive cell balancing by simultaneous comparison of actual cell voltages with a reference cell voltage and temperature measurement on two external NTC sensors through 12-bit ADC.

Cells that are above reference will sequentially be discharged through integrated switches and one external resistor.

There is also an active balancing option AS8506C A through factory setting to sequentially charge cells which are below reference from an external DC-DC Flyback converter and an integrated low side driver.

The device can be used flexibly for battery stacks up to 7 cells with a minimum stack voltage of 6V and a maximum stack voltage of 32V.

It can be chained to support battery packs of virtually any number of cells in synchronized mode through chained clock and trigger signal.

The status of the battery stack is communicated to outside world through OR'd voltage\_ok signal and balance ready signal.

Ordering Information and Content Guide appear at end of datasheet.

#### **Key Benefits & Features**

The benefits and features of AS8506C, Battery Cell Monitor and Balancer IC are listed below:

Figure 1: Added Value of using AS8506C

| Benefits                                                                                                                                                                      | Features                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| Reduce filter / synchronization effort. Acquired data have same time stamp to inherently generate accurate comparison results independent from load transients.               | Simultaneous cell voltage capture for safe operating area (SOA) monitoring and balancing. |

| Strongly reduces data communication and data processing and thereby improves EMC robustness.                                                                                  | Autonomous balancing and SOA monitoring.                                                  |

| To compensate accumulative charge differences only. This mitigates cases of occasional wrong balance decisions due to flat OCV characteristic or mismatch in cell temperature | Autonomous passive balancing in the 100 mA range                                          |

| Intrinsic inter module balancing through charge redistribution, efficiency improvement in case of leakage path due to defect induced leakage in particular cells.             | Option for active charge balancing with very few external components.                     |

| For OCV capture, cell impedance calculation, diagnosis                                                                                                                        | Absolute cell voltage read out, read out of two temperature sensors.                      |

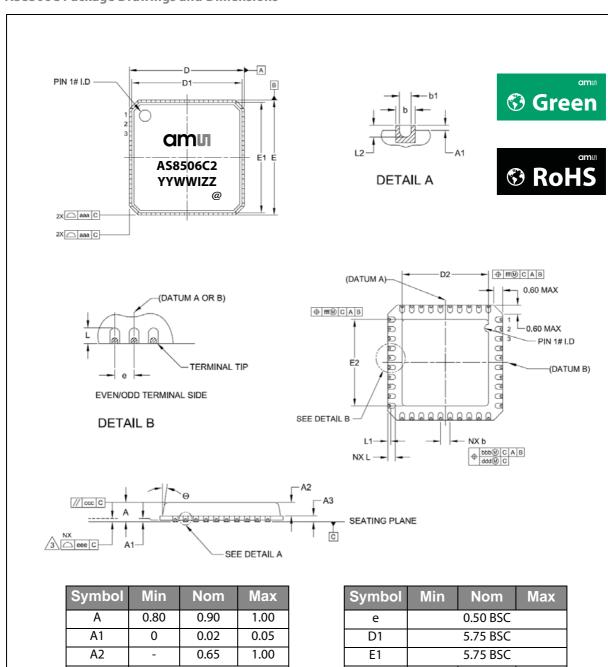

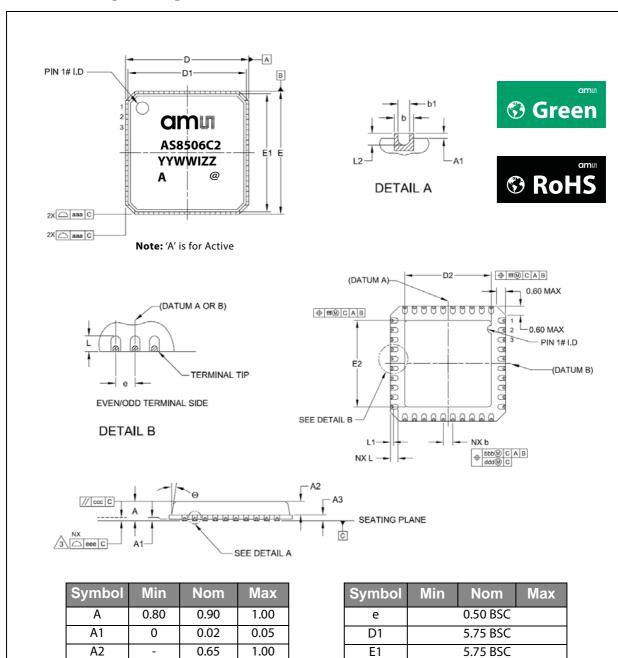

| Small form factor, low BOM                                                                                                                                                    | 40-pin MLF (6x6) package, very low number of external components.                         |

#### **Applications**

The applications of AS8506C include:

- The AS8506C is ideal for simultaneous cell monitoring and cell balancing in stacked energy storage systems. Current levels in the 100 mA range enables to compensate accumulative SOC mismatch over the entire cell pack.

- Typical applications are

- Li-lon batteries up to 200 cells,

- Energy storage systems to buffer energy from PV panels or for emergency power supplies,

- Battery management for e-scooters and e-bikes,

Page 2

Document Feedback

[v1-02] 2014-Nov-06

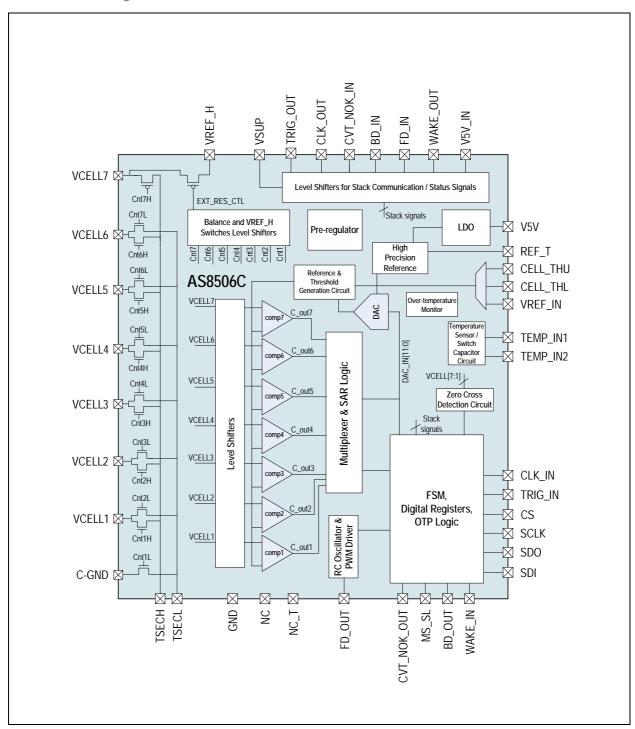

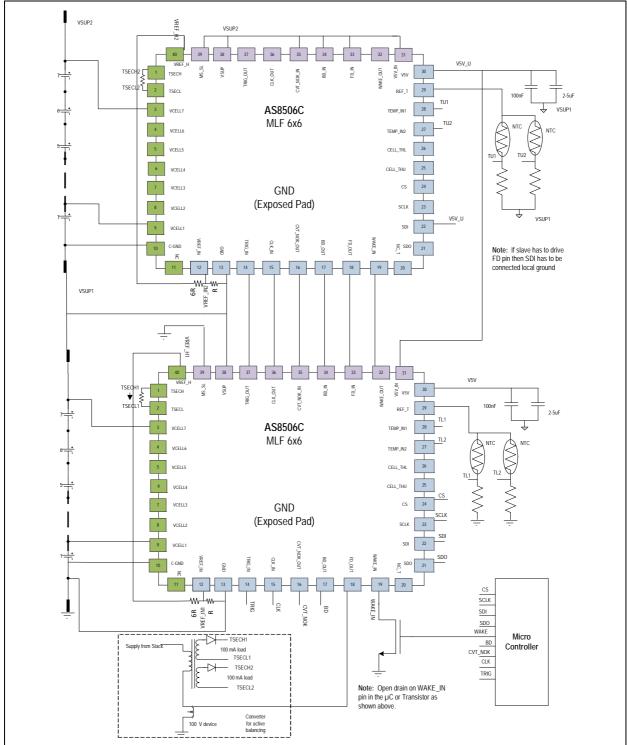

#### **Block Diagram**

The functional blocks of this device for reference are shown below:

Figure 2: AS8506C Block Diagram

ams Datasheet Page 3

[v1-02] 2014-Nov-06

Document Feedback

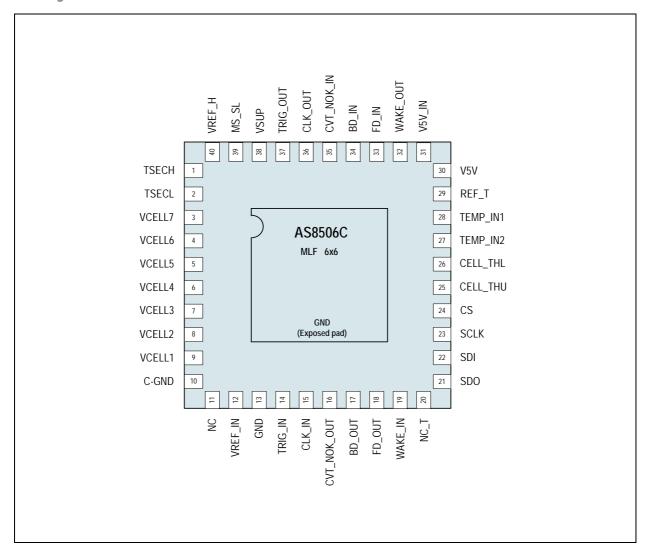

## **Pin Assignment**

Figure 3: Pin Diagram of AS8506C

Page 4ams DatasheetDocument Feedback[v1-02] 2014-Nov-06

Figure 4: Pin Description

| Pin Number | Pin Name    | Pin Type                 | Description                                                                                                                                                                                                                                                 |  |  |

|------------|-------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1          | TSECH       |                          | Flyback converter transformer secondary high side                                                                                                                                                                                                           |  |  |

| 2          | TSECL       |                          | Flyback converter transformer secondary low side                                                                                                                                                                                                            |  |  |

| 3          | VCELL7      |                          | Battery cell 7 high level pin                                                                                                                                                                                                                               |  |  |

| 4          | VCELL6      |                          | Battery cell 6 high level pin                                                                                                                                                                                                                               |  |  |

| 5          | VCELL5      | Analog input /<br>output | Battery cell 5 high level pin                                                                                                                                                                                                                               |  |  |

| 6          | VCELL4      |                          | Battery cell 4 high level pin                                                                                                                                                                                                                               |  |  |

| 7          | VCELL3      |                          | Battery cell 3 high level pin                                                                                                                                                                                                                               |  |  |

| 8          | VCELL2      |                          | Battery cell 2 high level pin                                                                                                                                                                                                                               |  |  |

| 9          | VCELL1      |                          | Battery cell 1 high level pin                                                                                                                                                                                                                               |  |  |

| 10         | C-GND       | Power supply input       | Battery cell 1 low level pin                                                                                                                                                                                                                                |  |  |

| 11         | NC          |                          | Not connected                                                                                                                                                                                                                                               |  |  |

| 12         | VREF_IN     | Analog input /<br>output | Cell voltage reference value (cell target voltage of battery)                                                                                                                                                                                               |  |  |

| 13         | GND         | Power supply input       | Ground to the IC                                                                                                                                                                                                                                            |  |  |

| 14         | TRIG_IN     | Digital input            | This pin triggers the cell balancing in the device. Short pulse is for receiving status and continuous 'High' for cell balancing. It also acts as a data line during 3-wire communication.                                                                  |  |  |

| 15         | CLK_IN      |                          | Clock input pin in the Slave device. This pin also acts as a clock during 3-wire communication. Scan clock in scan mode.                                                                                                                                    |  |  |

| 16         | CVT_NOK_OUT |                          | This pin alerts when the cell voltage or the device/cell temperature is not within limits. During 3-wire communication, the CRC error is indicated on this pin. The internal device cell voltage or temperature status is ORed with CVT_NOK_IN on this pin. |  |  |

| 17         | BD_OUT      | Digital output           | The 'device internal balance done' and 'balance done from above device' are ANDed on this pin. This pin in Master device indicates the complete system balance done. During address allocation process, this pin will be 'High' if BD_IN is 'High'.         |  |  |

| 18         | FD_OUT      |                          | Flyback converter gate/opto coupler drive (pad is push-pull type) can drive up to 12mA.                                                                                                                                                                     |  |  |

ams Datasheet Page 5

[v1-02] 2014-Nov-06

Document Feedback

| Pin Number | Pin Name   | Pin Type                        | Description                                                                                                                                                                        |

|------------|------------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 19         | WAKE_IN    | Digital input<br>with pull-up   | The wake pulse on this pin brings the IC into NORMAL mode. This pin has a pull-up resistor to the internal regulator. Should be driven with an open drain or external NMOS.        |

| 20         | NC_T       | Analog input /<br>output        | Not connected. Only used in Test mode.                                                                                                                                             |

| 21         | SDO        | Digital output                  | SPI data out                                                                                                                                                                       |

| 22         | SDI        | Digital input                   | SPI data in                                                                                                                                                                        |

| 23         | SCLK       | Digital input                   | SPI clock                                                                                                                                                                          |

| 24         | CS         | Digital input<br>with pull-up   | SPI chip select                                                                                                                                                                    |

| 25         | CELL_THU   |                                 | Cell voltage upper threshold                                                                                                                                                       |

| 26         | CELL_THL   |                                 | Cell voltage lower threshold                                                                                                                                                       |

| 27         | TEMP_IN2   | Analog input /                  | Temperature input 2 to the IC (NTC input; if NTC is not connected, then should be connected to GND with 1K resistor).                                                              |

| 28         | TEMP_IN1   | output                          | Temperature input 1 to the IC (NTC input; if NTC is not connected, then should be connected to GND with 1K resistor).                                                              |

| 29         | REF_T      |                                 | Supply to temperature sensor (Reference voltage to DAC and ADC).                                                                                                                   |

| 30         | V5V        | Power supply                    | LDO 5V output.                                                                                                                                                                     |

| 31         | V5V_IN     | input                           | Supply to the bottom IC from the cascaded top IC.                                                                                                                                  |

| 32         | WAKE_OUT   | Digital output<br>open drain    | Open drain o/p on the VSUP+5V domain. WAKE_IN information will be transmitted to top device.                                                                                       |

| 33         | FD_IN      | Digital input                   | Flyback converter gate drive input in daisy chain connection. (If FD_IN is 'high' then FD_OUT will be PWM o/p in balance mode).                                                    |

| 34         | BD_IN      | Digital input<br>with pull-down | In cell stack system, the device gets balance done status of above device. During address allocation process if this pin is 'High', then the device address is decremented by '1'. |

| 35         | CVT_NOK_IN |                                 | Indicates cell voltage or temperature status of above device.                                                                                                                      |

Page 6ams DatasheetDocument Feedback[v1-02] 2014-Nov-06

| Pin Number | Pin Name | Pin Type                 | Description                                                                                                                                                                                                |  |  |

|------------|----------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 36         | CLK_OUT  |                          | This pin propagates the clock to next device in the stack system. In case of Master device internal RC clock is transmitted on this pin to Slave device.                                                   |  |  |

| 37         | TRIG_OUT | Digital output           | This pin transmits the data from TRIG_IN for balance and measurement phase. This pin is also used for propagating the data information to next device in stack system in SPI3.                             |  |  |

| 38         | VSUP     | Power supply input       | Supply to the IC.                                                                                                                                                                                          |  |  |

| 39         | MS_SL    | Digital input            | This pin informs the device whether it should act as the Master or Slave. If this pin is connected to GND, then device will act as Master. If this pin is connected to VSUP then device will act as Slave. |  |  |

| 40         | VREF_H   | Analog input /<br>output | High sides PMOS switch for external resistive divided Input to VREF_IN can be taken from external resistive divider in one of the options.                                                                 |  |  |

ams Datasheet Page 7

[v1-02] 2014-Nov-06 Document Feedback

## **Absolute Maximum Ratings**

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated under Operating Conditions is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Figure 5:

Absolute Maximum Ratings

| Symbol                 | Parameter                                                                          | Min           | Тур | Max        | Units | Comments                                                                                              |  |  |  |

|------------------------|------------------------------------------------------------------------------------|---------------|-----|------------|-------|-------------------------------------------------------------------------------------------------------|--|--|--|

| Electrical Parameters  |                                                                                    |               |     |            |       |                                                                                                       |  |  |  |

| V <sub>VSUP</sub>      | Voltage at positive supply pin                                                     | -0.3          |     | 42         | V     | VSUP pin                                                                                              |  |  |  |

| V <sub>GND</sub>       | Voltage at negative supply pin                                                     | -0.3          |     | 0          | V     | GND, C-GND; Reference potential                                                                       |  |  |  |

| V <sub>V5V_IN</sub>    | Voltage at high side supply                                                        | -0.3          |     | VSUP + 0.3 | V     | MS_SL,VREF_H, TSECH and TSECL                                                                         |  |  |  |

| VSUP +<br>V5V_IN       | High side supply from top device                                                   | VSUP -<br>0.3 |     | VSUP + 5.5 | V     | TRIG_OUT, CLK_OUT, CVT_NOK_IN, FD_IN, BD_IN, WAKE_OUT                                                 |  |  |  |

| V <sub>V5V</sub>       | Voltage at on LDO o/p pins                                                         | -0.3          |     | 7          | V     | <b>V5V</b> pin                                                                                        |  |  |  |

| V <sub>ESD</sub>       | Voltage on 5V pins                                                                 | -0.3          |     | V5V+0.3    | V     | All pins expect VSUP,<br>VCELL1, VCELL2, VCELL3,<br>VCELL4, VCELL5, VCELL6,<br>VCELL7, MS_SL, WAKE_IN |  |  |  |

| VCELL1<br>to<br>VCELL7 | Voltage on pins<br>VCELL1, VCELL2,<br>VCELL3, VCELL4,<br>VCELL5, VCELL6,<br>VCELL7 | -0.3          |     | 7          | V     | Applied cell voltages                                                                                 |  |  |  |

| I <sub>SCR</sub>       | Latch-up Immunity                                                                  | -100          |     | +100       | mA    |                                                                                                       |  |  |  |

Page 8ams DatasheetDocument Feedback[v1-02] 2014-Nov-06

| Symbol              | Parameter                                                             | Min          | Тур      | Max            | Units   | Comments                                                                                                                                                                      |  |  |  |  |

|---------------------|-----------------------------------------------------------------------|--------------|----------|----------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                     | Electrostatic Discharge                                               |              |          |                |         |                                                                                                                                                                               |  |  |  |  |

|                     | Electrostatic<br>ESD discharge voltage<br>HBM standard <sup>(1)</sup> | ±2           |          |                |         | VSUP, VREF_IN, SDI, SDO,<br>CS, SCLK, CELL_THU,<br>CELL_THL, TEMP_IN1,<br>TEMP_IN2, REF_T, V5V,<br>V5V_IN, MS_SL, VREF_H,<br>NC_T                                             |  |  |  |  |

| ESD                 |                                                                       | ±4           |          |                | kV      | GND, C-GND, CELL1 – CELL7 (Cell-voltage pins,), TSECH, TSECL, TRIG_IN, TRIG_OUT, CLK_IN, CLK_OUT, CVT_NOK_IN, CVT_NOK_OUT, WAKE_IN, WAKE_OUT, FD_IN, FD_OUT, BD_IN and BD_OUT |  |  |  |  |

|                     |                                                                       | Continuo     | us Powe  | er Dissipation |         |                                                                                                                                                                               |  |  |  |  |

| P <sub>tot</sub>    | Maximum power dissipation                                             |              |          | 1              | W       |                                                                                                                                                                               |  |  |  |  |

|                     | Tem                                                                   | perature Rai | nges and | d Storage Con  | ditions |                                                                                                                                                                               |  |  |  |  |

| T <sub>stg</sub>    | Storage temperature                                                   | -55          |          | 150            | ۰C      |                                                                                                                                                                               |  |  |  |  |

| R <sub>thj_36</sub> | Thermal resistance package                                            |              | 30       |                | °C/W    |                                                                                                                                                                               |  |  |  |  |

| T <sub>BODY</sub>   | Package body<br>temperature                                           |              |          | 260            | ۰C      | Norm: IPC/JEDEC<br>J-STD-020 <sup>(2)</sup>                                                                                                                                   |  |  |  |  |

| MSL                 | Moisture Sensitive<br>Level                                           |              | 3        |                |         |                                                                                                                                                                               |  |  |  |  |

#### Note(s) and/or Footnote(s):

- 1. Human body model:  $R = 1.5k\Omega$ ; C = 100pF.

- $2. The \, reflow \, peak \, soldering \, temperature \, (body \, temperature) \, is \, specified \, according \, IPC/JEDEC \, J-STD-020 \, "Moisture/Reflow \, Sensitivity \, and \, reflow \, peak \, soldering \, temperature) \, is \, specified \, according \, IPC/JEDEC \, J-STD-020 \, "Moisture/Reflow \, Sensitivity \, and \, reflow \, peak \, soldering \, temperature) \, is \, specified \, according \, IPC/JEDEC \, J-STD-020 \, "Moisture/Reflow \, Sensitivity \, and \, reflow \, peak \, soldering \, temperature) \, is \, specified \, according \, IPC/JEDEC \, J-STD-020 \, "Moisture/Reflow \, Sensitivity \, and \, reflow \, peak \, soldering \, temperature) \, and \, reflow \, peak \, soldering \, according \, IPC/JEDEC \, J-STD-020 \, "Moisture/Reflow \, Sensitivity \, and \, reflow \, peak \, soldering \, according \, according$ Classification for Non-hermetic Solid State Surface Mount Devices".

ams Datasheet Page 9 **Document Feedback**

# Typical Operating Characteristics

Figure 6: Operating Conditions All defined tolerances for external components in this specification need to be assured over the whole operation conditions range and also over lifetime.

| Symbol                   | Parameter                                             | Min  | Тур | Max | Unit | Note                                                                              |

|--------------------------|-------------------------------------------------------|------|-----|-----|------|-----------------------------------------------------------------------------------|

| VSUP                     | Positive supply voltage                               | 6    |     | 32  | V    | Normal operating condition                                                        |

| VSS                      | Negative supply voltage                               | -0.3 |     | 0   | V    | With reference to all the voltages                                                |

| T <sub>AMB</sub>         | Ambient temperature                                   | -40  |     | 85  | °C   | Maximum junction<br>temperature (T <sub>J</sub> ) 115°C                           |

|                          | Supply current,<br>NORMAL mode                        | 2    | 3   | 6   | mA   | VSUP=32V, in <i>NORMAL</i> mode                                                   |

| I <sub>SUPP, nom</sub>   | Supply current, NORMAL mode, With External Components | 15   | 20  | 40  | mA   | VSUP=32V, in the balancing<br>phase with stack connection<br>(50% PWM duty cycle) |

| I <sub>SUPP, sleep</sub> | Supply current, SLEEP mode                            | 10   | 17  | 35  | μΑ   |                                                                                   |

Page 10ams DatasheetDocument Feedback[v1-02] 2014-Nov-06

## **Electrical Characteristics**

## **Device Level Specifications**

-40°C < Tj < 115°C.

Figure 7:

Device Level Specifications

| Symbol                      | Parameter                                                   | Min | Тур  | Max | Unit | Note                                                                                                                                                                      |

|-----------------------------|-------------------------------------------------------------|-----|------|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vcell_in                    | Cell Input voltage<br>measurement                           | 1.8 |      | 4.5 | V    |                                                                                                                                                                           |

| ADC/DAC                     | ADC/DAC Reference                                           |     | ±7   | ±15 | mV   | 0 hour, specification<br>does not include solder<br>stress / board stress<br>effects                                                                                      |

| DAC_error                   | Error of the DAC                                            |     | 2    |     | mV   | 0.1% error because of<br>the DAC/Guaranteed by<br>design                                                                                                                  |

| Com_off                     | Error because of the comparator resolution                  |     | 1    |     | mV   | Guaranteed by design                                                                                                                                                      |

| Sign_path_accuracy          | Signal path accuracy                                        |     | ±5   | ±15 | mV   | Typical value is from the lab evaluation data. Maximum value is from the test data. 0 hour accuracy, specification does not include solder stress / board stress effects. |

| T <sub>INITIALIZATION</sub> | Initialization time                                         |     |      | 50  | ms   | After Initialization, the system will go to sleep mode and waits for wake signal.                                                                                         |

| T <sub>WAKE-UP</sub>        | Wake up time from the<br>Wake signal to system<br>wait mode |     |      | 75  | ms   | After wake signal,<br>device enters into wait<br>mode and stays for two<br>seconds for TRIG_IN<br>signal, if no TRIG_IN<br>event occurs, device<br>goes to sleep mode.    |

| Tmeas                       | Cell voltage and<br>Temperature<br>measurement time         |     | 16   |     | ms   | At10KHz clock time                                                                                                                                                        |

| Tspi3_read5k                | SPI3 read time for                                          |     | 13.6 |     |      | At 5KHz clock time                                                                                                                                                        |

| Tspi3_read20k               | single channel<br>measurement                               |     | 3.4  |     | ms   | At 20KHz clock time                                                                                                                                                       |

| Tspi3_read40k               | measurement                                                 |     | 1.7  |     |      | At 40KHz clock time                                                                                                                                                       |

ams Datasheet Page 11

[v1-02] 2014-Nov-06 Document Feedback

#### **Low Dropout Regulator (5V Output LDO)**

-40°C < T $_{\rm J}$  < 115°C; all voltages are with respect to ground (GND); positive current flows into the pin, *NORMAL* operating mode, if not otherwise mentioned. The LDO block is a linear voltage regulator, which provides a regulated 5V.

Figure 8: LDO Parameters

| Symbol            | Parameter                    | Min  | Тур | Max  | Unit | Note                           |

|-------------------|------------------------------|------|-----|------|------|--------------------------------|

| V <sub>SUP</sub>  | Input supply voltage         | 6    | 12  | 32   | V    |                                |

| V5V               | Output voltage range         | 4.75 | 5.0 | 5.25 | V    |                                |

| I <sub>LOAD</sub> | Load Current                 |      |     | 50   | mA   |                                |

| ICC_SH            | Output short circuit current |      | 85  | 250  | mA   | NORMAL mode                    |

| PSRR              | PSRR                         |      | 60  |      | dB   | f=1kHz / No production<br>test |

| 1 3/111           | ronn                         |      | 35  |      | ub   | f=1MHz / No production test    |

| CL1               | LDO output Capacitor 1       | 2.2  |     | 10   | μF   | Electrolytic                   |

| ESR1              | LDO output capacitor i       | 1    |     | 10   | Ω    | Liectrolytic                   |

| CL2               | LDO output Capacitor 2       | 100  |     | 220  | nF   | Ceramic                        |

| ESR2              | 200 output capacitor 2       | 0.02 |     | 1    | Ω    | Ceramic                        |

#### Note(s) and/or Footnote(s):

- 1. In NORMAL mode, maximum load current will be 50mA. After internal thermal shutdown, current limit is 20mA.

- 2. The LDO is disabled in SLEEP mode.

Page 12ams DatasheetDocument Feedback[v1-02] 2014-Nov-06

## **High-precision Bandgap Reference**

-40°C <  $T_J$  < 115°C; all voltages are with respect to ground (GND).

Figure 9: Bandgap Reference Parameters

| Symbol                  | Parameter                                       | Min | Тур   | Max  | Unit | Note                       |  |

|-------------------------|-------------------------------------------------|-----|-------|------|------|----------------------------|--|

| BG_Out                  | Reference output after trim                     | 1.2 | 1.235 | 1.27 | V    | After temperature trim     |  |

| BG_out_T <sub>var</sub> | Reference variation with respect to Temperature |     | ±2.5  | ±4   | mV   | After trim on the absolute |  |

| PSRR1K                  | PSRR at 1KHz                                    | 20  |       |      | dB   | No production test         |  |

| PSRRDC                  | PSRR at DC                                      | 80  |       |      | dB   |                            |  |

#### Note(s) and/or Footnote(s):

1. This bandgap output is the reference for the V5V (LDO) regulator.

## **Digital to Analog Converter**

-40°C <  $T_J$  < 115°C; all voltages are with respect to ground (GND).

Figure 10:

Digital to Analog Converter

| Symbol                | Parameter               | Min   | Тур  | Max   | Unit | Note                                                                                              |

|-----------------------|-------------------------|-------|------|-------|------|---------------------------------------------------------------------------------------------------|

| V <sub>SUP_DAC</sub>  | Input supply voltage    | 4.75  | 5    | 5.25  | ٧    | LDO output as supply                                                                              |

| V <sub>INREF</sub>    | Input reference voltage | 4.485 | 4.5  | 4.515 | V    | After absolute trim at 0 hours, specification does not include solder stress/board stress effects |

| D <sub>IN</sub>       | Resolution              |       | 12   |       | bits | Guaranteed by design                                                                              |

| F <sub>DAC</sub>      | Update rate             |       | 10   |       | KHz  |                                                                                                   |

| T <sub>SETT_DAC</sub> | Settling time           |       | 50   |       | μs   | No production test                                                                                |

| DAC <sub>INL</sub>    | INL                     |       | ±4   |       | LSB  | The production test                                                                               |

| DAC <sub>DNL</sub>    | DNL                     |       | ±0.5 |       | LSB  |                                                                                                   |

ams Datasheet Page 13

[v1-02] 2014-Nov-06 Document Feedback

#### **Analog to Digital Converter**

-40°C <  $T_J$  < 115°C; all voltages are with respect to ground (GND).

Figure 11: Analog to Digital Converter

| Symbol                | Parameter                    | Min   | Тур | Max   | Unit | Note                                                                                              |

|-----------------------|------------------------------|-------|-----|-------|------|---------------------------------------------------------------------------------------------------|

| V <sub>SUP</sub>      | Input supply voltage         | 4.75  | 5   | 5.25  | V    | LDO output as supply                                                                              |

| V <sub>INREF</sub>    | Input reference voltage      | 4.485 | 4.5 | 4.515 | V    | After absolute trim at 0 hours, specification does not include solder stress/board stress effects |

| D <sub>OUT</sub>      | Resolution                   |       | 12  |       | bits |                                                                                                   |

| T <sub>MEAS_ADC</sub> | Measurement time per channel |       | 1.4 |       | ms   |                                                                                                   |

| ADC <sub>INL</sub>    | INL                          |       | ±4  |       | LSB  | No production test.                                                                               |

| ADC <sub>DNL</sub>    | DNL                          |       | ±2  |       | LSB  | No production test.                                                                               |

#### **Pre-Regulator**

This Pre\_reg is an internal regulator which provides supply to digital and a few analog blocks..

-40°C <  $T_J$  < 115°C; all voltages are with respect to ground (GND).

Figure 12: Pre-reg Parameters

| Symbol    | Parameter                   | Min | Тур | Max | Unit | Note |

|-----------|-----------------------------|-----|-----|-----|------|------|

| $V_{SUP}$ | Input supply voltage        | 6   | 12  | 32  | V    |      |

| P5V       | Prereg_output voltage range | 4.3 | 5.0 | 5.5 | V    |      |

| 3V3       | 3.3V_output voltage range   | 2.8 | 3.3 | 3.6 | V    |      |

Page 14ams DatasheetDocument Feedback[v1-02] 2014-Nov-06

#### **PWM Driver**

$40^{\circ}\text{C} < \text{T}_{\text{J}} < 115^{\circ}\text{C}$ ; all voltages are with respect to ground (GND).

Figure 13: PWM Driver

| Symbol                  | Parameter                      | Min | Тур | Max | Unit | Note                                     |

|-------------------------|--------------------------------|-----|-----|-----|------|------------------------------------------|

| V5V                     | Output voltage                 | 4.5 | 5   | 5.5 | V    |                                          |

| F <sub>PWM</sub>        | Frequency of PWM               | 25  | 100 | 200 | KHz  |                                          |

|                         |                                | 22  | 25  | 28  | %    |                                          |

|                         |                                | 12  | 15  | 18  | %    |                                          |

|                         | Duty cycle                     | 17  | 20  | 23  | %    |                                          |

| E_                      |                                | 27  | 30  | 33  | %    | CMOS load mode,                          |

| F <sub>Duty</sub>       |                                | 30  | 35  | 38  | %    | Optocoupler load mode                    |

|                         |                                | 37  | 40  | 43  | %    |                                          |

|                         |                                | 42  | 45  | 48  | %    |                                          |

|                         |                                | 47  | 50  | 53  | %    |                                          |

| F <sub>duty_error</sub> | Duty cycle error               | 7   | 12  | 20  | %    |                                          |

| tr <sub>pwm</sub>       | Rise time                      | 30  | 50  | 80  | ns   | CMOS load mode,<br>Optocoupler load mode |

| tf <sub>pwm</sub>       | Fall time                      | 30  | 50  | 80  | ns   | Guaranteed by design                     |

| Idrive <sub>opto</sub>  | Driver strength                |     | 10  | 12  | mA   | Optocoupler load mode                    |

| Cload <sub>fd_out</sub> | Driver switch load capacitance |     | 60  | 100 | pF   |                                          |

#### **PWM Oscillator**

-40°C <  $T_J$  < 115°C; all voltages are with respect to ground (GND).

Figure 14: PWM Oscillator

| Symbol               | Parameter | Min | Тур | Max | Unit | Note                                                                                                                             |

|----------------------|-----------|-----|-----|-----|------|----------------------------------------------------------------------------------------------------------------------------------|

| fosc                 | Frequency | 90  | 100 | 110 | kHz  | <ul> <li>After the frequency trim.</li> <li>Programmable frequency options for 25KHz, 50KHz and 200KHz are available.</li> </ul> |

| f <sub>OSC_ACC</sub> | Accuracy  |     | ±15 |     | %    |                                                                                                                                  |

## **Oscillator for Digital Circuit**

-40°C <  $T_J$  < 115°C; all voltages are with respect to ground (GND).

Figure 15: Oscillator for Digital Circuit

| Symbol               | Parameter | Min | Тур | Max | Unit | Note                           |

|----------------------|-----------|-----|-----|-----|------|--------------------------------|

| f <sub>OSC-DIG</sub> | Frequency | 9   | 10  | 11  | kHz  | Oscillator for Digital circuit |

| f <sub>OSC_ACC</sub> | Accuracy  |     | ±15 |     | %    |                                |

Page 16ams DatasheetDocument Feedback[v1-02] 2014-Nov-06

## **External Temperature Thresholds**

-40 °C <  $T_{J}$  < 115 °C; all voltages are with respect to ground (GND).

Figure 16: External Temperature Thresholds

| Symbol               | Parameter | Min   | Тур   | Max   | Unit | Note                                                   |

|----------------------|-----------|-------|-------|-------|------|--------------------------------------------------------|

|                      | Code 0000 | 3.084 | 3.165 | 3.238 |      |                                                        |

|                      | Code 0001 | 3.148 | 3.231 | 3.306 |      |                                                        |

|                      | Code 0010 | 3.213 | 3.297 | 3.373 |      |                                                        |

|                      | Code 0011 | 3.277 | 3.363 | 3.441 |      |                                                        |

|                      | Code 0100 | 3.341 | 3.429 | 3.508 |      |                                                        |

|                      | Code 0101 | 3.406 | 3.495 | 3.576 |      |                                                        |

|                      | Code 0110 | 3.470 | 3.561 | 3.643 |      | 16 reference<br>thresholds are with a<br>step of 66mV. |

| Ref_ext_warn/sutdown | Code 0111 | 3.534 | 3.627 | 3.711 | V    |                                                        |

| nci_cxt_warm sucdown | Code 1000 | 3.599 | 3.693 | 3.779 | V    |                                                        |

|                      | Code 1001 | 3.663 | 3.759 | 3.846 |      |                                                        |

|                      | Code 1010 | 3.727 | 3.825 | 3.914 |      |                                                        |

|                      | Code 0011 | 3.792 | 3.891 | 3.981 |      |                                                        |

|                      | Code 0100 | 3.856 | 3.957 | 4.049 |      |                                                        |

|                      | Code 0101 | 3.920 | 4.023 | 4.116 | _    |                                                        |

|                      | Code 0110 | 3.984 | 4.089 | 4.184 |      |                                                        |

|                      | Code 0111 | 4.049 | 4.155 | 4.25  |      |                                                        |

ams Datasheet Page 17

[v1-02] 2014-Nov-06 Document Feedback

# Ron of the Shuttle Switches (Internal Switch for Charging/Discharging)

-40°C  $< T_J < 115$ °C.

Figure 17: Ron of the Shuttle Switches

| Symbol   | Parameter                    | Min | Тур | Max | Unit | Note                                                                                                                                                                                                                 |

|----------|------------------------------|-----|-----|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ron_shut | Shuttle switch ON resistance |     | 5   | 20  | Ω    | The maximum charging/discharging current limit through shuttle switch is 100mA. Only for Cell1 maximum charging/discharging current is limited to 30mA less than 2V of cell voltage at 115 junction of cell voltage. |

### **Over-Temperature Measurement**

## Figure 18: OTM Parameters

| Symbol             | Parameter             |     | Тур | Max | Unit | Note                                 |

|--------------------|-----------------------|-----|-----|-----|------|--------------------------------------|

| T <sub>jshut</sub> | Shut down temperature | 115 | 135 | 145 | °C   | Junction temperature for<br>Shutdown |

| T <sub>jwarn</sub> | Warning temperature   | 100 | 125 | 140 | °C   | Junction temperature for<br>Warning  |

| T <sub>jrecv</sub> | Recovery temperature  | 100 | 115 | 130 | °C   | Junction temperature for Recovery    |

Page 18ams DatasheetDocument Feedback[v1-02] 2014-Nov-06

## Weak Cell Detection (Voltage Comparator)

Figure 19: Weak Cell Detection

| Symbol            | Parameter Min Typ Ma       |      | Max | Unit | Note      |                                          |

|-------------------|----------------------------|------|-----|------|-----------|------------------------------------------|

| V <sub>CELL</sub> | Supply voltage             | -0.3 | 3.6 | 4.5  | V         |                                          |

| V <sub>LOW</sub>  | Low voltage detection      |      | 100 | mV   |           |                                          |

|                   | Minimum input spike filter |      | 2   |      | -<br>- μs | No production test. Programmable option. |

| Tl_spike          |                            |      | 4   |      |           |                                          |

| п_эріке           |                            |      | 6   |      |           |                                          |

|                   |                            |      | 8   |      |           |                                          |

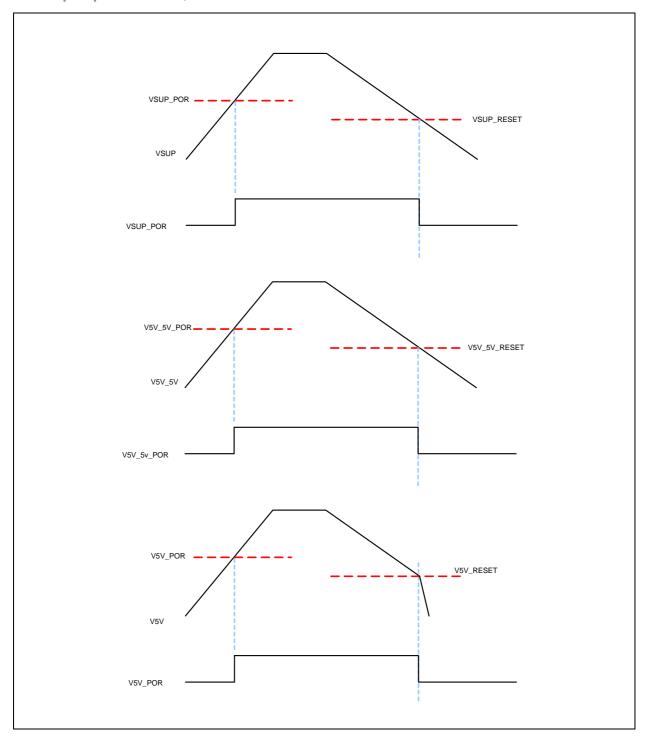

## **Power on Voltage Detection**

Figure 20: Power on Voltage Detection

| Symbol       | Parameter                                                |     | Тур  | Max                 | Unit | Note                                                   |

|--------------|----------------------------------------------------------|-----|------|---------------------|------|--------------------------------------------------------|

| VSUP_POR     | VSUP Power-on-Reset<br>threshold ON                      | 5.2 | 5.5  | 5.8                 | ٧    | Rising edge of VSUP                                    |

| VSUP_RESET   | VSUP Power-on-Reset<br>threshold OFF                     | 4.6 | 4.85 | 5.1                 | V    | Master reset for device                                |

| V5V_IN_POR   | V5V_IN Power-on-Reset<br>threshold ON                    | 3.8 | 4.45 | 4.8                 | V    | Voltages are with respect to VSUP measure as pass fail |

| V5V_IN_RESET | V5V_IN Power-on-Reset<br>threshold OFF                   | 3.6 | 4.1  | 4.5                 | V    | test                                                   |

| V5V_POR      | V5V Power-on-Reset<br>threshold ON                       | 4.1 | 4.5  | 4.7                 | V    | Rising edge of V5V                                     |

| V5V_RESET    | V5V_RESET V5V Power-on-Reset threshold OFF 3.8 4.1 4.3 V |     | V    | Falling edge of V5V |      |                                                        |

ams Datasheet Page 19

[v1-02] 2014-Nov-06 Document Feedback

# **Electrical Characteristics for Digital Inputs and Outputs**

All pull-up, pull-downs have been implemented with active devices.

Figure 21: Digital Inputs and Outputs

| Port Type                   | Symbol              | Parameter                    | Min      | Тур | Max     | Unit | Note                                   |  |  |  |  |  |

|-----------------------------|---------------------|------------------------------|----------|-----|---------|------|----------------------------------------|--|--|--|--|--|

|                             | CS                  |                              |          |     |         |      |                                        |  |  |  |  |  |

|                             | Vt-                 | Negative-going threshold     | 1.62     |     | 2.22    | V    | . V5V=5V                               |  |  |  |  |  |

| INPUT<br>Schmitt<br>Trigger | Vt+                 | Positive-going threshold     | 2.27     |     | 3.42    | V    | · v3v=3v                               |  |  |  |  |  |

| mgger                       |                     |                              |          |     |         |      |                                        |  |  |  |  |  |

|                             | I <sub>lil_cs</sub> | Pull-up current              | -100     |     | -30     | μΑ   | In CS pad, Pulled up to V5V. (ISUP_HV) |  |  |  |  |  |

|                             | SDO                 |                              |          |     |         |      |                                        |  |  |  |  |  |

|                             | V <sub>OH</sub>     | High level<br>output voltage | 2.5      |     |         | V    |                                        |  |  |  |  |  |

|                             | V <sub>OL</sub>     | Low level output voltage     |          |     | 0.4     | V    | VSUP ≥ 6V                              |  |  |  |  |  |

| OUTPUT<br>Tristate          | V <sub>IH</sub>     | High level input<br>voltage  | 0.7*V5V  |     |         | V    |                                        |  |  |  |  |  |

|                             | V <sub>IL</sub>     | Low level input voltage      |          |     | 0.3*V5V | V    |                                        |  |  |  |  |  |

|                             | I <sub>O</sub>      | Output drive current         |          |     | 4       | mA   |                                        |  |  |  |  |  |

|                             |                     |                              | SCLK, SI | DI  |         |      |                                        |  |  |  |  |  |

| IO Buffer                   | V <sub>IH</sub>     | High level input<br>voltage  | 0.7*V5V  |     |         | V    |                                        |  |  |  |  |  |

| io builei                   | V <sub>IL</sub>     | Low level input<br>voltage   |          |     | 0.3*V5V | V    |                                        |  |  |  |  |  |

Page 20ams DatasheetDocument Feedback[v1-02] 2014-Nov-06

| Port Type        | Symbol          | Parameter                    | Min        | Тур    | Max     | Unit | Note                   |

|------------------|-----------------|------------------------------|------------|--------|---------|------|------------------------|

|                  |                 |                              | CVT_NOK    | OUT    |         |      |                        |

|                  | V <sub>OH</sub> | High level<br>output voltage | 2.4        |        |         | V    |                        |

| OUTPUT<br>Buffer | V <sub>OL</sub> | Low level output voltage     |            |        | 0.4     | V    | VSUP ≥ 6V              |

|                  | I <sub>O</sub>  | Output drive current         |            |        | 2       | mA   |                        |

|                  |                 |                              | BD_OL      | JT     |         |      |                        |

|                  | V <sub>OH</sub> | High level<br>output voltage | 2.4        |        |         | V    |                        |

| OUTPUT<br>Buffer | V <sub>OL</sub> | Low level output voltage     |            |        | 0.4     | V    | VSUP ≥ 6V              |

|                  | I <sub>O</sub>  | Output drive current         |            |        | 1       | mA   |                        |

|                  |                 | TR                           | IG_OUT, C  | LK_OUT |         |      |                        |

|                  | V <sub>OH</sub> | High level<br>output voltage | 2.4        |        |         | V    |                        |

| OUTPUT<br>Buffer | V <sub>OL</sub> | Low level output voltage     |            |        | 0.4     | V    | VSUP ≥ 6V              |

|                  | I <sub>O</sub>  | Output drive current         |            |        | 4       | mA   |                        |

|                  |                 |                              | FD_OL      | ΙΤ     |         |      |                        |

|                  | V <sub>OH</sub> | High level input<br>voltage  | 2.4        |        |         | V    |                        |

| OUTPUT<br>Buffer | V <sub>OL</sub> | Low level input voltage      |            |        | 0.4     | V    | VSUP ≥ 6V              |

|                  | I <sub>O</sub>  | Output drive current         |            |        | 24      | mA   |                        |

|                  |                 |                              | MS_SI      | L      |         |      |                        |

| INPUT Buffer     | V <sub>IH</sub> | High level input voltage     |            |        | VSUP    | V    | High voltage input pad |

| IN ST DUITE      | V <sub>IL</sub> | Low level input<br>voltage   |            |        | 0.3*V5V | V    |                        |

|                  |                 | (                            | CLK_IN, TR | IG_IN  | •       |      |                        |

| INPUT<br>Schmitt | Vt-             | High level input voltage     | 1.62       |        | 2.22    | V    |                        |

| Trigger          | Vt+             | Low level input<br>voltage   | 2.27       |        | 0.3*V5V | V    |                        |

| Port Type               | Symbol          | Parameter                   | Min     | Тур | Max  | Unit | Note          |  |  |

|-------------------------|-----------------|-----------------------------|---------|-----|------|------|---------------|--|--|

| FD_IN,BD_IN,CVT_NOK_IN  |                 |                             |         |     |      |      |               |  |  |

| INPUT Buffer            | V <sub>IH</sub> | High level input<br>voltage | 0.7*V5V |     |      | V    |               |  |  |

| IN OT BUILT             | V <sub>IL</sub> | Low level input<br>voltage  |         |     | 3.42 | V    |               |  |  |

| WAKE_IN Pull up current | lpull_up        | Pull-up current             | -100    |     | -30  | μΑ   | Internal pull |  |  |

#### Note(s) and/or Footnote(s):

1. Test limits for lih and lil are 1.0uA and -1.0uA for input pads.

Page 22ams DatasheetDocument Feedback[v1-02] 2014-Nov-06

#### **Detailed Description**

The device consists of the following blocks:

- · PWM driver

- LDO\_5V with 5V / 50mA output

- Temperature monitor block

- High precision bandgap reference

- DAC for the reference voltage generation

- SAR ADC for cell voltage and external temperature measurement

- Oscillators for PWM drive and for the digital logic

- Pre-Regulator

- SC Comparator

- · Weak cell detection logic

- · PORs on different supplies

#### Voltage Regulator (LDO\_5V)

Power input to the LDO is VSUP pin. It is switched ON when the device is in *NORMAL* mode and switched OFF in *SLEEP* mode. The LDO takes the input from Bandgap and scales it up to the required voltage. It starts charging only after entering *NORMAL* mode. This LDO is the supply for DAC, the PWM driver and Cell voltage comparators.It's additional features are as follows:

- Stability is better than ±2.5% over input range.

- Load current up to 50mA.

#### High Precision Bandgap (HPBG)

AS8506C has a high precision bandgap to generate accurate reference. This reference voltage is used to generate reference for DAC and ADC.

HPBG is trimmed with respect to temperature. Variation of the bandgap with temperature is  $\pm 4$ mV in the temperature range from -40°C to 115°C.

## External Temperature Monitor and Measurement

Two sensor inputs TEMP\_IN1 and TEMP\_IN2 with a comparator on each pin, are available. If the temperature sensor connected to TEMP\_IN1 crosses its threshold, then a warning flag is set in the device (status can be read through SPI) and the device will continue balancing.

If the temperature sensor connected to TEMP\_IN2 crosses its threshold, then a flag is set in the device and balancing is stopped; but the device continues to stay in NORMAL mode for maintaining synchronism. In both the cases, the microcontroller will be interrupted by a pulse on CVT\_NOK\_OUT pin.

ams Datasheet Page 23

[v1-02] 2014-Nov-06 Document Feedback

In case the external temperature sensors are not being used, then both the inputs must be connected to GND pin through 1k resistor. In the measurement phase, external temperature is measured through the SAR ADC. Both channels of temperature will be measured and stored in temp\_in1\_lsb\_reg to temp\_in2\_msb\_reg.

#### **Internal Temperature Monitor**

The internal temperature monitor has two thresholds at  $T_{jwarn}$  125°C and  $T_{jshut}$  135°C. If the internal temperature exceeds 125°C, then a warning flag is set in the device (status can be read through SPI) and the device will continue balancing.

If the internal temperature exceeds 135°C, then a flag is set in the device and balancing is stopped; but the device continues to stay in *NORMAL* mode for maintaining synchronism. In both the cases, the microcontroller will be interrupted by a pulse on CVT\_NOK\_OUT pin. The balance recovery temperature is 115°C.

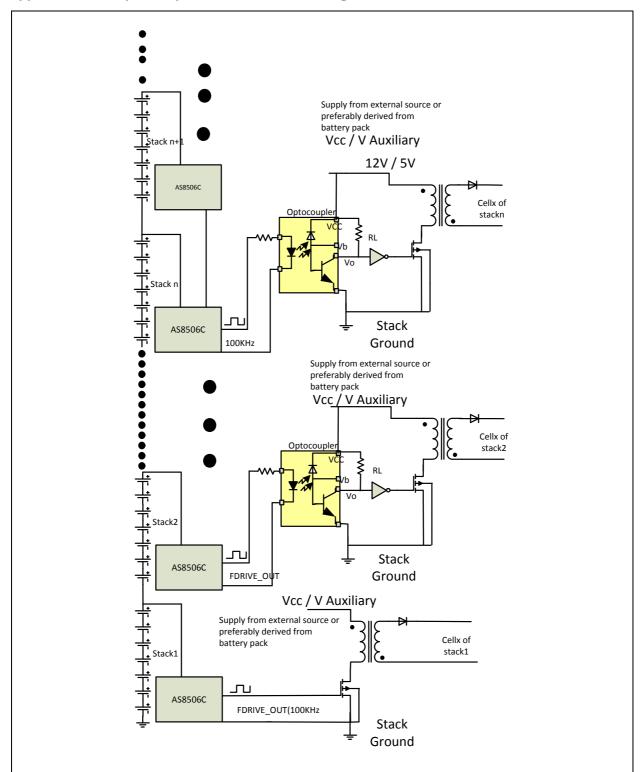

#### **PWM Generator**

In the Balance phase of the AS8506C, based on the decision made during the Compare phase, some part of the cell is charged with the Flyback converter. To drive the external Flyback converter, AS8506C generates a PWM signal to drive external FET or Optocoupler or Isolation device.

The frequency and of the PWM generator can be controlled by timer\_cntl\_reg register.

PWM frequency is not used for the passive balancing.

#### **RC** Oscillator

The AS8506C has a trimable RC oscillator. It is designed to generate  $f_{osc-dig}$  clock for the digital circuit and for the clocking of the IC. Each oscillator will be trimmed with the process to get the accuracy to  $f_{osc-accy}$  with 5-bit OTP Factory trim code.

#### **DAC for the Reference Generation**

AS8506C has a 12-bit DAC to generate the cell reference voltage, cell threshold low and high voltage. The DAC code is written into AS8506C with SPI interface from microcontroller. The output of the DAC is given to one of the inputs of the comparators, to compare the cell voltages synchronously. Reference for the DAC is 4.5V, which is internally generated and is available as reference for temperature inputs on REF\_T.

Page 24

Document Feedback [v1-02] 2014-Nov-06

#### SAR ADC

AS8506C has a 12-bit SAR ADC to measure the cell voltage and external temperature. The SAR ADC uses the 12-bit DAC to generate the digital code. The SAR ADC range is 1.8V to 4.5V for cell voltage measurement and 0.2V to 4.5V for the temperature measurement.

Cell voltage and temperature is measured in the short trigger phase. After the trigger goes 'high', compare phase starts and then all the cell voltages and external temperature are measured and stored in the digital registers.

#### **Pre-Regulator**

AS8506C has an internal pre-regulator, which generates supply voltages for the internal blocks. Pre-Regulator output is used as a supply for the oscillators. All the digital logic and the FSM will work on the pre-regulator supply.

In SLEEP mode only the pre-regulator will be working along with the WAKE\_IN detect circuit.

#### **Cell Threshold**

AS8506C has the potential to set the two threshold levels to the cell voltage through pins CELL\_THU and CELL\_THL. These values can be set externally, (or) through OTP trim bits, (or) from the external microcontroller by writing DAC code into the cell threshold registers in the register space.

#### **Weak Cell Detection**

AS8506C has the ability to detect the weak cell. During load conditions, if the cell reaches voltage of about 0.1V to -0.2V, then this variation is detected and stored in the zero cross detection register. This event is indicated to the master device by a pulse on CVT\_NOK\_OUT pin in Compare and Balance phase. The master device indicates the microcontroller by setting CVT\_NOK\_OUT 'high'. In WAIT mode only this will be stored in the register; there won't be any CVT\_NOK\_OUT to  $\mu C$ . The register is cleared on  $\mu C$  reading.

#### **External Resister Divider Control**

AS8506C has the provision to enable the external divider to give the desired cell voltage to the at VREF\_IN pin. External resister divider can be connected between VREF\_H pin to ground. Typical internal ON resistance of the VREF\_H switch is  $30\Omega.$  Calculate the external resister divider values such that the output of the divider will provide the desired reference value. When comparison is not happening, this divider can be disabled using SPI. PORs on Different Supplies

ams Datasheet Page 25

[v1-02] 2014-Nov-06 Document Feedback

AS8506C has power-on-reset blocks on VSUP, V5Vand V5V\_IN supply pins. The values for POR and Reset thresholds are given in Figure 20.

Figure 22: Power-up Sequence of VSUP, V5V and VSUP+5V

Page 26ams DatasheetDocument Feedback[v1-02] 2014-Nov-06

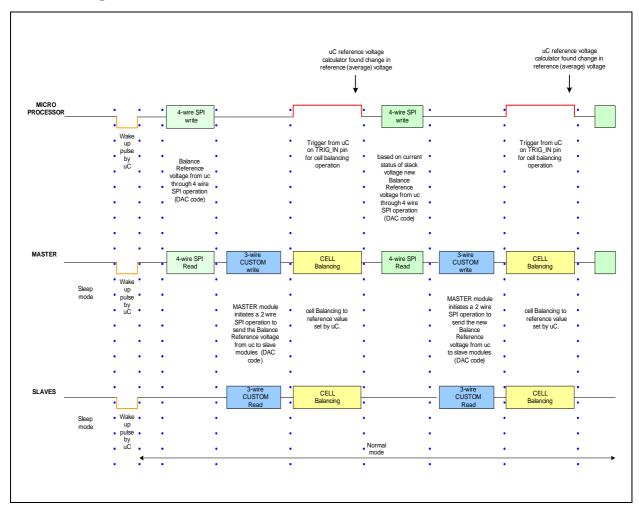

#### **AS8506C System Operation**

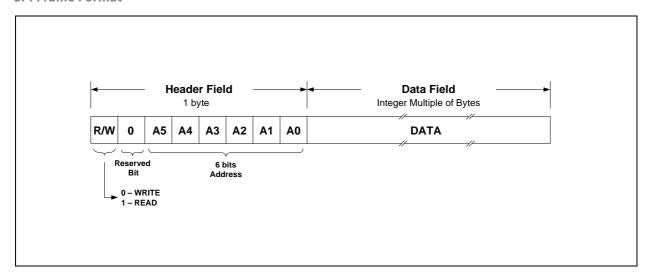

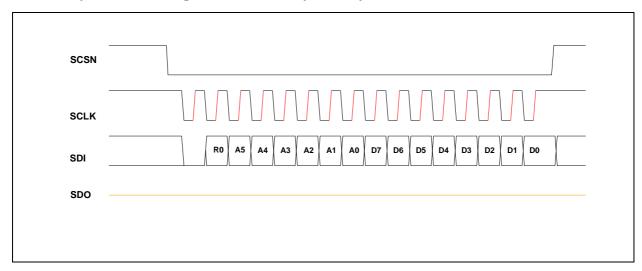

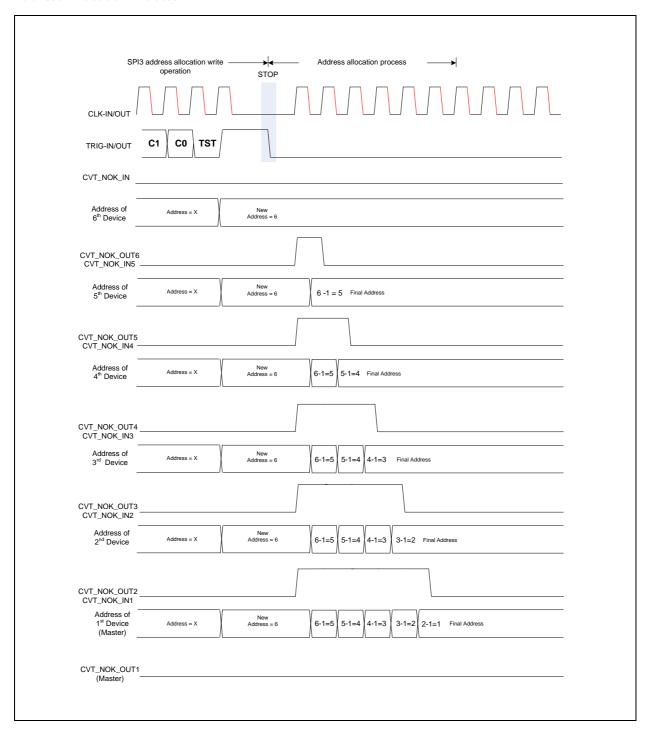

The AS8506C battery stack system can be set up by configuring one AS8506C device as 'Master' and the rest as 'Slave' devices. The AS8506C Master device is connected to the microcontroller, and the Slave devices are connected to Master through a daisy-chain of 3-wire customized SPI protocol. The microcontroller can communicate to the Slave devices through the Master. On power-up of the system, the microcontroller must assign an address to all AS8506C devices including the Master. The microcontroller can assign the address to AS8506C devices by initiating the address allocation process, by writing a top most Slave device address into dadd\_for\_allc\_reg register of Master and then writing '07' data into spi3\_cmd\_reg. Once the address allocation process is successful, the microcontroller can start the cell balancing. If cell balancing or check status command is not triggered by the microcontroller, after WAIT mode timeout period all devices enter into SLEEP mode.

The complete system communication procedure is explained below.

- The microcontroller gives wake pulse on WAKE\_IN to bring the Master and Slaves in NORMAL mode.

- After the wake-up time period, the microcontroller (μC) sends the reference voltage digital code to the Master device through a 4-wire SPI.

- After receiving the digital reference code from  $\mu$ C, the Master device initiates a 3-wire custom SPI operation to send the digital reference code to the Slave devices.

- The microcontroller waits for the 3-wire SPI operation time period. After the 3-wire SPI time period, it initiates the cell balancing through TRIG\_IN. The balancing will continue as long as TRIG\_IN is 'High'.

- The microcontroller can change the reference value at any time by making TRIG\_IN 'Low' and initiating a 4-wire SPI with new value of reference code. From here on, the procedure is same as from point 3.

- The balance done is indicated on BD\_OUT pin.

- The failure in the 3-wire SPI operation is indicated on CVT\_NOK\_OUT pin.

ams Datasheet Page 27

[v1-02] 2014-Nov-06 Document Feedback

Figure 23: Functional Diagram of AS8506C

Page 28ams DatasheetDocument Feedback[v1-02] 2014-Nov-06

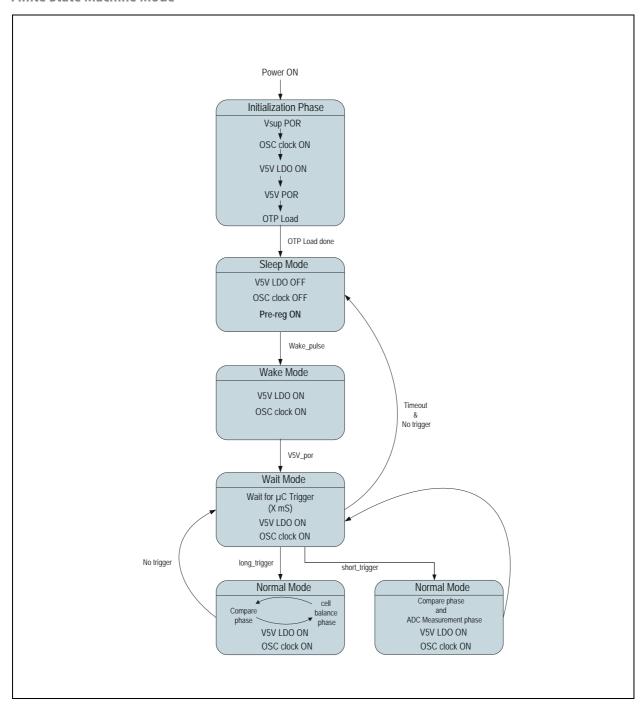

## **Functional State Diagram**

Figure 24: Finite State Machine Mode

ams Datasheet Page 29

[v1-02] 2014-Nov-06 Document Feedback

#### **Operating Modes**

The AS8506C has two main operating modes *NORMAL* and *SLEEP*, and has two transition modes *WAIT* and *WAKE*. The transition modes are intermediate modes for switching from *SLEEP* to *NORMAL* and vice versa. The detailed operation of each mode is explained in subsequent sections. The initialization phase is explained in Initialization Sequence.

#### **NORMAL** Mode

The device enters into NORMAL from WAKE when it receives a short or long trigger. The NORMAL mode is a full functional mode, where all the power supply and analog blocks are in ON-state and the digital is fully functional.

The NORMAL mode has two phases of operation:

- · Diagnosis phase

- Compare and Balance phase

#### **Diagnosis Phase**

In Diagnosis phase AS8506C detects the number of cells connected to the device. The connected cell voltages are then compared with upper & lower thresholds and target cell voltage of all cells connected. Upper and lower cell voltage thresholds as well as target cell voltages are provided from external in analog or digital format. The Diagnosis phase sequence of operation is explained below.

- Detects number of cells connected to the device by comparing each cell terminals to cell detect threshold voltage.

- Simultaneously compares each connected cell voltage with set lower operating voltage threshold Vlimit\_L. If any of the cell voltages is less than the set lower operating threshold, then an indication is given on CVT\_NOK\_OUT pin stating that one/more cell voltages are not within the operating voltage threshold range. Each cell status is stored in cel\_low\_thsld\_stat\_reg register.

- Simultaneously compares each connected cell voltage

with set higher operating voltage threshold Vlimit\_H. If

any of the cell voltages is greater than the set higher

operating threshold, then an indication is given on

CVT\_NOK\_OUT pin stating that one/more cell voltages are

not within the operating voltage threshold range. Each

cell status is stored in cel\_high\_thsld\_stat\_reg register.

- Simultaneously compares each connected cell voltage with reference value. This result is stored in cel\_ref\_stat\_reg register and used in balance phase. Cell reference can be provided by microcontroller by writing into register or by providing input at external pin VREF\_IN.

- Enables the SAR ADC and measures each cell voltage and two temperature inputs sequentially. The 12 bits cell voltage and temperature inputs information is stored in respective registers.

Page 30

Document Feedback

[v1-02] 2014-Nov-06

At the end of the Diagnosis phase, if trigger signal is 'High' then it enters into Balance phase. If trigger signal is 'Low' it enters into *WAIT* mode.

The Diagnosis phase without the cell voltage and temperature measurement with SAR ADC is called **Compare phase**.

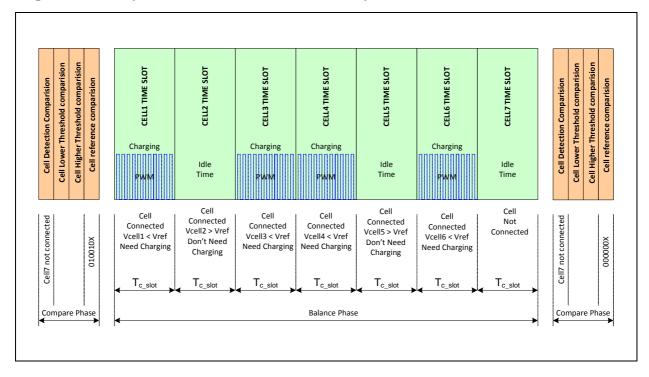

#### Compare and Balance Phase

The Balance phase is basically a charging cycle in case of active balancing and a discharging cycle in case of passive balancing. The Balance phase is divided into 7 time slots. The device will move through all 7 time slots irrespective of number of cells connected to the device. This is done to keep synchronization between each module in case of battery stack system. One time slot is assigned to each cell (sequential order) for charging or discharging. The period of time slots is programmable (see Status Registers).

In each time slot, following operations are done.

- Check CVT\_NOK flag status. If CVT\_NOK flag is set, then no operation is done till time slot is over. If CVT\_NOK flag is not set, then move to the next step.

- Based on Diagnosis phase results, shuttle switch corresponding to current time slot cell is switched ON for charging that cell in case of active balancing, and discharging in case of passive balancing.

- The PWM generator is enabled and PWM driver start driving the Flyback converter FET (external component) in case of active balancing. The PWM frequency and duty cycles are factory programmable and also register controllable. In case of stack system, the bottom module PWM driver is enabled when there is a request of charging or discharging from top module on FD\_OUT pin.

- At the end of the current time slot, stop the PWM generator and then open the corresponding shuttle switches. The device moves to the next time slot.

In the Balance phase, at any point, if the trigger input goes 'Low', then the device suspends balancing operation and enters into *WAIT* mode.

An example of Compare and Balance (active balance) phase sequence with respect to time is given in Figure 25. In this example it is assumed that only 6 cells are connected to AS8506C and comparators' outputs at Diagnosis phase is "010010X";

#### Where:

'0' indicates respective cell voltage is less than target voltage and needs charging.

'1' indicates respective cell voltage is more than target voltage and charging is not needed.

'X' indicates no cell is connected to respective comparator and output is neglected.

ams Datasheet Page 31

[v1-02] 2014-Nov-06 Document Feedback

Figure 25:

Diagnosis and Compare and Balance Phase with Time Sequence for AS8506C

#### Sleep Mode

This is the least power consumption mode of AS8506C. In this mode only pre-reg is ON, rest all analog blocks are OFF and digital clock is disabled. Only a digital wake detection circuit is active. The device enters into this mode when there is no trigger from microcontroller for time greater than *WAIT* mode timeout period.

#### **Wait Mode**

This mode is a transition mode, where the device waits for command on TRIG\_IN pin either from microcontroller, (or) from below module in case of stack system. The device will be in this state for T<sub>WMODE\_TOUT</sub> period. After the timeout, the device enters into *SLEEP* mode. In the *WAIT* period all power blocks are ON, all analog blocks are ON and digital is also functional. In this mode, power consumption is lesser than *NORMAL* mode because there are no charge balancing activities being carried out.

#### **Wake Mode**

This is also a transition mode, where the device does initialization after exiting *SLEEP* mode. In the *SLEEP* mode if AS8506C receives a wake pulse of width T<sub>WAKE</sub>, the device enters into *WAKE* mode. In the *WAKE* mode device enables the V5V LDO and waits for V5V\_por\_n signal. Once V5V\_por\_n signal becomes 'High', the device enters into *WAIT* mode.

Page 32

Document Feedback

[v1-02] 2014-Nov-06

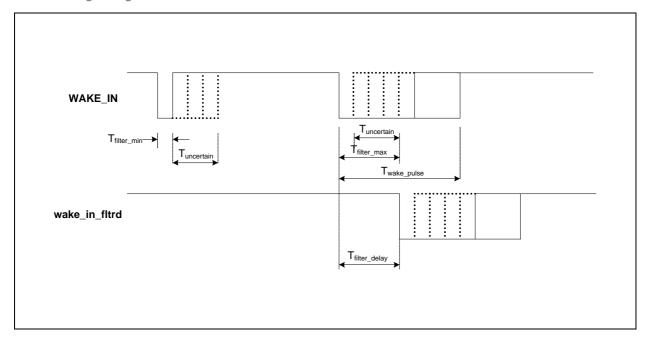

#### Wake-up Event

The AS8506C device comes out of *SLEEP* mode by a wake pulse on the WAKE\_IN pin. To avoid false wake by noises on the WAKE\_IN, the wake signal (Low pulse) is taken through a low-pass filter from WAKE\_IN pin. When a pulse of width Twake\_pulse is given on the WAKE\_IN by the microcontroller, the device wakes up and enters into *WAKE* mode. The low-pass filter discards all signals having width less than Tfilter\_min and allows all signals with width greater than Tfilter\_max. The filter is uncertain in Tuncertain region. The negative edge which is passing through the filter will wake the device from *SLEEP* mode. In chain of AS8506C devices, to propagate the negative edge the microcontroller has to give minimum low pulse of width Twake\_pulse. Before entering into *SLEEP* mode the wake pin must be 'High'.

Figure 26: WAKE-UP Signaling

ams Datasheet Page 33

[v1-02] 2014-Nov-06 Document Feedback

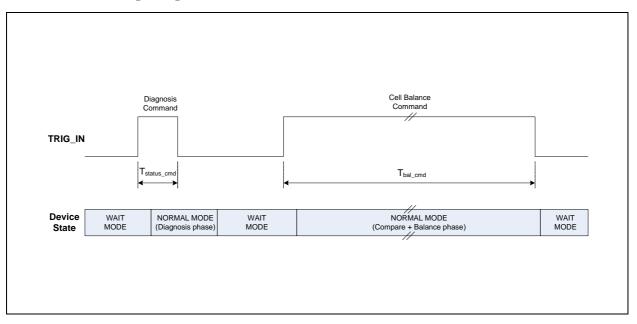

#### Trigger Event

The AS8506C device enters into *NORMAL* mode only when a valid command is present on the TRIG\_IN pin. There are two commands in the device.

- · Diagnosis command

- · Cell balance command

When a high pulse of width T<sub>diag\_cmd</sub> as shown in Figure 27, is given on TRIG\_IN pin, the device performs the following operations.

- Compares all connected cell voltages with the set lower operating voltage threshold, and if any of the cell voltage is less than lower threshold, then sets a corresponding flag in the cel\_low\_thsld\_stat\_reg register. This is indicated by high pulse on CVT\_NOK\_OUT pin.

- Compares all connected cell voltages with the set higher operating voltage threshold, and if any of the cell voltage is more than higher threshold, then sets a corresponding flag in the cel\_high\_thsld\_stat\_reg register. This is indicated by high pulse on CVT\_NOK\_OUT pin.

- Sets a corresponding flag in the temp\_stat\_reg register if ambient temperature or internal chip temperature is higher than respective thresholds. This is indicated by high pulse on CVT\_NOK\_OUT pin.

- It will enable SAR ADC and starts measuring each cell voltage, and then measures temperature channel measurement. The 12 bits digital value will be stored in corresponding registers.

Thus, on diagnosis command the device gives the cell operating voltage, ambient temperature and internal temperature status with respect to its safe operating range.

When the TRIG\_IN pin is 'High' for longer than the status command, the device enters into Balance phase. Depending upon cell voltage status, the device starts balancing the cell voltages. The cell voltage balancing is continued till the high voltage on the TRIG\_IN pin. As soon as TRIG\_IN goes 'Low', the device stops balancing and enters into WAIT mode. Thus, the microcontroller has full control over the balancing time and stop balancing whenever required.

Page 34

Document Feedback [v1-02] 2014-Nov-06

Figure 27: TRIG\_IN Command Signaling

ams Datasheet Page 35

[v1-02] 2014-Nov-06 Document Feedback

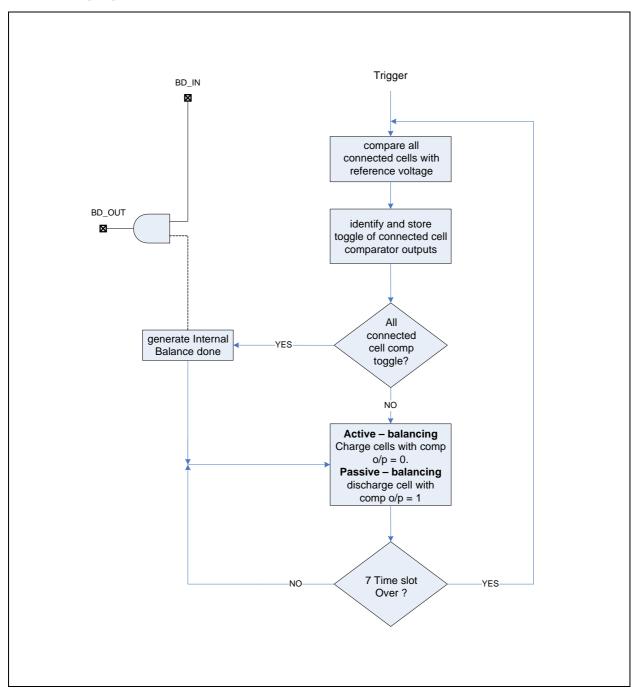

## **Balancing Algorithm**

Figure 28: Cell Balancing Algorithm

Page 36

Document Feedback

[v1-02] 2014-Nov-06

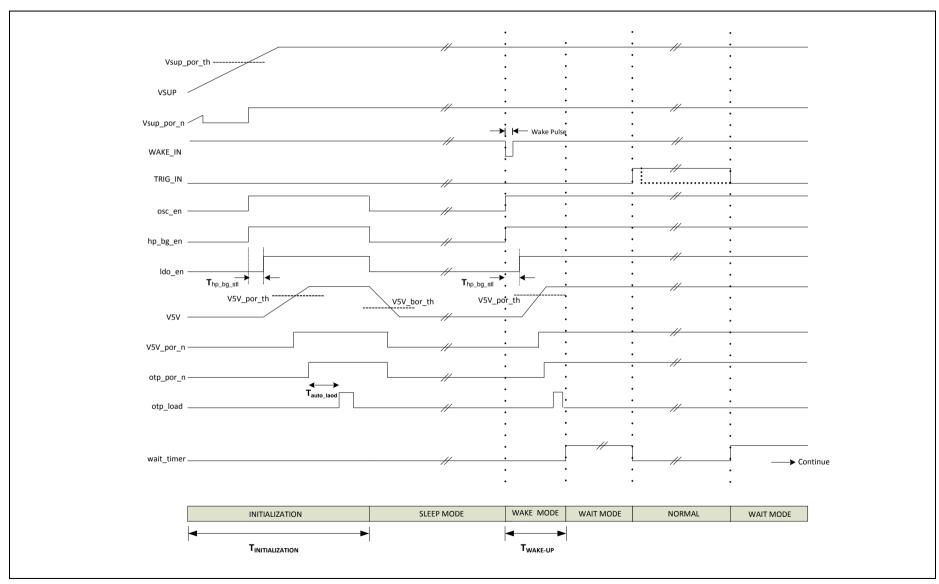

#### **Initialization Sequence**

The power-up initialization sequence diagram for AS8506C is shown in Figure 29.

- When the power supply is switched ON, initially VSUP POR output Vsup\_por\_n is 'Low'; hence all the digital logic will be in reset state.

- Once the VSUP crosses the Vsup\_por\_th, the VSUP POR output becomes 'High' enabling the oscillator and high-precision bandgap (HPBG) block.

- The digital block is now operational. It will now enable the V5V LDO and waits for V5V\_por\_n high signal from the V5V POR block.

- Once the V5V crosses V5V\_por\_th, the V5V\_por\_n will be 'High'. The OTP auto load command is generated by 'High' on otp\_por\_n signal. Now the device waits for T<sub>auto\_load</sub> period for OTP contents to load into digital local registers.

- After the OTP contents are loaded into digital local registers, the device power-up sequence is completed. The device enters into SLEEP mode. In SLEEP mode, the LDO, oscillator and HPBG are disabled.

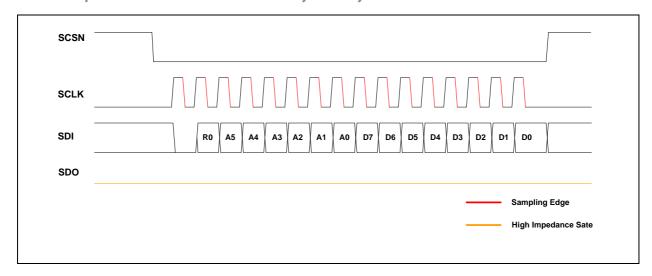

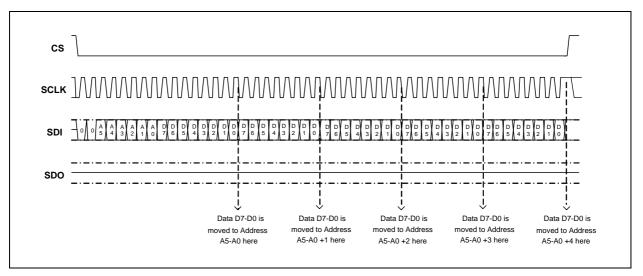

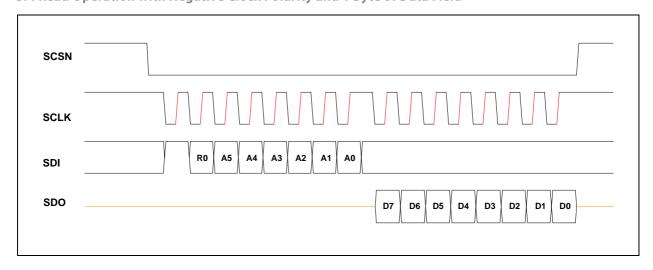

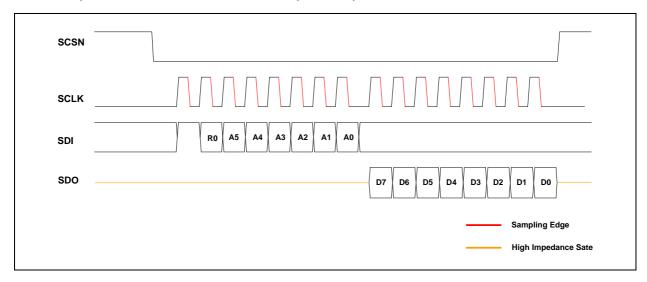

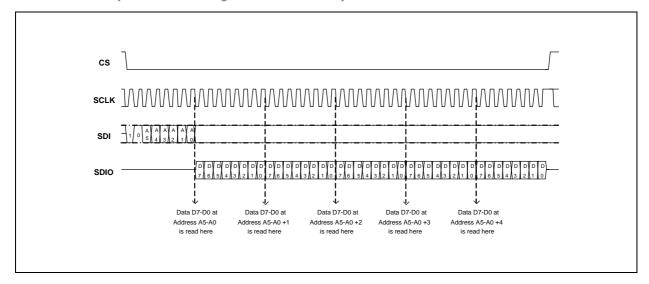

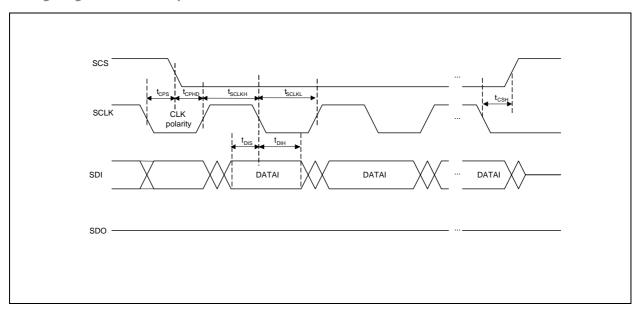

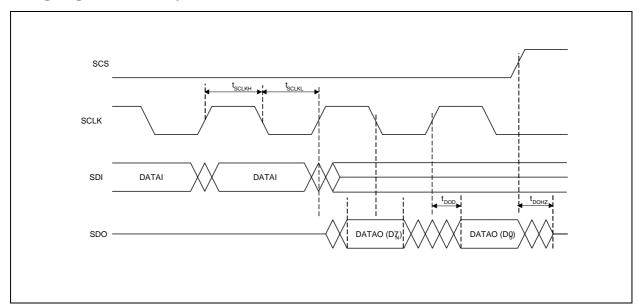

- The wake-up circuit monitors the WAKE\_IN pin for wake-up pulse. When a wake-up pulse is received, the oscillator and HPBG block are enabled and device enters into WAKE mode. In the WAKE mode, the device enables V5V LDO and waits for V5V\_por\_n high signal.