# 2M x 32 FLASH

FLASH MEMORY MODULE

#### AVAILABLE AS MILITARY SPECIFICATIONS

- Military Processing (MIL-STD-883C para 1.2.2)

- Temperature Range -55C to 125C

#### FEATURES

- Fast access times of 90ns, 120ns, and 150ns

- 5.0V  $\pm 10\%$ , single power supply operation

- Low power consumption(TYP): 4µA CMOS stand-by

- \* TYP ICC(active) <120mA for READ/WRITE • 20 year DATA RETENTION

- Minimum 1,000,000 Program/Erase Cycles per sector guaranteed

- 32 equal sectors of 64 Kbytes each

- Any combination of Sectors can be Erased

- Group Sector Protection

- Supports FULL Chip Erase

- Compatible with JEDEC standards

- Embedded Erase and Program Algorithms

• Data\ Polling and Toggle bits for detection of program or erase cycle completion.

- Erase Suspend/Resume

- Hardware Reset pin (RESET\)

• Built in Decoupling Caps and Multiple Ground Pins for Low Noise Operation

• Separate Power and Ground Planes to improve noise immunity

| OPTION                                                                                  | MARKING |

|-----------------------------------------------------------------------------------------|---------|

| • Timing                                                                                |         |

| 90ns                                                                                    | -90     |

| 120ns                                                                                   | -120    |

| 150ns                                                                                   | -150    |

| Packages                                                                                |         |

| Ceramic Quad Flat Pack (0.88" sq)<br>- MAX height .140"<br>- Stand-off Height .035" min | QT      |

#### For more products and information please visit our web site at *www.micross.com*

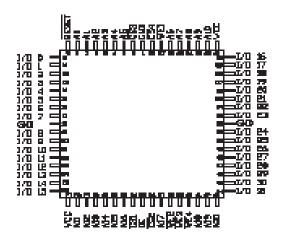

**FIGURE 1: PIN ASSIGNMENT**

(Top View)

#### **GENERAL DESCRIPTION**

The AS8F2M32 is a 64 Mbit, 5.0 volt-only Flash memory. This device is designed to be programmed in-system with the standard system 5.0 volt VCC supply. The AS8F2M32 offers an access time of 90ns, allowing high-speed microprocessors to operate without wait states. To eliminate bus contention, the device has separate chip enable (CE\), write enable (WE\) and output enable (OE\) controls.

The device requires only a single 5.0 volt power supply for both read and write functions. internally generated and regulated voltages are provided for the program and erase operations.

The device is entirely command set compatible with the JEDEC single-power-supply FLASH standard. Commands are written to the command register using standard microprocessor write timings. Register contents serve as input to an internal state-matching that controls the erase and programming circuitry. Write cycles also internally latch addresses and data needed for the programming and erase operations. Reaching data out of the device is similar to reading from other FLASH or EPROM devices.

Device programming occurs by executing the program command sequence. This initiates the Embedded Program algorithm - an internal algorithm that automatically time the program pulse widths and verifies proper cell margin.

Device erasure occurs by executing the erase command sequence. This initiates the Embedded Erase algorithm - an internal algorithm that automatically preprograms the array (if it is not already programmed) before executing the erase operation. During erase, the device automatically times the erase pulse widths and verifies proper cell margin.

The host system can detect whether a program or erase operation is complete by observing the RY/BY\ pin, or by reading the DQ7 (DATA\ Polling) and DQ6 (toggle) status bits. After a program or erase cycle has been completed, the device is ready to read array data or accept another command.

Micross Components reserves the right to change products or specifications without notice

(continued on page 2)

#### **GENERAL DESCRIPTION (cont.)**

The Sector Erase Architecture allows memory sectors to be erased and reprogrammed without affecting the data contents of other sectors. The device is fully erased when shipped from the factory.

Hardware Data Protection measures include a low VCC detector that automatically inhibits write operations during power transitions. The Hardware Sector Protection feature disables both program and erase operations in any combinations of the sectors of memory. This can be achieved via programming equipment.

The Erase Suspend feature enables the user to put erase on hold

for any period of time to read data form, or program data to, any sector that is not selected for erasure. True background erase can thus be achieved.

The Hardware RESET\ pin terminates any operation in progress and resets the internal state machine to reading array data. The RESET\ pin may be tied to the system reset circuitry. A system reset would thus also reset the device, enabling the system microprocessor to read the boot-up firmware from the FLASH memory.

The system can place the device into the standby mode. Power consumption is greatly reduced in this mode.

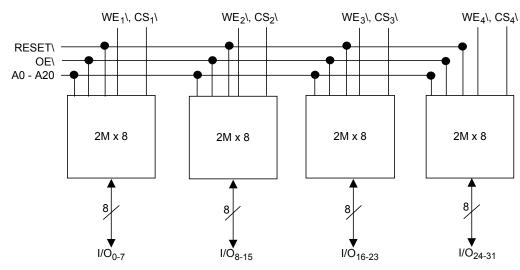

#### FIGURE 2: FUNCTIONAL BLOCK DIAGRAM

#### **PIN DESCRIPTION**

| PIN                 | DESCRIPTION         |

|---------------------|---------------------|

| I/O <sub>0-31</sub> | Data Inputs/Outputs |

| A <sub>0-20</sub>   | Address Inputs      |

| WE\ <sub>1-4</sub>  | Write Enables       |

| CS\ <sub>1-4</sub>  | Chip Selects        |

| OE\                 | Output Enable       |

| V <sub>CC</sub>     | Power Supply        |

| GND                 | Ground              |

| RESET\              | Reset               |

#### **ABSOLUTE MAXIMUM RATINGS**\*

| Voltage on any pin relative to $V_{SS}$ , $V_T^{**}$ 2.0V to +7.0V      |

|-------------------------------------------------------------------------|

| Power Dissipation, P <sub>T</sub> 4W                                    |

| Storage Temperature, T <sub>stg</sub> 65°C to +125°C                    |

| Short Circuit Output Current, I <sub>OS</sub> (1 output at a time)100mA |

| Endurance - Write/Erase Cycles100,000 min cycles                        |

| Data Retention                                                          |

\*Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

\*\*Junction temperature depends upon package type, cycle time, loading, ambient temperature and airflow, and humidity (plastics).

## ELECTRICAL CHARACTERISTICS AND RECOMMENDED DC OPERATING CONDITIONS

| DESCRIPTION                                         | CONDITIONS                                                                                                       | SYMBOL             | MIN                    | MAX  | UNITS |

|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--------------------|------------------------|------|-------|

| Input Leakage Current                               | $V_{CC}$ = 5.5, $V_{IN}$ = GND to $V_{CC}$                                                                       |                    | -10                    | 10   | μA    |

| Output Leakage Current                              | $V_{CC}$ = 5.5, $V_{IN}$ = GND to $V_{CC}$                                                                       | I <sub>LOx32</sub> | -10                    | 10   | μA    |

| V <sub>CC</sub> Active Current for Read             | $CS = V_{IL}, OE = V_{IH}$                                                                                       | I <sub>CC1</sub>   |                        | 160  | mA    |

| V <sub>CC</sub> Active Current for Program or Erase | $CS = V_{IL}, OE = V_{IH}$                                                                                       | I <sub>CC2</sub>   |                        | 240  | mA    |

| V <sub>CC</sub> CMOS Standby                        | $V_{CC}$ = 5.5V, All Inputs @ $V_{CC}$ - 0.2V or $V_{SS}$ +0.2V,<br>RESET\ = CS\ <sub>1-4</sub> = $V_{CC}$ -0.2V |                    |                        | 4    | mA    |

| V <sub>CC</sub> Standby Current                     | $V_{CC}$ = 5.5, CS\ = $V_{IH}$ , RESET\ = $V_{CC} \pm 0.3V$ , f=0                                                | I <sub>CC3</sub>   |                        | 8    | mA    |

| Output Low Voltage                                  | I <sub>OL</sub> = 12.0 mA, V <sub>CC</sub> = 4.5                                                                 | V <sub>OL</sub>    |                        | 0.45 | V     |

| Output High Voltage                                 | I <sub>OH</sub> = -2.5 mA, V <sub>CC</sub> = 4.5                                                                 | V <sub>OH</sub>    | 0.85 x V <sub>CC</sub> |      | V     |

| Low V <sub>CC</sub> Lock-Out Voltage                |                                                                                                                  | V <sub>LKO</sub>   | 3.2                    | 4.2  | V     |

$(4.5V \le VCC \le 5.5V$ ,  $-55^{\circ}C \le T_A \le +125^{\circ}C)$

| PARAMETER          | SYMBOL          | MIN  | TYP | MAX                   | UNIT |

|--------------------|-----------------|------|-----|-----------------------|------|

| Supply Voltage     | V <sub>CC</sub> | 4.5  | 5.0 | 5.5                   | V    |

| Ground             | V <sub>SS</sub> | 0    | 0   | 0                     | V    |

| Input High Voltage | V <sub>IH</sub> | 2.2  |     | V <sub>CC</sub> + 0.5 | V    |

| Input Low Voltage  | V <sub>IL</sub> | -0.5 |     | +0.8                  | V    |

## **CAPACITANCE** $(T_A = +25^{\circ}C)^*$

| PARAMETER          | SYM              | CONDITIONS                        | MAX | UNITS |

|--------------------|------------------|-----------------------------------|-----|-------|

| OE\                | C <sub>OE</sub>  |                                   | 50  | pF    |

| WE\ <sub>1-4</sub> | C <sub>WE</sub>  |                                   | 50  | pF    |

| CS\ <sub>1-4</sub> | C <sub>CS</sub>  | V <sub>IN</sub> = 0V, f = 1.0 MHz | 20  | pF    |

| Data I/O           | C <sub>I/O</sub> |                                   | 20  | pF    |

| Address input      | C <sub>AD</sub>  |                                   | 50  | pF    |

\*Parameter is guaranteed, but not tested.

# ELECTRICAL CHARACTERISTICS AND RECOMMENDED AC OPERATING CONDITIONS

$(V_{CC} = 5.0V, -55^{\circ}C \le T_{A} \le +125^{\circ}C)$

| DADAMETER                                                           |                    | ///                | -9  | 90  | -1  | 20  | -1   | 50  |

|---------------------------------------------------------------------|--------------------|--------------------|-----|-----|-----|-----|------|-----|

|                                                                     | _                  | (M                 | MIN | MAX | MIN | MAX | MIN  | MAX |

| WE\ CONTROLLED (WRITE/ERASE/PRO                                     |                    |                    | í í |     | (00 |     | 1.00 |     |

| Write Cycle Time                                                    | t <sub>AVAV</sub>  | t <sub>WC</sub>    | 90  |     | 120 |     | 150  | ——  |

| Chip Select Setup Time                                              | t <sub>ELWL</sub>  | t <sub>CS</sub>    | 0   |     | 0   |     | 0    |     |

| Write Enable Pulse Width                                            | t <sub>WLWH</sub>  | t <sub>WP</sub>    | 45  |     | 50  |     | 50   |     |

| Address Setup Time                                                  | t <sub>AVWL</sub>  | t <sub>AS</sub>    | 0   |     | 0   |     | 0    |     |

| Data Setup Time                                                     | t <sub>DVWH</sub>  | t <sub>DS</sub>    | 45  |     | 50  |     | 50   |     |

| Data Hold Time                                                      | t <sub>WHDX</sub>  | t <sub>DH</sub>    | 0   |     | 0   |     | 0    |     |

| Address Hold Time                                                   | t <sub>WLAX</sub>  | t <sub>AH</sub>    | 45  |     | 50  |     | 50   |     |

| Write Enable Pulse Width High                                       | t <sub>WHWL</sub>  | t <sub>WPH</sub>   | 20  |     | 20  |     | 20   |     |

| Duration of Byte Progreamming Operation <sup>1</sup>                | t <sub>WHWH1</sub> |                    |     | 300 |     | 300 |      | 300 |

| Sector Erase <sup>2</sup>                                           | t <sub>WHWH2</sub> |                    |     | 15  |     | 15  |      | 15  |

| Read Recovery Time before Write                                     | t <sub>GHWL</sub>  |                    | 0   |     | 0   |     | 0    |     |

| V <sub>CC</sub> Setup Time                                          | t <sub>VCS</sub>   |                    | 50  |     | 50  |     | 50   |     |

| Chip Programming Time <sup>3</sup>                                  |                    |                    |     | 44  |     | 44  |      | 44  |

| Chip Erase Time <sup>4</sup>                                        |                    |                    |     | 256 |     | 256 |      | 256 |

| Output Enable Hold Time <sup>5</sup>                                |                    | t <sub>OEH</sub>   | 10  |     | 10  |     | 10   |     |

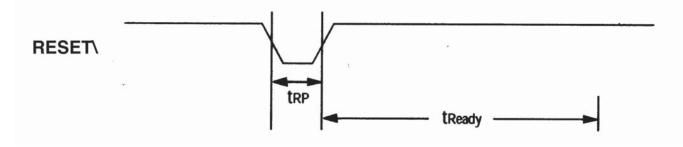

| RESET\ Pulse Width                                                  |                    | t <sub>RP</sub>    | 500 |     | 500 |     | 500  |     |

| READ-ONLY OPERATIONS                                                |                    |                    | 1   |     |     |     |      |     |

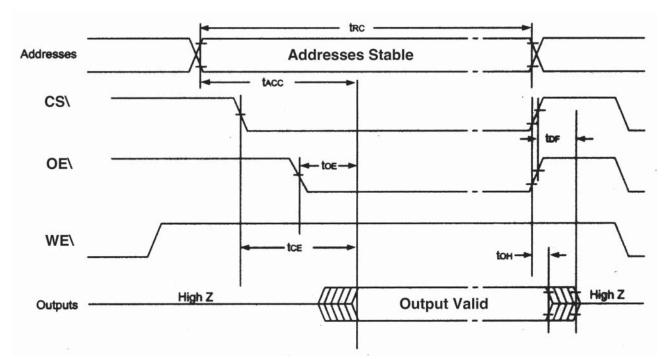

| Read Cycle Time                                                     | t <sub>AVAV</sub>  | t <sub>RC</sub>    | 90  |     | 120 |     | 150  |     |

| Address Access Time                                                 | t <sub>AVQV</sub>  | t <sub>ACC</sub>   |     | 90  |     | 120 |      | 150 |

| Chip Select Access Time                                             | t <sub>ELQV</sub>  | t <sub>CE</sub>    |     | 90  |     | 120 |      | 150 |

| Output Enable to Output Valid                                       | t <sub>GLQV</sub>  | t <sub>OE</sub>    |     | 40  |     | 50  |      | 55  |

| Chip Select High to Output High <sup>6</sup>                        | t <sub>EHQZ</sub>  | t <sub>DF</sub>    |     | 20  |     | 30  |      | 35  |

| Output Enable High to Output High                                   | t <sub>GHQZ</sub>  | t <sub>DF</sub>    |     | 20  |     | 30  |      | 35  |

| Output Hold from Adresses, CS\ or<br>OE\ Change, whichever is First | t <sub>AXQX</sub>  | t <sub>OH</sub>    | 0   |     | 0   |     | 0    |     |

| RST Low to Read Mode <sup>6</sup>                                   |                    | t <sub>Ready</sub> |     | 20  |     | 20  |      | 20  |

| CS\ CONTROLLED (WRITE/ERASE/PRO                                     | GRAM OP            | ERATIO             | NS) |     |     |     |      |     |

| Write Cycle Time                                                    | t <sub>AVAV</sub>  | t <sub>WC</sub>    | 90  |     | 120 |     | 150  |     |

| Write Enable Setup Time                                             | t <sub>WLEL</sub>  | t <sub>WS</sub>    | 0   |     | 0   |     | 0    |     |

| Chip Select Pulse Width                                             | t <sub>ELEH</sub>  | t <sub>CP</sub>    | 45  |     | 50  |     | 50   |     |

| Address Setup Time                                                  | t <sub>AVEL</sub>  | t <sub>AS</sub>    | 0   |     | 0   |     | 0    |     |

| Data Setup Time                                                     | t <sub>DVEH</sub>  | t <sub>DS</sub>    | 45  |     | 50  |     | 50   |     |

| Data Hold Time                                                      | t <sub>EHDX</sub>  | t <sub>DH</sub>    | 0   |     | 0   |     | 0    |     |

| Address Hold Time                                                   | t <sub>ELAX</sub>  | t <sub>AH</sub>    | 45  |     | 50  |     | 50   |     |

| Chip Select Pulse Width High                                        | t <sub>EHEL</sub>  | t <sub>CPH</sub>   | 20  |     | 20  |     | 20   |     |

| Duration of Byte Progreamming Operation <sup>1</sup>                | t <sub>WHWH1</sub> |                    |     | 300 |     | 300 |      | 300 |

| Sector Erase Time <sup>2</sup>                                      | t <sub>WHWH2</sub> |                    |     | 15  |     | 15  |      | 15  |

| Read Recovery Time                                                  | t <sub>GHEL</sub>  |                    | 0   |     | 0   |     | 0    |     |

| Chip Programming Time <sup>3</sup>                                  | U.ILL              | L                  |     | 44  |     | 44  |      | 44  |

| Chip Erase Time <sup>4</sup>                                        |                    |                    |     | 256 |     | 256 |      | 256 |

| Output Enable Hold Time <sup>5</sup>                                |                    | t <sub>OEH</sub>   | 10  |     | 10  |     | 10   |     |

Micross Components reserves the right to change products or specifications without notice.

#### NOTES:

- 1. Typical value for  $t_{WHWH1}$  is 7µs.

- Typical value for t<sub>WHWH2</sub> is 1 sec.

Typical value for Chip Programming is 14 sec.

- 4. Typical value for Chip Erase Time is 32 sec.

- 5. For Toggle an Data Polling.

- 6. This parameter is guaranteed, but not tested.

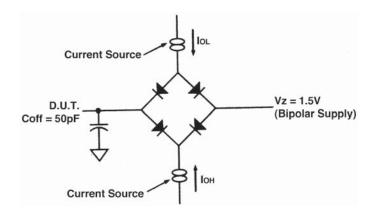

## **AC TEST CONDITIONS**

| PARAMETER                        | ТҮР                                        | UNIT |

|----------------------------------|--------------------------------------------|------|

| Input Pulse Levels               | V <sub>IL</sub> = 0, V <sub>IH</sub> = 3.0 | V    |

| Input Rise and Fall              | 5                                          | ns   |

| Input and Output Reference Level | 1.5                                        | V    |

| Output Timing Reference Level    | 1.5                                        | V    |

## **FIGURE 3: AC TEST CURRENT**

#### FIGURE 4: RESET Timing Diagram

#### FIGURE 5: AC Waveforms for READ Operations

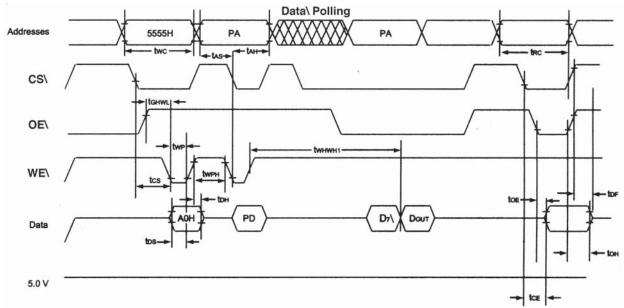

#### FIGURE 6: WE\ Controlled, WRITE/ERASE/PROGRAM Operation

#### NOTES:

- 1. PA is the address of the memory location to be programmed.

- 2. PD is the data to be programmed at byte address.

- 3.  $D_{\gamma}$  is the output of the complement of the data written to each chip.

- 4.  $D_{OUT}$  is the output of the data written to the device.

- 5. Figure indicates last two bus cycles of four bus cycle sequence.

Micross Components reserves the right to change products or specifications without notice

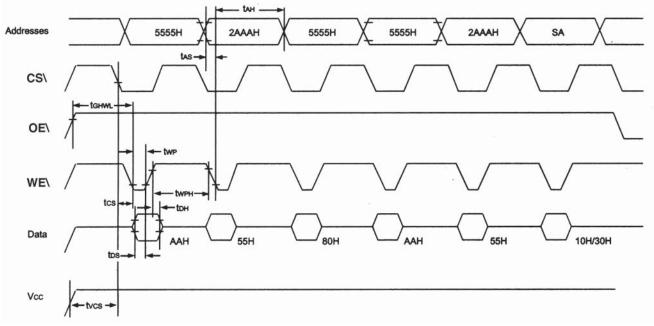

#### FIGURE 7: AC Waveforms Chip/Sector ERASE Operations

#### NOTES:

1. SA is the sector address for Sector ERASE.

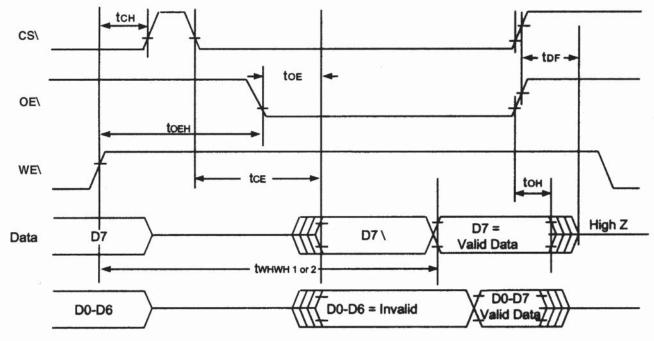

# FIGURE 8: AC Waveforms for DATA\ Polling During Embedded Algorithm Operations

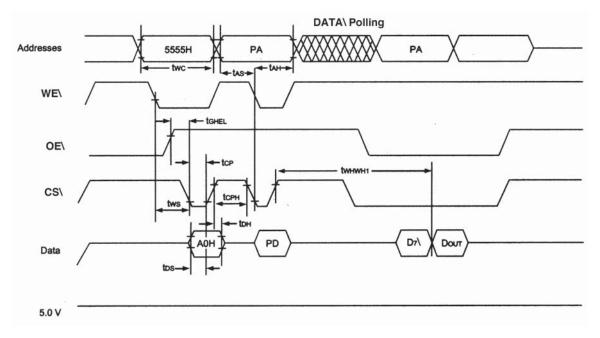

### FIGURE 9: Alternate CS\ Controlled Programming Operation Timings

#### NOTES:

- 1. PA is the address of the memory location to be programmed.

- 2. PD is the data to be programmed at byte address.

- 3.  $D_{7}$  is the output of the complement of the data written to each chip.

- 4. D<sub>OUT</sub> is the output of the data written to the device.

5. Figure indicates last two bus cycles of four bus cycle sequence.

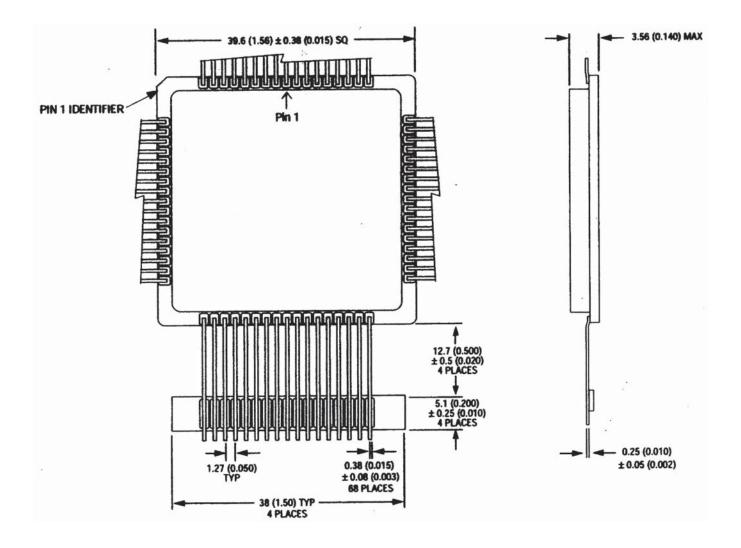

## **MECHANICAL DEFINITION** Micross Case #703 (Package Designator QW)

#### **NOTES:** 1. Dimensions are shown as millimeters(inches).

Micross Components reserves the right to change products or specifications without notice

# **MECHANICAL DEFINITIONS\***

(Package Designator QT)

Micross Components reserves the right to change products or specifications without notice.

# **ORDERING INFORMATION**

EXAMPLE: AS8F2M32QW-120/XT

| Device Number | Package<br>Type | Speed ns | Process |

|---------------|-----------------|----------|---------|

| AS8F2M32      | QW              | - 90     | /*      |

| AS8F2M32      | QW              | - 120    | /*      |

| AS8F2M32      | QW              | - 150    | /*      |

EXAMPLE: AS8F2M32QT-90/MIL

| Device Number | Package<br>Type | Speed ns | Process |

|---------------|-----------------|----------|---------|

| AS8F2M32      | QT              | - 90     | /*      |

| AS8F2M32      | QT              | - 120    | /*      |

| AS8F2M32      | QT              | - 150    | /*      |

### \*AVAILABLE PROCESSES

IT = Industrial Temperature Range XT = Extended Temperature Range MIL = MIL-STD-883C para 1.2.2 Processing **Temperature** -40°C to +85°C

-40°C to +83°C -55°C to +125°C -55°C to +125°C

Micross Components reserves the right to change products or specifications without notice.

NOTE: QW package is planned future offering

#### DOCUMENT TITLE

64Mb, 2M x 32 Flash Memory Module

#### **REVISION HISTORY**

| <u>Rev #</u> | <u>History</u>                     | Release Date | <u>Status</u> |

|--------------|------------------------------------|--------------|---------------|

| 2.5          | Updated Order Chart                | May 2009     | Release       |

| 2.6          | Updated Order Chart & Package Info | May 2009     | Release       |

| 2.7          | Updated Micross Informati          | January 2010 | Release       |