## 2.5V or 3.3V, 200 MHz, 9-Output Zero Delay Buffer

#### **Features**

Output frequency range: 25 MHz to 200 MHz

Input frequency range: 25 MHz to 200 MHz

2.5V or 3.3V operation

Split 2.5V/3.3V outputs

± 2.5% max Output duty cycle variation

Nine Clock outputs: Drive up to 18 clock lines

Two reference clock inputs: LVPECL or LVCMOS

150-ps max output-output skew

Phase-locked loop (PLL) bypass mode

'SpreadTrak'

Output enable/disable

Pin-compatible with MPC9351 and CY29351.

Industrial temperature range: –40°C to +85°C

32-pin 1.0mm TQFP & LQFP Package.

#### **Functional Description**

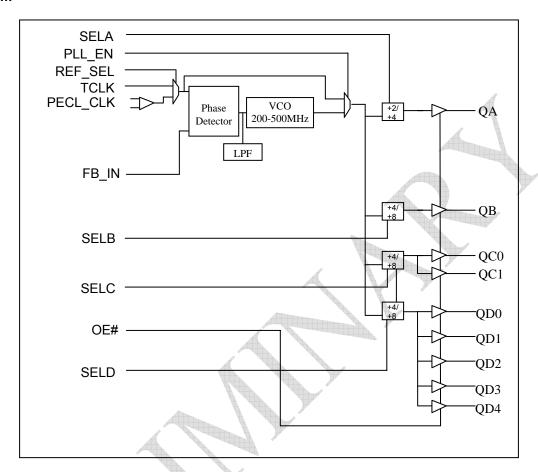

The ASM5I9351 is a low voltage high performance 200MHz PLL-based zero delay buffer designed for high speed clock distribution applications.

The ASM5I9351 features LVPECL and LVCMOS reference clock inputs and provides 9 outputs partitioned in 4 banks of 1, 1, 2, and 5 outputs. Bank A divides the VCO output by 2 or 4 while the other banks divide by 4 or 8 per SEL(A:D) settings, see Table.2. These dividers allow output to input ratios of 4:1, 2:1, 1:1, 1:2, and 1:4. Each LVCMOS compatible output can drive  $50\Omega$  series or parallel terminated transmission lines. For series terminated transmission lines, each output can drive one or two traces giving the device an effective fanout of 1:18.

The PLL is ensured stable given that the VCO is configured to run between 200 MHz to 500 MHz. This allows a wide range of output frequencies from 25 MHz to 200 MHz. For normal operation, the external feedback input, FB\_IN, is connected to one of the outputs. The internal VCO is running at multiples of the input reference clock set by the feedback divider, see the Table 1.

When PLL\_EN is LOW, PLL is bypassed and the reference clock directly feeds the output dividers. This mode is fully static and the minimum input clock frequency specification does not apply.

rev 0.2 Block Diagram

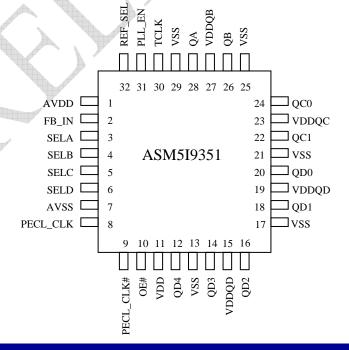

# Pin Configuration

## Pin Configuration<sup>1</sup>

| Pin#                  | Pin Name  | I/O      | Туре   | Description                                                                                                                                                           |

|-----------------------|-----------|----------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8                     | PECL_CLK  | I, PU    | Analog | LVPECL reference clock input.                                                                                                                                         |

| 9                     | PECL_CLK# | I, PU/PD | Analog | LVPECL reference clock input. Weak pull-up to VDD/2.                                                                                                                  |

| 30                    | TCLK      | I, PD    | LVCMOS | LVCMOS/LVTTL reference clock input                                                                                                                                    |

| 28                    | QA        | 0        | LVCMOS | Clock output bank A                                                                                                                                                   |

| 26                    | QB        | 0        | LVCMOS | Clock output bank B                                                                                                                                                   |

| 22, 24                | QC(1:0)   | 0        | LVCMOS | Clock output bank C                                                                                                                                                   |

| 12, 14, 16, 18,<br>20 | QD(4:0)   | 0        | LVCMOS | Clock output bank D                                                                                                                                                   |

| 2                     | FB_IN     | I, PD    | LVCMOS | <b>Feedback clock input</b> . Connect to an output for normal operation. This input should be at the same voltage rail as input reference clock. See <i>Table 1</i> . |

| 10                    | OE#       | I, PD    | LVCMOS | Output enable/disable input. See Table 2.                                                                                                                             |

| 31                    | PLL_EN    | I, PU    | LVCMOS | PLL enable/disable input. See Table 2.                                                                                                                                |

| 32                    | REF_SEL   | I, PD    | LVCMOS | Reference select input. See Table 2.                                                                                                                                  |

| 3, 4, 5, 6            | SEL(A:D)  | I, PD    | LVCMOS | Frequency select input, Bank (A:D). See Table 2.                                                                                                                      |

| 27                    | VDDQB     | Supply   | VDD    | 2.5V or 3.3V Power supply for bank B output clock <sup>2,3</sup>                                                                                                      |

| 23                    | VDDQC     | Supply   | VDD    | 2.5V or 3.3V Power supply for bank C output clocks <sup>2,3</sup>                                                                                                     |

| 15, 19                | VDDQD     | Supply   | VDD    | 2.5V or 3.3V Power supply for bank D output clocks <sup>2,3</sup>                                                                                                     |

| 1                     | AVDD      | Supply   | VDD _  | 2.5V or 3.3V Power supply for PLL <sup>2,3</sup>                                                                                                                      |

| 11                    | VDD       | Supply   | VDD    | 2.5V or 3.3V Power supply for core, inputs, and bank A output clock <sup>2,3</sup>                                                                                    |

| 7                     | AVSS      | Supply   | Ground | Analog ground                                                                                                                                                         |

| 13, 17, 21, 25,<br>29 | VSS       | Supply   | Ground | Common ground                                                                                                                                                         |

Note: 1 PU = Internal pull-up, PD = Internal pull-down.

2. A 0.1µF bypass capacitor should be placed as close as possible to each positive power pin (<0.2"). If these bypass capacitors are not close to the pins their high frequency filtering characteristics will be cancelled by the lead inductance of the traces.

3. AVDD and VDD pins must be connected to a power supply level that is at least equal or higher than that of VDDQB, VDDQC, and VDDQD output

power supply pins.

**Table 1: Frequency Table**

| Feedback Output<br>Divider | vco             | Input Frequency Range<br>(AVDD = 3.3V) | Input Frequency Range<br>(AVDD = 2.5V) |

|----------------------------|-----------------|----------------------------------------|----------------------------------------|

| ÷2                         | Input Clock * 2 | 100 MHz to 200 MHz                     | 100 MHz to 190MHz                      |

| ÷4                         | Input Clock * 4 | 50 MHz to 125 MHz                      | 50 MHz to 95MHz                        |

| ÷8                         | Input Clock * 8 | 25 MHz to 62.5 MHz                     | 25 MHz to 47.5MHz                      |

#### **Table 2: Function Table**

| Control | Default | 0                                                                          | 1                                                                    |

|---------|---------|----------------------------------------------------------------------------|----------------------------------------------------------------------|

| REF_SEL | 0       | PCLK                                                                       | TCLK                                                                 |

| PLL_EN  | 1       | Bypass mode, PLL disabled. The input clock connects to the output dividers | PLL enabled. The VCO output connects to the output dividers          |

| OE#     | 0       | Outputs enabled                                                            | Outputs disabled (three-state), VCO running at its minimum frequency |

| SELA    | 0       | ÷2 (Bank A)                                                                | ÷ 4 (Bank A)                                                         |

| SELB    | 0       | ÷4 (Bank B)                                                                | ÷ 8 (Bank B)                                                         |

| SELC    | 0       | ÷4 (Bank C <b>)</b>                                                        | ÷ 8 (Bank C)                                                         |

| SELD    | 0       | ÷4 (Bank D)                                                                | ÷ 8 (Bank D)                                                         |

## **Absolute Maximum Ratings**

| Parameter | Description                       | Condition                  | Min   | Max      | Unit  |

|-----------|-----------------------------------|----------------------------|-------|----------|-------|

| VDD       | DC Supply Voltage                 |                            | -0.3  | 5.5      | V     |

| VDD       | DC Operating Voltage              | Functional                 | 2.375 | 3.465    | V     |

| VIN       | DC Input Voltage                  | Relative to Vss            | -0.3  | VDD+ 0.3 | V     |

| Vout      | DC Output Voltage                 | Relative to Vss            | -0.3  | VDD+ 0.3 | V     |

| VTT       | Output termination Voltage        | , ,                        |       | VDD ÷2   | V     |

| LU        | Latch Up Immunity                 | Functional                 | 200   |          | mA    |

| Rps       | Power Supply Ripple               | Ripple Frequency < 100 kHz |       | 150      | mVp-p |

| Ts        | Temperature, Storage              | Non-functional             | -65   | +150     | °C    |

| TA        | Temperature, Operating Ambient    | Functional                 | -40   | +85      | °C    |

| TJ        | Temperature, Junction             | Functional                 |       | +150     | °C    |

| ØJC /     | Dissipation, Junction to Case     | Functional                 | 42    |          | °C/W  |

| ØJA       | Dissipation, Junction to Ambient  | Functional                 |       | 105      | °C/W  |

| ESDH      | ESD Protection (Human Body Model) |                            | 2000  |          | Volts |

| FÍT       | Failure in Time                   | Manufacturing test         |       | 10       | ppm   |

Note: These are stress ratings only and functional operation is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

#### DC Electrical Specifications (V<sub>DD</sub> = 2.5V ± 5%, T<sub>A</sub> = -40°C to +85°C)

| Parameter | Description                       | Condition                | Min | Тур | Max      | Unit |

|-----------|-----------------------------------|--------------------------|-----|-----|----------|------|

| VIL       | Input Voltage, Low                | LVCMOS                   | -   | -   | 0.7      | V    |

| VIH       | Input Voltage, High               | LVCMOS                   | 1.7 | -   | VDD+0.3  | V    |

| VPP       | Peak-Peak Input Voltage           | LVPECL                   | 250 | -   | 1000     | mV   |

| VCMR      | Common Mode Range <sup>1</sup>    | LVPECL                   | 1.0 | -   | VDD- 0.6 | V    |

| VoL       | Output Voltage, Low <sup>2</sup>  | IoL= 15mA                | -   | -   | 0.6      | V    |

| Voн       | Output Voltage, High <sup>2</sup> | IOH= -15mA               | 1.8 | - 4 | -        | V    |

| IIL.      | Input Current, Low <sup>3</sup>   | VIL= VSS                 | -   | -   | -100     | μA   |

| IIH       | Input Current, High <sup>3</sup>  | VIL= VDD                 | -   |     | 100      | μA   |

| IDDA      | PLL Supply Current                | AVDD only                | - 4 | 5   | 10       | mA   |

| IDDQ      | Quiescent Supply Current          | All VDD pins except AVDD | -   |     | 7        | mA   |

| ldd       | Dynamia Supply Current            | Outputs loaded @ 100 MHz | -   | 180 | -        | mA   |

| טטו       | Dynamic Supply Current            | Outputs loaded @ 200 MHz |     | 210 | <u>-</u> | IIIA |

| CIN       | Input Pin Capacitance             | A                        | 1-> | 4   | -        | pF   |

| Zout      | Output Impedance                  |                          | 14  | 18  | 22       | Ω    |

Note: 1 VCMR (DC) is the crossing point of the differential input signal. Normal operation is obtained when the crossing point is within the V<sub>CMR</sub> range and the input swing is within the V<sub>PP</sub> (DC) specification.

#### DC Electrical Specifications ( $V_{DD} = 3.3V \pm 5\%$ , $T_A = -40$ °C to +85°C)

| Parameter | Description                       | Condition                | Min | Тур | Max      | Unit |  |

|-----------|-----------------------------------|--------------------------|-----|-----|----------|------|--|

| VIL       | Input Voltage, Low                | LVCMOS                   | -   | -   | 0.8      | V    |  |

| VIH       | Input Voltage, High               | LVCMOS                   | 2.0 | -   | VDD+0.3  | V    |  |

| VPP       | Peak-Peak Input Voltage           | LVPECL                   | 250 | -   | 1000     | mV   |  |

| VCMR      | Common Mode Range <sup>1</sup>    | LVPECL                   | 1.0 | -   | VDD- 0.6 | V    |  |

| Vol       | Output Voltage, Low <sup>2</sup>  | IoL= 24 mA               | -   | -   | 0.55     | V    |  |

| VOL       | Output voltage, Low               | IoL= 12 mA               | -   | -   | 0.30     | V    |  |

| Vон       | Output Voltage, High <sup>2</sup> | Iон= –24 mA              | 2.4 | -   | -        | V    |  |

| lı∟       | Input Current, Low <sup>3</sup>   | VIL= VSS                 | -   | -   | -100     | μΑ   |  |

| IIН       | Input Current, High <sup>3</sup>  | VIL= VDD                 | -   | -   | 100      | μΑ   |  |

| IDDA      | PLL Supply Current                | AVDD only                | -   | 5   | 10       | mA   |  |

| IDDQ      | Quiescent Supply Current          | All VDD pins except AVDD | -   | -   | 7        | mA   |  |

| IDD       | Dynamic Supply Current            | Outputs loaded @ 100 MHz | -   | 270 | -        | mA   |  |

| IDD       | Dynamic Supply Current            | Outputs loaded @ 200 MHz | -   | 300 | -        | ША   |  |

| CIN       | Input Pin Capacitance             |                          | -   | 4   | -        | pF   |  |

| Zout      | Output Impedance                  |                          | 12  | 15  | 18       | Ω    |  |

Note: 1 VCMR (DC) is the crossing point of the differential input signal. Normal operation is obtained when the crossing point is within the V<sub>CMR</sub> range and the input swing is within the V<sub>PP</sub> (DC) specification.

<sup>2.</sup>Driving one 50Ω parallel terminated transmission line to a termination voltage of V<sub>TT</sub>. Alternatively, each output drives up to two 50Ω series terminated transmission lines.

<sup>3.</sup>Inputs have pull-up or pull-down resistors that affect the input current.

<sup>2.</sup>Driving one 50Ω parallel terminated transmission line to a termination voltage of V<sub>TT</sub>. Alternatively, each output drives up to two 50Ω series terminated transmission lines.

<sup>3.</sup>Inputs have pull-up or pull-down resistors that affect the input current.

rev 0.2 AC Electrical Specifications  $(V_{DD} = 2.5V \pm 5\%, T_A = -40^{\circ}C \text{ to } +85^{\circ}C)^{-1}$

| Parameter                       | Description                      | Condition                  | Min  | Тур  | Max      | Unit  |  |

|---------------------------------|----------------------------------|----------------------------|------|------|----------|-------|--|

| f <sub>VCO</sub>                | VCO Frequency                    |                            | 200  | -    | 380      | MHz   |  |

|                                 |                                  | ÷2 Feedback                | 100  | -    | 190      | MHz   |  |

| f <sub>in</sub>                 | Input Frequency                  | ÷4 Feedback                | 50   | -    | 95       |       |  |

| lin                             | Imput Frequency                  | ÷8 Feedback                | 25   | -    | 47.5     | IVITZ |  |

|                                 |                                  | Bypass mode (PLL_EN = 0)   | 0    | -4   | 200      |       |  |

| f <sub>refDC</sub>              | Input Duty Cycle                 |                            | 25   | 4    | 75       | %     |  |

| t <b>V</b> ppcom                | Peak-Peak Input Voltage          | LVPECL                     | 500  | -    | 1000     | mV    |  |

| V <sub>CMR</sub>                | Common Mode Range <sup>2</sup>   | LVPECL                     | 1.2  | 4    | VDD- 0.6 | V     |  |

| t <sub>r</sub> , t <sub>f</sub> | TCLK Input Rise/FallTime         | 0.7V to 1.7V               |      | 4    | 1.0      | nS    |  |

|                                 |                                  | ÷2 Output                  | 100  | -    | 190      |       |  |

| $f_{MAX}$                       | Maximum Output Frequency         | ÷4 Output                  | 50   |      | 95       | MHz   |  |

|                                 |                                  | ÷8 Output                  | 25   | -    | 47.5     |       |  |

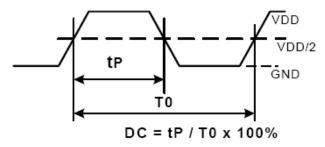

| DC                              | Output Duty Cycle                | f <sub>MAX</sub> < 100 MHz | 47.5 | -    | 52.5     | %     |  |

|                                 | Output Duty Cycle                | f <sub>MAX</sub> > 100 MHz | 45   | -    | 55       | /0    |  |

| t <sub>r</sub> , t <sub>f</sub> | Output Rise/Fall times           | 0.6V to 1.8V               | 0.1  | -    | 1.0      | nS    |  |

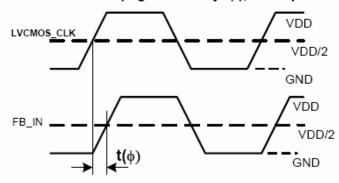

| <b>+</b>                        | Propagation Delay                | TCLK to FB_IN              | -100 | -    | 100      | pS    |  |

| $t_{(\phi)}$                    | (static phase offset)            | PCLK to FB_IN              | -100 | -    | 100      | ρS    |  |

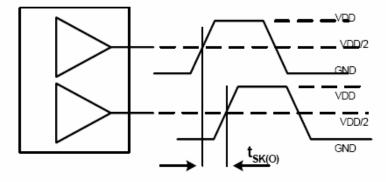

| t <sub>sk(O)</sub>              | Output-to-Output Skew            |                            | -    | -    | 150      | pS    |  |

| t <sub>PLZ, HZ</sub>            | Output Disable Time              |                            | -    | -    | 10       | nS    |  |

| t <sub>PZL, ZH</sub>            | Output Enable Time               |                            | -    | -    | 10       | nS    |  |

|                                 |                                  | ÷2 Feedback                | -    | 2.2  | -        |       |  |

| BW                              | PLL Closed Loop Bandwidth (–3dB) | ÷4 Feedback                | -    | 0.85 | -        | MHz   |  |

|                                 | ( 502)                           | ÷8 Feedback                | -    | 0.6  | -        |       |  |

| 4                               | Cycle to Cycle litter            | Same frequency             | -    | -    | 150      |       |  |

| $t_{\text{JIT(CC)}}$            | Cycle-to-Cycle Jitter            | Multiple frequencies       | -    | -    | 250      | pS    |  |

| 4                               | Daried litter                    | Same frequency             | -    | -    | 100      | 20    |  |

| t <sub>JIT(PER)</sub>           | Period Jitter                    | Multiple frequencies       | -    | -    | 175      | pS    |  |

| $t_{JIT(\phi)}$                 | I/O Phase Jitter                 |                            | -    | 175  | -        | pS    |  |

| t <sub>LOCK</sub>               | Maximum PLL Lock Time            |                            | -    | -    | 1        | mS    |  |

Note: 1 AC characteristics apply for parallel output termination of 50Ω to VTT. Parameters are guaranteed by characterization and are not 100% tested.

2. VCMR (AC) is the crosspoint of the differential input signal. Normal AC operation is obtained when the crosspoint is within the VCMR range and the input swing lies within the VPP (AC) specification. Violation of VCMR or VPP impacts static phase offset t(φ).

rev 0.2 AC Electrical Specifications  $(V_{DD}$  = 3.3V ± 5%,  $T_A$  = -40°C to +85°C) $^1$

| Parameter                       | Description                      | Condition                   | Min  | Тур  | Max      | Unit |  |

|---------------------------------|----------------------------------|-----------------------------|------|------|----------|------|--|

| f <sub>VCO</sub>                | VCO Frequency                    |                             | 200  | -    | 500      | MHz  |  |

|                                 |                                  | ÷2 Feedback                 | 100  | -    | 200      |      |  |

| f <sub>in</sub>                 |                                  | ÷4 Feedback                 | 50   | -    | 125      |      |  |

|                                 | Input Frequency                  | ÷8 Feedback                 | 25   | -    | 62.5     | MHz  |  |

|                                 |                                  | Bypass mode (PLL_EN = 0)    | 0    | - 4  | 200      |      |  |

| f <sub>refDC</sub>              | Input Duty Cycle                 |                             | 25   | -    | 75       | %    |  |

| V <sub>PP</sub>                 | Peak-Peak Input Voltage          | LVPECL                      | 500  |      | 1000     | mV   |  |

| $V_{CMR}$                       | Common Mode Range <sup>2</sup>   | LVPECL                      | 1.2  | -    | VDD- 0.9 | V    |  |

| t <sub>r</sub> , t <sub>f</sub> | TCLK Input Rise/FallTime         | 0.8V to 2.0V                | -    |      | 1.0      | nS   |  |

|                                 |                                  | ÷2 Output                   | 100  | -    | 200      |      |  |

| $f_{\text{MAX}}$                | Maximum Output Frequency         | ÷4 Output                   | 50   | - )  | 125      | MHz  |  |

|                                 |                                  | ÷8 Output                   | 25   |      | 62.5     |      |  |

| DC                              | Output Duty Cycle                | fmax < 100 MHz              | 47.5 | -    | 52.5     | %    |  |

|                                 | Output Duty Cycle                | fmax > 100 MHz              | 45   | -    | 55       | 70   |  |

| t <sub>r</sub> , t <sub>f</sub> | Output Rise/Fall times           | 0.8V to 2.4V                | 0.1  | -    | 1.0      | nS   |  |

| 4                               | Propagation Delay                | TCLK to FB_IN, same VDD     | -100 | -    | 100      | 20   |  |

| $t_{(\phi)}$                    | (static phase offset)            | PCLK to FB_IN, same VDD     | -100 | -    | 100      | pS   |  |

| t <sub>sk(O)</sub>              | Output-to-Output Skew            | Banks at same voltage       | -    | -    | 150      | pS   |  |

| t <sub>sk(B)</sub>              | Bank-to-Bank Skew                | Banks at different voltages | -    | -    | 350      | pS   |  |

| t <sub>PLZ, HZ</sub>            | Output Disable Time              |                             | -    | -    | 10       | nS   |  |

| t <sub>PZL, ZH</sub>            | Output Enable Time               |                             | -    | -    | 10       | nS   |  |

|                                 | But Object to Book 1986          | ÷2 Feedback                 | -    | 2.2  | ı        | MHz  |  |

| BW                              | PLL Closed Loop Bandwidth (–3dB) | ÷4 Feedback                 | -    | 0.85 | -        |      |  |

|                                 | ( 0.0.2)                         | ÷8 Feedback                 | -    | 0.6  | -        |      |  |

| t.,_,,                          | Cycle-to-Cycle Jitter            | Same frequency              | -    | -    | 150      | pS   |  |

| t <sub>JIT(CC)</sub>            | Gycle-to-Gycle Sitter            | Multiple frequencies        | -    | -    | 250      | рЗ   |  |

| t <sub>JIT(PER)</sub>           | Period Jitter                    | Same frequency              | -    | -    | 100      | pS   |  |

| UII(PER)                        | I eriod sitter                   | Multiple frequencies        | -    | -    | 150      | ρυ   |  |

| t <sub>JIT(φ)</sub>             | I/O Phase Jitter                 | I/O same VDD                | -    | 175  | -        | pS   |  |

| t <sub>LOCK</sub>               | Maximum PLL Lock Time            |                             | -    | -    | 1        | mS   |  |

Note: 1 AC characteristics apply for parallel output termination of 50Ω to VTT. Parameters are guaranteed by characterization and are not 100% tested.

2. VCMR (AC) is the crosspoint of the differential input signal. Normal AC operation is obtained when the crosspoint is within the VCMR range and the input swing lies within the VPP (AC) specification. Violation of VCMR or VPP impacts static phase offset t(φ).

July 2005 ASM5I9351

rev 0.2

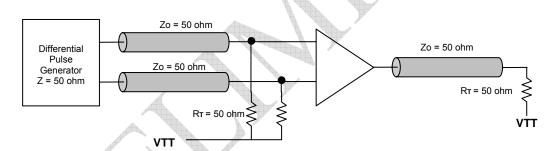

Pulse Generator Z = 50 ohm  $Z_0 = 50 \text{ ohm}$   $Z_0 = 50 \text{ ohm}$

Figure 1. LVCMOS\_CLK AC Test Reference for VDD = 3.3V / 2.5V

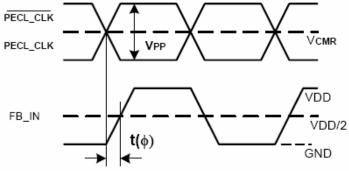

Figure 2. PECL\_CLK AC Test Reference for VDD = 3.3V / 2.5V

Figure 3. LVPECL Propagation Delay t(f), static phase offset

Figure 4. LVCMOS Propagation Delay t(φ), static phase offset

Figure 5. Output Duty Cycle (DC)

Figure 6. Output-to-Output Skew,  $t_{sk(O)}$

rev 0.2

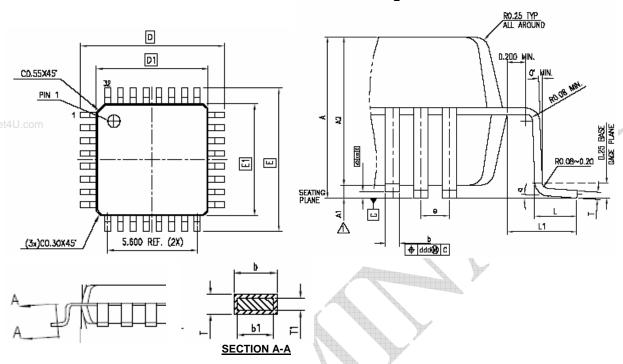

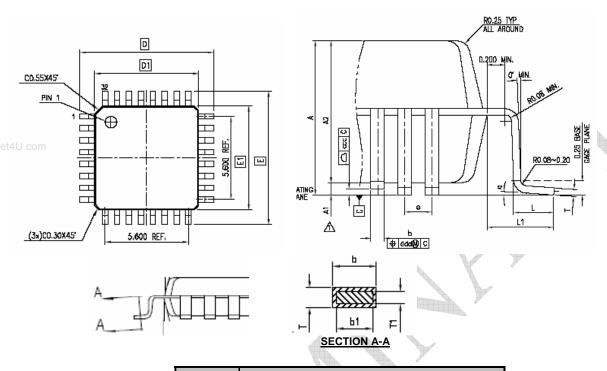

## **Package Diagram**

## 32-lead TQFP Package

|        | Dimensions |             |        |       |  |  |

|--------|------------|-------------|--------|-------|--|--|

| Symbol | Inch       | es          | Millim | eters |  |  |

|        | Min        | Max         | Min    | Max   |  |  |

| Α      | \          | 0.0472      |        | 1.2   |  |  |

| A1     | 0.0020     | 0.0059      | 0.05   | 0.15  |  |  |

| A2     | 0.0374     | 0.0413      | 0.95   | 1.05  |  |  |

| D      | 0.3465     | 0.3622      | 8.8    | 9.2   |  |  |

| D1     | 0.2717     | 0.2795      | 6.9    | 7.1   |  |  |

| E      | 0.3465     | 0.3622      | 8.8    | 9.2   |  |  |

| E1     | 0.2717     | 0.2795      | 6.9    | 7.1   |  |  |

| L      | 0.0177     | 0.0295      | 0.45   | 0.75  |  |  |

| L1     | 0.03937    | 0.03937 REF |        | REF   |  |  |

| Т      | 0.0035     | 0.0079      | 0.09   | 0.2   |  |  |

| T1     | 0.0038     | 0.0062      | 0.097  | 0.157 |  |  |

| b      | 0.0118     | 0.0177      | 0.30   | 0.45  |  |  |

| b1     | 0.0118     | 0.0157      | 0.30   | 0.40  |  |  |

| R0     | 0.0031     | 0.0079      | 0.08   | 0.2   |  |  |

| а      | 0°         | 7°          | 0°     | 7°    |  |  |

| е      | 0.031 E    | BASE        | 0.8 B  | ASE   |  |  |

rev 0.2

## 32-lead LQFP Package

|        | Dimensions     |        |             |       |  |

|--------|----------------|--------|-------------|-------|--|

| Symbol | Inch           | es     | Millimeters |       |  |

|        | Min            | Max    | Min         | Max   |  |

| Α      | ··· A          | 0.0630 |             | 1.6   |  |

| A1     | 0.0020         | 0.0059 | 0.05        | 0.15  |  |

| A2     | 0.0531         | 0.0571 | 1.35        | 1.45  |  |

| D      | 0.3465         | 0.3622 | 8.8         | 9.2   |  |

| D1     | 0.2717         | 0.2795 | 6.9         | 7.1   |  |

| E      | 0.3465         | 0.3622 | 8.8         | 9.2   |  |

| E1     | 0.2717         | 0.2795 | 6.9         | 7.1   |  |

| L      | 0.0177         | 0.0295 | 0.45        | 0.75  |  |

| L1     | 0.03937        | 7 REF  | 1.00        | REF   |  |

| Т      | 0.0035         | 0.0079 | 0.09        | 0.2   |  |

| T1     | 0.0038         | 0.0062 | 0.097       | 0.157 |  |

| b      | 0.0118         | 0.0177 | 0.30        | 0.45  |  |

| b1     | 0.0118         | 0.0157 | 0.30        | 0.40  |  |

| R0     | 0.0031         | 0.0079 | 0.08        | 0.20  |  |

| е      | 0.031 BASE 0.8 |        | 0.8 B       | ASE   |  |

| а      | 0°             | 7°     | 0°          | 7°    |  |

rev 0.2

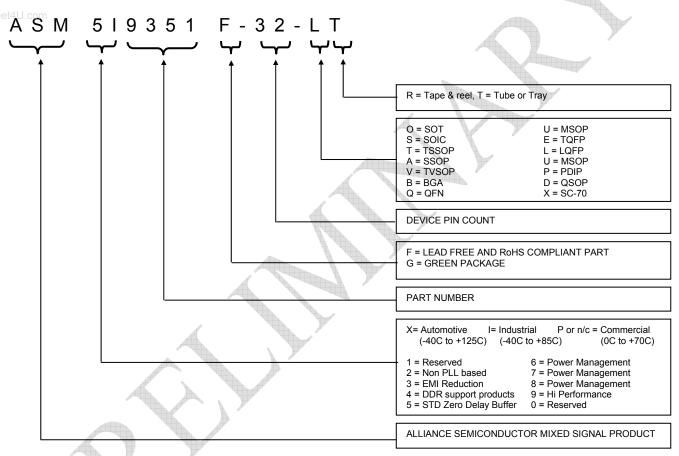

Ordering Information

| Part Number      | Marking    | Package Type                      | Temperature |

|------------------|------------|-----------------------------------|-------------|

| ASM5I9351-32-ET  | ASM5I9351  | 32-pin TQFP                       | Industrial  |

| ASM5I9351-32-LT  | ASM5I9351  | 32-pin LQFP –Tape and Reel        | Industrial  |

| ASM5I9351G-32-ET | ASM5I9351G | 32-pin TQFP, Green                | Industrial  |

| ASM5I9351G-32-LT | ASM5I9351G | 32-pin LQFP –Tape and Reel, Green | Industrial  |

## **Device Ordering Information**

Licensed under US patent #5,488,627, #6,646,463 and #5,631,920.

ww.DataSheet4U.com

Alliance Semiconductor Corporation 2575, Augustine Drive, Santa Clara, CA 95054 Tel# 408-855-4900 Fax: 408-855-4999 www.alsc.com Copyright © Alliance Semiconductor All Rights Reserved Part Number: ASM5I9351 Document Version: 0.2

Note: This product utilizes US Patent # 6,646,463 Impedance Emulator Patent issued to Alliance Semiconductor, dated 11-11-2003

© Copyright 2003 Alliance Semiconductor Corporation. All rights reserved. Our three-point logo, our name and Intelliwatt are trademarks or registered trademarks of Alliance. All other brand and product names may be the trademarks of their respective companies. Alliance reserves the right to make changes to this document and its products at any time without notice. Alliance assumes no responsibility for any errors that may appear in this document. The data contained herein represents Alliance's best data and/or estimates at the time of issuance. Alliance reserves the right to change or correct this data at any time, without notice. If the product described herein is under development, significant changes to these specifications are possible. The information in this product data sheet is intended to be general descriptive information for potential customers and users, and is not intended to operate as, or provide, any guarantee or warrantee to any user or customer. Alliance does not assume any responsibility or liability arising out of the application or use of any product described herein, and disclaims any express or implied warranties related to the sale and/or use of Alliance products including liability or warranties related to fitness for a particular purpose, merchantability, or infringement of any intellectual property rights, except as express agreed to in Alliance's Terms and Conditions of Sale (which are available from Alliance). All sales of Alliance products are made exclusively according to Alliance's Terms and Conditions of Sale. The purchase of products from Alliance does not convey a license under any patent rights, copyrights; mask works rights, trademarks, or any other intellectual property rights of Alliance or third parties. Alliance does not authorize its products for use as critical components in life-supporting systems where a malfunction or failure may reasonably be expected to result in significant injury to the user, and the inclusion of Alliance products in such life-supporting systems implies that the manufacturer assumes all risk of such use and agrees to indemnify Alliance against all claims arising from such use.