#### **Features**

- Complies with Intel Low-Pin Count (LPC) Interface Specification Revision 1.1

- Supports both Firmware Hub (FWH) and LPC Memory Read and Write Cycles

- Auto-detection of FWH and LPC Memory Cycles

- Can Be Used as FWH for Intel 8xx, E7xxx, and E8xxx Series Chipsets

- Can Be Used as LPC Flash for Non-Intel Chipsets

- Flexible, Optimized Sectoring for BIOS Applications

- 32-Kbyte Top Boot Sector, Two 8-Kbyte Sectors, One 16-Kbyte Sector, Seven 64-Kbyte Sectors

- Or Memory Array Can Be Divided Into Eight Uniform 64-Kbyte Sectors for Erasing

- Two Configurable Interfaces

- FWH/LPC Interface for In-System Operation

- Address/Address Multiplexed (A/A Mux) Interface for Programming during

Manufacturing

- FWH/LPC Interface

- Operates with the 33 MHz PCI Bus Clock

- 5-signal Communication Interface Supporting Byte Reads and Writes

- Two Hardware Write Protect Pins: TBL for Top Boot Sector and WP for All Other Sectors

- Five General-purpose Input (GPI) Pins for System Design Flexibility

- Identification (ID) Pins for Multiple Device Selection

- Sector Locking Registers for Individual Sector Read and Write Protection

- A/A Mux Interface

- 11-pin Multiplexed Address and 8-pin Data Interface

- Facilitates Fast In-System or Out-of-System Programming

- Single Voltage Operation

- 3.0V to 3.6V Supply Voltage for Read and Write Operations

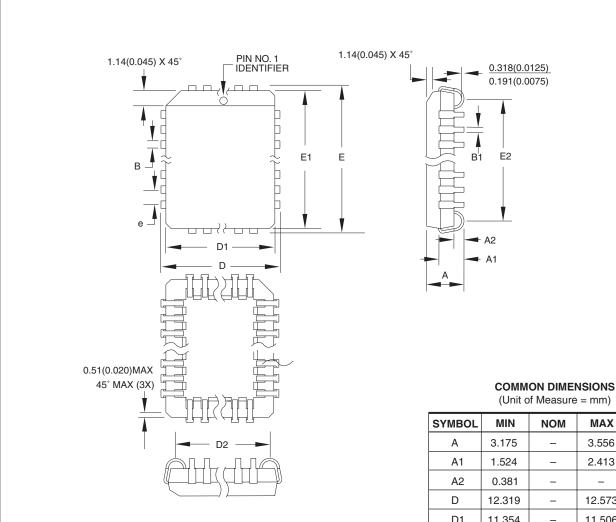

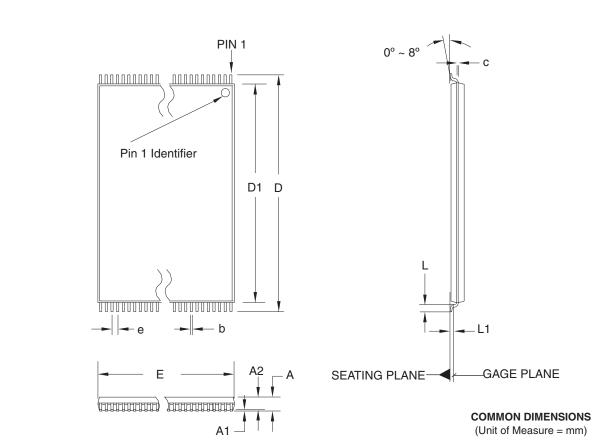

- Industry-Standard Package Options

- 32-lead PLCC

- 40-lead TSOP

- Green (Pb/Halide-free) Packaging Option

# 1. Description

The AT49LH004 is a Flash memory device designed for use in PC and notebook BIOS applications. The device complies with version 1.1 of Intel's LPC Interface Specification, providing support for both FWH and LPC memory read and write cycles. The device can also automatically detect the memory cycle type to allow the AT49LH004 to be used as a FWH with Intel chipsets or as an LPC Flash with non-Intel chipsets.

The sectoring of the AT49LH004's memory array has been optimized to meet the needs of today's BIOS applications. By optimizing the size of the sectors, the BIOS code memory space can be used more efficiently. Because certain BIOS code modules must reside in their own sectors by themselves, the wasted and unused memory space that occurred with previous generation BIOS Flash memory devices can be greatly reduced. This increased memory space efficiency allows additional BIOS routines to be developed and added while still maintaining the same overall device density.

4-megabit

Firmware Hub

and Low-Pin

Count Flash

Memory

AT49LH004

3383D-FLASH-6/05

The memory array of the AT49LH004 can be sectored in two ways simply by using two different erase commands. Using one erase command allows the device to contain a total of 11 sectors comprised of a 32-Kbyte boot sector, two 8-Kbyte sectors, a 16-Kbyte sector, and seven 64-Kbyte sectors. The 32-Kbyte boot sector is located at the top (uppermost) of the device's memory address space. Alternatively, by using a different erase command, the memory array can be arranged into eight even erase sectors of 64-Kbyte each.

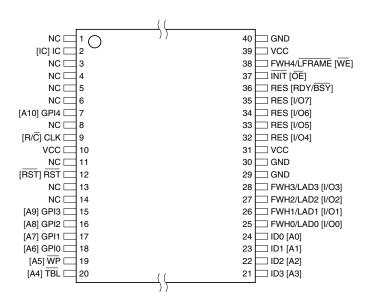

The AT49LH004 supports two hardware interfaces: The FWH/LPC interface for In-System operations and the A/A Mux interface for programming during manufacturing. The Interface Configuration (IC) pin of the device provides the control between these two interfaces. An internal Command User Interface (CUI) serves as the control center between the device interfaces and the internal operation of the nonvolatile memory. A valid command sequence written to the CUI initiates device automation.

Specifically designed for use in 3-volt systems, the AT49LH004 supports read, program, and erase operations with a supply voltage range of 3.0V to 3.6V. No separate voltage is required for programming and erasing.

The AT49LH004 utilizes fixed program and erase times, independent of the number of program and erase cycles that have occurred. Therefore, the system does not need to be calibrated or correlated to the cumulative number of program and erase cycles.

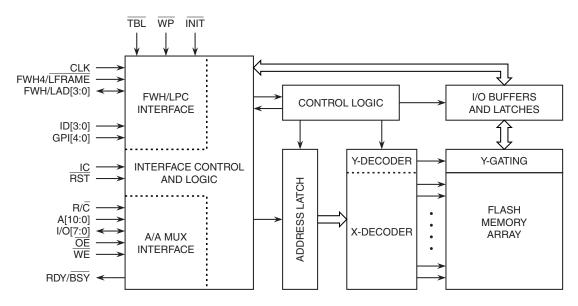

# 2. Pin Configurations

### 2.1 32-lead PLCC

#### GP14 [A10] 32 [A7] GPI1 5 [A6] GPI0 [ ☐ GND 28 [A5] WP □ 7 27 □ NC 26 □ NC [A3] ID3 🗆 9 25 □ VCC [A2] ID2 🗆 10 ☐ INIT [OE] [A1] ID1 🗆 11 23 FWH4/LFRAME [WE] [A0] ID0 🗆 12 22 RES [RDY/BSY] 21 S [I/O0] FWH0/LAD0 [ RES [I/O7] 8 6 I/O1] FWH1/LAD1 П П П П GND 1/O2] FWH2/LAD2 FWH3/LAD3 RES RES RES [/04] [(03

#### 2.2 40-lad TSOP

Note: [ ] Designates A/A Mux Interface.

# 3. Block Diagram

# 4. Device Memory Map

| Sector | Туре        | Size (Bytes) | Address Range     |

|--------|-------------|--------------|-------------------|

| 10     | Sub-sector  | 32K          | 078000H - 07FFFFH |

| 9      | Sub-sector  | 8K           | 076000H - 077FFFH |

| 8      | Sub-sector  | 8K           | 074000H - 075FFFH |

| 7      | Sub-sector  | 16K          | 070000H - 073FFFH |

| 6      | Main Sector | 64K          | 060000H - 06FFFFH |

| 5      | Main Sector | 64K          | 050000H - 05FFFFH |

| 4      | Main Sector | 64K          | 040000H - 04FFFFH |

| 3      | Main Sector | 64K          | 030000H - 03FFFFH |

| 2      | Main Sector | 64K          | 020000H - 02FFFFH |

| 1      | Main Sector | 64K          | 010000H - 01FFFFH |

| 0      | Main Sector | 64K          | 000000H - 00FFFFH |

# 5. Pin Description

Table 5-1 provides a description of each of the device pins. Most of the pins have dual functionality in that they are used for both the FWH/LPC interface as well as the A/A Mux interface.

Table 5-1.Signal Descriptions

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Interf  |         |                  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|------------------|--|

| Symbol           | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | FWH/LPC | A/A Mux | Туре             |  |

| IC               | <b>INTERFACE COMMUNICATION</b> : The IC pin determines which interface is operational. If the IC pin is held high, then the A/A Mux interface is enabled, and if the IC pin is held low, then the FWH/LPC interface is enabled. The IC pin must be set at power-up or before returning from a reset condition and cannot be changed during device operation. The IC pin is internally pulled-down with a resistor valued between 20 k $\Omega$ and 100 k $\Omega$ , so connection of this pin is not necessary if the FWH/LPC interface will always be used in the system. If the IC pin is driven high to enable the A/A Mux interface, then the pin will exhibit some leakage current.                                                                                               | X       | X       | Input            |  |

| CLK              | <b>FWH/LPC CLOCK</b> : This pin is used to provide a clock to the device. This pin is usually connected to the 33 MHz PCI clock and adheres to the PCI specification. This pin is used as the R/C pin in the A/A Mux interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Х       |         | Input            |  |

| FWH4/<br>LFRAME  | <b>FWH INPUT/LPC FRAME</b> : This pin is used to indicate the start of a FWH or LPC data transfer operation. The pin is also used to abort a FWH or LPC cycle in progress.  This pin is used as the WE pin in the A/A Mux interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | х       |         | Input            |  |

| FWH/<br>LAD[3:0] | <b>FWH/LPC ADDRESS AND DATA</b> : These pins are used for FWH/LPC bus information such as addresses, data, and command inputs/outputs.  These pins are used as the I/O[3:0] pins in the A/A Mux interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Х       |         | Input/<br>Output |  |

| RST              | INTERFACE RESET: The RST pin is used for both FWH/LPC and A/A Mux interfaces. When the RST pin is driven low, write operations are inhibited, internal automation is reset, and the FWH/LAD[3:0] pins (when using the FWH/LPC interface) are put into a high-impedance state. When the device exits the reset state, it will default to the read array mode.                                                                                                                                                                                                                                                                                                                                                                                                                           | X       | X       | Input            |  |

| ĪNIT             | PROCESSOR RESET/INITIALIZE: The INIT pin is used as a second reset pin for In-System operation and functions identically to the RST pin. The INIT pin is designed to be connected to the chipset's INIT signal.  The maximum voltage to be applied to the INIT pin depends on the processor's or chipset's specifications. Systems must take care to not violate processor or chipset specifications regarding the INIT pin voltage.  This pin is used as the OE pin in the A/A Mux interface.                                                                                                                                                                                                                                                                                         | Х       |         | Input            |  |

| TBL              | TOP BOOT SECTOR LOCK: When the TBL pin is held low, program and erase operations cannot be performed to the top 64-Kbyte region (in FWH mode) or the top 32-Kbyte boot sector (in LPC mode) regardless of the state of the Sector Locking Registers. In addition, the TBL pin will protect the uppermost 64-Kbyte region against erasures when using the LPC mode and the Uniform Sector Erase command. Please refer to the Sector Protection section for more details. If the TBL pin is held high, then hardware write protection for the top boot sector will be disabled. However, register-based sector protection will still apply. The state of the TBL pin does not affect the state of the Sector Locking Registers. This pin is used as the A4 pin in the A/A Mux interface. | X       |         | Input            |  |

Table 5-1.

Signal Descriptions (Continued)

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Inter   | ace     |                  |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|------------------|

| Symbol   | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | FWH/LPC | A/A Mux | Type             |

| WP       | WRITE PROTECT: The WP pin is used to protect all remaining sectors that are not being used for the top boot region. See "Sector Protection" on page 17. for more details.  If the WP pin is high, then hardware write protection for all of the sectors except the top boot sector will be disabled. Register-based sector protection, however, will still apply. The state of the WP pin does not affect the state of the Sector Locking Registers.  This pin is used as the A5 pin in the A/A Mux interface.                                                                                                                                                                                                                                                                          | х       |         | Input            |

| ID[3:0]  | <b>IDENTIFICATION INPUTS</b> : These four pins are part of the mechanism that allows multiple devices to be attached to the same bus. The strapping of these pins is used to assign an ID to each device. The boot device must have ID[3:0] = 0000, and it is recommended that all subsequent devices should use sequential up-count strapping (e.g., 0001, 0010, 0011, etc.). The ID[3:0] pins are internally pulled-down with resistors valued between 20 kΩ and 100 kΩ when using the FWH/LPC interface, so connection of these pins is not necessary if only a single device will be used in a system. Any pins intended to be low may be left floating. Any ID pin driven high will exhibit some leakage current. These pins are used as the A[3:0] pins in the A/A Mux interface. | х       |         | Input            |

| GPI[4:0] | GENERAL-PURPOSE INPUTS: The individual GPI pins can be used for additional board flexibility. The state of the GPI pins can be read, using the FWH/LPC interface, through the GPI register. The GPI pins should be at their desired state before the start of the PCI clock cycle during which the read is attempted, and they should remain at the same level until the end of the read cycle.  The voltages applied to the GPI pins must comply with the devices V <sub>IH</sub> and V <sub>IL</sub> requirements. Any unused GPI pins must not be left floating.  These pins are used as the A[10:6] pins in the A/A Mux interface.                                                                                                                                                  | X       |         | Input            |

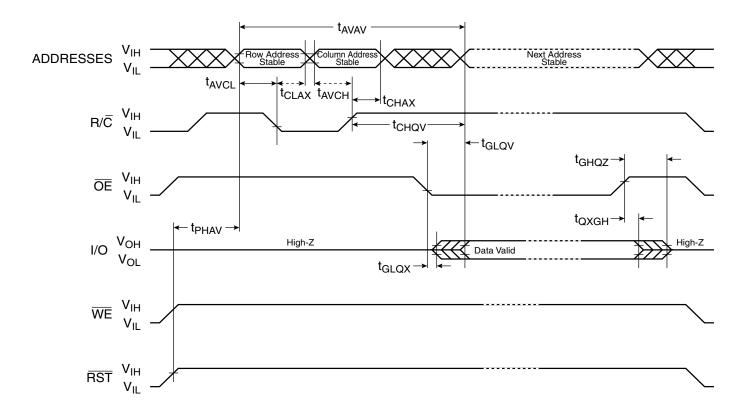

| A[10:0]  | <b>ADDRESS INPUTS</b> : These pins are used for inputting the multiplexed address values when using the A/A Mux interface. The addresses are latched by the rising and falling edge of R/C pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         | Х       | Input            |

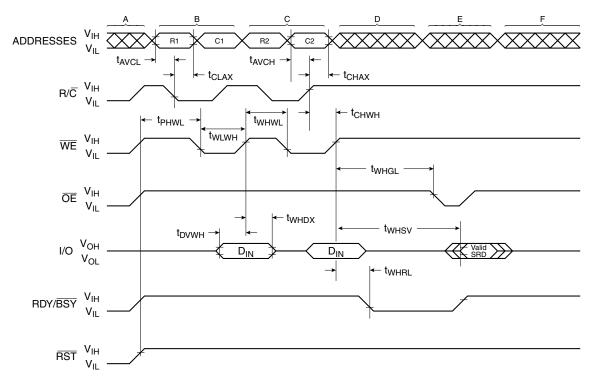

| I/O[7:0] | DATA INPUTS/OUTPUTS: The I/O pins are used in the A/A Mux interface to input data and commands during write cycles and to output data during memory array, Status Register, and identifier code read cycles. Data is internally latched during a write cycle.  The I/O pins will be in a high-impedance state when the outputs are disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                            |         | x       | Input/<br>Output |

| R/C      | <b>ROW/COLUMN ADDRESS SELECT</b> : In the A/A Mux interface, the R/ $\overline{C}$ pin is used to latch the address values presented on the A[10:0] pins. The row addresses (A10 - 0) are latched on the falling edge of R/ $\overline{C}$ , and the column addresses (A18 - A11) are latched on the rising edge of R/ $\overline{C}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         | х       | Input            |

| ŌĒ       | OUTPUT ENABLE: The $\overline{OE}$ pin is used in the A/A Mux interface to control the device's output buffers during a read cycle.  The I/O[7:0] pins will be in high-impedance state when the $\overline{OE}$ pin is deasserted (high).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         | Х       | Input            |

| WE       | WRITE ENABLE: The WE pin is used in the A/A Mux interface to control write operations to the device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         | Х       | Input            |

Table 5-1.

Signal Descriptions (Continued)

|         |                                                                                                                                                                                                                                                                                                                                    | Inter   | ace     |        |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|--------|

| Symbol  | Name and Function                                                                                                                                                                                                                                                                                                                  | FWH/LPC | A/A Mux | Туре   |

| RDY/BSY | READY/BUSY: The RDY/BSY pin provides the device's ready/busy status when using the A/A Mux interface. The RDY/BSY pin is a reflection of Status Register bit 7, which is used to indicate whether a program or erase operation has been completed.  Use of the RDY/BSY pin is optional, and the pin does not need to be connected. |         | x       | Output |

| vcc     | <b>DEVICE POWER SUPPLY</b> : The VCC pin is used to supply the source voltage to the device. Program and erase operations are inhibited when $V_{CC}$ is less than or equal to $V_{LKO}$ . Operations at invalid $V_{CC}$ voltages may produce spurious results and should not be attempted.                                       | Х       | х       | Power  |

| GND     | <b>GROUND</b> : The ground reference for the power supply. GND should be connected to the system ground.                                                                                                                                                                                                                           | Х       | Х       | Power  |

| NC      | <b>NO CONNECT</b> : NC pins have no internal connections and can be driven or left floating. If the pins are driven, the voltage levels should comply with $V_{\rm IH}$ and $V_{\rm IL}$ requirements.                                                                                                                             | Х       | х       | _      |

| RES     | <b>RESERVED</b> : RES pins are reserved for future device enhancements or functionality. These pins may be left floating or may be driven. If the pins are driven, the voltage levels should comply with $V_{IH}$ and $V_{IL}$ requirements.  These pins are used as the RDY/BSY and I/O[7:4] pins in the A/A Mux interface.       | х       | х       | -      |

### 6. Interface Selection

The AT49LH004 can operate in two distinct interface modes: The FWH/LPC interface and the A/A Mux interface. Selection of the interface is determined by the state of the IC pin. When the IC pin is held low, the device will operate using the FWH/LPC interface. Alternatively, when the IC pin is held high, the device will operate using the A/A Mux interface.

### 7. FWH/LPC Interface

The FWH/LPC interface is designed as an In-System interface used in communicating with either the I/O Controller Hub (ICH) in Intel chipsets or typically the PCI south bridge in non-Intel chipsets.

The FWH/LPC interface uses a 5-signal communication interface consisting of a 4-bit data bus, the FWH/LAD[3:0] pins, and one control line, the FWH4/LFRAME pin. The operation and timing of the interface is based on the 33 MHz PCI clock, and the buffers for the FWH/LPC interface are PCI compliant. To ensure the effective delivery of security and manageability features, the FWH/LPC interface is the only way to get access to the full feature set of the device.

Commands, addresses, and data are transferred via the FWH/LPC interface using a series of fields. The field sequences and contents are strictly defined for FWH and LPC memory cycles. These field sequences are detailed in the FWH Interface Operation and LPC Interface Operation sections.

Since the AT49LH004 can be used as either a FWH Flash or an LPC Flash, the device is capable of automatically detecting which type of memory cycle is being performed. For a FWH/LPC cycle, the host will drive the FWH4/LFRAME pin low for one or more clock cycles to initiate the operation. After driving the FWH4/LFRAME pin low, the host will send a START value to indicate the type of FWH/LPC cycle that is to be performed. The value of the START field determines whether the device will operate using a FWH cycle or an LPC cycle. Table 7-1 details the three valid START fields that the device will recognize.

Table 7-1. FWH/LPC Start Fields

| START Value | Cycle Type                                                                                                                                                                                             |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0000b       | LPC Cycle – The type (memory, I/O, DMA) and direction of the cycle (read or write) is determined by the second field (CYCTYPE + DIR) of the LPC cycle. Only memory cycles are supported by the device. |

| 1101b       | FWH Memory Read Cycle                                                                                                                                                                                  |

| 1110b       | FWH Memory Write Cycle                                                                                                                                                                                 |

If a valid START value is not detected, then the device will enter standby mode when the FWH4/LFRAME pin is high and no internal operation is in progress. The FWH/LAD[3:0] pins will also be placed in a high-impedance state.

#### 7.1 FWH4/LFRAME Pin

FWH4/LFRAME is used by the master to indicate the start of cycles and the termination of cycles due to an abort or time-out condition. This signal is to be used by peripherals to know when to monitor the bus for a cycle.

The FWH4/LFRAME signal is used as a general notification that the FWH/LAD[3:0] lines contain information relative to the start or stop of a cycle, and that peripherals must monitor the bus to determine whether the cycle is intended for them. The benefit to peripherals of FWH4/LFRAME is that it allows them to enter lower power states internally when a cycle is not intended for them.

When peripherals sample FWH4/\overline{LFRAME} is active, they are to immediately stop driving the FWH/LAD[3:0] signal lines on the next clock and monitor the bus for new cycle information.

### 7.2 FWH/LAD[3:0] Pins

The FWH/LAD[3:0] signal lines communicate address, control, and data information over the LPC bus between a master and a peripheral. The information communicated are: start, stop (abort a cycle), transfer type (memory, I/O, DMA), transfer direction (read/write), address, data, wait states, DMA channel, and bus master grant.

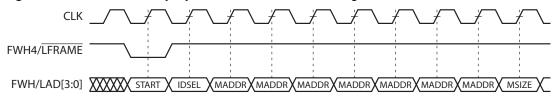

### 7.3 FWH Memory Cycles

A valid FWH memory cycle begins with the host driving the FWH4/\overline{LFRAME} signal low for one or more clock cycles. While the FWH4/\overline{LFRAME} signal is low, a valid START value of either 1101b (FWH memory read) or 1110b (FWH memory write) must be driven on the FWH/LAD[3:0] pins. Following the START field, an IDSEL (Device Select) field must be sent to the device. The IDSEL field acts like a chip select in that it indicates which device should respond to the current operation. After the IDSEL field has been sent, the 7-clock MADDR (Memory Address) field must be sent to the device to provide the 28-bit starting address location of where to begin reading or writing in the memory. Following the MADDR field, the MSIZE (Memory Size) field must be sent to indicate the number of bytes to transfer.

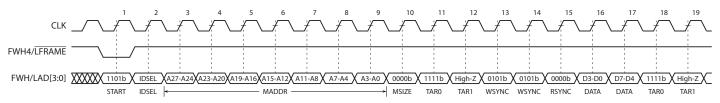

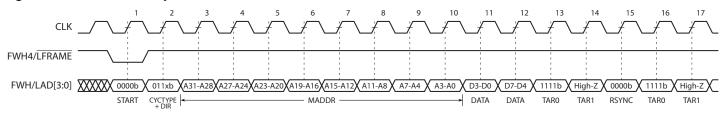

Figure 7-1. FWH Memory Cycle Initiation and Addressing

#### 7.3.1 Start Field

This 1-clock field indicates the start of a cycle. It is valid on the last clock that FWH4/\overline{LFRAME} is sampled low. The two start fields that are used for a FWH cycle are: 1101b to indicate a FWH memory read cycle and 1110b to indicate a FWH memory write cycle. If the start field that is sampled is not one of these values, then the cycle attempted is not a FWH memory cycle. It may be a valid LPC memory cycle that the device will attempt to decode.

#### 7.3.2 IDSEL (Device Select) Field

This 1-clock field is used to indicate which FWH component in the system is being selected. The four bits transmitted over FWH/LAD[3:0] during this clock are compared with values strapped on the ID[3:0] pins. If there is a match, the device will continue to decode the cycle to determine which bytes are requested on a read or which bytes to update on a write. If there isn't a match, the device may discard the rest of the cycle and go into a standby power state.

#### 7.3.3 MADDR (Memory Address) Field

This is a 7-clock field that is used to provide a 28-bit (A27 - A0) memory address. This allows for provisioning of up to 256 MB per FWH memory device, for a total of a 4 GB addressable space if 16 FWH memory devices (256 MB each) were used in a system.

The AT49LH004 only decodes the last six MADDR nibbles (A23 - A0) and ignores address bits A27 - A23 and A21 - A19. Address bit A22 is used to determine whether reads or writes to the device will be directed to the memory array (A22 = 1) or to the register space (A22 = 0).

Addresses are transferred to the device with the most significant nibble first.

#### 7.3.4 MSIZE (Memory Size) Field

The 1-clock MSIZE is used to indicate how many bytes of data will be transferred during a read or write. The AT49LH004 only supports single-byte transfers, so 0000b must be sent in this field to indicate a single-byte transfer.

#### 7.3.5 Additional Fields for FWH Memory Cycles

Additional fields are required to complete a FWH read or write cycle. The placement of these fields, in addition to the data field, depends on whether the cycle is a FWH read or write. The FWH Read Cycle and FWH Write Cycle sections detail the order of the various fields.

#### 7.3.6 TAR (Turn-around) Field

This 2-clock field is driven by the master when it is turning control over to the FWH memory device, and it is driven by the FWH device when it is turning control back over to the master. On the first clock of the TAR field, the master or FWH drives the FWH/LAD[3:0] lines to 1111b. On the second clock, the master or FWH device puts the FWH/LAD[3:0] lines into a high-impedance state.

#### 7.3.7 SYNC (Synchronize) Field

This field is used to add wait-states for an access. It can be several clocks in length. On target cycles, this field is driven by the FWH memory device. If the FWH device needs to assert wait-states, it does so by driving a "wait" SYNC value of 0101b on the FWH/LAD[3:0] pins until it is ready. When ready, the device will drive a "ready" SYNC value of 0000b on the FWH/LAD[3:0] lines. Valid values for the SYNC field are shown in Table 7-2.

Table 7-2. Valid SYNC Values

| SYNC Value | SYNC Type                                                                              |

|------------|----------------------------------------------------------------------------------------|

| 0000b      | RSYNC (Ready SYNC) – Synchronization has been achieved with no error.                  |

| 0101b      | WSYNC (Wait SYNC) – Device is indicating wait-states (also referred to as short-sync). |

### 7.4 FWH Read Cycle

FWH read cycles are used to read data from the memory array, the Sector Locking Registers, the GPI register, the Status Register, and to read the product ID information. Upon initial device power-up or after exiting from a reset condition, the device will automatically default to the read array mode.

Valid FWH read cycles begin with a START field of 1101b being sent to the device. Following the IDSEL, MADDR, and MSIZE fields, a 2-clock TAR field must be sent to the device to indicate that the master is turning control of the LPC bus over to the FWH memory device. After the second clock of the TAR phase, the FWH device assumes control of the bus and begins driving SYNC fields to add wait-states. When the device is ready to output data, it will first send a "ready" SYNC and then output one byte of data during the next two clock cycles. The data is sent one nibble at a time with the low nibble being output first followed by the high nibble. After the data has been output, the FWH device will send a 2-clock TAR field to the master to indicate that it is turning control of the LPC bus back over to the master.

Table 7-2 shows a FWH read cycle that requires three SYNC clocks to access data from the memory array.

Figure 7-2. FWH Read Cycle

**Table 7-3.** FWH Read Cycle

| Clock Cycle | Field Name | Field Value <sup>(1)</sup><br>FWH/LAD[3:0] | FWH/LAD[3:0]<br>Direction | Comments                                                                                                                                                                                                                                |

|-------------|------------|--------------------------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1           | START      | 1101b                                      | IN                        | FWH4/LFRAME must be active (low) for the device to respond. Only the last START field (before FWH4/LFRAME transitioning high) should be recognized. The START field contents indicate a FWH memory read cycle.                          |

| 2           | IDSEL      | 0000b to 1111b                             | IN                        | Indicates which FWH memory device should respond. If the IDSEL field matches the strapping values on ID[3:0], then that particular device will respond to subsequent commands.                                                          |

| 3 - 9       | MADDR      | YYYY                                       | IN                        | These seven clock cycles make up the 28-bit memory address. YYYY is one nibble of the entire address. Addresses are transferred with the most significant nibble first.                                                                 |

| 10          | MSIZE      | 0000b<br>(indicates<br>1 byte)             | IN                        | The MSIZE field indicates how many bytes will be transferred. The device only supports single-byte operations, so MSIZE must be 0000b.                                                                                                  |

| 11          | TAR0       | 1111b                                      | IN then float             | In this clock cycle, the master has driven the bus to all 1s and then floats the bus prior to the next clock cycle. This is the first part of the bus "turn-around cycle".                                                              |

| 12          | TAR1       | 1111b (float)                              | Float then OUT            | The device takes control of the bus during this clock cycle.                                                                                                                                                                            |

| 13 - 14     | WSYNC      | 0101b (wait)                               | OUT                       | The device outputs the value 0101b, a "wait" SYNC, for two clock cycles. This value indicates to the master that data is not yet available from the device. This number of wait-syncs is a function of the device's memory access time. |

| 15          | RSYNC      | 0000b (ready)                              | OUT                       | During this clock cycle, the device will generate a "ready" SYNC indicating that the least significant nibble of the data byte will be available during the next clock cycle.                                                           |

| 16          | DATA       | YYYY                                       | OUT                       | YYYY is the least significant nibble of the data byte.                                                                                                                                                                                  |

| 17          | DATA       | YYYY                                       | OUT                       | YYYY is the most significant nibble of the data byte.                                                                                                                                                                                   |

| 18          | TAR0       | 1111b                                      | OUT then float            | The FWH memory device drives the bus to 1111b to indicate a turn-around cycle.                                                                                                                                                          |

| 19          | TAR1       | 1111b (float)                              | Float then IN             | The FWH memory device floats its outputs, and the master regains control of the bus during this clock cycle.                                                                                                                            |

Note: 1. Field contents are valid on the rising edge of the present clock cycle.

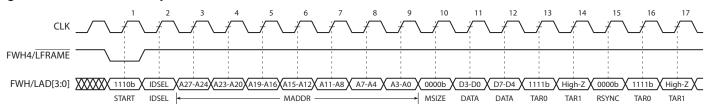

### 7.5 FWH Write Cycle

FWH write cycles are used to send commands to the device and to program data into the memory array.

Valid FWH write cycles begin with a START field of 1110b being sent to the device. Following the IDSEL, MADDR, and MSIZE fields, the master sends one byte of data to the FWH device during the next two clock cycles. The data is sent one nibble at a time with the low nibble being output first followed by the high nibble. After the data has been sent, the master will send a 2-clock TAR field to the FWH device to indicate that it is turning control of the LPC bus back over to the FWH. After the second clock of the TAR phase, the FWH device assumes control of the bus and drives a "ready" SYNC field to verify that it has received the data. The FWH device will then send a 2-clock TAR field to the master to indicate that it is turning control of the bus back over to the master.

Figure 7-3. FWH Write Cycle

**Table 7-4.** FWH Write Cycle

| Clock<br>Cycle | Field Name | Field Value <sup>(1)</sup><br>FWH/LAD[3:0] | FWH/LAD[3:0]<br>Direction | Comments                                                                                                                                                                                                        |

|----------------|------------|--------------------------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1              | START      | 1110b                                      | IN                        | FWH4/LFRAME must be active (low) for the device to respond. Only the last START field (before FWH4/LFRAME transitioning high) should be recognized. The START field contents indicate a FWH memory write cycle. |

| 2              | IDSEL      | 0000b to 1111b                             | IN                        | Indicates which FWH memory device should respond. If the IDSEL field matches the strapping values on ID[3:0], then that particular device will respond to subsequent commands.                                  |

| 3 - 9          | MADDR      | YYYY                                       | IN                        | These seven clock cycles make up the 28-bit memory address. YYYY is one nibble of the entire address. Addresses are transferred with the most significant nibble first.                                         |

| 10             | MSIZE      | 0000b<br>(indicates<br>1 byte)             | IN                        | The MSIZE field indicates how many bytes will be transferred. The device only supports single-byte operations, so MSIZE must be 0000b.                                                                          |

| 11             | DATA       | YYYY                                       | IN                        | YYYY is the least significant nibble of the data byte. The data byte is either any valid Flash command or the data to be programmed into the memory array.                                                      |

| 12             | DATA       | YYYY                                       | IN                        | YYYY is the most significant nibble of the data byte.                                                                                                                                                           |

| 13             | TAR0       | 1111b                                      | IN then float             | In this clock cycle, the master has driven the bus to all 1s and then floats the bus prior to the next clock cycle. This is the first part of the bus "turn-around cycle".                                      |

| 14             | TAR1       | 1111b (float)                              | Float then OUT            | The device takes control of the bus during this clock cycle.                                                                                                                                                    |

| 15             | RSYNC      | 0000b (ready)                              | OUT                       | During this clock cycle, the device will generate a "ready" SYNC indicating that the data byte has been received.                                                                                               |

| 16             | TAR0       | 1111b                                      | OUT then float            | The FWH memory device drives the bus to 1111b to indicate a turn-around cycle.                                                                                                                                  |

| 17             | TAR1       | 1111b (float)                              | Float then IN             | The FWH memory device floats its outputs, and the master regains control of the bus during this clock cycle.                                                                                                    |

Note: 1. Field contents are valid on the rising edge of the present clock cycle.

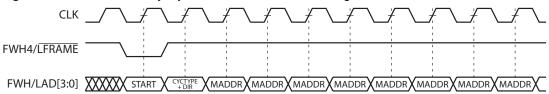

### 7.6 LPC Memory Cycles

A valid LPC memory cycle begins with the host driving the FWH4/LFRAME signal low for one or more clock cycles. While the FWH4/LFRAME signal is low, a valid START value of 0000b must be driven on the FWH/LAD[3:0] pins. Following the START field, a CYCTYPE + DIR (Cycle Type and Direction) field must be sent to the device to indicate the type of cycle (e.g., memory access, I/O access, etc.) and the direction (read or write) of the transfer. After the CYCTYPE + DIR field has been sent, the 8-clock MADDR (Memory Address) field must be sent to the device to provide the 32-bit starting address location of where to begin reading or writing in the memory.

Figure 7-4. LPC Memory Cycle Initiation and Addressing

#### 7.6.1 Start Field

This 1-clock field indicates the start of a cycle. It is valid on the last clock that FWH4/LFRAME is sampled low. The start field that is used for an LPC cycle is 0000b. If the start field that is sampled is not 0000b, then the cycle attempted is not an LPC memory cycle. It may be a valid FWH memory cycle that the device will attempt to decode.

#### 7.6.2 CYCTYPE + DIR (Cycle Type And Direction) Field

This 1-clock field is used to indicate the type of cycle and the direction of the transfer to be performed. Of the four bits placed on the FWH/LAD[3:0] pins, bits[3:2] must be 01b to indicate that the transfer will be a memory cycle. Values other than 01b, which may be used to specify an I/O cycle or a DMA cycle for other components in the system, will cause the device to enter standby mode when the FWH4/LFRAME pin is brought high and no internal operation is in progress. The FWH/LAD[3:0] pins will also be placed in a high-impedance state.

Bit[1] is used to determine the direction of the transfer. 0 is used to indicate a read, and 1 is used to indicate a write. Bit[0] is ignored and reserved for future use. Table 7-5 details the two valid CYCTYPE + DIR fields that the device will respond to.

**Table 7-5.** Valid CYCTYPE + DIR Values

| FWH/LAD[3:0] | Cycle Type       |

|--------------|------------------|

| 010xb        | LPC Memory Read  |

| 011xb        | LPC Memory Write |

#### 7.6.3 MADDR (Memory Address) Field

This is an 8-clock field that is used to provide a 32-bit (A31 - A0) memory address. The 32 address bits allow for the provisioning to access up to 4 GB of memory space.

The AT49LH004 only decodes the last six MADDR nibbles (A23 - A0) and ignores address bits A31 - A24. Address bit A23 is used to determine whether reads or writes to the device will be directed to the memory array (A23 = 1) or to the register space (A23 = 0).

Unlike FWH memory cycles, LPC cycles do not use an IDSEL field to determine which LPC device in the system is being selected. Instead, the strapping values on the ID[3:0] pins are compared against address bits A22 - A19 in the MADDR field. For the actual comparison, the strapped values are internally inverted. For example, if ID3 was strapped to GND, a logical value of 1 would be compared against address bit A22. If the inverted states of the ID[3:0] pins match with address bits A22 - A19, then the device will continue to decode the rest of cycle (see LPC Multiple Device Selection for mode details).

Addresses are transferred to the device with the most significant nibble first.

#### 7.6.4 Additional Fields for LPC Memory Cycles

Additional fields are required to complete an LPC read or write cycle. The placement of these fields, in addition to the data field, depends on whether the cycle is an LPC read or write. The LPC Read Cycle and LPC Write Cycle sections detail the order of the various fields.

#### 7.6.5 TAR (Turn-around) Field

This 2-clock field is driven by the master when it is turning control over to the LPC memory device, and it is driven by the LPC device when it is turning control back over to the master. On the first clock of the TAR field, the master or LPC device drives the FWH/LAD[3:0] lines to 1111b. On the second clock, the master or LPC device puts the FWH/LAD[3:0] lines into a high-impedance state.

#### 7.6.6 SYNC (Synchronize) Field

This field is used to add wait-states for an access. It can be several clocks in length. On target cycles, this field is driven by the LPC memory device. If the LPC device needs to assert wait-states, it does so by driving a "wait" SYNC value of 0101b on the FWH/LAD[3:0] pins until it is ready. When ready, the device will drive a "ready" SYNC value of 0000b on the FWH/LAD[3:0] lines. Valid values for the SYNC field are shown in Table 7-6.

Table 7-6. Valid SYNC Values

| SYNC Value | SYNC Type                                                                              |

|------------|----------------------------------------------------------------------------------------|

| 0000b      | RSYNC (Ready SYNC) – Synchronization has been achieved with no error.                  |

| 0101b      | WSYNC (Wait SYNC) – Device is indicating wait-states (also referred to as short-sync). |

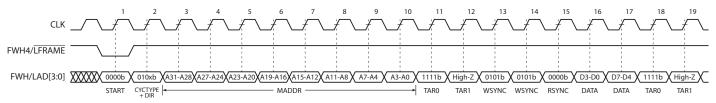

### 7.7 LPC Read Cycle

LPC read cycles are used to read data from the memory array, the Sector Locking Registers, the GPI register, the Status Register, and the product ID information. Upon initial device power-up or after exiting from a reset condition, the device will automatically default to the read array mode.

Valid LPC read cycles begin with a START field of 0000b and a CYCTYPE + DIR field of 010xb being sent to the device. Following the MADDR field, a 2-clock TAR field must be sent

to the device to indicate that the master is turning control of the LPC bus over to the LPC memory device. After the second clock of the TAR phase, the LPC device assumes control of the bus and begins driving SYNC fields to add wait-states. When the device is ready to output data, it will first send a "ready" SYNC and then output one byte of data during the next two clock cycles. The data is sent one nibble at a time with the low nibble being output first followed by the high nibble. After the data has been output, the LPC device will send a 2-clock TAR field to the master to indicate that it is turning control of the LPC bus back over to the master.

Figure 7-5 shows a LPC read cycle that requires three SYNC clocks to access data from the memory array.

Figure 7-5. LPC Read Cycle

Table 7-7. LPC Read Cycle

| Clock Cycle | Field Name       | Field Value <sup>(1)</sup><br>FWH/LAD[3:0] | FWH/LAD[3:0]<br>Direction | Comments                                                                                                                                                                                                                                |

|-------------|------------------|--------------------------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1           | START            | 0000b                                      | IN                        | FWH4/LFRAME must be active (low) for the device to respond. Only the last START field (before FWH4/LFRAME transitioning high) should be recognized. The START field contents indicate an LPC cycle.                                     |

| 2           | CYCTYPE +<br>DIR | 010xb                                      | IN                        | Indicates that the cycle type is an LPC memory cycle and the direction of the transfer is a read.                                                                                                                                       |

| 3 - 10      | MADDR            | YYYY                                       | IN                        | These eight clock cycles make up the 32-bit memory address. YYYY is one nibble of the entire address. Addresses are transferred with the most significant nibble first.                                                                 |

| 11          | TAR0             | 1111b                                      | IN then float             | In this clock cycle, the master has driven the bus to all 1s and then floats the bus prior to the next clock cycle. This is the first part of the bus "turn-around cycle".                                                              |

| 12          | TAR1             | 1111b (float)                              | Float then OUT            | The device takes control of the bus during this clock cycle.                                                                                                                                                                            |

| 13 - 14     | WSYNC            | 0101b (wait)                               | OUT                       | The device outputs the value 0101b, a "wait" SYNC, for two clock cycles. This value indicates to the master that data is not yet available from the device. This number of wait-syncs is a function of the device's memory access time. |

| 15          | RSYNC            | 0000b (ready)                              | OUT                       | During this clock cycle, the device will generate a "ready" SYNC indicating that the least significant nibble of the data byte will be available during the next clock cycle.                                                           |

| 16          | DATA             | YYYY                                       | OUT                       | YYYY is the least significant nibble of the data byte.                                                                                                                                                                                  |

| 17          | DATA             | YYYY                                       | OUT                       | YYYY is the most significant nibble of the data byte.                                                                                                                                                                                   |

| 18          | TAR0             | 1111b                                      | OUT then float            | The LPC memory device drives the bus to 1111b to indicate a turn-around cycle.                                                                                                                                                          |

| 19          | TAR1             | 1111b (float)                              | Float then IN             | The LPC memory device floats its outputs, and the master regains control of the bus during this clock cycle.                                                                                                                            |

Note: 1. Field contents are valid on the rising edge of the present clock cycle.

### 7.8 LPC Write Cycle

LPC write cycles are used to send commands to the device and to program data into the memory array.

Valid LPC write cycles begin with a START field of 0000b and a CYCTYPE + DIR field of 011xb being sent to the device. Following the MADDR field, the master sends one byte of data to the LPC device during the next two clock cycles. The data is sent one nibble at a time with the low nibble being output first followed by the high nibble. After the data has been sent, the master will send a 2-clock TAR field to the LPC device to indicate that it is turning control of the bus back over to the LPC device. After the second clock of the TAR phase, the LPC device assumes control of the bus and drives a "ready" SYNC field to verify that it has received the data. The LPC device will then send a 2-clock TAR field to the master to indicate that it is turning control of the bus back over to the master.

Figure 7-6. LPC Write Cycle

Table 7-8. LPC Write Cycle

| Clock Cycle | Field Name       | Field Value <sup>(1)</sup><br>FWH/LAD[3:0] | FWH/LAD[3:0]<br>Direction | Comments                                                                                                                                                                                            |

|-------------|------------------|--------------------------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1           | START            | 0000b                                      | IN                        | FWH4/LFRAME must be active (low) for the device to respond. Only the last START field (before FWH4/LFRAME transitioning high) should be recognized. The START field contents indicate an LPC cycle. |

| 2           | CYCTYPE +<br>DIR | 011xb                                      | IN                        | Indicates that the cycle type is an LPC memory cycle and the direction of the transfer is a write.                                                                                                  |

| 3 - 10      | MADDR            | YYYY                                       | IN                        | These eight clock cycles make up the 32-bit memory address. YYYY is one nibble of the entire address. Addresses are transferred with the most significant nibble first.                             |

| 11          | DATA             | YYYY                                       | IN                        | YYYY is the least significant nibble of the data byte. The data byte is either any valid Flash command or the data to be programmed into the memory array.                                          |

| 12          | DATA             | YYYY                                       | IN                        | YYYY is the most significant nibble of the data byte.                                                                                                                                               |

| 13          | TAR0             | 1111b                                      | IN then float             | In this clock cycle, the master has driven the bus to all 1s and then floats the bus prior to the next clock cycle. This is the first part of the bus "turn-around cycle".                          |

| 14          | TAR1             | 1111b (float)                              | Float then OUT            | The device takes control of the bus during this clock cycle.                                                                                                                                        |

| 15          | RSYNC            | 0000b (ready)                              | OUT                       | During this clock cycle, the device will generate a "ready" SYNC indicating that the data byte has been received.                                                                                   |

| 16          | TAR0             | 1111b                                      | OUT then float            | The LPC memory device drives the bus to 1111b to indicate a turn-around cycle.                                                                                                                      |

| 17          | TAR1             | 1111b (float)                              | Float then IN             | The LPC memory device floats its outputs, and the master regains control of the bus during this clock cycle.                                                                                        |

Note: 1. Field contents are valid on the rising edge of the present clock cycle.

# 8. Response to Invalid FWH/LPC Fields

During FWH/LPC operations, the device will not explicitly indicate that it has received invalid field sequences. The response to specific invalid fields or sequences is outlined in the following paragraphs.

### 8.1 FWH Cycles

#### 8.1.1 ID Mismatch

If the IDSEL field does not match ID[3:0], then the device will ignore the FWH cycle. The device will then enter standby mode when the FWH4/LFRAME pin is brought high and no internal operation is in progress. The FWH/LAD[3:0] pins will also be placed in a high-impedance state.

### 8.1.2 Address Out of Range

The FWH address sequences is seven fields long (28 bits), but only the last six address fields (A23 - A0) will be decoded. Therefore, address bits A27 - A24 will be ignored. In addition, because of the device density, address bits A23 and A21 - A19 will be ignored. Address bit A22 is used to determine whether reads or writes to the device will be directed to the memory array (A22 = 1) or to the register space (A22 = 0).

#### 8.1.3 Invalid MSIZE Field

If the device receives an invalid size field during a read or write operation, the internal state machine will reset and no operation will be attempted. The device will generate no response of any kind in this situation. Invalid size fields for a read or write cycle are anything but 0000b. In addition, when accessing register space, invalid field sizes are anything but 0000b.

Once valid START, IDSEL, and MSIZE fields are received, the device will always respond to subsequent inputs as if they were valid. As long as the states of FWH/LAD[3:0] and FWH4/LFRAME are known, the response of the device to signals received during the FWH cycle should be predictable. The device will make no attempt to check the validity of incoming Flash operation commands.

### 8.2 LPC Cycles

#### 8.2.1 Address Out of Range

The LPC address sequences is eight fields long (32 bits), but only the last six address fields (A23 - A0) will be decoded. Therefore, address bits A31 - A24 will be ignored. Address bits A22 - A19 will be decoded based on the strapping values on the ID[3:0] pins. Address bit A23 is used to determine whether reads or writes to the device will be directed to the memory array (A23 = 1) or to the register space (A23 = 0).

Once valid START and CYCTYPE + DIR fields are received, the device will always respond to subsequent inputs as if they were valid. As long as the states of FWH/LAD[3:0] and FWH4/LFRAME are known, the response of the device to signals received during the LPC cycle should be predictable. The device will make no attempt to check the validity of incoming Flash operation commands.

### 9. Bus Abort

The Bus Abort operation can be used to immediately abort the current bus operation. A Bus Abort occurs when FWH4/\(\overline{LFRAME}\) is driven low for one or more clock cycles after the start of a bus cycle. The memory will place the FWH/LAD[3:0] pins in a high-impedance state, and the internal state machine will reset. During a write cycle, there is the possibility that an internal Flash write or erase operation may be in progress (or has just been initiated). If the FWH4/\(\overline{LFRAME}\) pin is asserted during this time frame, the internal operation will not abort. However, the internal state machine will not initiate a Flash write or erase operation until it has received the last nibble from the host. This means that FWH4/\(\overline{LFRAME}\) can be asserted as late as clock cycle 12 (see Table 7-4 and Table 7-8) and no internal Flash operation will be attempted.

When the FWH4/LFRAME pin has been driven low to abort a cycle, the host may issue a START field of 1111b (stop/abort) to return the interface to the ready mode.

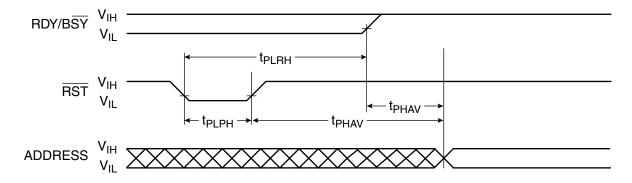

### 10. Device Reset

Asserting RST or NIT initiates a device reset. In read mode, RST or NIT low deselects the memory, places the output drivers in a high-impedance state, and turns off all internal circuits. RST or NIT must be held low for the minimum specified t<sub>PLPH</sub> time (FWH/LPC and A/A Mux operations). The device resets to read array mode upon return from reset, and all Sector Locking Registers are reset to their default (write-locked) state. Since all Sector Locking Registers are reset, all sectors in the memory array are set to the write-locked status regardless of their locked state prior to reset.

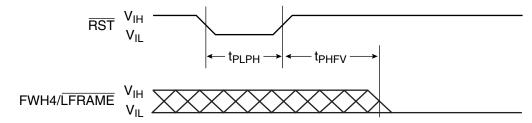

A reset recovery time  $(t_{PHFV} \text{ using the FWH/LPC})$  interface and  $t_{PHAV} \text{ using the A/A Mux}$  interface) is required from  $\overline{RST}$  or  $\overline{INIT}$  switching back high until writes to the CUI are recognized. A reset latency will occur if a reset procedure is performed during a programming or erase operation.

During sector erase or program, driving RST or INIT low will abort the operation underway in addition to causing a reset latency. Memory contents being altered are no longer valid since the data may be partially erased or programmed.

It is important to assert RST or INIT during system reset. When the system comes out of reset, it will expect to read from the memory array of the device. If a system reset occurs with no FWH/LPC device reset (this will be hardware dependent), it is possible that proper CPU initialization will not occur (the FWH/LPC memory may be providing status information instead of memory array data).

### 11. Sector Protection

Sectors in the memory array can be protected from program and erase operations using a hardware controlled method and/or a software (register-based) controlled method.

#### 11.1 Hardware Write Protection

Two pins are available to provide hardware write protection capabilities. The Top Boot Sector Lock (TBL) pin, when held low, prevents program and sector erase operations to the top sector of the device (sector 10) where critical code can be stored. When operating in FWH mode, the TBL pin is also used to protect sectors 9, 8, and 7 against program and erase operations. In addition, when operating in LPC mode, the TBL pin has the flexibility to provide erase

protection to the top 64-Kbyte region (sectors 10, 9, 8, and 7) of the device when using the Uniform Sector Erase command. This allows the TBL pin to protect a larger region for systems that require a 64-Kbyte top boot sector rather than a 32-Kbyte top boot sector.

When the TBL pin is high, hardware write protection for program and erase operations to the top 64-Kbyte region (in FWH mode) or the top 32-Kbyte boot sector (in LPC mode) is disabled. Provided that the Write-Lock bits in the Sector Locking Registers are not set (detailed later), sector erase or program commands can then be issued to the device to program or erase these regions. In addition, in LPC mode, the entire top 64-Kbyte region (sectors 10, 9, 8, and 7) can be erased if using the Uniform Sector Erase command.

The Write Protect  $(\overline{WP})$  pin, which operates independently from the  $\overline{TBL}$  pin, serves the same basic function as the  $\overline{TBL}$  pin for the remaining sectors except the top boot sector (in LPC mode) or the top 64-Kbyte region (in FWH mode). When the  $\overline{WP}$  pin is held low in LPC mode, program and standard Sector Erase command operations to sectors 9 through 0 will not be allowed. If using the Uniform Sector Erase command, then erase operations to sectors 6 through 0 cannot be performed, and erase protection for sectors 10 through 7 will be controlled by the  $\overline{TBL}$  pin. In FWH mode, the  $\overline{WP}$  pin will always protect sectors 6 through 0 against both erase and program operations.

The TBL and WP pins must be set to the desired protection state prior to starting a program or erase operation because they are sampled at the beginning of the operation. Changing the state of TBL or WP during a program or erase operation may cause unpredictable results. The new lock status will take place after the program or erase operation completes.

**Table 11-1.** Hardware Write Protection Options

|        |                 |                   |                                             | Hardware Write Protect                                                            | ction                                                       |

|--------|-----------------|-------------------|---------------------------------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------|

|        |                 |                   | FWH Mode                                    | LPC                                                                               | Mode                                                        |

| Sector | Size<br>(Bytes) | Address Range     | For All<br>Program and<br>Erase<br>Commands | For the Following<br>Commands:<br>Sector Erase (21H)<br>Byte Program (40H or 10H) | For the Following<br>Command:<br>Uniform Sector Erase (20H) |

| 10     | 32K             | 078000H - 07FFFFH | TBL                                         | TBL                                                                               | TBL                                                         |

| 9      | 8K              | 076000H - 077FFFH | TBL                                         | WP                                                                                | TBL                                                         |

| 8      | 8K              | 074000H - 075FFFH | TBL                                         | WP                                                                                | TBL                                                         |

| 7      | 16K             | 070000H - 073FFFH | TBL                                         | WP                                                                                | TBL                                                         |

| 6      | 64K             | 060000H - 06FFFFH | WP                                          | WP                                                                                | WP                                                          |

| 5      | 64K             | 050000H - 05FFFFH | WP                                          | WP                                                                                | WP                                                          |

| 4      | 64K             | 040000H - 04FFFFH | WP                                          | WP                                                                                | WP                                                          |

| 3      | 64K             | 030000H - 03FFFFH | WP                                          | WP                                                                                | WP                                                          |

| 2      | 64K             | 020000H - 02FFFFH | WP                                          | WP                                                                                | WP                                                          |

| 1      | 64K             | 010000H - 01FFFFH | WP                                          | WP                                                                                | WP                                                          |

| 0      | 64K             | 000000H - 00FFFFH | WP                                          | WP                                                                                | WP                                                          |

The TBL and WP pins function independently from the Sector Locking Registers. These pins, when active, will write protect the appropriate sector(s) against program and erase operations regardless of the values of the Sector Locking Registers. For example, when TBL is active, writing to the top sector is prevented regardless of the state of the Write-Lock bit for the top sector's locking register. In such a case, clearing the Write-Lock bit in the Sector Locking Register will have no functional effect even though the register may indicate that the sector is no longer locked. However, the register may still be set to Read-Lock the sector if desired.

For protecting the sectors of the memory array, the  $\overline{TBL}$  and  $\overline{WP}$  pins always take precedence over the Sector Locking Registers. In addition, the states of the  $\overline{TBL}$  and  $\overline{WP}$  pins have no effect on the values or status of the Sector Locking Registers.

### 11.2 Register-Based Sector Locking

The device has eight Sector Locking Registers in FWH mode and 11 Sector Locking Registers in LPC mode that are used in lieu of or in conjunction with the  $\overline{\text{TBL}}$  and  $\overline{\text{WP}}$  pins to control the lock protection for each sector in the memory array. The Sector Locking Registers are accessed through their respective address locations (detailed in Table 11-2) in the 4 GB system memory map. Since the address bit used to distinguish between memory and register accesses differs when the device is used as a FWH or LPC Flash (A22 for FWH and A23 for LPC), the register memory address will also differ.

The Sector Locking Registers are both readable and writable, and each register has three dedicated locking bits to control Read Lock, Write Lock, and Lock Down functions. Therefore, a Sector Locking Register can be read to determine what its current value is set to (e.g., set to Lock Down status). Reading the Sector Locking Registers, however, will not determine the status of the  $\overline{\text{TBL}}$  and  $\overline{\text{WP}}$  pins.

When returning from a reset condition or after power-up, the Sector Locking Registers will always default to a state of 01H.

**Table 11-2.** Sector Locking Registers

| Register              | Associated | Sector Size | Register Men | nory Address |               |

|-----------------------|------------|-------------|--------------|--------------|---------------|

| Name                  | Sector     | (Bytes)     | FWH MODE     | LPC MODE     | Default Value |

| S10_LK <sup>(1)</sup> | 10         | 32K         |              | FF7F8002H    | 01H           |

| S9_LK <sup>(1)</sup>  | 9          | 8K          | FFREGORIA    | FF7F6002H    | 01H           |

| S8_LK <sup>(1)</sup>  | 8          | 8K          | FFBF0002H    | FF7F4002H    | 01H           |

| S7_LK <sup>(1)</sup>  | 7          | 16K         |              | FF7F0002H    | 01H           |

| S6_LK                 | 6          | 64K         | FFBE0002H    | FF7E0002H    | 01H           |

| S5_LK                 | 5          | 64K         | FFBD0002H    | FF7D0002H    | 01H           |

| S4_LK                 | 4          | 64K         | FFBC0002H    | FF7C0002H    | 01H           |

| S3_LK                 | 3          | 64K         | FFBB0002H    | FF7B0002H    | 01H           |

| S2_LK                 | 2          | 64K         | FFBA0002H    | FF7A0002H    | 01H           |

| S1_LK                 | 1          | 64K         | FFB90002H    | FF790002H    | 01H           |

| S0_LK                 | 0          | 64K         | FFB80002H    | FF780002H    | 01H           |

Note: 1. In FWH mode, these registers are treated as one; therefore, only one Sector Locking Register is available for all sub-sectors (sectors 10, 9, 8, and 7) and the sub-sectors cannot be individually protected. The default value for this register is 01H.

#### 11.2.1 Read Lock

The default read status of all sectors upon power-up is read-unlocked. When a sector's Read-Lock bit is set (1 state), data cannot be read from that sector. An attempted read from a read-locked sector will result in data 00H being read (note that a read failure is not reflected in the Status Register). The read lock status can be unlocked by clearing (0 state) the Read-Lock bit, provided that the Lock-Down bit has not been set. The current read lock status of a particular sector can be determined by reading the corresponding Read-Lock bit.

#### 11.2.2 Write Lock

The default write status of all sectors upon power-up is write-locked (1 state). Any program or erase operations attempted on a locked sector will return an error in the Status Register (indicating sector lock). The status of the locked sector can be changed to unlocked (0 state) by clearing the Write-Lock bit, provided that the Lock-Down bit is not set. The current write lock status of a particular sector can be determined by reading the corresponding Write-Lock bit.