# Features

- Advanced RISC Architecture, 130 Powerful Instructions, Most Single-Clock Cycle Execution

- Clock Generator Provides CPU Rates up to 48 MHz

- Only One External Clock Crystal of 12 MHz Can Generate All the Required System Clocks:

- Internal Clock for Standard UART Rates

- A 48 MHz and 96 MHz Clock for USB Data Recovery

- AVR Processor and System Clock

- Full-speed USB Interface (12 Mbits per Second) 2.0 Compliant

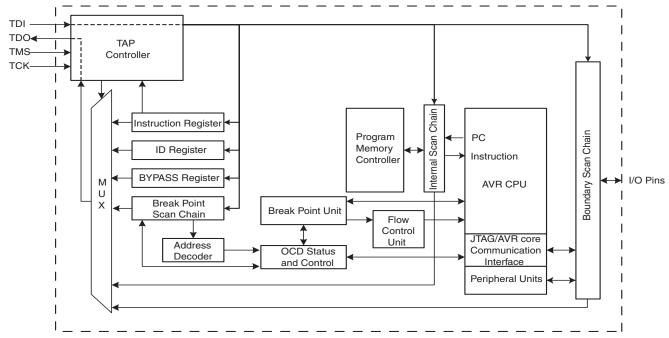

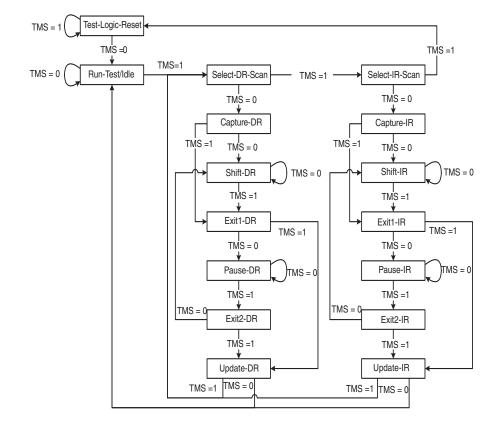

- JTAG (IEEE std. 1149.1 compliant) Interface

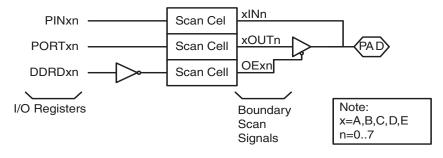

- Boundary-Scan Capabilities According to the JTAG Standard

- Extensive On-Chip Debug Support

- Two On-chip 16550 UARTs Supporting Baud Rates up to 921 Kbaud

- Both UARTs Incorporate Individual Transmit and Receive FIFOs of 16 Bytes

- UART0 Supports Modem Control Signals

- Programmable SPI Interface

- On-chip Bootstrap ROM Provides a Variety of Firmware Upgrade Modes

- Device Firmware Upgrade Through USB for the Internal Program SRAM (No External Non-volatile SPI Memory Required)

- Device Firmware Upgrade Through USB for both the Internal Program SRAM and the External SPI DataFlash<sup>®</sup> or EEPROM

- SPI Program Mode from the External DataFlash or EEPROM

- External Memory Interface Supporting up to 32 Kbytes of External RAM in Address Multiplexed Mode, 2 Banks of 256 Bytes in Non-multiplexed Mode, FIFO, or with an Extra 20 GPIOs

- DMA Channels Allow Fast Data Transfers between Endpoint Buffers and Internal or External SRAM (DMA Transfer Rate is 12 MHz for All Channels)

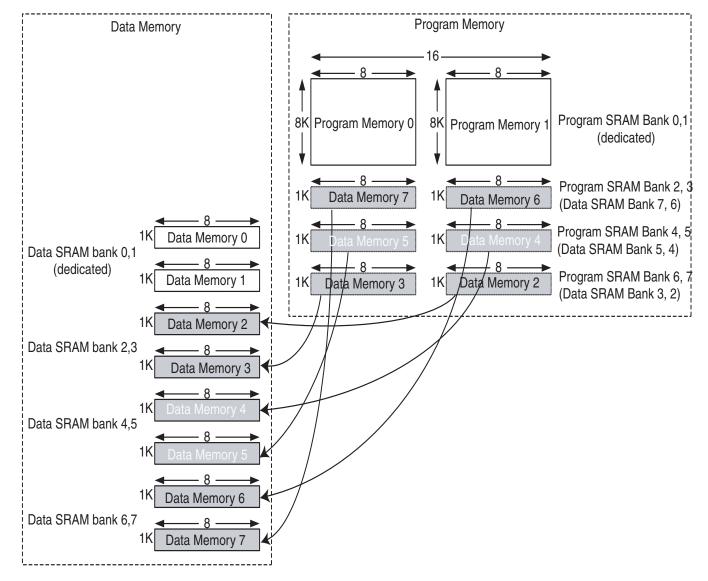

- 8K x 16 bits (up to 11K x 16 Bits), In-System SRAM for Program Code (Program Memory)

- On-chip 8 Kbytes SRAM for Data and Variables (2, 4, or 6 Kbytes can be Remapped for Program Storage in the Address Area Above the Program Memory

- Two 8-bit Timer/Counters

- One 16-bit Timer/Counter

- Four External Interrupts Through GPIOs

- Programmable Watchdog Timer

- Low Voltage Operation:

- 1.8V for the Core

- 1.8V or 3.3V for the Periphery

- 3.3V for the USB

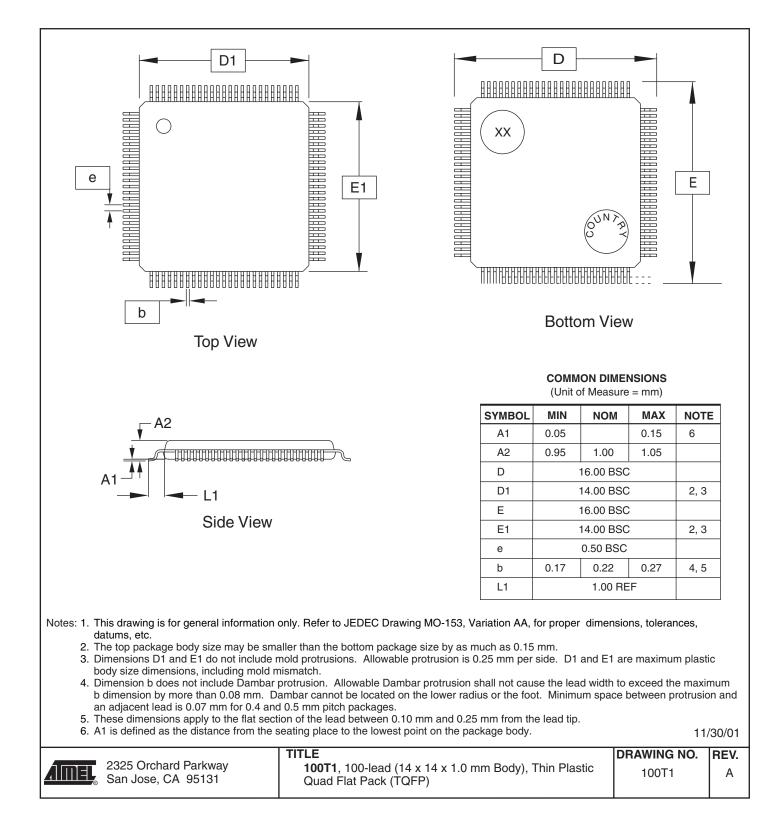

- 100-pin TQFP Package

- Applications

- Programmable USB-to-Serial Bridge for RS-2332 Devices (Cell Phones, Printers, PDAs, etc.)

- IrDA Control over USB

- USB Memory Sticks

- General High-speed Microcontroller Application

High-speed (48 MHz) AVR<sup>®</sup> Microcontroller with USB Interface

# AT76C713

5665B-USB-04/05

# 1. Overview

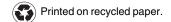

The AT76C713 is a low-power, high performing USB 2.0 full-speed microcontroller providing advanced features for USB peripherals. It combines a number of functions required in such a device, including the following:

The device is based on the AVR-enhanced RISC architecture core, which combines an advanced instruction set with 32 general-purpose working registers. By executing powerful instructions in a single clock cycle, the AT76C713 achieves throughputs approaching 1 MIPS per MHz, allowing the system designer to optimize the power consumption versus the processing speed

The clock generation circuit requires a clock input of 12 MHz and provides standard clock rates for the USB module and the on-chip UARTs, as well as several AVR CPU rates varying from 16 MHz up to 48 MHz

Internal DMA channels allow fast data transfers between the USB buffers and the external or the on-chip memory without processor interruption. USB DMA transfers use devoted data paths with a 12 Mbytes transfer rate

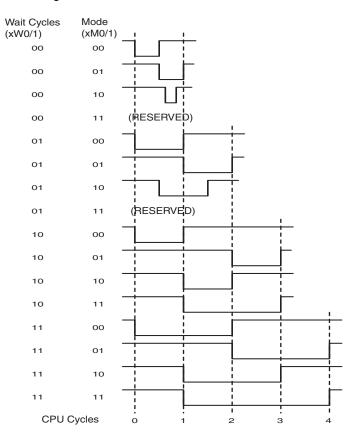

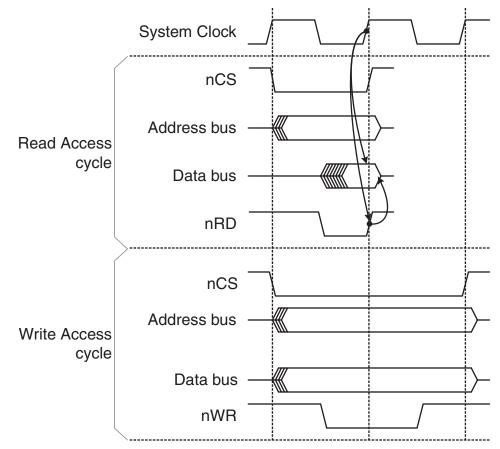

An on-chip flexible memory controller allows dynamic memory mapping and provides the required timing for interfacing with slow or fast external memory devices, like SRAM or FIFOs

Five multipurpose I/O ports, PORT(A-E), provide the signals for all the serial and parallel interfaces. Programmable strobe signals are provided for external FIFO access. In addition, the AT76C713 supports various power-down modes and offers four external interrupts, a programmable Watchdog Timer, and flexible Timer/Counters with compare modes

On power-up, the bootstrap code is executed from the boot ROM. The purpose of the bootstrap code is to load the application code into the program memory. The application code is executed from the on-chip SRAM program memory, contributing to the low-power consumption. Different programming modes are supported, depending on the application (that is, the mode is selected externally by the PMODE0 and PMODE1 pins)

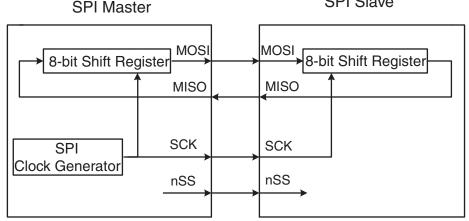

In the slave programming mode, an external system (that is, the Host), operating as SPI master, can transfer the program image in a raw format to the program memory of the device. In this case, the AT76C713 operates as an SPI slave and starts running from the internal boot ROM code, which switches to the start of program memory when it detects the end of a valid program transfer from the Host to the AT76C713

In the master programming mode, the AT76C713 reads the whole program image from an external serial EEPROM or DataFlash<sup>®</sup> and switches to the start of the program memory when it completes this reading. Alternatively, the AT76C713 reads only configuration parameters from a small serial non-volatile memory (EEPROM or DataFlash), enables the USB Controller, and executes the USB Device Firmware Upgrade (DFU) code that is stored in the boot ROM

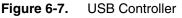

The USB Controller consists of a Serial Interface Engine (SIE), a Function Interface Unit (FIU), and a System Interface (SI). The SIE performs bit processing, line coding, packet generation, packet type recognition, serial-parallel data conversion, and packet delineation. The FIU consists of a protocol engine and a USB device with one Control Endpoint (EP0) and four programmable Endpoints with up to 512 bytes maximum total size. All Endpoints support double buffering in order to provide the maximum performance specified for the USB

The AT76C713 supports two 16550 UART modules with 16 bytes FIFOs in each direction. The UART0 serial interface provides full modem control functionality with the RTS/CTS, DTR/DSR, RI, and CD signals. These signals are provided by the general-purpose I/O pins of PORTD

The AT76C713 AVR is supported with a full suite of program and system development tools, including: C compiler, macro assemblers, program debugger/simulators, in-circuit emulators, and evaluation kits

# 2. AT76C713 Functional Diagram

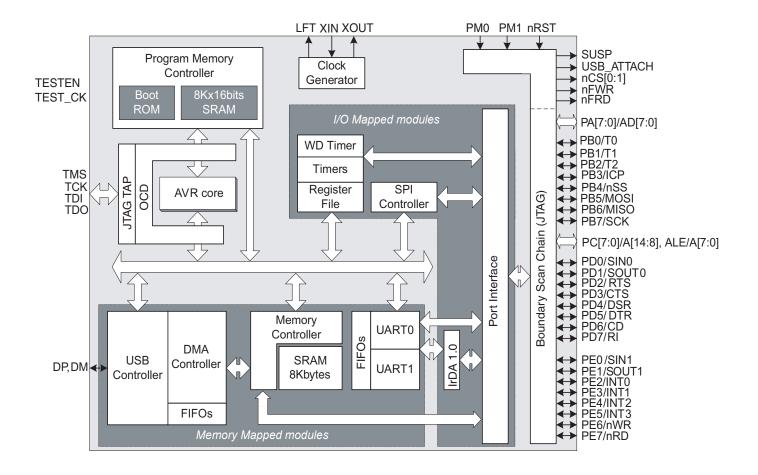

# 3. Pin Diagram

# 3.1 100-pin TQFP Package

4

# 4. Pin Summary – Pin Assignment

Table 4-1.

Pin Summary – Pin Assignment

| Table 4-1. | Fill Summary – Fill |

|------------|---------------------|

| Pin #      | Pin Name            |

| 1          | N/C                 |

| 2          | N/C                 |

| 3          | PGND                |

| 4          | nRST                |

| 5          | CVDD                |

| 6          | PE7/nRD             |

| 7          | PE6/nWR             |

| 8          | PE5/nINT3           |

| 9          | PE4/nINT2           |

| 10         | PE3/nINT1           |

| 11         | PE2/nINT0           |

| 12         | PE1/SOUT1           |

| 13         | PE0/SIN1            |

| 14         | PVDD                |

| 15         | PMODE0              |

| 16         | PMODE1              |

| 17         | CGND                |

| 18         | PGND                |

| 19         | LFT                 |

| 20         | PAGND               |

| 21         | XIN                 |

| 22         | XOUT                |

| 23         | PAVDD               |

| 24         | N/C                 |

| 25         | PAVDD               |

| 26         | PAGND               |

| 27         | VEXT                |

| 28         | POR_VSEL            |

| 29         | PVDD                |

| 30         | PC7/ALE             |

| 31         | PC6/A14             |

| 32         | PC5/A13             |

| 33         | CGND                |

| 34         | PC4/A12             |

|            |                     |

| Pin # | Pin Name   |

|-------|------------|

| 35    | PC3/A11    |

| 36    | PC2/A10    |

| 37    | PC1/A9     |

| 38    | PC0/A8     |

| 39    | CVDD       |

| 40    | PB7/SCK    |

| 41    | PB6/MISO   |

| 42    | PB5/MOSI   |

| 43    | PB4/nSS    |

| 44    | PB3/ICP    |

| 45    | PB2/T2     |

| 46    | PVDD       |

| 47    | PGND       |

| 48    | N/C        |

| 49    | N/C        |

| 50    | PVDD       |

| 51    | PGND       |

| 52    | N/C        |

| 53    | PVDD_PORTD |

| 54    | PD7/RI     |

| 55    | PD6/CD     |

| 56    | PD5/DTR    |

| 57    | PD4/DSR    |

| 58    | PD3/CTS    |

| 59    | PD2/RTS    |

| 60    | PD1/SOUT0  |

| 61    | PD0/SIN0   |

| 62    | CVDD       |

| 63    | PGND       |

| 64    | CGND       |

| 65    | SUSP       |

| 66    | DP         |

| 67    | DM         |

| 68    | PVDD_USB   |

| Pin # | Pin Name   |

|-------|------------|

| 69    | PA7        |

| 70    | PA6        |

| 71    | PA5        |

| 72    | PA4        |

| 73    | PA3        |

| 74    | N/C        |

| 75    | PVDD       |

| 76    | PGND       |

| 77    | N/C        |

| 78    | PGND       |

| 79    | PVDD       |

| 80    | USB_ATTACH |

| 81    | ТСК        |

| 82    | TMS        |

| 83    | TDI        |

| 84    | TDO        |

| 85    | CGND       |

| 86    | nCS1       |

| 87    | nCS0       |

| 88    | nFWR       |

| 89    | nFRD       |

| 90    | CVDD       |

| 91    | PA2        |

| 92    | PA1        |

| 93    | PA0        |

| 94    | PB1/T1     |

| 95    | PB0/T0     |

| 96    | TEST_EN    |

| 97    | TEST_CLK   |

| 98    | PVDD       |

| 99    | N/C        |

| 100   | N/C        |

# 5. Signal Description

# Table 5-1. Signal Description

Type: I = Input, O = Output, I/O = Bi-directional, A = Analog Signal

| Name         | Туре | Description                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JTAG Signals |      |                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| ТСК          | I    | JTAG clock input                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| TDI          | Ι    | Scan chain bitstream input                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| TDO          | 0    | Scan chain bitstream output                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| TMS          | Ι    | JTAG mode select input                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Port Signals |      |                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| PA[0:7]      | В    | If the alternative function of the p<br>internal pull-up resistors. Port A                                                                                                                                                                                                 | with external memory, where it acts as the AD0-7 address and/or data bus<br>port is not used, Port A also serves as an 8-bit bi-directional I/O port with<br>putput buffers can sink 20 mA and can drive the LED displays directly. Por<br>low will source current. The Port A pins are inputs when a reset condition<br>< is not running.                                                                                                                                                                                          |

|              |      | from the three internal timers as<br>direction of the PB[3-0] pins.<br>Port B serves also as an 8-bit bi<br>functions of the port are not used<br>directly. As inputs, Port B pins the<br>when a reset condition becomes<br>The alternative functions of Port<br>sections. | <ul> <li>4]) offers the signals for the SPI interface. The low-nibble (PB[3-0]) is used trigger and capture inputs. These functions can operate regardless the -directional I/O port with internal pull-up resistors, if the alternative d. The Port B output buffers can sink 20 mA and can drive LED displays at are externally pulled low will source current. The Port B pins are inputs active, even if the clock is not running.</li> <li>B are explained in more details at the following table and at the proper</li> </ul> |

| PB[0:7]      | В    | Port                                                                                                                                                                                                                                                                       | ctions of Port B Alternate Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| FD[0.7]      | Б    | PB0                                                                                                                                                                                                                                                                        | T0: Timer/Counter 0 clock input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|              |      | PB1                                                                                                                                                                                                                                                                        | T1: Timer/Counter 1 clock input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|              |      | PB2                                                                                                                                                                                                                                                                        | T2: Timer/Counter 2 clock input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|              |      | PB3                                                                                                                                                                                                                                                                        | ICP1: Input Capture Pin for Timer/Counter1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|              |      | PB4                                                                                                                                                                                                                                                                        | nSS: SPI slave port select input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|              |      | PB5                                                                                                                                                                                                                                                                        | MOSI: SPI slave port select input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|              |      | PB6                                                                                                                                                                                                                                                                        | MISO: SPI master data in, slave data out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|              |      | PB7                                                                                                                                                                                                                                                                        | SCK: SPI master clock out, slave clock in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| PC[0:7]      | В    | ALE in a multiplexed address mo<br>If the alternative functions of the<br>with internal pull-up resistors.Th                                                                                                                                                               | with external memory, where it acts as the address bus bits A8-15 and<br>ode and A0-7 in a non-multiplexed mode.<br>port are not used, Port C also serves as an 8-bit bi-directional I/O port<br>e Port C output buffers can sink 20 mA and can drive the LED displays<br>ernally pulled low will source current. The Port C pins are inputs when a<br>even if the clock is not running.                                                                                                                                            |

6

# **Table 5-1.**Signal Description (Continued)

## Type: I = Input, O = Output, I/O = Bi-directional, A = Analog Signal

| Name    | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                           |

|---------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|

|         |      | Port D offers the data and handshaking signals for UART0 interface, as listed below.<br>When the UART0 is not used, PORT D is also an 8-bit bi-directional I/O port with internal pull-up resistors.<br>The Port D output buffers can sink 20 mA. Port D pins that are externally pulled low will source current.<br>The Port D pins are inputs when a reset condition becomes active, even if the clock is not running. |                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                           |

|         |      | <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                 | Alternativ                                                                                                                              | ve Functions of Port D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                           |

|         |      |                                                                                                                                                                                                                                                                                                                                                                                                                          | Port                                                                                                                                    | Alternate Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                           |

|         |      |                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                         | SIN0, Serial In UART0 (I): This pin provides the serial receive data input to UART0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                           |

| PD[0:7] | В    |                                                                                                                                                                                                                                                                                                                                                                                                                          | PD1                                                                                                                                     | SOUT0, Serial Out UART0 (O): This pin provides the serial transmit data from the UART0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                           |

|         |      |                                                                                                                                                                                                                                                                                                                                                                                                                          | PD2                                                                                                                                     | nRTS, Ready To Send (B): RTS UART0 handshaking signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                           |

|         |      |                                                                                                                                                                                                                                                                                                                                                                                                                          | PD3                                                                                                                                     | nCTS, Clear To Send (B): CTS UART0 handshaking signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                           |

|         |      |                                                                                                                                                                                                                                                                                                                                                                                                                          | PD4                                                                                                                                     | nDSR, Data Set Ready (B): DSR UART0 handshaking signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                           |

|         |      |                                                                                                                                                                                                                                                                                                                                                                                                                          | PD5                                                                                                                                     | nDTR, Data Terminal Ready (B): DTR UART0 handshaking signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                           |

|         |      |                                                                                                                                                                                                                                                                                                                                                                                                                          | PD6                                                                                                                                     | nCD, Carrier Detect (B): CD UART0 handshaking signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                           |

|         |      |                                                                                                                                                                                                                                                                                                                                                                                                                          | PD7                                                                                                                                     | nRI, Ring Indicator (B): RI UART0 handshaking signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                           |

|         |      | Bort E offere th                                                                                                                                                                                                                                                                                                                                                                                                         | ha data a                                                                                                                               | ignals for the UADT1 interface, offers 4 outernal interrupt lines (adds                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | triagorod or                                              |

|         |      | level sensitive<br>If the alternativ<br>up/down resist<br>The output but<br>PE2 and PE3<br>even if the close                                                                                                                                                                                                                                                                                                             | external<br>ve functic<br>tors. Pins<br>ffers of P<br>pins) will<br>ck is not                                                           | ignals for the UART1 interface, offers 4 external interrupt lines (edge<br>interrupt) and the nWR/nRD signals for configurations with external n<br>ons are not used, PORT E serves as an 8-bit bi-directional I/O port with<br>s PE2 and PE3 have pull-down resistors while the rest pins have pull-<br>ort E pads can sink 20 mA. Port E pins that are externally pulled low<br>source current. The Port E pins are inputs when a reset condition bed<br>running.                                                                                                                                                                                                                                                                                                                | nemory.<br>h internal pu<br>up resistors.<br>(or high for |

|         |      | level sensitive<br>If the alternativ<br>up/down resist<br>The output but<br>PE2 and PE3<br>even if the close                                                                                                                                                                                                                                                                                                             | external<br>ve functic<br>tors. Pins<br>ffers of P<br>pins) will<br>ck is not                                                           | interrupt) and the nWR/nRD signals for configurations with external nons are not used, PORT E serves as an 8-bit bi-directional I/O port with PE2 and PE3 have pull-down resistors while the rest pins have pull-<br>ort E pads can sink 20 mA. Port E pins that are externally pulled low source current. The Port E pins are inputs when a reset condition bec<br>running.                                                                                                                                                                                                                                                                                                                                                                                                       | nemory.<br>h internal pu<br>up resistors.<br>(or high for |

| PE[0:7] | В    | level sensitive<br>If the alternativ<br>up/down resist<br>The output but<br>PE2 and PE3<br>even if the close                                                                                                                                                                                                                                                                                                             | external<br>ve functic<br>tors. Pins<br>ffers of P<br>pins) will<br>ck is not                                                           | interrupt) and the nWR/nRD signals for configurations with external nons are not used, PORT E serves as an 8-bit bi-directional I/O port with E PE2 and PE3 have pull-down resistors while the rest pins have pull-<br>ort E pads can sink 20 mA. Port E pins that are externally pulled low a source current. The Port E pins are inputs when a reset condition becarunning.                                                                                                                                                                                                                                                                                                                                                                                                      | nemory.<br>h internal pu<br>up resistors.<br>(or high for |

| PE[0:7] | В    | level sensitive<br>If the alternativ<br>up/down resist<br>The output but<br>PE2 and PE3<br>even if the close                                                                                                                                                                                                                                                                                                             | external<br>ve functic<br>tors. Pins<br>ffers of P<br>pins) will<br>ck is not<br>Alternativ<br>Port                                     | interrupt) and the nWR/nRD signals for configurations with external mons are not used, PORT E serves as an 8-bit bi-directional I/O port with PE2 and PE3 have pull-down resistors while the rest pins have pull-<br>ort E pads can sink 20 mA. Port E pins that are externally pulled low a source current. The Port E pins are inputs when a reset condition bed running.                                                                                                                                                                                                                                                                                                                                                                                                        | nemory.<br>h internal pu<br>up resistors.<br>(or high for |

| PE[0:7] | В    | level sensitive<br>If the alternativ<br>up/down resist<br>The output but<br>PE2 and PE3<br>even if the close                                                                                                                                                                                                                                                                                                             | external<br>ve functic<br>tors. Pins<br>ffers of P<br>pins) will<br>ck is not<br>Alternativ<br>Port<br>PE0                              | interrupt) and the nWR/nRD signals for configurations with external mons are not used, PORT E serves as an 8-bit bi-directional I/O port with PE2 and PE3 have pull-down resistors while the rest pins have pull-ort E pads can sink 20 mA. Port E pins that are externally pulled low source current. The Port E pins are inputs when a reset condition bed running.         //e Functions of Port E         Alternate Function         SIN1, Serial In UART1 (I): This pin provides the serial receive data input to UART1.         SOUT1, Serial Out UART1 (O): This pin provides the serial                                                                                                                                                                                    | nemory.<br>h internal pu<br>up resistors.<br>(or high for |

| PE[0:7] | В    | level sensitive<br>If the alternativ<br>up/down resist<br>The output but<br>PE2 and PE3<br>even if the close                                                                                                                                                                                                                                                                                                             | external<br>ve functic<br>tors. Pins<br>ffers of P<br>pins) will<br>ck is not<br>Alternativ<br>Port<br>PE0<br>PE1                       | interrupt) and the nWR/nRD signals for configurations with external nons are not used, PORT E serves as an 8-bit bi-directional I/O port with a PE2 and PE3 have pull-down resistors while the rest pins have pull-ort E pads can sink 20 mA. Port E pins that are externally pulled low a source current. The Port E pins are inputs when a reset condition becarunning.         ve Functions of Port E         Alternate Function         SIN1, Serial In UART1 (I): This pin provides the serial receive data input to UART1.         SOUT1, Serial Out UART1 (O): This pin provides the serial transmit data from the UART1                                                                                                                                                    | nemory.<br>h internal pu<br>up resistors.<br>(or high for |

| PE[0:7] | В    | level sensitive<br>If the alternativ<br>up/down resist<br>The output but<br>PE2 and PE3<br>even if the close                                                                                                                                                                                                                                                                                                             | external<br>ve function<br>tors. Pins<br>ffers of Pi<br>pins) will<br>ck is not<br>Alternativ<br>Port<br>PE0<br>PE1<br>PE2              | interrupt) and the nWR/nRD signals for configurations with external mons are not used, PORT E serves as an 8-bit bi-directional I/O port with SPE2 and PE3 have pull-down resistors while the rest pins have pull-ort E pads can sink 20 mA. Port E pins that are externally pulled low isource current. The Port E pins are inputs when a reset condition bedrunning.         ve Functions of Port E         Alternate Function         SIN1, Serial In UART1 (I): This pin provides the serial receive data input to UART1.         SOUT1, Serial Out UART1 (O): This pin provides the serial transmit data from the UART1         INT0, edge-triggered or level sensitive interrupt with pull-down                                                                              | nemory.<br>h internal pu<br>up resistors<br>(or high for  |

| PE[0:7] | В    | level sensitive<br>If the alternativ<br>up/down resist<br>The output but<br>PE2 and PE3<br>even if the close                                                                                                                                                                                                                                                                                                             | external<br>ve function<br>tors. Pins<br>ffers of Pi<br>pins) will<br>ck is not<br>Alternativ<br>Port<br>PE0<br>PE1<br>PE2<br>PE3       | interrupt) and the nWR/nRD signals for configurations with external mons are not used, PORT E serves as an 8-bit bi-directional I/O port with PE2 and PE3 have pull-down resistors while the rest pins have pull-ort E pads can sink 20 mA. Port E pins that are externally pulled low source current. The Port E pins are inputs when a reset condition bed running.         //e Functions of Port E         Alternate Function         SIN1, Serial In UART1 (I): This pin provides the serial receive data input to UART1.         SOUT1, Serial Out UART1 (O): This pin provides the serial transmit data from the UART1         INT0, edge-triggered or level sensitive interrupt with pull-down         INT1, edge-triggered or level sensitive interrupt with pull-down     | nemory.<br>h internal pu<br>up resistors<br>(or high for  |

| PE[0:7] | В    | level sensitive<br>If the alternativ<br>up/down resist<br>The output but<br>PE2 and PE3<br>even if the close                                                                                                                                                                                                                                                                                                             | external<br>ve function<br>tors. Pins<br>ffers of P<br>pins) will<br>ck is not<br>Alternativ<br>Port<br>PE0<br>PE1<br>PE2<br>PE3<br>PE4 | interrupt) and the nWR/nRD signals for configurations with external monstare not used, PORT E serves as an 8-bit bi-directional I/O port with serves and PE3 have pull-down resistors while the rest pins have pull-ort E pads can sink 20 mA. Port E pins that are externally pulled low is source current. The Port E pins are inputs when a reset condition bedrunning.         ve Functions of Port E         Alternate Function         SIN1, Serial In UART1 (I): This pin provides the serial receive data input to UART1.         SOUT1, Serial Out UART1 (O): This pin provides the serial transmit data from the UART1         INT0, edge-triggered or level sensitive interrupt with pull-down         INT1, edge-triggered or level sensitive interrupt with pull-down | nemory.<br>h internal pu<br>up resistors<br>(or high for  |

# Table 5-1. Signal Description (Continued)

Type: I = Input, O = Output, I/O = Bi-directional, A = Analog Signal

| Name             | Туре      | Description                                                                                                                                                         |

|------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| USB Serial Inte  | rface     |                                                                                                                                                                     |

| DP               | I/O       | USB data I/O (positive differential line). DP and DM form the differential signal pin pair connected to the Host Controller or an upstream Hub.                     |

| DM               | I/O       | USB data I/O (negative differential line)                                                                                                                           |

| USB_ATTACH       | 0         | This output controls the pullup resistor of the DP signal. When low, it enforces the host to re-enumerate the device.                                               |

| Programming M    | /lode Con | trol Signals                                                                                                                                                        |

| PMODE0<br>PMODE1 | I         | PMODE0 and PMODE1 pins are used from the on-chip bootstrap code and define the programming mode. For more details refer to the Program Modes section.               |

| Test Signals     |           |                                                                                                                                                                     |

| TEST_EN          | I         | General-purpose signal for test. Tied to V <sub>SS</sub> in normal conditions.                                                                                      |

| TEST_CLK         | I         | Used only for production setting. Tied to V <sub>SS</sub> in normal conditions.                                                                                     |

| POR_VSEL         | I         | Used in production phase only. Tied to V <sub>SS</sub> in normal conditions.                                                                                        |

| VEXT             | I         | Used in production phase only. Tied to 1.8V in normal conditions.                                                                                                   |

| Other Signals    |           |                                                                                                                                                                     |

| nRST             | I         | Reset input. A low on this pin for two clock cycles while the oscillator is running resets the device. Note that there is no internal pull-up resistor on this pin. |

| SUSP             | 0         | Indicates if the IC is in power down mode                                                                                                                           |

| nCS0             | 0         | External Memory Chip Select 0                                                                                                                                       |

| nCS1             | 0         | External Memory Chip Select 1                                                                                                                                       |

| nFWR             | 0         | External FIFO Write                                                                                                                                                 |

| nFRD             | 0         | External FIFO Readl                                                                                                                                                 |

| XIN              | I         | System clock oscillator pad, input to the inverting oscillator amplifier and input to the internal system clock operating circuit.                                  |

| XOUT             | 0         | System clock oscillator pad, output from the inverting oscillator amplifier.                                                                                        |

| LFT              | Α         | An external RC filter should be connected to this pin to stabilize the lock-in time of the internal PLL for the master clock input XIN.Main PLL LFT input           |

| Power Supply p   | oins      |                                                                                                                                                                     |

| CGND             | Power     | 0 Volts supply to the core                                                                                                                                          |

| CVDD             | Power     | 1.8 Volts supply to the core                                                                                                                                        |

| PGND             | Power     | 0 Volts supply to the external section of the I/O circuitry                                                                                                         |

| PVDD             | Power     | 1.8V or 3.3 Volts supply to the external section of the I/O circuitry                                                                                               |

| PVDD_PortD       | Power     | 1.8V or 3.3 Volts supply to the external section of the Port D I/O circuitry                                                                                        |

| PVDD_USB         | Power     | 3.3 Volts supply for the USB and SUSPEND pins                                                                                                                       |

| PAGND            | Power     | 0 Volts Analog supply to the core, AC and DC sections of the I/O circuitry                                                                                          |

| PAVDD            | Power     | 1.8 Volts Analog supply to the core, AC and DC sections of the I/O circuitry                                                                                        |

8

# 6. Functional Description

## 6.1 Bootstrap ROM and Programming Modes

The bootstrap code in the boot ROM of the AT76C713 is always activated on power-up or after a system reset. The functionality of the bootstrap code is configured by pins PMODE0 and PMODE1. In the SPI master programming modes, the AT76C713 is master over the SPI interface and can support an external EEPROM or DataFlash. The SPI slave programming mode is useful in a system where an external host is present and keeps the image code for the AT76C713 in its own memory.

Table 6-1. Programming Modes

| PMODE0 | PMODE1 | Programming Mode                           |  |

|--------|--------|--------------------------------------------|--|

| 0      | 0      | USB DFU only (SPI disabled)                |  |

| 0      | 1      | SPI Slave: SPI master host must be present |  |

| 1      | 0      | SPI Master: SPI serial EEPROM is assumed   |  |

| 1      | 1      | SPI Master: SPI DataFlash is assumed       |  |

### 6.1.1 USB DFU-only Mode

When both the PMODE0 and PMODE1 pins are tied low, the bootstrap code will not enable the USB controller but not the SPI controller. The system will wait for a USB DFU sequence using the default USB descriptors stored in the boot ROM.

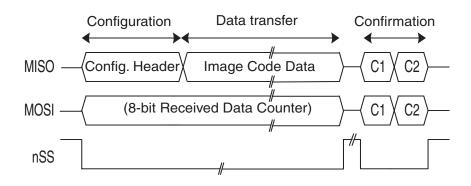

### 6.1.2 Slave Programming Mode

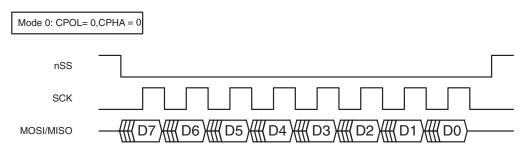

When the PMODE0 pin is tied low and the PMODE1 pin is tied high, the bootstrap ROM configures the SPI as a slave and waits for a specific sequence of data through the SPI. The sequence is as follows

- 1. The nSS pin is enabled.

- 2. The Configuration Header (256 bytes) is transmitted.

- 3. Image of the code to be stored in program memory is transmitted, starting from address 0. (The code size is determined in the Configuration Header.)

- 4. The nSS pin is disabled and re-enabled.

- 5. Confirmation byte 1 is transmitted.

- 6. Confirmation byte 2 is transmitted.

- 7. The nSS pin is disabled

#### Figure 6-1. Slave Programming Mode Sequence

During the transmission of the configuration data and code image, the AT76C713 returns an 8bit counter value that counts the received bytes. Thus, the Host can verify if the AT76C713 has received the correct amount of data.

During the first confirmation cycle, the SPI master sends \$CA to command "Continue Analyzing" or \$AB to command "Abort". The SPI slave will return "Data was OK" by sending \$D0 or "Error" by sending \$EE.

During the second confirmation cycle, the SPI master data is ignored and the SPI slave sends the positive acknowledgment \$AD "Analyzing Data", or one of the following error messages: \$DD "Discarding data", \$DE "Discarding due to transmission error", or \$EE "Error in confirmation command".

| Ca      | Case   |      | 2    | 3    | 4       |

|---------|--------|------|------|------|---------|

|         | Master | \$CA | \$AB | хх   | Invalid |

| Cycle 1 | Slave  | \$D0 | \$D0 | \$EE | xx      |

| Cuala 0 | Master | xx   | xx   | хх   | хх      |

| Cycle 2 | Slave  | \$AD | \$DD | \$DE | \$EE    |

| Progra  | mming  | ОК   | Fail | Fail | Fail    |

Table 6-2.

Possible Cases of Programming during the Slave Program Mode

If the slave programming sequence fails, then the AT76C713 will enable the USB controller waiting for the DFU sequence, using the default USB descriptors.

### 6.1.3 Master Programming Modes

When the PMODE0 pin is tied high, the bootstrap ROM configures the SPI as a master and is prepared to communicate either with a serial EEPROM if PMODE1 is tied low, or with a DataFlash if PMODE1 is tied high. The AT76C713 supports any Atmel EEPROM of the AT25xxx type (for example, AT25040) and Dataflash of the AT45xxx type.

The first 256 bytes that are read by the EEPROM or DataFlash are known as the configuration header, which contains useful information for the rest of the downloading procedure.

The bytes fetched from the external serial memory may be an image code or configuration parameters. If the bytes are an image code, after data fetching is complete the program running in the boot ROM resets the AVR program counter and switches to the SRAM program memory by setting the remap bit in the memory access interface.

If the data fetched from the external serial memory is configuration parameters only, the bootstrap code of the boot ROM will not switch to the program memory at the end of data fetching. Instead, it will enable the USB controller. The USB will enumerate using the descriptors loaded from the SPI memory. Upon enumeration completion, if a DFU application is enabled in the host, then the bootstrap ROM will support program storing in the program memory through the USB. When program storing is complete, the device will switch to the program memory.

#### 6.1.4 **Configuration Header**

Table 6-3

The Configuration Header is at least 256 bytes length and consumes the first page of the SPI memory. For systems that use SPI slave programming or SPI EEPROM memory (for example, AT25128A), the Configuration Header length is fixed to 256 bytes. For systems that use SPI DataFlash, the page size is equal to the page size of the used DataFlash. For example, using the AT45DB011B, the page size is 264 bytes and thus, the Configuration Header will consume 264 bytes.

|      | Configuration neader |                          |  |

|------|----------------------|--------------------------|--|

| Byte | Description          |                          |  |

| 0    | \$55                 |                          |  |

| 1    | \$AA                 |                          |  |

| 2    | Size[7:0]            |                          |  |

| 3    | Size[15:8]           |                          |  |

| 4    | Control Byte         |                          |  |

| 5    | MEMMAP               |                          |  |

|      |                      | Device descriptor        |  |

| 6    | CIS[ ]               | Configuration descriptor |  |

| 0    |                      | Serial descriptor        |  |

|      |                      | Product descriptor       |  |

The meaning of each byte is described in Table 6-3. Configuration Header

The first 2 bytes must be \$55 and \$AA in order to detect the rest of the information as valid. If those bytes are invalid, then the bootstrap code rejects the operation immediately and starts the USB DFU procedures.

**Size[15:0]** is the length of the image code counted in pages. During the slave programming mode and the SPI EEPROM master programming mode, each page is 256 bytes long.

The control bitmap (or control byte) is described in Table 6-4.

| Control Bitmap |

|----------------|

|                |

|     | Control Byte |                                                                                                                       |  |

|-----|--------------|-----------------------------------------------------------------------------------------------------------------------|--|

| Bit | Field        | Description                                                                                                           |  |

| 7   | WSOF         | Wait USB SOF.                                                                                                         |  |

| 6   |              | Reserved to zero ('0').                                                                                               |  |

| 5   | PLCK         | If set, then don't use the PLL Lock signal (see also the PLCK bit of "Clock Control Register (CLK_CNTR)" on page 51). |  |

#### Table 6-4. Control Bitmap

| Control Byte |         |                                                                                               |

|--------------|---------|-----------------------------------------------------------------------------------------------|

| Bit          | Field   | Description                                                                                   |

| 4            | REMAP   | If set, then remap right after the downloading of the image code is successful.               |

| 3            | STDBY   | If set, use for sleep state in suspend mode the stand-by mode instead of power-<br>down mode. |

| 2            | INTPROT | Interrupt Protect.                                                                            |

| 1            | DTCH    | Detach Enable: If set, detach before remap.                                                   |

| 0            | SUSP    | If set the Suspend Circuit is on.                                                             |

Note: Bits 7, 3, 2, 1 and 0 affect only the bootstrap USB DFU process

**MEMMAP** byte will be assigned immediately to the MEMMAP register (see MEMMAP description in the "Memory Access Interface" on page 15). This register configures the size of the program memory and data memory.

**CIS[**] is a table that carries the USB descriptors. Each descriptor starts right after the end of the previous one. The order is shown in Table 6-3. The remaining bytes from the end of the CIS[] table up to the end of the page have no meaning.

Note: If the Remap bit of the control byte is cleared, then the image code will be loaded into the AT76C713 program memory (see Size[15:0]), the system will not remap, and the bootstrap code will enable the USB core and enumerate using the new USB descriptors (CIS[]) instead of the default USB descriptors.

### 6.2 AVR Core

The AT76C713 chip is based on the AVR core architecture. All peripherals, apart from SPI, IrDA, and timers, are memory mapped to the data address space.

#### 6.2.1 Interrupt Handling

The interrupt vector table of the AT76C713 is shown in Table 6-5.

| Vector<br>Number | Program<br>Address | Source       | Interrupt Definition           |

|------------------|--------------------|--------------|--------------------------------|

| 1                | \$0000             | RESET        | H/W Pin and Watchdog Reset     |

| 2                | \$0002             | SUSP_RESM    | USB Suspend and Resume         |

| 3                | \$0004             | USB          | USB H/W & USB DMA Interrupt    |

| 4                | \$0006             | INT0         | External Interrupt Request 0   |

| 5                | \$0008             | INT1         | External Interrupt Request 1   |

| 6                | \$000A             | INT2         | External Interrupt Request 2   |

| 7                | \$000C             | INT3         | External Interrupt Request 3   |

| 8                | \$000E             | TIMER2_OVF   | Timer/Counter2 Overflow        |

| 9                | \$0010             | TIMER1_CAPT  | Timer/Counter1 Capture Event   |

| 10               | \$0012             | TIMER1_COMPA | Timer/Counter1 Compare Match A |

| 11               | \$0014             | TIMER1_COMPB | Timer/Counter1 Compare Match B |

Table 6-5.

Interrupt Vector Table of the AT76C713

| Vector<br>Number | Program<br>Address | Source     | Interrupt Definition         |

|------------------|--------------------|------------|------------------------------|

| 12               | \$0016             | TIMER1_OVF | Timer/Counter1 Overflow      |

| 13               | \$0018             | TIMER0_OVF | Timer/Counter0 Overflow      |

| 14               | \$001A             | SPI_STC    | SPI Serial Transfer Complete |

| 15               | \$001C             | UART0_IRQ  | UART0 Interrupt Request      |

| 16               | \$001E             | UART1_IRQ  | UART1 Interrupt Request      |

**Table 6-5.**Interrupt Vector Table of the AT76C713

Note: The program memory word length is 16-bits wide.

## 6.3 Oscillator and Clock Generator

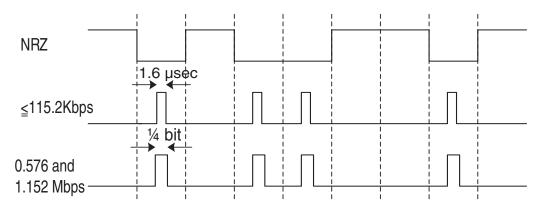

The AT76C713 clock generation circuit is based on a single clock input from an external 12 MHz crystal connected to the oscillator pad. All internal clocks are generated by multiplying this clock input incorporating an on-chip PLL. The output of the PLL can be configured in 96 MHz (default) or 192 MHz. In order to produce the desired clocks, the clock generator circuit divides the PLL output. Generating and then dividing a high frequency PLL output reduces the impact of jitter imported by the PLL.

An elaborate gobbling circuit produces a 14.769 MHz clock from the PLL output, which can support all standard baud rates with an acceptable frequency error.

### Figure 6-2. AT76C713 Clock Generation Tree

#### 6.3.1 PLL LFT Pin

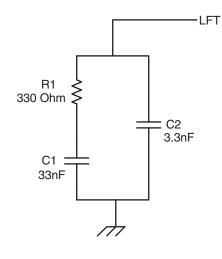

Figure 6-3 shows the circuit that must be attached to an LFT pin. The circuit consists of R1 =  $330 \Omega$ , C1 = 33nF, and C2 = 3.3nF.

# Figure 6-3. LFT Pin Circuit

# 6.4 Memory Map

| Base Address     | Module                                    | Description                  | n              |

|------------------|-------------------------------------------|------------------------------|----------------|

| \$FF00           | Program Memory Controller                 |                              |                |

| \$F800           | Memory Access Interface                   |                              |                |

| \$F300           | UART1                                     | Memory Mapp                  | ed Peripherals |

| \$F200           | UART0                                     |                              |                |

| \$F000           | USB                                       |                              |                |

| \$F000<br>\$A000 |                                           |                              |                |

|                  | External Memory<br>(Application Specific) | External Da                  | ta Memory      |

| \$2000           |                                           |                              |                |

| <b>#1000</b>     | Internal SRAM Bank 6,7                    |                              |                |

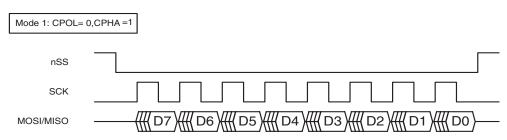

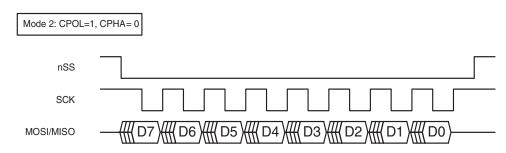

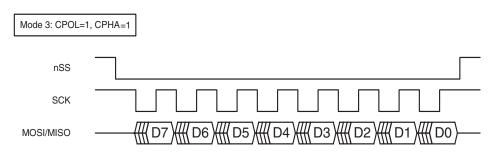

| \$1800           | Internal SRAM Bank 4,5                    |                              | Max. Internal  |