## **Features**

- Also known as SMCS116SpW

- Single Bidirectional SpaceWire link allowing

- Full duplex communication

- Transmit rate from 1.25 up to 200 Mbit/s in each direction

- Supports Serial Transfer Universal Protocol (STUP)

- · Derived from the T7906 Single Point to Point IEEE 1355 High Speed Controller

- Known anomalies of the T7906 chip corrected

- · Host interface

- Gives read/write accesses to the AT7912E configuration registers

- Gives read/write accesses to the SpaceWire channel

- ADC/ DAC interface

- Allows direct connection of an ADC with a width of up to 16 bits

- Allows direct connection of a DAC with up to 16 data lines and the required control signals

- FIFO interface

- RAM interface

- 16-bit data bus and 16-bit address bus

- Four chip selects to address 4 different memory partitions

- · Two independent UART interfaces

- 24 Bidirectional General Purpose I/Os

- Two 32-Bit Timers / Event Counters

- SpaceWire Link Performance

- At 3.3V: 100Mbit/s full duplex communication

- At 5V: 200Mbit/s full duplex communication

- Operating range

- Voltages

- 3V to 3.6V

- 4.5V to 5.5V

- Temperature

- - 55°C to +125°C

- Maximum Power consumption

- At 3.6V with a 5MHz clock: 150mW

- At 5.5V with a 5MHz clock: 700mW

- Radiation Performance

- Total dose tested successfully up to 50 Krad (Si)

- No single event latchup below a LET of 80 MeV/mg/cm2

- · ESD better than 2000V

- Quality Grades

- QML-Q or V with SMD

- · Package: 100pins MQFPF

- · Mass: 3grams

# Single SpaceWire link High Speed Controller

# **AT7912E**

#### 1. **Description**

The AT7912E provides an interface between a SpaceWire link according to the SpaceWire Standard ECSS-E-50-12A and several different interfaces.

The AT7912E was designed by EADS Astrium in Germany under the name 'SMCS116SpW" for "Scalable Multi-channel Communication Subsystem for SpaceWire". It is manufactured using the SEU hardened cell library from Atmel MG2RT CMOS 0.5µm radiation tolerant sea of gates technology.

For any technical question relative to the functionality of the AT7912E please contact Atmel technical support at assp-applab.hotline@nto.atmel.com.

This document should be read in conjunction with EADS Astrium 'SMCS116SpW User Manual'. This user manual is available at www.atmel.com.

A block diagram of the AT7912E is given in figure 1.

UART **GPIO JTAG** internal control data bus transmit / receive Link Interface ADC I/F address / command bus DAC Bus I/F Control F internal Controller RAM I/F FIFO I/F Host Interface internal control & data bus Bus Data system

Figure 1. AT7912E Block Diagram

util.

The AT7912E provides one SpaceWire serial communication link with up to 200 Mbit/s data transmit rate. It features a link disconnect detection and parity check at character

Timer

www.DataSheet4LL.com

level as well as an additional checksum generation/check at packet level. The AT7912E supports both the standard SpaceWire link protocol (transparent mode) and the STUP (Serial Transfer Universal Protocol) for efficient packet oriented data transfer.

In addition to the serial SpaceWire link, the AT7912E provides several different interfaces:

- · Host interface

- ADC interface

- · DAC interface

- · RAM interface

- FIFO interface

- General purpose I/O

- · UART interfaces

- Timers / Event Counters

- JTAG (IEEE 1149.1)

# 2. Pin Configuration

Table 1. Pin assignment

| Pin<br>Number | Name   | Pin<br>Number | Name  | Pin<br>Number | Name     | Pin<br>Number | Name      |

|---------------|--------|---------------|-------|---------------|----------|---------------|-----------|

| 1             | PLLOUT | 26            | IOB9  | 51            | DATA4    | 76            | TMR2_CLK  |

| 2             | GND    | 27            | VCC   | 52            | DATA5    | 77            | RxD1      |

| 3             | VCC    | 28            | GND   | 53            | DATA6    | 78            | TMR1_EXP  |

| 4             | VCC    | 29            | IOB10 | 54            | DATA7    | 79            | TMR2_EXP  |

| 5             | LDO    | 30            | IOB11 | 55            | DATA8    | 80            | TxD1      |

| 6             | LSO    | 31            | IOB12 | 56            | VCC      | 81            | HDATA0    |

| 7             | LDI    | 32            | IOB13 | 57            | GND      | 82            | HDATA1    |

| 8             | LSI    | 33            | IOB14 | 58            | DATA9    | 83            | HDATA2    |

| 9             | GND    | 34            | IOB15 | 59            | DATA10   | 84            | HDATA3    |

| 10            | TCK    | 35            | IOB16 | 60            | DATA11   | 85            | HDATA4    |

| 11            | TMS    | 36            | IOB17 | 61            | VCC      | 86            | HDATA5    |

| 12            | TDI    | 37            | IOB18 | 62            | GND      | 87            | HDATA6    |

| 13            | TRST*  | 38            | IOB19 | 63            | DATA12   | 88            | VCC       |

| 14            | TDO    | 39            | IOB20 | 64            | DATA13   | 89            | GND       |

| 15            | GND    | 40            | IOB21 | 65            | DATA14   | 90            | HDATA7    |

| 16            | VCC    | 41            | IOB22 | 66            | DATA15   | 91            | HDATNADR* |

| 17            | IOB0   | 42            | IOB23 | 67            | GPIO0    | 92            | HSEL*     |

| 18            | IOB1   | 43            | IOB24 | 68            | GPIO1    | 93            | HWRNRD    |

| 19            | IOB2   | 44            | IOB25 | 69            | GPIO2    | 94            | HINTR*    |

| 20            | IOB3   | 45            | IOB26 | 70            | GPIO3    | 95            | RESET*    |

| 21            | IOB4   | 46            | IOB27 | 71            | GPIO4    | 96            | CLK       |

| 22            | IOB5   | 47            | DATA0 | 72            | GPIO5    | 97            | VCC_3VOLT |

| 23            | IOB6   | 48            | DATA1 | 73            | GPIO6    | 98            | GND       |

| 24            | IOB7   | 49            | DATA2 | 74            | GPIO7    | 99            | GND       |

| 25            | IOB8   | 50            | DATA3 | 75            | TMR1_CLK | 100           | VCC       |

# Pin Description www.DataSheet4U.com 3.

Table 2. Pin description

|                               | 1                      | <del> </del>                                                                                                                                                                                                                                              |                          | İ                          | i         |

|-------------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|----------------------------|-----------|

| (1)(3)                        | - (2)(4)               |                                                                                                                                                                                                                                                           | 5V ± 0.5V<br>max. output | 3.3V ± 0.3V<br>max. output |           |

| Signal Name <sup>(1)(3)</sup> | Type <sup>(2)(4)</sup> | Function                                                                                                                                                                                                                                                  | current [mA]             | current [mA]               | load [pF] |

| HSEL*                         | I                      | When low, the external host selects the AT7912E host interface                                                                                                                                                                                            |                          |                            |           |

| HWRnRD                        | 1                      | Host interface write/read signal if HWRnRD is high during HSEL* low, the host writes data to the address register or to the AT7912E registers. if HWRnRD is low during HSEL* low, the host reads data from the address register or the AT7912E registers. |                          |                            |           |

| HDATnADR                      | ı                      | Host interface data/address signal if HDATnADR is high during read, the host reads/writes data from/to the internal AT7912E (data) registers. if HDATnADR is low during read, the host reads/writes address from/to the address register.                 |                          |                            |           |

| HDATA(7:0)                    | I/O/Z                  | AT7912E data bus.<br>HDATA(7:0) can be used as GPIO(2), if the Host interface is<br>disabled                                                                                                                                                              | 3                        | 1.5                        | 50        |

| HINTR*                        | 0                      | Host interrupt request line                                                                                                                                                                                                                               | 3                        | 1.5                        | 50        |

| TMR1_CLK                      | ı                      | Timer1 clock (max. 12.5 MHz)                                                                                                                                                                                                                              |                          |                            |           |

| TMR1_EXP                      | O                      | Timer1 expired. Asserted for one cycle if the value of counter1 is equal to the content of register TPERIOD1(3:0).                                                                                                                                        | 3                        | 1.5                        | 50        |

| TMR2_CLK                      | ı                      | Timer2 clock (max. 12.5 MHz)                                                                                                                                                                                                                              |                          |                            |           |

| TMR2_EXP                      | O                      | Timer2 expired. Asserted for one cycle if the value of counter2 is equal to the content of register TPERIOD2(3:0).                                                                                                                                        | 3                        | 1.5                        | 50        |

| RxD1                          | I                      | Receive data to UART1                                                                                                                                                                                                                                     |                          |                            |           |

| TxD1                          | 0                      | Transmit data from UART1                                                                                                                                                                                                                                  | 3                        | 1.5                        | 50        |

| LDI                           | ı                      | Link Data Input                                                                                                                                                                                                                                           |                          |                            |           |

| LSI                           | ı                      | Link Strobe Input                                                                                                                                                                                                                                         |                          |                            |           |

| LDO                           | 0                      | Link Data Output                                                                                                                                                                                                                                          | 12                       | 6                          | 25        |

| LSO                           | 0                      | Link Strobe Output                                                                                                                                                                                                                                        | 12                       | 6                          | 25        |

| DATA(15:0)                    | I/O/Z                  | Common AT7912E data bus                                                                                                                                                                                                                                   | 3                        | 1.5                        | 25        |

| GPIO(7:0)                     | I/O                    | General purpose input/output lines                                                                                                                                                                                                                        | 3                        | 1.5                        | 25        |

| IOB(21:0)                     | I/O                    |                                                                                                                                                                                                                                                           | 6                        | 3                          | 25        |

| IOB(24:22)<br>IOB27           | I/O                    | Control bus. The AT7912E controls the connected interface via these                                                                                                                                                                                       | 3                        | 1.5                        | 25        |

| IOB(26:25)                    | I                      | lines.                                                                                                                                                                                                                                                    |                          |                            |           |

|                               |                        |                                                                                                                                                                                                                                                           |                          |                            |           |

| TRST*                         | I                      | Test Reset. Resets the test state machine                                                                                                                                                                                                                 |                          |                            |           |

| тск                           | ı                      | Test Clock. Provides an asynchronous clock for JTAG boundary scan                                                                                                                                                                                         |                          |                            |           |

| www.DataShe | et4U.com<br>Type <sup>(2)(4)</sup> | Function                                                                                                                                                         | 5V ± 0.5V<br>max. output<br>current [mA] | 3.3V ± 0.3V<br>max. output<br>current [mA] | load [pF] |

|-------------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|--------------------------------------------|-----------|

| TMS         | I                                  | Test Mode Select. Used to control the test state machine. This input should be left unconnected or tied to ground during normal operation                        |                                          |                                            |           |

| TDI         | I                                  | Test Data Input. Provides serial data for the boundary scan logic                                                                                                |                                          |                                            |           |

| TDO         | O/Z                                | Test Data Output. Serial scan output of the boundary scan path                                                                                                   | 3                                        | 1.5                                        | 50        |

| RESET*      | ı                                  | AT7912E Reset.  Sets the AT7912E to a known state. This input must be asserted (low) at power-up. The minimum width of RESET low is 2 cycles when CLK is running |                                          |                                            |           |

| CLK         | I                                  | External clock input to AT7912E (max. 5 MHz)                                                                                                                     |                                          |                                            |           |

| PLLOUT      | 0                                  | Output of internal PLL. Used to connect a network of external RC filter devices.                                                                                 |                                          |                                            |           |

| VCC_3VOLT   | ı                                  | PLL Control signal Configure PLL for 3.3V or 5V operation VCC = 5 Volt: connect this signal with GND VCC = 3.3 Volt: connect this signal with VCC                |                                          |                                            |           |

| vcc         |                                    | Power Supply                                                                                                                                                     |                                          |                                            |           |

| GND         |                                    | Ground                                                                                                                                                           |                                          |                                            |           |

- Notes: 1. Groups of pins represent busses where the highest number is the MSB.

- 2. O = Output; I = Input; Z = High Impedance

- 3. (\*) = active low signal

- 4. O/Z = if using a configuration with two AT7912Es these signals can directly be connected together (WIROR)

# 3.1 Signals Organization

www.DataSheet4U.com

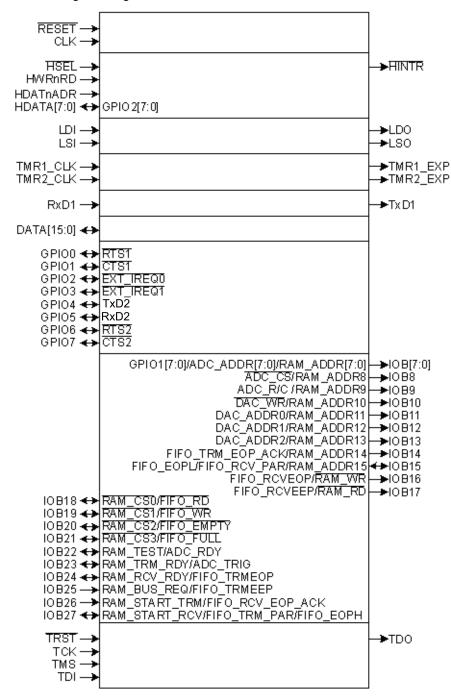

This section describes the signals of the AT7912E. Groups of signals represent buses where the highest number is the MSB.

Figure 3-1. Signals Organization

# 3.2 Shared I/O

www.DataSheet4LLcom

Some of the functions of the AT7912E share the same I/O pins. This means that some functions are mutually exclusive. As an example, the GPIO port shares some of its I/O pins with the host interface. If the host interface is not used, these pins are available for GPIO; otherwise they are used as the host address and data bus. The selection of which functions are being used is made by programming the appropriate registers after a chip reset.

A short overview of the signals allocation for the various functions is given in the table below.

Table 3-1.Shared I/Os description

|            | Functions  |     |                  |     |                           |     |                      |     |                      |     |

|------------|------------|-----|------------------|-----|---------------------------|-----|----------------------|-----|----------------------|-----|

| Signal     | GPIO       | I/O | RAM<br>Interface | I/O | FIFO<br>Interface         | I/O | DAC/ADC<br>Interface | I/O | UART &<br>Interrupts | I/O |

| HDATA[7:0] |            | 1/0 | interrace        | 1/0 | interrace                 | 1/0 | Interface            | 1/0 | interrupts           | 1/0 |

|            | GPIO2[7:0] |     |                  |     |                           |     |                      |     | DTO4*                | +   |

| GPIO0      | GPIO0_0    | I/O |                  |     |                           |     |                      |     | RTS1*                | 1   |

| GPIO1      | GPIO0_1    | I/O |                  |     |                           |     |                      |     | CTS1*                | ı   |

| GPIO2      | GPIO0_2    | I/O |                  |     |                           |     |                      |     | EXT_IRQ0*            | I   |

| GPIO3      | GPIO0_3    | I/O |                  |     |                           |     |                      |     | EXT_IRQ1*            | I   |

| GPIO4      | GPIO0_4    | I/O |                  |     |                           |     |                      |     | TxD2                 | 0   |

| GPIO5      | GPIO0_5    | I/O |                  |     |                           |     |                      |     | RxD2                 | 1   |

| GPIO6      | GPIO0_6    | I/O |                  |     |                           |     |                      |     | RTS2*                | 0   |

| GPIO7      | GPIO0_7    | I/O |                  |     |                           |     |                      |     | RTS2*                | I   |

| IOB[7:0]   | GPIO1[7:0] | I/O | RAM_ADDR[7:0]    | 0   |                           |     | ADC_ADDR[7:0]        | 0   |                      |     |

| IOB8       |            |     | RAM_ADDR8        | 0   |                           |     | ADC_CS*              | 0   |                      |     |

| IOB9       |            |     | RAM_ADDR9        | 0   |                           |     | ADC_R/C*             | 0   |                      |     |

| IOB10      |            |     | RAM_ADDR10       | 0   |                           |     | DAC_WR*              | 0   |                      |     |

| IOB11      |            |     | RAM_ADDR11       | 0   |                           |     | DAC_ADDR0            | 0   |                      |     |

| IOB12      |            |     | RAM_ADDR12       | 0   |                           |     | DAC_ADDR1            | 0   |                      |     |

| IOB13      |            |     | RAM_ADDR13       | 0   |                           |     | DAC_ADDR2            | 0   |                      |     |

| IOB14      |            |     | RAM_ADDR14       | 0   | FIFO_TRM_EOP_ACK          | 0   |                      |     |                      |     |

| IOB15      |            |     | RAM_ADDR15       | 0   | FIFO_RCV_PAR<br>FIFO_EOPL | I/O |                      |     |                      |     |

| IOB16      |            |     | RAM_WR*          | 0   | FIFO_RCVEOP               | 0   |                      |     |                      |     |

| IOB17      |            |     | RAM_RD*          | 0   | FIFO_RCVEEP               | 0   |                      |     |                      |     |

| IOB18      |            |     | RAM_CS0*         | 0   | FIFO_RD*                  | I/O |                      |     |                      |     |

| IOB19      |            |     | RAM_CS1*         | 0   | FIFO_WR*                  | I/O |                      |     |                      |     |

| IOB20      |            |     | RAM_CS2*         | 0   | FIFO_EMPTY*               | I/O |                      |     |                      |     |

| IOB21      |            |     | RAM_CS3*         | 0   | FIFO_FULL*                | I/O |                      |     |                      |     |

| www.DataS | heet/U.com | Functions |                  |     |                           |     |                      |     |                      |     |  |

|-----------|------------|-----------|------------------|-----|---------------------------|-----|----------------------|-----|----------------------|-----|--|

| Signal    | GPIO       | I/O       | RAM<br>Interface | I/O | FIFO<br>Interface         | I/O | DAC/ADC<br>Interface | I/O | UART &<br>Interrupts | I/O |  |

| IOB22     |            |           | RAM_TEST         | 0   |                           |     | ADC_RDY              | I   |                      |     |  |

| IOB23     |            |           | RAM_TMR_RDY      | 0   |                           |     | ADC_TRIG             | I   |                      |     |  |

| IOB24     |            |           | RAM_RCV_RDY      | 0   | FIFO_TRMEOP               | 1   |                      |     |                      |     |  |

| IOB25     |            |           | RAM_BUS_REQ*     | I   | FIFO_TRMEEP               | I   |                      |     |                      |     |  |

| IOB26     |            |           | RAM_START_TRM    | I   | FIFO_RCV_EOP_ACK          | I   |                      |     |                      |     |  |

| IOB27     |            |           | RAM_START_RCV    | I   | FIFO_TRM_PAR<br>FIFO_EOPH | I/O |                      |     |                      |     |  |

## 4. Interfaces

www.DataSheet4II.com

The AT7912E provides an interface between a SpaceWire link according to the SpaceWire Standard ECSS-E-50-12A and several different interfaces:

- · Host interface

- ADC/DAC interface

- RAM interface

- FIFO interface

- General purpose I/O

- UART interfaces

- Timers / Event Counters

## 4.1 Host Interface

Although the AT7912E is primarily designed to be remotely controlled, it can nevertheless be programmed and controlled by a local host if required. For that purpose the host interface provides 8 multiplexed data and address lines.

# 4.2 ADC/DAC interface

The ADC interface allows connecting an ADC with a width of up to 16 bits directly to the AT7912E. The AD conversion can be started by request via link or in a cyclic manner triggered by the on chip timers. When the AD conversion is ready, this is recognized by an external signal like "ready" or by an internal trigger, for example from the on chip timer. After reading the sample from the ADC it is then sent over the link. An 8-bit address generator is provided to allow multiplexing of analog signals. The address generator will start at a pre-programmed start address and will be incremented after each conversion.

The DAC interface is very similar to the ADC interface. It provides up to 16 data lines and the required control signals. The data to be sent to the DAC is received from the link and is stored in a register until the command "start DAC" is received. After that command the register values will be put to the DAC.

# 4.3 RAM Interface

The RAM interface provides a 16-bit data bus and 16-bit address bus. Four chip select lines allow addressing four different memory partitions (banks). This partitioning into different banks is done using 4 internal address boundary registers. These are 8 bit wide and provide a minimum page size of 1024 words. The memory interface can be programmed to use 0 to 7 wait states.

## 4.4 FIFO interface

www.DataSheet4U.com

The FIFO (8-bit or 16-bit data width) interface provides the control signals full, write, empty and read, depending on the direction of the data flow (receive/transmit).

Data received from the FIFO interface is sent over the SpaceWire link grouped in packets. The length of a packet (in bytes) can be specified either by setting an internal counter or by external signals. This interface can be programmed to use 0 to 7 wait states.

The FIFO interface handles two operating modes:

- An active mode where the AT7912E FIFO controller reads and writes from/to an external FIFO

- A passive mode where an external controller reads and writes from/to the AT7912E internal FIFO.

## 4.5 **GPIO** Interface

The general purpose I/O (GPIO Interface) provides up to 24 bidirectional signal lines. The direction (input or output) of each GPIO line can be set individually via register. Data to/from the GPIO lines is written / read via the GPIO data register. The GPIO provides 8 dedicated I/O lines, the remaining 16 lines of the port are shared with the ADC address and host data bus. These GPIO lines are available when the corresponding unit (e.g. the host data bus) of the AT7912E is not being used (disabled).

## 4.6 UART interface

Two independent UARTs are included in the AT7912E as well. One UART uses dedicated I/O lines whereas the second UART is sharing its pins with the GPIO port. The transmit rate of the UARTs in bps can be programmed via a 12-bit wide register with a maximum bit rate of about 780 kbit/s.

Each UART has a 4-byte FIFO in transmit, and a 4-byte FIFO in receive direction.

The UARTs can optionally use hardware handshake (rts/cts).

## 4.7 Timers / Event Counter

Two 32-bit on-chip timers are available on the AT7912E.

Each timer provides a 32-bit counter and a 32-bit reload register. The two timers can be operated independently or cascaded.

The timers can be used to set an external signal when the timeout value is reached. Each timer can generate periodic interrupts or only one interrupt, depending on configuration. An external output, TMR\_EXP, signals to other devices that the timer count has expired. An external input, TMR\_CLK, is provided which can be used as trigger source for the timer.

# 5. Operating Modes

www.DataSheet4LLcom

# 5.1 Configuration of the AT7912E

The AT7912E provides registers and ports for configuration. Each register contains exactly one byte (read / write), whereas a port (e.g. a FIFO interface) behaves like a FIFO, meaning that multiple data bytes can be read or written from/to the port.

The ports of the AT7912E such as the FIFO, UART, ADC and RAM interfaces are accessed by a read/write command to the corresponding port address. In the case of FIFO, Host, UART and memory interfaces, a packet oriented access is also possible (meaning transferring multiple data bytes with a single command). The read/write selection of a command is done by setting bit 7 (MSB) of the first byte to one (read) or zero (write).

All internal registers are 8-bit wide addressable. Two simple commands, read and write, suffice to access all registers of the AT7912E.

Configuration/Programming of the AT7912E internal registers is done via either a simple protocol over the SpaceWire link or STUP over the SpaceWire link or directly via the host interface.

- The simple protocol over the SpaceWire, compatible with the T7906 (SCMCS116) link requires a command byte and, if necessary, one or more data bytes. The simple protocol ignores following bytes, if more bytes are sent.

- The STUP over the SpaceWire link uses 4 bytes for commands. It also supports logical addressing.

- The host interface provides a direct access to the internal registers through a 8-bit multiplexed address/data bus. After reset, the host interface is enabled.

After a chip reset the AT7912E is configured via the internal controller. This can be either by receiving the configuration data from the SpaceWire link or by an external controller connected to the host port of the AT7912E.

# 6. Test Interface

www.DataSheet4U.com

## 6.1 JTAG

This represents the boundary scan testing provisions specified by IEEE Standard 1149.1 of the Joint Testing Action Group (JTAG). The AT7912E test access port and on-chip circuitry is fully compliant with the IEEE 1149.1 specification. The test access port enables boundary scan testing of circuitry connected to the AT7912E I/O pins.

# 7. AT7912E differences with the T7906E

A few differences between the AT7912E and the T7906E exist in the registers, the signals and the pinout. These differences are detailed in the section 15 of the 'SMCS116SpW User Manual".

# 8. Typical Applications

Many applications require a SpaceWire link front end, however, no controller is required on the unit. Thanks to its communication memory interface, the AT7912E satisfies the requirements of these applications. Due to its small package and low power consumption it is an excellent alternative to FPGA based solutions.

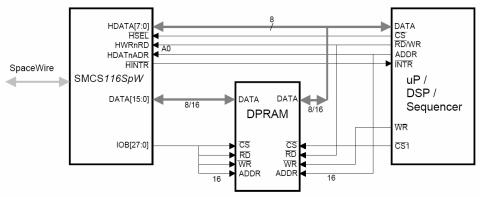

A system using the AT7912E as a communication front-end for a microcontroller is shown in the following figure:

Figure 8-1. Processor Interface

Additional application targets of the AT7912E are modules and units without any built-in communication features, such as special image compression chips, application specific programmable logic or mass memory. The AT7912E is perfectly suited to be used on "non intelligent" modules such as A/D converter or sensor interfaces, due to its "control by link" feature and system control facilities. In addition, its fault tolerance feature makes the device very interesting for many critical industrial measurement and control systems.

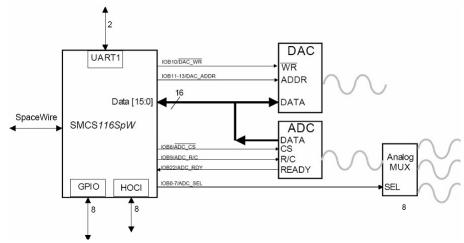

Example applications of the AT7912E as communication and system controller on an interface node consisting of an ADC and DAC is given in the figure below:

Figure 8-2. ADC/DAC Interface

# 9. PLL Filter

www.DataSheet4U.com

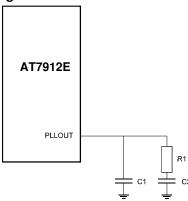

The AT7912E embeds a PLL to generate its internal clock reference. The PLLOUT pin of the PLL is the output of the AT7912E that allows connection of the external filter of the PLL. The following figure presents the connection of the PLL filter.

Figure 9-1. PLL filter

**Table 9-1.** PLL filter recommended components

| R1 | 1,5 kΩ ± 5%, ¼W |

|----|-----------------|

| C1 | 22pF, ± 5%      |

| C2 | 1.8nF, ± 5%     |

# 10. Power Supply

To achieve its fast cycle time, the AT7912E is designed with high speed drivers on output pins. Large peak currents may pass through a circuit board's ground and power lines, especially when many output drivers are simultaneously charging or discharging their load capacitances. These transient currents can cause disturbances on the power and ground lines. To minimize these effects, the AT7912E provides separate supply pins for its internal logic and for its external drivers.

All GND pins should have a low impedance path to ground. A ground plane is required in AT7912E systems to reduce this impedance, minimizing noise.

The VCC pins should be bypassed to the ground plane using 8 high-frequency capacitors (0.1  $\mu$ F ceramic). Keep each capacitor's lead and trace length to the pins as short as possible. This low inductive path provides the AT7912E with the peak currents required when its output drivers switch. The capacitors' ground leads should also be short and connect directly to the ground plane. This provides a low impedance return path for the load capacitance of the AT7912E output drivers.

The following pins must have a capacitor: 3, 4, 16, 27, 56, 61, 88 and 100.

# 11. Electrical Characteristics

www.DataSheet4U.com

# 11.1 Absolute Maximum Ratings

Table 11-1. Absolute Maximum Ratings

| Parameter                                | Symbol | Value             | Unit |

|------------------------------------------|--------|-------------------|------|

| Supply Voltage                           | VCC    | -0.5 to +7        | V    |

| I/O Voltage                              |        | -0.5 to VCC + 0.5 | V    |

| Operating Temperature<br>Range (Ambient) | TA     | -55 to +125       | .€   |

| Junction Temperature                     | TJ     | TJ < TA +20       | ℃    |

| Storage Temperature<br>Range             | Tstg   | -65 to +150       | ℃    |

| Thermal resistance<br>Junction to case   | RThJC  | 5                 | °C/W |

Stresses above those listed may cause permanent damage to the device.

#### 11.2 **DC Electrical Characteristics**

The AT7912E can work with VCC = + 5 V  $\pm$  0.5 V and VCC = + 3.3V  $\pm$  0.3V. Although specified for TTL outputs, all AT7912E outputs are CMOS compatible and will drive to VCC and GND assuming no DC loads.

Table 11-2. 5V operating range DC Characteristics.

| Parameter                    | Symbol | Min. | Max.                                                          | Unit           | Conditions                         |

|------------------------------|--------|------|---------------------------------------------------------------|----------------|------------------------------------|

| Operating Voltage            | VCC    | 4.5  | 5.5                                                           | ٧              |                                    |

| Input HIGH Voltage           | VIH    | 2.2  |                                                               | ٧              |                                    |

| Input LOW Voltage            | VIL    |      | 0.8                                                           | ٧              |                                    |

| Output HIGH Voltage          | VOH    | 2.4  |                                                               | ٧              | IOL = 1.5, 3, 6mA / VCC = VCC(min) |

| Output LOW Voltage           | VOL    |      | 0.4                                                           | ٧              | IOH = 1, 2, 4mA / VCC = VCC(min)   |

| Output Short circuit current | IOS    |      | 90 <sup>(1)</sup><br>180 <sup>(2)</sup><br>270 <sup>(3)</sup> | mA<br>mA<br>mA | VOUT = VCC<br>VOUT = GND           |

- Notes: 1. Applicable for HDATA[7:0], HINTR\*, TMR1\_EXP, TMR2\_EXP, TxD1, DATA[15:0], GPIO[7:0], IOB[24:22], IOB27 and TDO pins

- 2. Applicable for IOB[21:0] pins

- 3. Applicable for LDO and LSO pins

Table 11-3. 3.3V operating range DC Characteristics.

| Parameter                    | Symbol | Min. | Max.                                                         | Unit           | Conditions                        |

|------------------------------|--------|------|--------------------------------------------------------------|----------------|-----------------------------------|

| Operating Voltage            | VCC    | 3.0  | 3.6                                                          | ٧              |                                   |

| Input HIGH Voltage           | VIH    | 2.0  |                                                              | ٧              |                                   |

| Input LOW Voltage            | VIL    |      | 0.8                                                          | ٧              |                                   |

| Output HIGH Voltage          | VOH    | 2.4  |                                                              | ٧              | IOL = 3, 6, 12mA / VCC = VCC(min) |

| Output LOW Voltage           | VOL    |      | 0.4                                                          | ٧              | IOH = 3, 6, 12mA / VCC = VCC(min) |

| Output Short circuit current | IOS    |      | 50 <sup>(1)</sup><br>100 <sup>(2)</sup><br>155 <sup>(3</sup> | mA<br>mA<br>mA | VOUT = VCC<br>VOUT = GND          |

- Notes: 1. Applicable for HDATA[7:0], HINTR\*, TMR1\_EXP, TMR2\_EXP, TxD1, DATA[15:0], GPIO[7:0], IOB[24:22], IOB27 and TDO pins

- 2. Applicable for IOB[21:0] pins

- 3. Applicable for LDO and LSO pins

# 11.3 Power consumption

www.DataSheet4U.com

Maximum power consumption figures at Vcc = 5.5V; -55 °C; CLK = 5 MHz are presented in the following table.

**Table 11-4.** 5V Power Consumption

| Operation Mode      | Power consumption [mA] |

|---------------------|------------------------|

| not clocked         | 2                      |

| AT7912E in RESET    | 22                     |

| AT7912E in IDLE (1) | 75                     |

| Maximum             | 120                    |

<sup>1.</sup> IDLE means clk = 5 MHz, link started and running at 10Mbit/s, no activity on the other interfaces.

Maximum power consumption figures at Vcc = 3.6V; -55 °C; CLK = 5 MHz are presented in the following table.

Table 11-5. 3.3V Power Consumption

| Operation Mode      | Power consumption [mA] |

|---------------------|------------------------|

| not clocked         | 1                      |

| AT7912E in RESET    | 10                     |

| AT7912E in IDLE (1) | 23                     |

| Maximum             | 40                     |

<sup>1.</sup> IDLE means clk = 5 MHz, link started and running at 10Mbit/s, no activity on the other interfaces.

# 11.4 AC Electrical Characteristics

www.DataSheet4U.com

The following table gives the worst case timings measured by Atmel on the 4.5V to 5.5V operating range

**Table 11-6.** 5V operating range timings.

| Parameter                                  | Symbol | Min. | Max. | Unit |

|--------------------------------------------|--------|------|------|------|

| Propagation delay TCK Low to TDO Low       | Tp1    |      | 20   | ns   |

| Propagation delay CLK High to TMR1_EXP Low | Tp2    |      | 23   | ns   |

| Propagation delay CLK High to LDO Low      | Тр3    |      | 16   | ns   |

| Propagation delay CLK High to HINTR* Low   | Tp4    |      | 25   | ns   |

| Propagation delay CLK High to IOB18 Low    | Tp5    |      | 16   | ns   |

The following table gives the worst case timings measured by Atmel on the 3.0V to 3.6V operating range

**Table 11-7.** 3.3V operating range timings

| Parameter                                  | Symbol | Min. | Max. | Unit |

|--------------------------------------------|--------|------|------|------|

| Propagation delay TCK Low to TDO Low       | Tp1    |      | 33   | ns   |

| Propagation delay CLK High to TMR1_EXP Low | Tp2    |      | 38   | ns   |

| Propagation delay CLK High to LDO Low      | Тр3    |      | 27   | ns   |

| Propagation delay CLK High to HINTR* Low   | Tp4    |      | 41   | ns   |

| Propagation delay CLK High to IOB18 Low    | Tp5    |      | 27   | ns   |

For guaranteed timings on the two operating voltage ranges, refer to the section 12 of the 'SMCS116SpW User Manual'

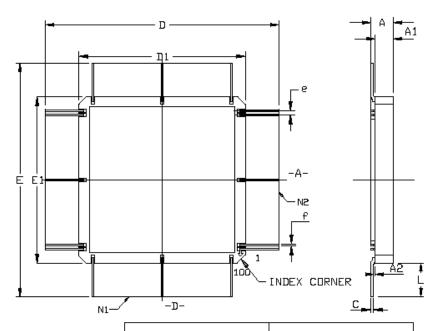

# 12. Package Drawings www.DataSheet4U.com

#### 12.1 MQFPF100

100 pins Ceramic Quad Flat Pack (MQFPF 100)

|    | Min        | Мшж    | Min       | Max    |

|----|------------|--------|-----------|--------|

| Α  | 2, 21      | 2, 67  | . 087     | . 105  |

| С  | D. 15      | 0, 20  | , 006     | . 008  |

| D  | 31. 80     | 32. 80 | 1. 252    | 1. 291 |

| D1 | 18, 80     | 19, 30 | . 740     | . 760  |

| E  | 31. 80     | 32. 80 | 1. 252    | 1. 450 |

| E1 | 18, 80     | 19, 30 | . 740     | . 760  |

| е  | O. 635 BSC |        | . D25 BSC |        |

| f  | 0, 254 REF |        | , 010 REF |        |

| A1 | 1, 83      | 2, 24  | , 072     | , 088  |

| A2 | 0,203 REF  |        | , 008 REF |        |

| L  | 6, 50      | 6, 75  | , 256     | , 266  |

| N1 | 25         |        | 25        |        |

| N2 | 25         |        | 25        |        |

# 13. Ordering Information www.DataSheet4U.com

| Part-number  | Temperature Range | Package  | Quality Flow       |

|--------------|-------------------|----------|--------------------|

| AT7912EKF-E  | 25℃               | MQFPF100 | Engineering sample |

| AT7912EKF-MQ | -55℃ to +125℃     | MQFPF100 | Mil Level B (*)    |

| AT7912EKF-SV | -55℃ to +125℃     | MQFPF100 | Space Level B (*)  |

<sup>(\*)</sup> according to Atmel Quality flow document 4288, see Atmel web site.

#### www.DataSheet4U.com

# **Atmel Corporation**

2325 Orchard Parkway San Jose, CA 95131 Tel: 1(408) 441-0311 Fax: 1(408) 487-2600

## Regional Headquarters

### Europe

Atmel Sarl Route des Arsenaux 41 Case Postale 80 CH-1705 Fribourg Switzerland

Tel: (41) 26-426-5555 Fax: (41) 26-426-5500

#### Asia

Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong Kong

Tel: (852) 2721-9778 Fax: (852) 2722-1369

#### Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan

Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

# **Atmel Operations**

### Memory

2325 Orchard Parkway San Jose, CA 95131 Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

#### Microcontrollers

2325 Orchard Parkway San Jose, CA 95131 Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

La Chantrerie BP 70602 44306 Nantes Cedex 3, France Tel: (33) 2-40-18-18-18

Tel: (33) 2-40-18-18-18 Fax: (33) 2-40-18-19-60

### ASIC/ASSP/Smart Cards

Zone Industrielle 13106 Rousset Cedex, France Tel: (33) 4-42-53-60-00

Fax: (33) 4-42-53-60-01

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906

Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

Scottish Enterprise Technology Park Maxwell Building East Kilbride G75 0QR, Scotland

Tel: (44) 1355-803-000 Fax: (44) 1355-242-743

### RF/Automotive

Theresienstrasse 2 Postfach 3535 74025 Heilbronn, Germany Tel: (49) 71-31-67-0 Fax: (49) 71-31-67-2340

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906

Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

## Biometrics/Imaging/Hi-Rel MPU/ High Speed Converters/RF Datacom

Avenue de Rochepleine BP 123

38521 Saint-Egreve Cedex, France

Tel: (33) 4-76-58-30-00 Fax: (33) 4-76-58-34-80

e-mail literature@atmel.com

Web Site http://www.atmel.com

**Disclaimer:** Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company's standard warranty which is detailed in Atmel's Terms and Conditions located on the Company's web site. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Atmel are granted by the Company in connection with the sale of Atmel products, expressly or by implication. Atmel's products are not authorized for use as critical components in life support devices or systems.

©2007 Atmel Corporation. All rights reserved. Atmel®, logo and combinations thereof are registered trademarks, or are the trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.