#### **Features**

- Audio Processor

- Proprietary Digital Signal Processor

- MP3 and WMA Decoders

- WAV PCM and ADPCM Decoder/Coder with AGC

- JPEG decoder

- Video Animation (MTV up to 16fps)

- Audio Codec

- 16-bit Stereo D/A Converters<sup>(3)</sup>

- Headphone Amplifier with Analog Volume Control<sup>(3)</sup>

- Microphone Pre-Amplifier with Bias Control

- 16-bit Mono A/D Converter: Microphone or Line Inputs Recording

- Stereo Lines Input for FM Playback or Mono Recording

- 3-band EQ and Bass Boost and 3D Sound Effects

- Graphical EQ

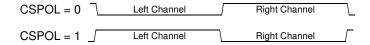

- Digital Audio DAC Interface

- PCM / I<sup>2</sup>S Format Compatible

- USB Rev 2.0 Controller

- 7 Endpoints, Multiple Enumeration

- High Speed Mode (480 Mbps)

- Full Speed Mode (12 Mbps)

- On The Go Full Speed Mode

- File Management

- Fat 12, 16, 32 Management

- Multiple Drive Management: Nand Flash, Card, U-Disk...

- Multiple Folders and Sub-Folders (user defined)

- Multiple File Read and Write

- Playlist and Lyrics Support

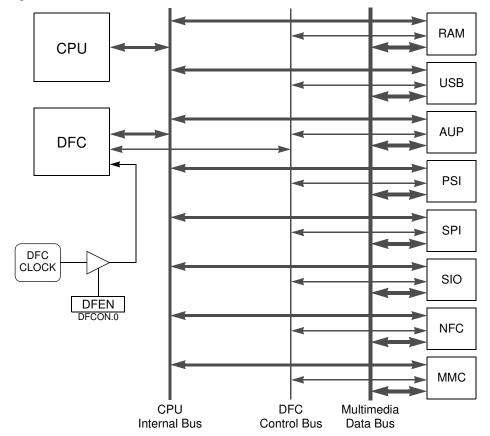

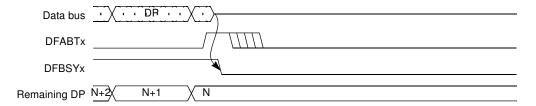

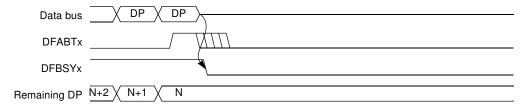

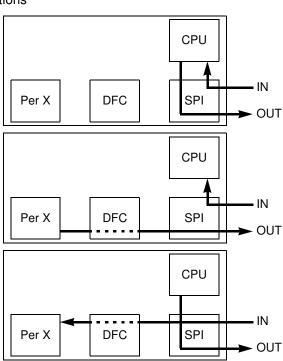

- · Data Flow Controller

- 16-bit Multimedia Bus with 2 DMA Channels for high speed transfer with USB

- Nand Flash Controller

- Multiple Nand as 1 Drive, Support All Page Size

- Read up to 10MB/s, Write up to 8MB/s

- Built-in ECC and Hardware Write Protection

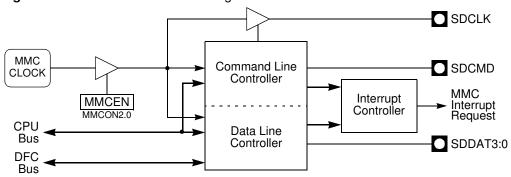

- MultiMediaCard<sup>®</sup> Controller

- MultiMediaCard 1-bit / 4-bits Modes (V4 compatible)

- Secure Digital Card 1-bit / 4-bit Modes

- · Man Machine Interface

- Glueless Generic LCD Interface

- Keyboard Interface

- FM Tuner Input and Control including RDS

- PSI I80 Slave Interface (EBI Compatible) up to 6Mbytes/s

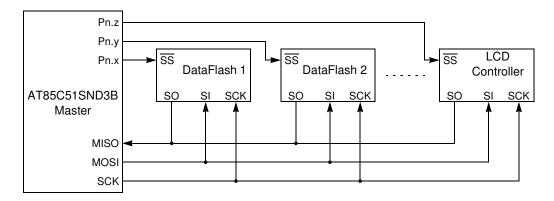

- SPI Master and Slave Modes

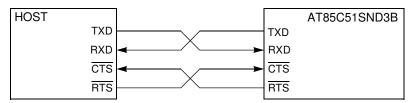

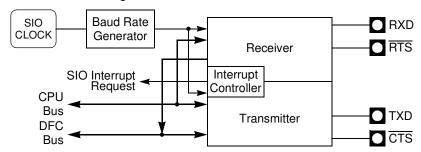

- Full Duplex UART with Baud Rate Generator up to 6 Mbit/s (Rx, Tx, RTS, CTS)

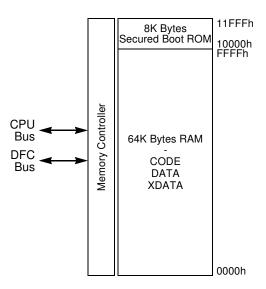

- Control Processor

- Enhanced 8-bit MCU C51 Core (F<sub>MAX</sub> = 24 MHz)

- 64K Bytes of Internal RAM for application code and data

- Boot ROM Memory: Secured Nand Flash Boot Strap (standard), USB Boot Loader

- Two 16-bit Timers/Counters: Hardware Watchdog Timer

- In-System and In-Application Programming

- Power Management

- 1.8V 40 mA Single AAA or AA Battery Powered(4)

- Direct USB V<sub>BUS</sub> Supply

- 3V or 1.8V 50 mA Regulator Output

- Battery Voltage Monitoring

- Power-on Reset, Idle, Power-Down, Power-Off Modes

- Software Programmable MCU Clock

- Operating Conditions

- Supply 1.8V to 5V for all Product range, plus 0.9V to 1.8V<sup>(4)</sup>

Single-Chip

Digital Audio

Decoder Encoder with

USB 2.0

Interface

AT85C51SND3B

**Preliminary**

7632D-MP3-01/07

- 25 mA Typical Operating at 25 °C (estimation to be confirmed)

- Temperature Range: -40 °C to +85 °C

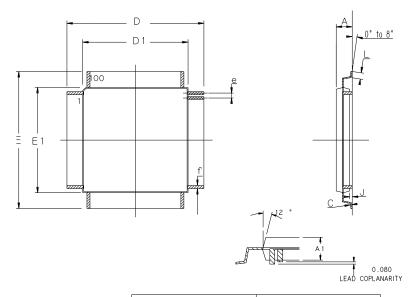

- Packages

- LQFP100, BGA100, Dice

Notes: 1. See Ordering Information

- 2. AT85C51SND3B1 & AT85C51SND3B2 only

- 3. AT85C51SND3B2 only

### **Description**

Digital Music Players, Mobile Phones need ready to use low-cost solutions for very fast time to market. The AT85C51SND3B with associated firmware embeds in a single chip all features, hardware and software, for Digital Music Players, Mobile Phones and Industrial or Toys applications: MP3 decoder, WMA decoder, Display interface, serial interface, parallel interface, USB high speed and USB host.

Close to a plug and play solution for most applications, the AT85C51SND3B drastically reduces system development for the best time to market. The AT85C51SND3B handles full file system management with Nand Flash and Flash Cards, including full detection and operation of a thumb drive. The AT85C51SND3Bx is used either as a master controller, or as a slave controller interfacing easily with most of the base-band or host processors available on the market.

The AT85C51SND3B includes Power Management with: 5V USB  $V_{BUS}$  direct supply, 2.7V to 3.6V supply, 1.8V supply or alkaline battery supply (0.9V to 1.8V). External Nand Flash or Flash Card can be supplied by the AT85C51SND3B at 1.8V or 3V.

The AT85C51SND3B supports many applications including: mobile phones, music players, portable navigation, car audio, music in shopping centers, applications including MMC/SD Flash Cards in Industrial applications.

To facilitate custom applications with the AT85C51SND3B, a development kit AT85DVK-07 and a reference design AT85RFD-07 are available with hardware and firmware database.

# **Key Features**

- Firmware to support

- MP3

- WMA

- ADPCM/WAV voice or line recording

- JPEG Decoder

- Audio Codec

- Internal DAC

- FM inputs

- Memory Support

- Up to 4x Nand-Flash

- SD/MMC cards

- USB

- High Speed, Full Speed

- OTG (reduced Host)

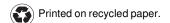

### **Block Diagram**

Figure 1. AT85C51SND3B Block Diagram

Notes: 1. AT85C51SND3B2 only

2. AT85C51SND3B1 & AT85C51SND3B2 only

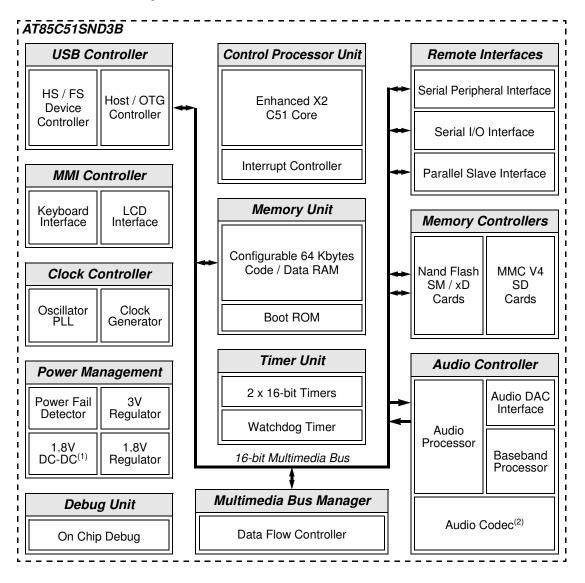

## **Application Information**

The AT85C51SND3B derivatives allow design of 2 typical applications which differentiate by the power supply voltage:

- The Very Low Voltage System

The player operates at 1.8V and allows very low power consumption.

- The Low Voltage System

The player operates at 3V and allows low power consumption.

Figure 2. Typical Low Voltage 3V Application

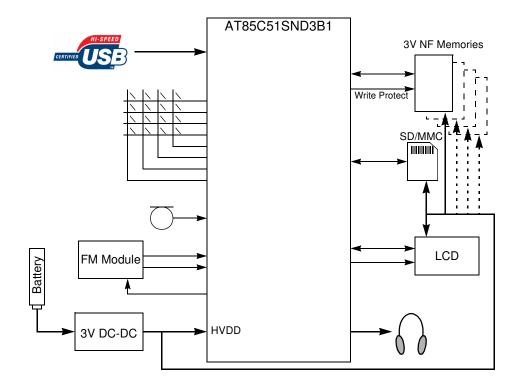

### **Pin Description**

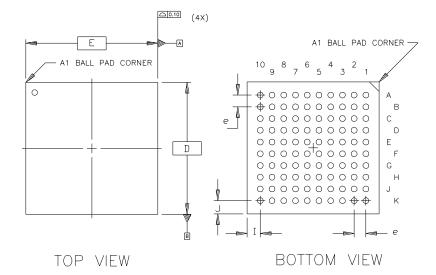

#### **Pinouts**

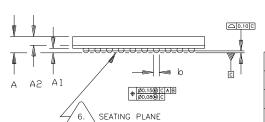

Figure 3. AT85C51SND3B 100-pin QFP Package

Notes: 1. Leave these pins unconnected for AT85C51SND3B0 & AT85C51SND3B1 products

2. Leave these pins unconnected for AT85C51SND3B0 product

Figure 4. AT85C51SND3B 100-pin BGA Package (no ADC)

|   | 1            | 2     | 3             | 4             | 5    | 6               | 7              | 8               | 9               | 10              |

|---|--------------|-------|---------------|---------------|------|-----------------|----------------|-----------------|-----------------|-----------------|

| A | UPDD         | DMH   | DPH           | DPF           | DMF  | HVDD            | Uvcc           | BVDD            | P1.3            | P1.4            |

| В | UPVSS        | UBIAS | Uvss          | UHVDD (       | NC   | NC              | P1.0           | P1.2            | P1.6            | P1.5            |

| С | AVSS1        | RLVDD | NC            | NC (          | NC   | NC              | P2.2/<br>SDCMD | P2.1/<br>SDLCK  | P2.0/<br>SDINS  | P1.7            |

| D | LINR         | MICIN | MICBIAS       | NC (          | P3.6 | NC              | P1.1           | P2.5/<br>SDDAT1 | P2.4/<br>SDDAT0 | P2.3/<br>SDLCK  |

| Ε | AVCM         | LINL  | AVREF         | NC (          | P3.7 | OUTR            | OUTL           | P2.7/<br>SDDAT3 | NFWP            | P2.6/<br>SDDAT1 |

| F | X1           | APVSS | NC            | P4.3/<br>DSEL | P3.4 | vss             | P0.3           | NFCE0           | P4.5/<br>NFCE2  | P4.4/<br>NFCE1  |

| G | X2           | NC    | APVDD         | P4.1/<br>DCLK | NC   | AVDD2/<br>IOVDD | P0.2           | P0.1            | P4.6/<br>NFCE3  | NFCLE           |

| Н | NC           | OCDR  | P4_2<br>/DDAT | P3.2          | P3.1 | P0.5            | P0.0           | NFRE            | NFALE           | NFWE            |

| J | OCDT/<br>ISP | P5.1  | P5.3          | P4.0/<br>OCLK | P0.7 | P0.4            | NFD6           | NFD4            | NFD0            | NFD1            |

| K | RST          | P5.0  | P5.2          | P3.3          | P3.0 | P0.6            | NFD7           | NFD5            | NFD3            | NFD2            |

### **Signals Description**

### System

Table 1. System Signal Description

| Signal<br>Name | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Alternate<br>Function |

|----------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| RST            | I/O  | Reset Input Holding this pin low for 64 oscillator periods while the oscillator is running resets the device. The Port pins are driven to their reset conditions when a voltage lower than $V_{\rm IL}$ is applied, whether or not the oscillator is running. This pin has an internal pull-up resistor $(R_{\rm RST})$ which allows the device to be reset by connecting a capacitor between this pin and $V_{\rm SS}$ . Asserting RST when the chip is in Idle mode or Power-Down mode returns the chip to normal operation. In order to reset external components connected to the $\overline{\rm RST}$ line a low level 96-clock period pulse is generated when the watchdog timer reaches its time-out period. | -                     |

| ĪSP            | I    | In System Programming Assert this pin during reset phase to enter the in system programming mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | OCDT                  |

Table 2. Ports Signal Description

| Signal<br>Name   | Туре | Description                                                          | Alternate<br>Function                                   |

|------------------|------|----------------------------------------------------------------------|---------------------------------------------------------|

| P0.7:0           | I/O  | Port 0 P0 is an 8-bit bidirectional I/O port with internal pull-ups. | LD7:0                                                   |

| P1.7:0           | I/O  | Port 1 P1 is an 8-bit bidirectional I/O port with internal pull-ups. | KIN3:0                                                  |

| P2.7:0           | I/O  | Port 2 P2 is an 8-bit bidirectional I/O port with internal pull-ups. | SDINS<br>SDLCK<br>SDCMD<br>SDCLK<br>SDDAT3:0            |

| P3.4:0<br>P3.7:6 | I/O  | Port 3 P3 is a 7-bit bidirectional I/O port with internal pull-ups.  | RXD MISO TXD MOSI INTO RTS SCK INT1 CTS SS T0 UVCON UID |

| Signal<br>Name | Туре | Description                                                         | Alternate<br>Function                                  |

|----------------|------|---------------------------------------------------------------------|--------------------------------------------------------|

| P4.6:0         | I/O  | Port 4 P4 is a 7-bit bidirectional I/O port with internal pull-ups. | OCLK DCLK DDAT DSEL NFCE1/SMLCK NFCE2/SMINS NFCE3/SMCE |

| P5.3:0         | I/O  | Port 5 P5 is a 4-bit bidirectional I/O port with internal pull-ups. | LRD/LDE SDR LCS SCS LA0/LRS SA0 LWR/LRW SWR            |

Table 3. Timer 0 and Timer 1 Signal Description

| Signal<br>Name | Туре | Description                                                                                                                                                                                                                                                                                                                    | Alternate<br>Function           |

|----------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

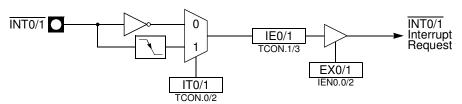

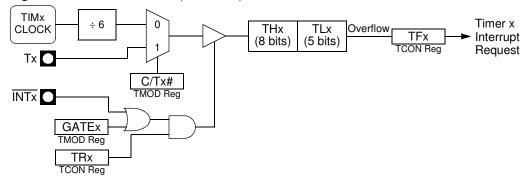

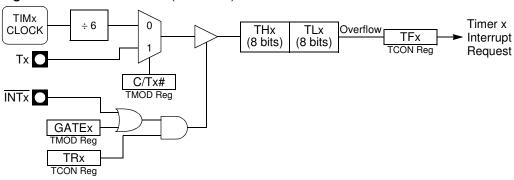

| ĪNTO           | I    | Timer 0 Gate Input  INTO serves as external run control for timer 0, when selected by GATE0 bit in TCON register.  External Interrupt 0  INTO input sets IE0 in the TCON register. If bit IT0 in this register is set, bit IE0 is set by a falling edge on INTO. If bit IT0 is cleared, bit IE0 is set by a low level on INTO. | P3.2<br>RTS<br>SCK              |

| ĪNT1           | I    | Timer 1 Gate Input  INT1 serves as external run control for timer 1, when selected by GATE1 bit in TCON register.  External Interrupt 1  INT1 input sets IE1 in the TCON register. If bit IT1 in this register is set, bit IE1 is set by a falling edge on INT1. If bit IT1 is cleared, bit IE1 is set by a low level on INT1. | P3.3<br><u>CTS</u><br><u>SS</u> |

| T0             | I    | Timer 0 External Clock Input When timer 0 operates as a counter, a falling edge on the T0 pin increments the count.                                                                                                                                                                                                            | P3.4                            |

#### **Clock Controller**

Table 4. Clock Signal Description

| Signal<br>Name | Туре | Description                                                                                                                                                                                                                                                    | Alternate<br>Function |

|----------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

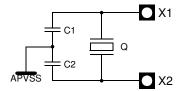

| X1             | I    | Input of the on-chip inverting oscillator amplifier  To use the internal oscillator, a crystal/resonator circuit is connected to this pin. If an external oscillator is used, its output is connected to this pin. X1 is the clock source for internal timing. | -                     |

| X2             | 0    | Output of the on-chip inverting oscillator amplifier  To use the internal oscillator, a crystal/resonator circuit is connected to this pin. If an external oscillator is used, leave X2 unconnected.                                                           | -                     |

| UPVDD          | PWR  | USB PLL Supply voltage Connect this pin to LVDD pin.                                                                                                                                                                                                           | -                     |

| UPVSS          | GND  | USB PLL Circuit Ground Connect this pin to LVSS pin.                                                                                                                                                                                                           | -                     |

| APVDD          | PWR  | Audio PLL / Oscillator Supply voltage Connect this pin to LVDD pin.                                                                                                                                                                                            | -                     |

| APVSS          | GND  | Audio PLL / Oscillator Circuit Ground Connect this pin to LVSS pin.                                                                                                                                                                                            | -                     |

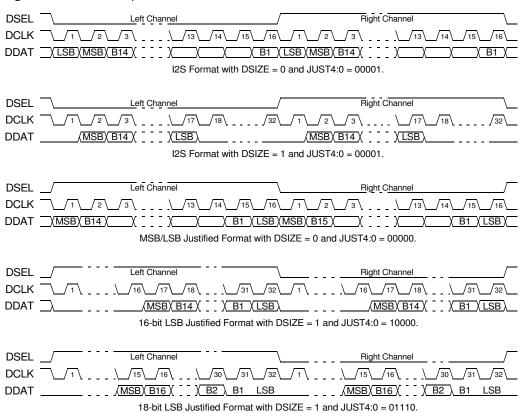

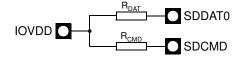

### **Memory Controllers**

Table 5.

Secure Digital Card / MutiMediaCard Controller Signal Description

| Signal<br>Name | Туре | Description                                                                                                                                                                                        | Alternate<br>Function |

|----------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| SDCLK          | 0    | SD/MMC Clock Data or command clock transfer.                                                                                                                                                       | P2.3                  |

| SDCMD          | I/O  | SD/MMC Command Line Bidirectional command line used for commands and responses transfer.                                                                                                           | P2.2                  |

| SDDAT3:0       | I/O  | SD/MMC Data Lines Bidirectional data lines. In 1-bit mode configuration SDDAT0 is the DAT signal and SDDAT3:1 are not used and can be reused as I/O ports.                                         | P2.7:4                |

| SDINS          | I    | SD/MMC Card Insertion Signal SDINS is the card presence signal. A low level on this input indicates the card is present in its slot.  Note: This signal is generated by the SD/MMC card connector. | P2.0                  |

| SDLCK          | ı    | SD Card Write Lock Signal SDLCK is the SD Card write protected input. A low level on this pin indicates the card is write protected. Note: This signal is generated by the SD/MMC card connector.  | P2.1                  |

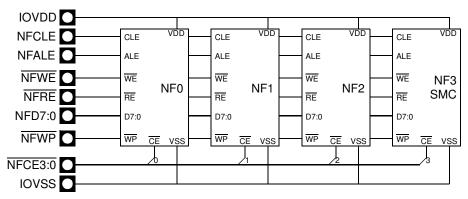

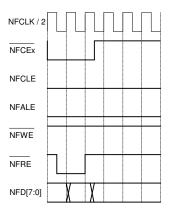

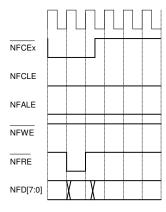

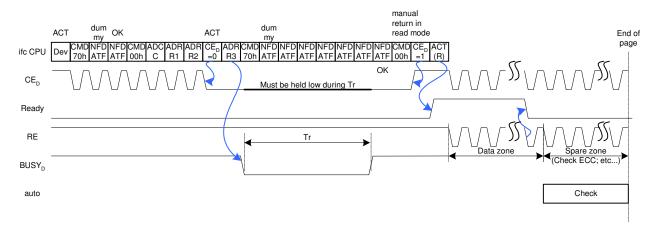

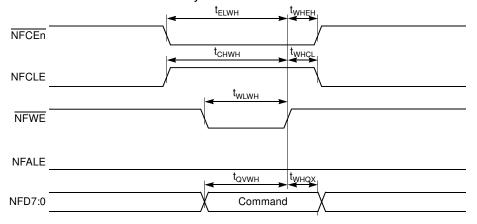

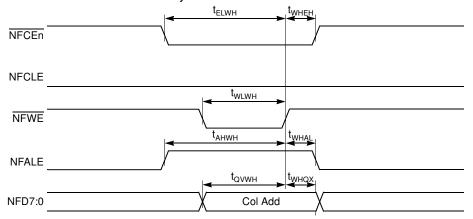

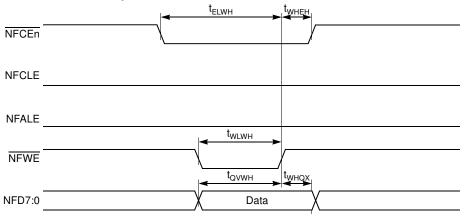

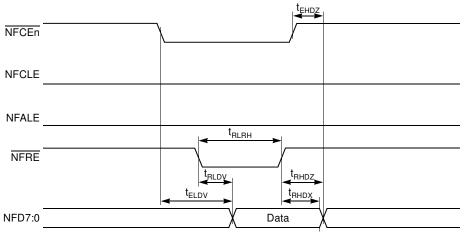

Table 6. Nand Flash / SmartMedia Card Controller Signal Description

| Signal<br>Name | Туре | Description                                                           | Alternate<br>Function |

|----------------|------|-----------------------------------------------------------------------|-----------------------|

| NFD7:0         | I/O  | Memory Data Bus<br>8-bit bidirectional data bus.                      | -                     |

| NFALE          | 0    | Address Latch Enable Signal Asserted high during address write cycle. | -                     |

| Signal<br>Name | Туре | Description                                                                                                                                                                                                                                                                                                                                                        | Alternate<br>Function |

|----------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| NFCLE          | 0    | Command Latch Enable Signal Asserted high during command write cycle.                                                                                                                                                                                                                                                                                              | -                     |

| NFRE           | 0    | Read Enable Signal Read signal asserted low during NF/SMC read operation.                                                                                                                                                                                                                                                                                          | -                     |

| NFWE           | 0    | Write Enable Signal Write signal asserted low during NF/SMC write operation.                                                                                                                                                                                                                                                                                       | -                     |

| NFCE0          | 0    | Nand Flash 0 Chip Enable  NFCE0 is active low and is asserted by the nand flash controller each time it makes access to the device 0.                                                                                                                                                                                                                              | -                     |

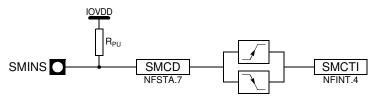

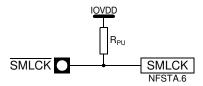

| NFCE1          | 0    | Nand Flash 1 Chip Enable  NFCE1 is active low and is asserted by the nand flash controller each time it makes access to the selected device.  SmartMediaCard/xD-Picture Card Write Lock Signal  SMLCK is the card write protected input. A low level on this pin indicates the card is write protected.  Note: When used as SMLCK input, pad has internal pull-up. | P4.4                  |

| NFCE2          | 0    | Nand Flash 2 Chip Enable  NFCE2 is active low and is asserted by the nand flash controller each time it makes access to the selected device.  SmartMediaCard/xD-Picture Card Insertion Signal  SMINS is the card presence signal. A low level on this input indicates the card is present in its slot.  Note: When used as SMINS input, pad has internal pull-up.  | P4.5                  |

| NFCE3          | 0    | Nand Flash 3 Chip Enable  NFCE3 is active low and is asserted by the nand flash controller each time it makes access to the selected device.  SmartMediaCard/xD-Picture Card Chip Enable  SMCE is active low and is asserted by the nand flash controller each time it makes access to the card.                                                                   | P4.6                  |

| NFWP           | 0    | Write Protect Signal NFWP is the Nand Flash / SmartMediaCard/xD-Picture Card write protect signal. This signal is active low and is set to low during reset in order to protect the memory against parasitic writes.                                                                                                                                               | -                     |

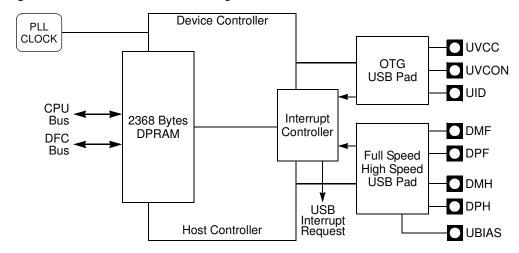

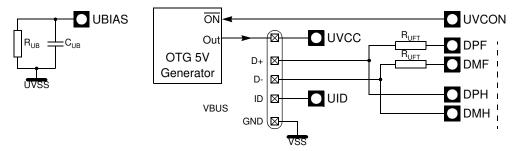

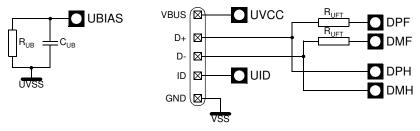

#### **USB Controller**

Table 7. USB Controller Signal Description

| Signal<br>Name | Туре | Description                                                                                                                           | Alternate<br>Function |

|----------------|------|---------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| DPF            | I/O  | USB Full Speed Positive Data Upstream Port                                                                                            | -                     |

| DMF            | I/O  | USB Full Speed Minus Data Upstream Port                                                                                               | -                     |

| DPH            | I/O  | USB High Speed Plus Data Upstream Port                                                                                                | -                     |

| DMH            | I/O  | USB High Speed Minus Data Upstream Port                                                                                               | -                     |

| UVCON          | 0    | USB VBUS Control line UVCON is used to control the external VBUS power supply ON or OFF. Note: This output is requested for OTG mode. | P3.6                  |

| Signal<br>Name | Туре | Description                                                                                                            | Alternate<br>Function |

|----------------|------|------------------------------------------------------------------------------------------------------------------------|-----------------------|

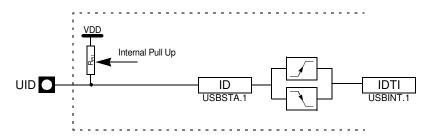

| UID            | I    | USB OTG Identifier Input This pin monitors the function of the OTG device. Note: This input is requested for OTG mode. | P3.7                  |

| UVCC           | PWR  | USB Supply Voltage Connect this pin to USB V <sub>BUS</sub> power line.                                                | -                     |

| ULVDD          | PWR  | USB Pad Low Voltage Connect this pin to LVDD pin.                                                                      | -                     |

| UHVDD          | PWR  | USB Pad High Voltage Connect this pin to HVDD pin.                                                                     | -                     |

| UVSS           | GND  | USB Ground                                                                                                             | -                     |

| UBIAS          | 0    | USB Bias Connect this pin to external resistor and capacitor.                                                          |                       |

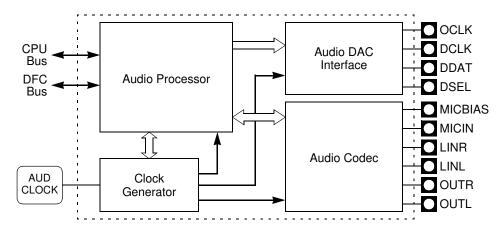

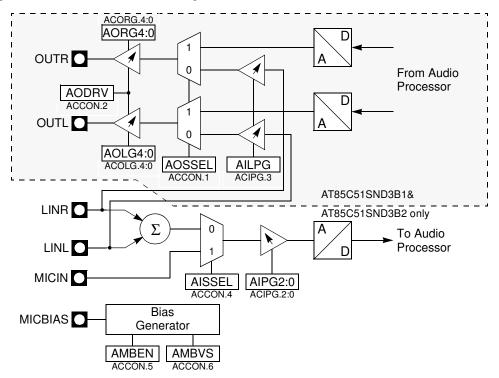

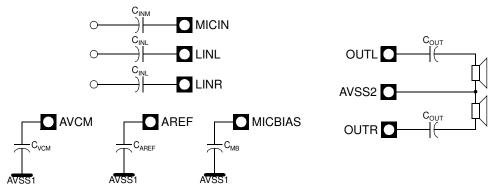

#### **Audio Processor**

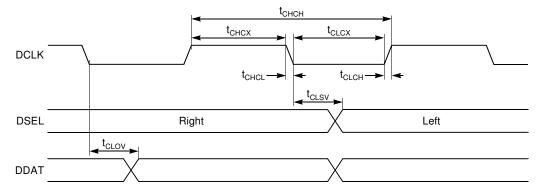

Table 8. I2S Output Description

| Signal<br>Name | Туре | Description                 | Alternate<br>Function |

|----------------|------|-----------------------------|-----------------------|

| OCLK           | 0    | Over-sampling Clock Line    | P4.0                  |

| DCLK           | 0    | Data Clock Line             | P4.1                  |

| DDAT           | 0    | Data Lines                  | P4.2                  |

| DSEL           | 0    | Data Channel Selection Line | P4.3                  |

Table 9. Audio Codec Description

| Signal<br>Name | Туре | Description                                                                   | Alternate<br>Function |

|----------------|------|-------------------------------------------------------------------------------|-----------------------|

| LINR           | - 1  | Right Channel Analog Input                                                    | -                     |

| LINL           | - 1  | Left Channel Analog Input                                                     | -                     |

| MICIN          | - 1  | Electret Microphone Analog Input                                              | -                     |

| MICBIAS        | 0    | Electret Microphone Bias Output                                               | -                     |

| OUTR           | 0    | Right Channel Output  Do not connect on AT85C51SND3B0 product                 | -                     |

| OUTL           | 0    | Left Channel Output Do not connect on AT85C51SND3B0 product                   | -                     |

| AVCM           | I    | Analog Common Mode Voltage Connect this pin to external decoupling capacitor. | -                     |

| AREF           | 0    | Analog Reference Voltage Connect this pin to external decoupling capacitor.   | -                     |

| AVDD1          | PWR  | Analog Power Supply 1 Connect this pin to LVDD pin.                           | -                     |

| AVSS1          | GND  | Analog Ground 1 Connect this pin to LVSS pin.                                 | -                     |

| Signal<br>Name | Туре | Description                                                                                                                                 | Alternate<br>Function |

|----------------|------|---------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| AVDD2          | PWR  | Analog Power Supply 2 Low Voltage system: connect this pin to LVDD pin. High voltage system: connect this pin to external +3V power supply. | ,                     |

| AVSS2          | GND  | Analog Ground 2 Low Voltage system: connect this pin to LVSS pin. High voltage system: connect this pin to external +3V ground.             | -                     |

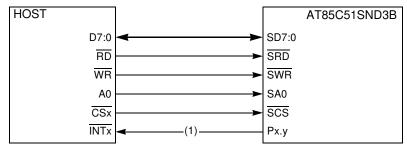

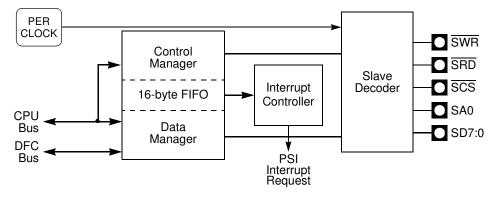

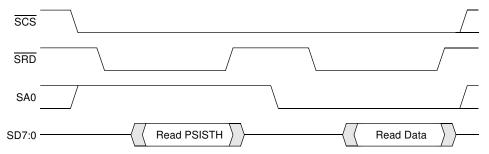

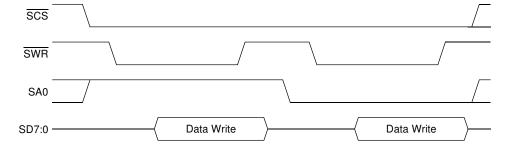

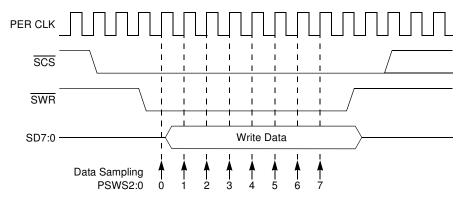

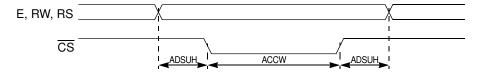

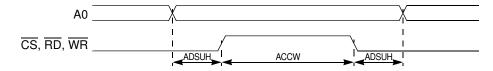

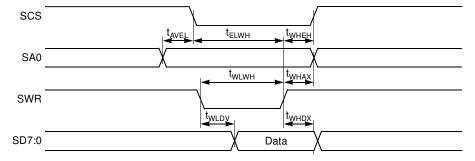

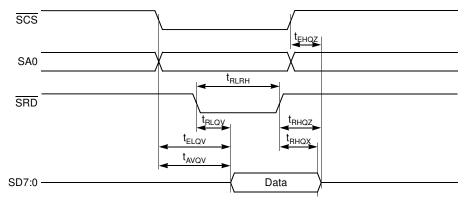

#### **Parallel Slave Interface**

### Table 10. PSI Signal Description

| Signal<br>Name | Туре | Description                                                                                | Alternate<br>Function |

|----------------|------|--------------------------------------------------------------------------------------------|-----------------------|

| SD7:0          | I/O  | Slave Data Bus<br>8-bit bidirectional data bus.                                            | P0.7:0<br>LD7:0       |

| SRD            | I    | Slave Read Signal Read signal asserted low during external host read operation.            | P5.0<br>LRD/LDE       |

| SWR            | I    | Slave Write Signal Write signal asserted low during external host write operation.         | P5.3<br>LWR/LRW       |

| SCS            | I    | Slave Chip Select Select signal asserted low during external host read or write operation. | P5.1<br>LCS           |

| SA0            | I    | Slave Address Bit 0 Address signal asserted during external host read or write operation.  | P5.2<br>LA0/LRS       |

#### **Serial Interfaces**

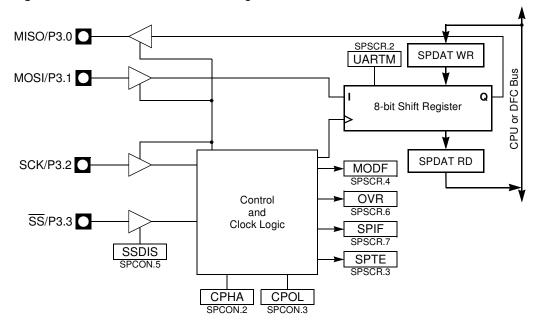

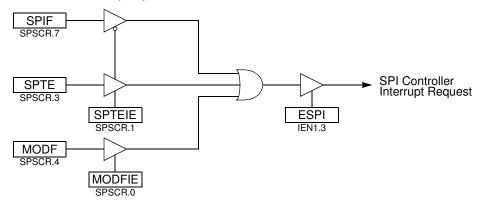

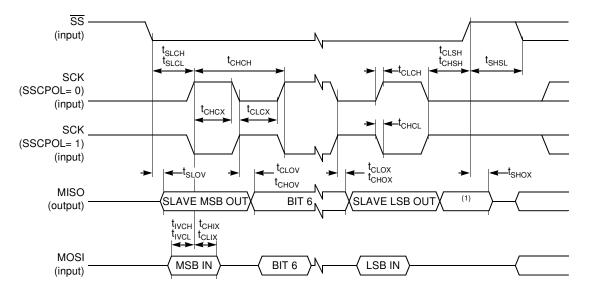

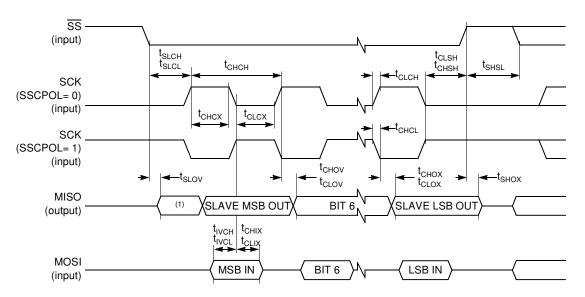

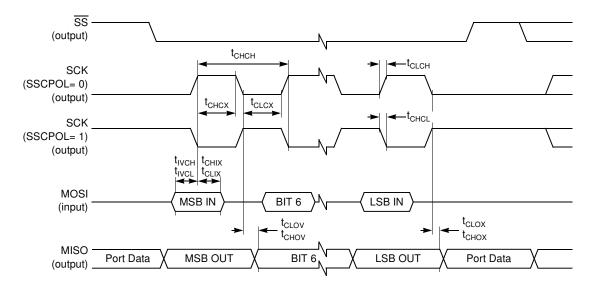

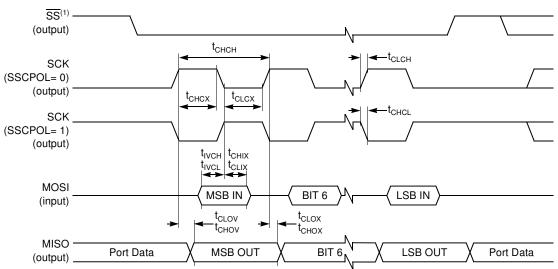

### Table 11. SPI Controller Signal Description

| Signal<br>Name | Туре | Description                                                                                                                                                                | Alternate<br>Function |  |

|----------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--|

| MISO           | I/O  | SPI Master Input Slave Output Data Line When in master mode, MISO receives data from the slave peripheral. When in slave mode, MISO outputs data to the master controller. | P3.0<br>RXD           |  |

| MOSI           | I/O  | SPI Master Output Slave Input Data Line When in master mode, MOSI outputs data to the slave peripheral. When in slave mode, MOSI receives data from the master controller. |                       |  |

| SCK            | I/O  | SPI Clock Line When in master mode, SCK outputs clock to the slave peripheral. When in slave mode, SCK receives clock from the master controller.                          |                       |  |

| SS             | I    | SPI Slave Select Line When in controlled slave mode, SS enables the slave mode.                                                                                            | P3.3<br>INT1<br>CTS   |  |

Table 12. SIO Signal Description

| Signal<br>Name | Туре | Description                                                                                                            | Alternate<br>Function |

|----------------|------|------------------------------------------------------------------------------------------------------------------------|-----------------------|

| RXD            | I/O  | Receive Serial Data RXD sends and receives data in serial I/O mode 0 and receives data in serial I/O modes 1, 2 and 3. | P3.0<br>MISO          |

| Signal<br>Name | Туре | Description                                                                                                               | Alternate<br>Function |

|----------------|------|---------------------------------------------------------------------------------------------------------------------------|-----------------------|

| TXD            | 0    | Transmit Serial Data  TXD outputs the shift clock in serial I/O mode 0 and transmits data in serial I/O modes 1, 2 and 3. | P3.1<br>MOSI          |

| RTS            | 0    | O Request To Send Hardware Handshake Line Asserted low by hardware when SIO is ready to receive data.                     |                       |

| CTS            | ı    | Clear To Send Hardware Handshake Line Asserted low by external hardware when SIO is allowed to send data.                 | P3.3<br>INT1<br>SS    |

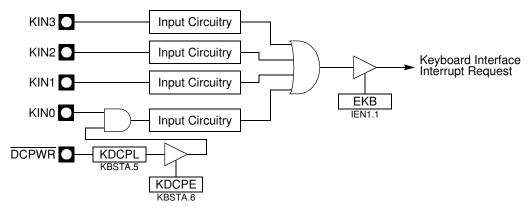

#### **MMI Interface**

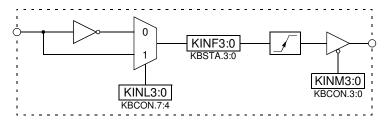

### Table 13. Keypad Controller Signal Description

| Signal<br>Name | Туре | Description                                                                                                     | Alternate<br>Function |

|----------------|------|-----------------------------------------------------------------------------------------------------------------|-----------------------|

| KIN3:0         | -    | Keypad Input lines Holding one of these pins high or low for 24 oscillator periods triggers a keypad interrupt. | P1.3:0                |

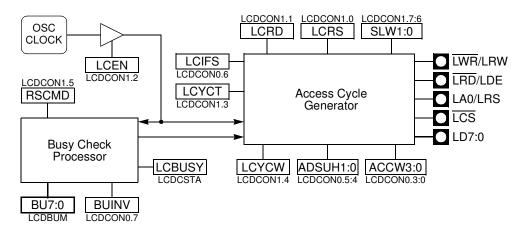

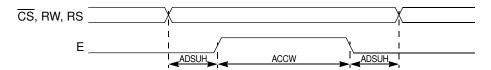

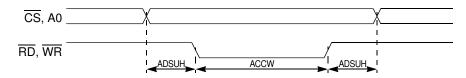

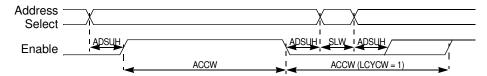

### Table 14. LCD Interface Signal Description

| Signal<br>Name | Туре | Description                                                                                                                                                              | Alternate<br>Function |

|----------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| LD7:0          | I/O  | Display Data Bus<br>8-bit bidirectional data bus.                                                                                                                        | P0.7:0<br>SD7:0       |

| LRD/LDE        | 0    | Read Signal/Enable Signal  8080: Read signal asserted low during display read access.  6800: Enable signal asserted high during display access.                          | P5.0<br>SRD           |

| LWR/LRW        | 0    | Write Signal/Read Write Signal  8080: Write signal asserted low during display write access.  6800: Read/Write signal asserted low/high during display read/write access | P5.3<br>SWR           |

| LCS            | 0    | Display Chip Select Select signal asserted low during display access.                                                                                                    | P5.1<br>SCS           |

| LA0/LRS        | 0    | Display Address Bit 0/Register Select Address signal asserted during display access.                                                                                     | P5.2<br>SA0           |

### **Power Management**

### Table 15. Power Signal Description

| Signal<br>Name | Туре | Description                                                                         | Alternate<br>Function |

|----------------|------|-------------------------------------------------------------------------------------|-----------------------|

| DCPWR          | I    | DC-DC Power ON Input Connect DCPWR to V <sub>SS</sub> to start the DC-DC converter. | -                     |

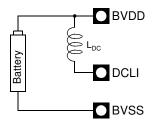

| DCLI           | PWR  | DC-DC Inductance Input Connect low ESR inductance to DCLI and BVDD.                 |                       |

| BVDD           | PWR  | Battery Supply Voltage Connect this pin to the positive pin of the battery.         | -                     |

| Signal<br>Name | Туре | Description                                                                                                                                                                                        | Alternate<br>Function |  |

|----------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--|

| BVSS           | GND  | Battery Ground Connect this pin to the negative pin of the battery.                                                                                                                                | -                     |  |

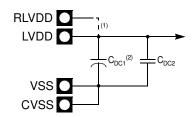

| LVDD           | PWR  | Low Voltage DC-DC Power Supply output This pin outputs +1.8V typ. from internal DC-DC (battery powered).                                                                                           | -                     |  |

| RLVDD          | PWR  | Low Voltage Regulator Power Supply Output This pin outputs +1.8V typ. from internal regulator (USB powered or +3V external power supply). Connect this pin to LVDD incase of internal DC-DC usage. | -                     |  |

| HVDD           | PWR  | High Voltage Power Supply This pin outputs +3V typ. from internal regulator (USB powered). Connect this pin to +3V external power supply.                                                          | -                     |  |

| VSS            | GND  | Power Ground Connect this pin to the system ground.                                                                                                                                                | -                     |  |

| CVSS           | GND  | Core Ground Connect this pin to VSS pin.                                                                                                                                                           | -                     |  |

| IOVDD          | PWR  | Input/Output Supply voltage Connect this pin to LVDD or HVDD pin.                                                                                                                                  | -                     |  |

| IOVSS          | GND  | Input/Output Circuit Ground Connect this pin to VSS pin.                                                                                                                                           | -                     |  |

### **OCD Interface**

Table 16. OCD Signal Description

| Signal<br>Name | Туре | Description                                        | Alternate<br>Function |

|----------------|------|----------------------------------------------------|-----------------------|

| OCDR           | I    | On Chip Debug Receive Input OCDR receives data.    | -                     |

| OCDT           | I/O  | On Chip Debug Transmit Output OCDT transmits data. | ĪSP                   |

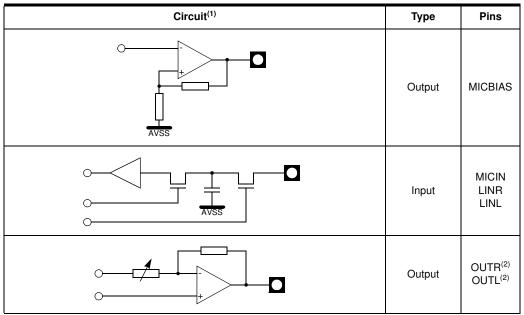

### **Internal Pin Structure**

Table 17. Detailed Internal Pin Structure

| Circuit <sup>(1)</sup>                    | Туре         | Pins                                                             |

|-------------------------------------------|--------------|------------------------------------------------------------------|

| IOVES IOVES                               | Input/Output | RST                                                              |

| 2 osc periods Latch Output Ps Pm Pw Novss | Input/Output | P0.7:0<br>P1.7:0<br>P2.7:0<br>P3.5:0<br>P4.6:0<br>P5.3:0<br>OCDT |

| Latch Output Ps Pm Pw                     | Input/Output | P3.7:6                                                           |

| IOVDD IOVDD IOVDD IOVS IOVS               | Input        | KIN3:0 SDINS SDLCK SMINS SMLCK TST ISP UID INTO INT1 T0 RXD OCDR |

| ○ <b>─</b>                                | Input        | SWR<br>SA0<br>SRD<br>SCS<br>SS                                   |

| IOVED P P IOVES                           | Input/Output | NFD7:0<br>SD7:0<br>LD7:0<br>SDCMD<br>SDDAT3:0<br>MISO<br>MOSI    |

| Circuit <sup>(1)</sup>                      | Туре         | Pins                                                                                                       |

|---------------------------------------------|--------------|------------------------------------------------------------------------------------------------------------|

| IOVED P P P P P P P P P P P P P P P P P P P | Output       | SDCLK SCK NFCE3:0 NFCEE NFALE NFWE NFRE NFWP SMCE DSEL DDAT DCLK OCLK LWR/LE LA0/LRS LRD/LRW LCS UVCON TXD |

| DPF DMF                                     | Input/Output | DPF<br>DMF                                                                                                 |

| DPH DMH                                     | Input/Output | DPH<br>DMH                                                                                                 |

| BVDD                                        | Input        | DCPWR <sup>(2)</sup>                                                                                       |

| P N CVSS                                    | -            | DCLI <sup>(2)</sup>                                                                                        |

Notes: 1. For information on resistor value, input/output levels, and drive capability, refer to Section "DC Characteristics", page 242.

- 2. AT85C51SND3B2 only

- 3. AT85C51SND3B1 & AT85C51SND3B2 only

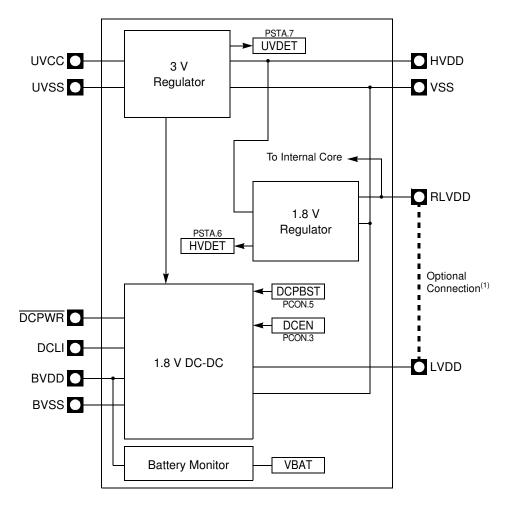

### **Power Management**

The Power Management of AT85C51SND3B dervatives implements all the internal power circuitry (regulators, links...) as well as power failure detector and reset circuitry.

### **Power Supply**

The AT85C51SND3B2 embeds the regulators and a DC to DC step-up convertor to be able to operate from either USB power supply (5V nominal) or from a single cell battery such as AAA battery.

The AT85C51SND3B0 and AT85C51SND3B1 embed the regulators to be able to operate from either USB power supply (5V nominal) or from an external 3 volts supply.

Figure 5. Power Supply Diagram

Note: 1. External connection mandatory when 1.8V DC-DC is used.

#### Regulators

The high voltage regulator supplies power to the external devices through HVDD power pin. Its nominal voltage output is 3V.

The low voltage regulator supplies power to the internal device and external devices through RLVDD power pin. Its nominal voltage output is 1.8V.

Figure 6 shows how to connect external components, capacitors value along with power characteristics are specified in the section "DC characteristics".

Schematic

Figure 6. Regulator Connection

Note: Depending on power supply scheme,  $C_{LV}$  may replace  $C_{DC}$  capacitor (see Figure 8).

# Low Voltage DC-DC in AT85C51SND3B2

The low voltage output DC-DC converter supplies power to the internal device and external devices through LVDD power pin. It operates from a single AAA battery. Its nominal voltage output is 1.8V.

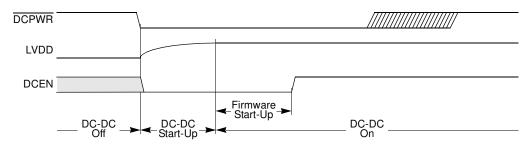

DC-DC Start-Up

DC-DC start-up is done by asserting the DCPWR input until the voltage reaches its nominal value (see Section "Power Fail Detector") and firmware starts execution and sets the DCEN bit in PCON to maintain the DC-DC enabled. DCPWR input can then be released. As shown in Figure 8 DCPWR input is asserted by pressing a key connected to BVSS.

Figure 7. DC-DC Start-Up Phase

DC-DC Shut-Down

DC-DC shut-down is done by two different ways:

- Clearing the DCEN bit while DCPWR pin is de-asserted

- Detecting the presence of an internal or external 3V supply, e.g. when the device is connected to USB, DC-DC is disabled to save battery power<sup>(1)</sup>.

Note: 1. If DCEN bit is left set, the DC-DC will restart as soon as the USB power supply disappears.

DC-DC Connection

Figure 8 shows how to connect external components, inductance and components value along with power characteristics are specified in the section "DC characteristics".

Figure 8. Battery DC-DC Connection

Note: Depending on power supply scheme, C<sub>DC1</sub> may replace C<sub>LV</sub> capacitor (see Figure 6).

#### **Battery Voltage Monitor**

The battery voltage monitor is a 5-bit / 50 mV resolution A to D converter with fixed conversion range as detailed in Table 18.

Table 18. Battery Voltage Value

| VB4:0 | Battery Voltage (V) |

|-------|---------------------|

| 00000 | [0.9 - 0.95[        |

| 00001 | [0.95 - 1.0[        |

| 00010 | [1.0 - 1.05[        |

|       |                     |

| 01110 | [1.6 - 1.65[        |

| 01111 | [1.65 - 1.7[        |

| 10000 | [1.7 - 1.75[        |

#### Conversion Management

The battery voltage monitor is turned on by setting the VBPEN and VBCEN bits in PCON (see Table 20). VBPEN bit is set first and VBCEN bit is set 1 ms later. An additional delay of 16 cycles is required before lauching any conversion.

Launching a conversion is done by setting VBEN bit in VBAT (see Table 22). VBEN is automatically cleared at the end of the conversion which takes 34 clock periods. At this step two cases occur:

- Voltage is valid (inside conversion range)

VBERR is cleared and conversion value is set in VB4:0 according to Table 18.

- Voltage is invalid (out of conversion range)

VBERR is set and value reported by VB4:0 is indeterminate.

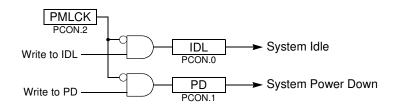

#### **Power Reduction Mode**

Two power reduction modes are implemented in the AT85C51SND3B: the Idle mode and the Power-down mode. These modes are detailed in the following sections. In addition to these power reduction modes, the clocks of the core and peripherals can be dynamically divided by 2 using the X2 mode as detailed in Section "X2 Feature", page 31.

#### Lock Mode

In order to allow firmware to efficiently enter in idle mode and not to lose any events that should come from one or more interrupts, power reduction modes entry are conditioned to an hardware bit: PMLCK in PCON.

PMLCK is set by software in each ISR that needs to report an event to the system and thus disables entry in power reduction mode and allows immediate processing of this event. It is cleared by software after exiting power reduction mode.

As shown in Figure 9, when power reduction modes are disabled by setting PMLCK, IDL and PD bits in PCON can not be set and idle or power down modes are not entered.

Figure 9. Power Reduction Controller Block Diagram

#### Idle Mode

Idle mode is a power reduction mode that reduces the power consumption. In this mode, program execution halts. Idle mode freezes the clock to the CPU at known states while the peripherals continue to be clocked (refer to Section "System Clock Generator", page 30). The CPU status before entering Idle mode is preserved, i.e., the program counter and program status word register retain their data for the duration of Idle mode. The contents of the SFRs and RAM are also retained.

Entering Idle Mode

To enter Idle mode, the user must set the IDL bit in PCON register while PMLCK is cleared. The AT85C51SND3B enters Idle mode upon execution of the instruction that sets IDL bit. The instruction that sets IDL bit is the last instruction executed.

Note: If IDL bit and PD bit are set simultaneously, the AT85C51SND3B enter Power-down mode. Then it does not go in Idle mode when exiting Power-down mode.

Exiting Idle Mode

There are 2 ways to exit Idle mode:

- 1. Generate an enabled interrupt.

- Hardware clears IDL bit in PCON register which restores the clock to the CPU. Execution resumes with the interrupt service routine. Upon completion of the interrupt service routine, program execution resumes with the instruction immediately following the instruction that activated Idle mode. The general-purpose flags (GF1 and GF0 in PCON register) may be used to indicate whether an interrupt occurred during normal operation or during Idle mode. When Idle mode is exited by an interrupt, the interrupt service routine may examine GF1 and GF0.

- Generate a reset.

- A logic high on the RST pin clears IDL bit in PCON register directly and asynchronously. This restores the clock to the CPU. Program execution momentarily resumes with the instruction immediately following the instruction that activated the Idle mode and may continue for a number of clock cycles before the internal reset algorithm takes control. Reset initializes the AT85C51SND3B and vectors the CPU to address 0000h.

Note: During the time that execution resumes, the internal RAM cannot be accessed; however, it is possible for the Port pins to be accessed. To avoid unexpected outputs at the Port pins, the instruction immediately following the instruction that activated Idle mode should not write to a Port pin or to the external RAM.

**Power-down Mode**

The Power-down mode places the AT85C51SND3B in a very low power state. Power-down mode stops the oscillator and freezes all clocks at known states (refer to the Section "Oscillator", page 28). The CPU status prior to entering Power-down mode is preserved, i.e., the program counter, program status word register retain their data for the duration of Power-down mode. In addition, the SFRs and RAM contents are preserved.

Entering Power-down Mode

To enter Power-down mode, set PD bit in PCON register while PMLCK is cleared. The AT85C51SND3B enters the Power-down mode upon execution of the instruction that sets PD bit. The instruction that sets PD bit is the last instruction executed.

Exiting Power-down Mode

There are 2 ways to exit the Power-down mode:

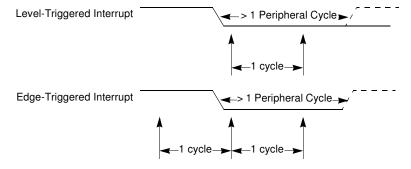

- 1. Generate an enabled external interrupt.

- The AT85C51SND3B provides capability to exit from Power-down using INT0, INT1, and KIN3:0 inputs. In addition, using KIN input provides high or low level exit capability (see Section "Keyboard Interface", page 240).

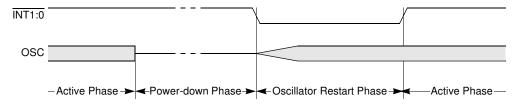

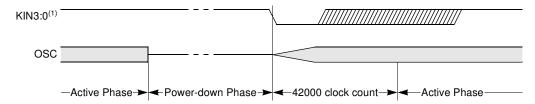

Hardware clears PD bit in PCON register which starts the oscillator and restores

the clocks to the CPU and peripherals. Using INTn input, execution resumes when the input is released (see Figure 10) while using KINx input, execution resumes after counting 1024 clock ensuring the oscillator is restarted properly (see Figure 11). This behavior is necessary for decoding the key while it is still pressed. In both cases, execution resumes with the interrupt service routine. Upon completion of the interrupt service routine, program execution resumes with the instruction immediately following the instruction that activated Powerdown mode.

Note:

- The external interrupt used to exit Power-down mode must be configured as level sensitive (INTO and INT1) and must be assigned the highest priority. In addition, the duration of the interrupt must be long enough to allow the oscillator to stabilize. The execution will only resume when the interrupt is de-asserted.

- Exit from power-down by external interrupt does not affect the SFRs nor the internal RAM content.

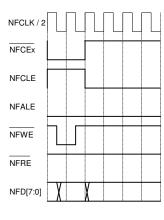

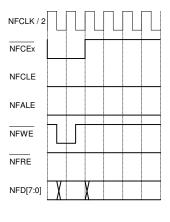

Figure 10. Power-down Exit Waveform Using INT1:0

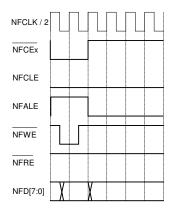

Figure 11. Power-down Exit Waveform Using KIN3:0

Note: 1. KIN3:0 can be high or low-level triggered.

#### 2. Generate a reset.

A logic high on the RST pin clears PD bit in PCON register directly and asynchronously. This starts the oscillator and restores the clock to the CPU and peripherals. Program execution momentarily resumes with the instruction immediately following the instruction that activated Power-down mode and may continue for a number of clock cycles before the internal reset algorithm takes control. Reset initializes the AT85C51SND3B and vectors the CPU to address 0000h.

Notes:

- During the time that execution resumes, the internal RAM cannot be accessed; however, it is possible for the Port pins to be accessed. To avoid unexpected outputs at the Port pins, the instruction immediately following the instruction that activated the Power-down mode should not write to a Port pin or to the external RAM.

- Exit from power-down by reset redefines all the SFRs, but does not affect the internal RAM content.

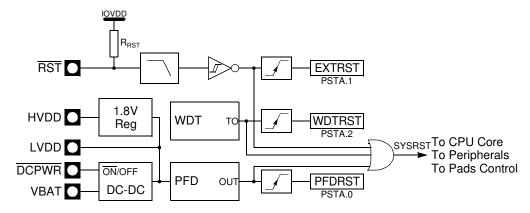

#### Reset

In order to secure the product functionality while in power-up or power-down phase or while in running phase, a number of internal mechanisms have been implemented. These mechanisms are listed below and detailed in the following paragraphs.

- External RST input

- Power Fail Detector (brown-out)

- Watchdog timer

- Pads control

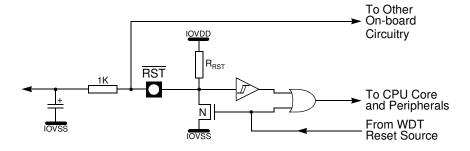

Figure 12 details the internal reset circuitry.

#### **Reset Source Reporting**

In order for the firmware to take specific actions depending on the source which has currently reset the device, activated reset source is reported to the CPU by EXTRST, WDTRST, and PFDRST flags in PSTA register.

Figure 12. Internal Reset Circuitry

#### **Pads Level Control**

As soon as one reset source is asserted, the pads go to their reset value. This ensures that pads level is steady during reset (e.g. NFWP set to low level and then protecting Nand Flash against spurious writing).

The status of the Port pins during reset is detailed in Table 19.

Table 19. Pin State Under Reset Condition.

| Port 0 | Port 1 | Port 2 | Port 3 | Port 4 | Port 5 | NFD7:0 | NFWP | NFCE0 |

|--------|--------|--------|--------|--------|--------|--------|------|-------|

| Float  | Н      | Н      | Н      | Н      | Н      | Float  | L    | Н     |

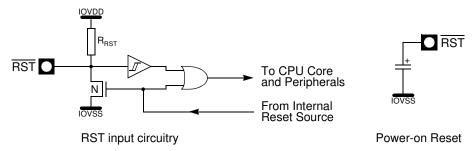

### External RST Input

In order to start-up (cold reset) or to restart (warm reset) properly the microcontroller, a low level has to be applied on the  $\overline{RST}$  pin. A bad level leads to a wrong initialization of the internal registers like SFRs, Program Counter... and to unpredictable behavior of the microcontroller. A proper device reset initializes the AT85C51SND3B and vectors the CPU to address 0000h.  $\overline{RST}$  input has a pull-up resistor allowing power-on reset by simply connecting an external capacitor to  $V_{SS}$  as shown in Figure 13. A warm reset can be applied either directly on the RST pin or indirectly by an internal reset source such as the watchdog timer. Resistor value and input characteristics are discussed in the Section "DC Characteristics", page 242.

Figure 13. Reset Circuitry and Power-On Reset

Cold Reset

2 conditions are required before enabling a CPU start-up:

- V<sub>DD</sub> must reach the specified V<sub>DD</sub> range

- The level on X1 input pin must be outside the specification (V<sub>IH</sub>, V<sub>II</sub>)

If one of these 2 conditions are not met, the microcontroller does not start correctly and can execute an instruction fetch from anywhere in the program space. An active level applied on the  $\overline{RST}$  pin must be asserted till both of the above conditions are met. A reset is active when the level  $V_{IL}$  is reached and when the pulse width covers the period of time where  $V_{DD}$  and the oscillator are not stabilized. 2 parameters have to be taken into account to determine the reset pulse width:

- V<sub>DD</sub> rise time,

- Oscillator startup time.

To determine the capacitor value to implement, the highest value of these 2 parameters has to be chosen.

Warm Reset

To achieve a valid reset, the reset signal must be maintained for at least 2 machine cycles (24 oscillator clock periods) while the oscillator is running. The number of clock periods is mode independent (X2 or X1).

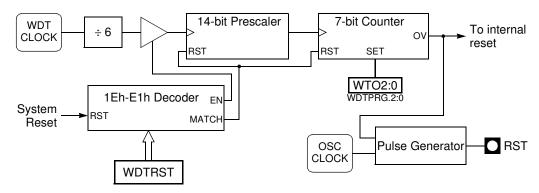

#### **Watchdog Timer Reset**

As detailed in Section "Watchdog Timer", page 75, the WDT generates a 96-clock period pulse on the  $\overline{\text{RST}}$  pin. In order to properly propagate this pulse to the rest of the application in case of external capacitor or power-supply supervisor circuit, a 1 k $\Omega$  resistor must be added as shown in Figure 14.

Figure 14. Reset Circuitry for WDT Reset-out Usage

**Power Fail Detector**

The Power Fail Detector (PFD) ensures that whole product is in reset when internal voltage is out of its limits specification. PFD limits are detailed in the Section "DC Characteristics", page 242.

### **Registers**

Table 20. PCON Register

PCON (0.87h) – Power Control Register

| ,     | ь     | 5      | 4   | 3    | 2     | ı  | U   |

|-------|-------|--------|-----|------|-------|----|-----|

| VBCEN | VBPEN | DCPBST | GF0 | DCEN | PMLCK | PD | IDL |

| Di:           | D'i             |                                                                                                                                                                                                                           |

|---------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                                                                               |

| 7             | VBCEN           | Battery Monitor Clock Enable Bit Set to enable the clock of the battery monitoring. Clear to disable the clock of the battery monitoring.                                                                                 |

| 6             | VBPEN           | Battery Monitor Power Enable Bit Set to power the battery monitoring. Clear to unpower the battery monitoring.                                                                                                            |

| 5             | DCPBST          | DC-DC Converter Power Boost Bit Set to disable DC-DC high power boost mode. Clear to enable DC-DC high power boost mode.                                                                                                  |

| 4             | GF0             | General-purpose flag 0 One use is to indicate whether an interrupt occurred during normal operation or during Idle mode.                                                                                                  |

| 3             | DCEN            | DC-DC Converter Enable Bit  Set to start the DC-DC converter or maintain its activity while DCPWR pin is asserted.  Clear to stop the DC-DC converter and shut off the device if not powered by an external power supply. |

| 2             | PMLCK           | Power Mode Lock Bit Set to lock power-down or Idle mode entry by preventing PD or IDL bits from being set by software. Clear to unlock power-down or Idle mode entry.                                                     |

| 1             | PD              | Power-down Mode bit Cleared by hardware when an interrupt or reset occurs. Set to activate the Power-down mode when PMLCK is cleared. If IDL and PD are both set, PD takes precedence.                                    |

| 0             | IDL             | Idle Mode bit Cleared by hardware when an interrupt or reset occurs. Set to activate the Idle mode when PMLCK is cleared. If IDL and PD are both set, PD takes precedence.                                                |

Reset Value = 00011 0000b

Table 21. PSTA Register

PSTA (0.86h) - Power Status Register

| 7     | 6     | 5 | 4 | 3 | 2      | 1      | 0      |

|-------|-------|---|---|---|--------|--------|--------|

| UVDET | HVDET | - | - | - | WDTRST | EXTRST | PFDRST |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                       |

|---------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------|

| 7             | UVDET           | USB Voltage Detect Flag Set by hardware when 5V is detected on UVDD pin. Cleared by hardware when 5V is not detected on UVDD pin. |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                                    |

|---------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6             | HVDET           | High Voltage Detect Flag Set by hardware when 3V is detected on HVDD pin. Cleared by hardware when 3V is not detected on HVDD pin.                                             |

| 5-3           | -               | Reserved The value of these bits is always 0. Do not set these bits.                                                                                                           |

| 2             | WDTRST          | Watchdog Timer Reset Flag Set by hardware when the watchdog timer has overflowed triggering and internal reset. Must be cleared by software at power-up.                       |

| 1             | EXTRST          | External Reset Flag Set by hardware when the external RST pin is asserted (warm reset). Must be cleared by software at power-up.                                               |

| 0             | PFDRST          | Power Failure Detector Reset Flag Set by hardware when the power voltage has been triggered outside its specified value (cold reset). Must be cleared by software at power-up. |

Reset Value = XX00 0XXXb<sup>(1)</sup>

Note: 1. Reset value depends on the power supply presence and on the internal reset source.

Table 22. VBAT Register

VBAT (0.85h) - Battery Voltage Monitor Register

| 7    | 6     | 5 | 4   | 3   | 2   | 1   | 0   |

|------|-------|---|-----|-----|-----|-----|-----|

| VBEN | VBERR | - | VB4 | VB3 | VB2 | VB1 | VB0 |

| Bit<br>Number                                                                             | Bit<br>Mnemonic | Description                                                                          |

|-------------------------------------------------------------------------------------------|-----------------|--------------------------------------------------------------------------------------|

| 7 VBEN Set to enable the battery monitoring. Cleared by hardware at the end of conversion |                 |                                                                                      |

| 6                                                                                         | VBERR           | Battery Monitor Error Flag Set by hardware when conversion is out of min/max values. |

| 5                                                                                         | -               | Reserved The value read from this bit is always 0. Do not set this bit.              |

| 4-0                                                                                       | VB4:0           | Battery Value Refer to Table 18 for voltage value correspondence.                    |

Reset Value = 0000 0000b

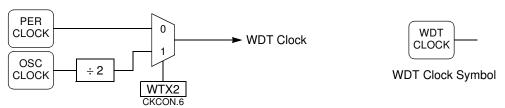

#### **Clock Controller**

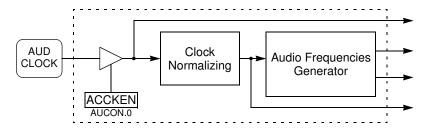

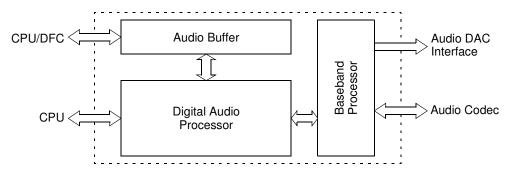

The clock controller implemented in AT85C51SND3B derivatives is based on an on-chip oscillator feeding two on-chip Phase Lock Loop (PLL) dedicated for the USB controller (see Section "USB Controller", page 85) and the Audio Controller (see Section "Audio Controller", page 149). All internal clocks to the peripherals and CPU core are generated by this controller.

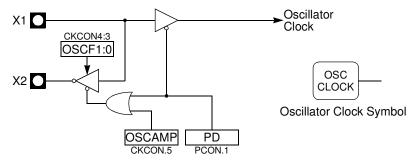

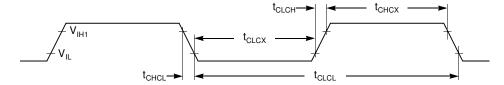

#### **Oscillator**

X1 and X2 pins are the input and the output of a frequency power-optimized singlestage on-chip inverter (see Figure 15) that can be configured with off-chip components such as a Pierce oscillator (see Figure 16). Value of capacitors and crystal characteristics are detailed in the Section "DC Characteristics", page 242.

#### **Authorized frequency**

In order to be able to be able to properly detect the oscillating frequency when in In System Programming mode and then generate the 480MHz requested for USB connection, only the following frequencies are authorized:

12MHz, 13MHz, 16MHz, 19.2MHz, 19.5MHz, 20MHz, 24MHz and 26MHz.

#### **Power Optimization**

In order to optimize the power consumption, oscillator gain can be adjusted by software depending on the crystal frequency. Such optimization is done after reset using OSCF1:0 bits in CKCON register (see Table 31) according to Table 23. Moreover if external frequency signal is input (X1 driven by a remote host) it is possible to switch off the internal amplifier by setting the OSCAMP bit in CKCON register as shown in Figure 15.

Table 23. Oscillator Frequency Configuration

| OSCF1:0 | Crystal Clock Frequency Range (F <sub>OSC</sub> ) |

|---------|---------------------------------------------------|

| 00      | 22 - 26 MHz (default)                             |

| 01      | 18 - 22 MHz                                       |

| 10      | 14 - 18 MHz.                                      |

| 11      | 10 - 14 MHz                                       |

The oscillator outputs a clock: the oscillator clock used to feed the clock generator and the system clock generator.

The oscillator clock can be disabled by entering the power-down reduction mode as detailed in the Section "Power Management", page 19.

Figure 15. Oscillator Block Diagram and Symbol

Figure 16. Crystal Connection

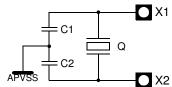

#### **Clock Generator**

The clock generator provides the oscillator and higher frequency clocks to the System, the DFC, the memory controllers: Nand Flash and MMC controllers, the USB and the high speed Serial I/O port. It is based on a 480 MHz PLL namely the PLL clock followed by a frequency divider giving a broad range of available clock frequency: the CLOCK GEN clocks.

The clock generation is enabled by setting CKGENE bit in CKEN (see Table 32).

The PLL is enabled by setting PLLEN bit in CKEN and reports a filtered lock status by the PLOCK Flag in CKEN.

As soon as the PLL is locked, the generated clocks can be used by the peripherals as detailed in the following sections.

Figure 17. Clock Generator Block Diagram and Symbol

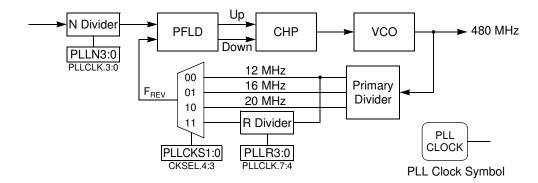

480 MHz PLL

The PLL is based on a Phase Frequency Comparator and Lock Detector block (PFLD) which makes the comparison between the reference clock coming from the 4-bit N divider (PLLN3:0 + 1 in PLLCLK) and the reverse clock coming from either fixed frequencies or the 4-bit R divider (PLLR3:0 + 1 in PLLCLK) and generates some pulses on the Up or Down signal depending on the edge position of the reverse clock. These pulses feed the Charge Pump block (CHP) that generates a voltage reference to the 480 MHz Voltage Controlled Oscillator (VCO) by injecting or extracting charges from an internal filter. The reverse clock selection mechanism is implemented in order to support many oscillator frequencies and to minimize the PLL output jitter.

Figure 18. PLL Block Diagram and Symbol

Table 24. PLL Reverse Clock Selection

| PLLCKS1:0 | Clock Selection (F <sub>REV</sub> ) |

|-----------|-------------------------------------|

| 00        | 12 MHz (default)                    |

| 01        | 16 MHz                              |

| 10        | 20 MHz                              |

| 11        | 12 MHz ÷ (PLLR + 1)                 |

PLL Programming

The PLL is programmed depending on the oscillator clock frequency. In order to minimize the output jitter,  $F_{REV}$  must be as higher as possible. Table 26 shows the PLL programming values and reverse frequency depending on some oscillator frequency.

Table 25. PLL Programming Values versus Input Frequency

| F <sub>OSC</sub> (MHz) | PLLCKS1:0 | PLLN3:0 / N | PLLR3:0 / R | F <sub>REV</sub> (MHz) |

|------------------------|-----------|-------------|-------------|------------------------|

| 12                     | 00        | 0000        | XXXX        | 12                     |

| 13                     | 11        | 1100 / 13   | 1011 / 12   | 1                      |

| 16                     | 01        | 0000        | XXXX        | 16                     |

| 19.2                   | 11        | 0111 / 8    | 0100 / 5    | 2.4                    |

| 19.5                   | 11        | 1100 / 13   | 0111 / 8    | 1.5                    |

| 20                     | 10        | 0000        | XXXX        | 20                     |

| 24                     | 00        | 0001 / 2    | xxxx        | 12                     |

| 26                     | 11        | 1100 / 13   | 0101 / 6    | 2                      |

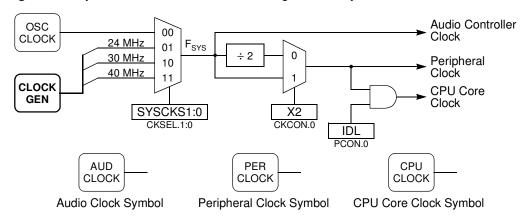

### **System Clock Generator**

In order to increase the system computation throughput, it is possible to switch the system clock to higher value when PLL is enabled. System clock generator block diagram is shown in Figure 19 and is based on a frequency selector controlled by SYSCKS1:0 bits in CKSEL (see Table 34) according to Table 26.

The CPU clock can be disabled by entering the idle reduction mode as detailed in the Section "Power Management", page 19.

Note:

In order to prevent any incorrect operation while dynamically switching the system frequency, user must be aware that all peripherals using the peripheral clock as time reference (timers, etc...) will have their time reference modified by this frequency change.

Figure 19. System Clock Generator Block Diagram and Symbols

Table 26. System Clock Selection

| SYSCKS1:0 | Clock Selection (F <sub>SYS</sub> ) |

|-----------|-------------------------------------|

| 00        | F <sub>OSC</sub> (default)          |

| 01        | 24 MHz                              |

| 10        | 30 MHz                              |

| 11        | 40 MHz                              |

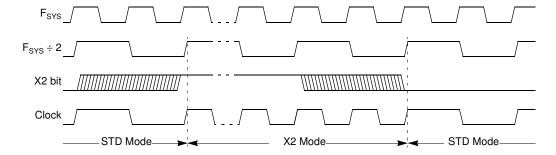

X2 Feature

Unlike standard C51 products that require 12 clock periods per machine cycle, the AT85C51SND3B needs only 6 clock periods per machine cycle. This feature called the "X2 feature" can be enabled using the X2 bit<sup>(1)</sup> in CKCON and allows the AT85C51SND3B to operate in 6 or 12 clock periods per machine cycle. As shown in Figure 19, both CPU and peripheral clocks are affected by this feature. Figure 20 shows the X2 mode switching waveforms. After reset the standard mode is activated. In standard mode the CPU and peripheral clock frequency is the oscillator frequency divided by 2 while in X2 mode, it is the oscillator frequency.

Figure 20. Mode Switching Waveforms

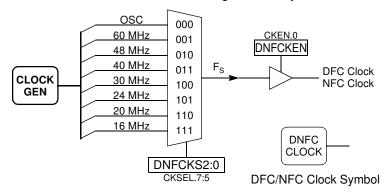

DFC/NFC Clock Generator

In order to optimize the data transfer throughput between the DFC and the NFC, both peripherals share the same clock frequency. The DFC and NFC clock generator block diagram is shown in Figure 21 and is based on a frequency selector.

Frequency selection is done using DNFCKS2:0 bits in CKSEL (see Table 33) according to Table 27.

Frequency is enabled by setting DNFCKEN bit in CKEN.

Figure 21. DFC/NFC Clock Generator Block Diagram and Symbol

Table 27. DFC/NFC Clock Selection

| DNFCKS2:0 | Clock Selection (F <sub>S</sub> ) |

|-----------|-----------------------------------|

| 000       | F <sub>OSC</sub> (default)        |

| 001       | 60 MHz                            |

| 010       | 48 MHz                            |

| 011       | 40 MHz                            |

| 100       | 30 MHz                            |

| 101       | 24 MHz                            |

| 110       | 20 MHz                            |

| 111       | 16 MHz                            |

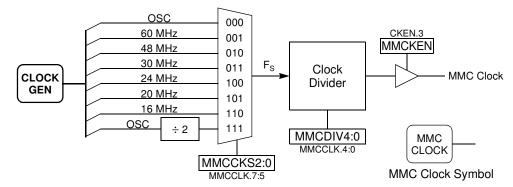

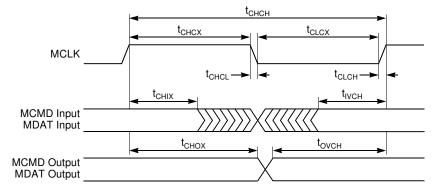

#### **MMC Clock Generator**

The MMC clock generator block diagram is shown in Figure 22 and is based on a frequency selector followed by a frequency divider.

Frequency selection is done using MMCCKS2:0 bits in MMCCLK (see Table 35) according to Table 28<sup>(1)</sup>.

Frequency division is done using MMCDIV4:0 bits in MMCCLK according to Table 29.

Frequency configuration (selection and division) must be done prior to enable the MMC clock generation by setting MMCKEN bit in CKEN.

Note: 1. To allow low frequency as low as 400 KHz (frequency needed in MMC identification phase), F<sub>OSC</sub> selection can be divided by 2.

Figure 22. MMC Clock Generator Block Diagram and Symbol

Table 28. MMC Clock Selection

| MMCCKS2:0 | Clock Selection (F <sub>S</sub> ) |

|-----------|-----------------------------------|

| 000       | F <sub>OSC</sub> (default)        |

| 001       | 60 MHz                            |

| 010       | 48 MHz                            |

| 011       | 30 MHz                            |

| 100       | 24 MHz                            |

| 101       | 20 MHz                            |

| 110       | 16 MHz                            |

| 111       | F <sub>OSC</sub> ÷2               |

Table 29. MMC Clock Divider

| MMCDIV4:0 | Clock Division              |

|-----------|-----------------------------|

| 00000     | Disabled (no clock out)     |

| ≥ 00001   | $F_{MMC} = F_S \div MMCDIV$ |

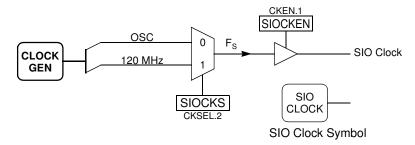

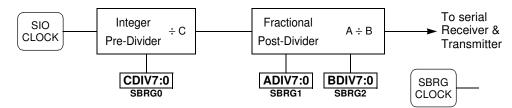

#### **SIO Clock Generator**

As detailed in Figure 23, the SIO clock which feeds the internal SIO baud rate generator can be programmed using SIOCKS bit in CKSEL register according to Table 30 to generate either the oscillator frequency or a very high frequency allowing very high baud rate when PLL is enabled. SIO clock is enabled by SIOCKEN bit in CKEN register.

Figure 23. SIO Clock Generator Block Diagram and Symbol

Table 30. SIO Clock Selection

| SIOCKS | Clock Selection (F <sub>S</sub> ) |

|--------|-----------------------------------|

| 0      | F <sub>osc</sub>                  |

| 1      | 120 MHz                           |

### Registers

Table 31. CKCON Register

CKCON (0.8Fh) - Clock Control Register

| 7 | 6    | 5      | 4     | 3     | 2    | 1    | 0  |

|---|------|--------|-------|-------|------|------|----|

| - | WDX2 | OSCAMP | OSCF1 | OSCF0 | T1X2 | T0X2 | X2 |

| Bit         | Bit      |                                                                                                         |

|-------------|----------|---------------------------------------------------------------------------------------------------------|

| Number      | Mnemonic | Description                                                                                             |

| 7           | _        | Reserved                                                                                                |

| ,           |          | The value read from this bit is always 0. Do not set this bit.                                          |

|             |          | Watchdog Clock Control Bit                                                                              |

| 6           | WDX2     | Set to select the oscillator clock divided by 2 as watchdog clock input (X2                             |

|             |          | independent). Clear to select the peripheral clock as watchdog clock input (X2 dependent).              |

|             |          | Oscillator Amplifier Control Bit                                                                        |

| 5           | OSCAMP   | Set to optimize power consumption by disabling the oscillator amplifier when an external clock is used. |

|             |          | Clear to enable the oscillator amplifier in case of crystal usage (default).                            |

| 4.0         | 00051.0  | Oscillator Frequency Range Bits                                                                         |

| 4-3 OSCF1:0 |          | Set this bits according to Table 23 to optimize power consumption.                                      |

|             |          | Timer 1 Clock Control Bit                                                                               |

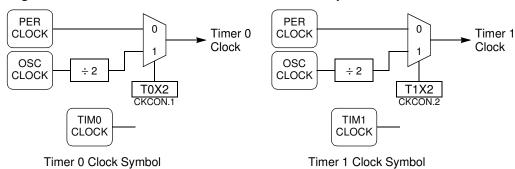

| 2           | T1X2     | Set to select the oscillator clock divided by 2 as timer 1 clock input (X2                              |

|             |          | independent).  Clear to select the peripheral clock as timer 1 clock input (X2 dependent).              |

|             |          | Timer 0 Clock Control Bit                                                                               |

| 1           | T0X2     | Set to select the oscillator clock divided by 2 as timer 0 clock input (X2                              |

|             | 1082     | independent).                                                                                           |

|             |          | Clear to select the peripheral clock as timer 0 clock input (X2 dependent).                             |

|             |          | System Clock Control Bit                                                                                |

| 0           | X2       | Clear to select 12 clock periods per machine cycle (STD mode, $F_{CPU} = F_{PER} = F_{OSC}/2$ ).        |

|             |          | Set to select 6 clock periods per machine cycle (X2 mode, $F_{CPU} = F_{PER} = F_{OSC}$ ).              |

Reset Value = 0000 0000b

Table 32. CKEN Register

CKEN (0.B9h) - Clock Enable Register

76543210CKGENEPLLEN-PLOCKMMCKEN-SIOCKENDNFCKEN

| Bit<br>Number                        | Bit<br>Mnemonic | Description                                                                                                         |

|--------------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------|

| 7                                    | CKGENE          | Clock Generator Enable Bit Set to enable the clock generator. Clear to disable the clock generators.                |

| 6                                    | PLLEN           | PLL Enable Bit Set to enable the 480 MHz PLL. Clear to disable the 480 MHz PLL.                                     |

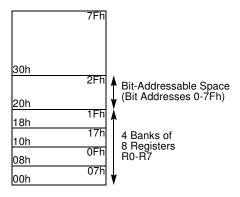

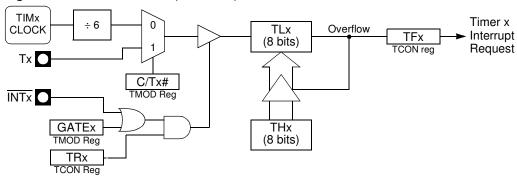

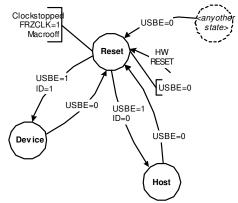

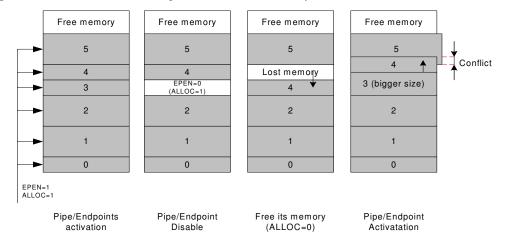

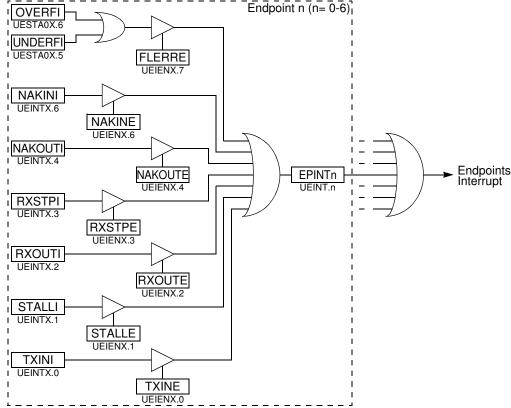

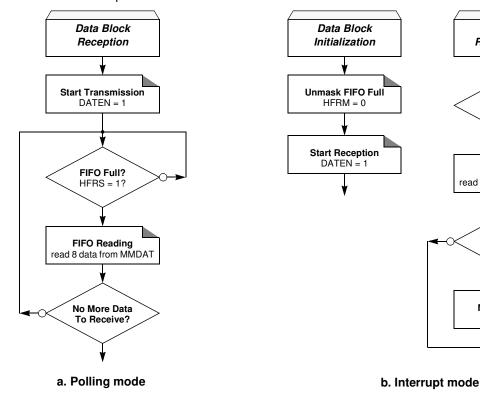

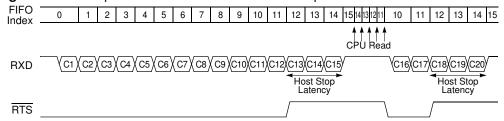

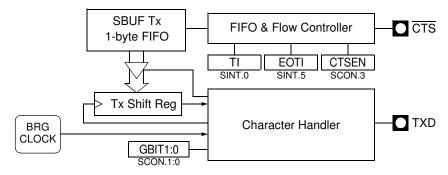

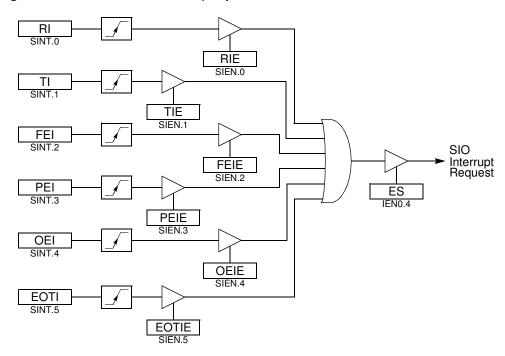

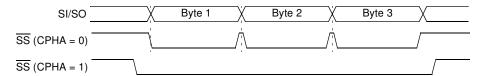

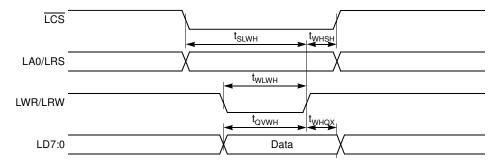

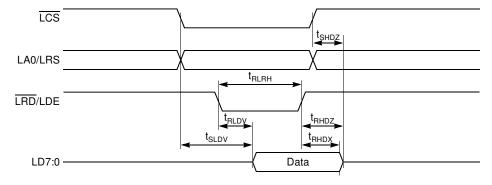

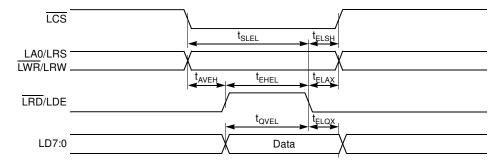

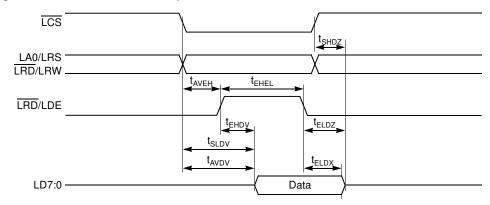

| 5                                    | -               | Reserved The value read from this bit is always 0. Do not set this bit.                                             |