## Features

- Single Chip All-in-one Design

- MIDI Control Processor, Serial and Parallel Interface

- Synthesis, General MIDI Wavetable Implementation

- General MIDI Compatible Effects: Reverb + Chorus

- Spatial Effect

- 4-band Stereo Equalizer

- Stereo DAC. DR: 86 dB min, THD+N: -80 dB max

- State of the art Synthesis for Products Providing Best Quality for Price

- 64-voice Polyphony (without effects)

- 38-voice Polyphony + Effects

- On-chip CleanWave<sup>™</sup> Wavetable Data, Firmware, RAM Delay Lines

- Audio Stereo Line Output

- Typical Applications: Battery Operated Musical Keyboards, Portable Phones, Karaokes

- QFN44 (7mm x 7mm) Package: Small Footprint, Small Pin Count

- Low Power

- 75 mW typ. Operating

- Single 3.3V or Single 1.8V Power Supply

- Built-in Power Switch and 3.3V to 1.8V Regulator

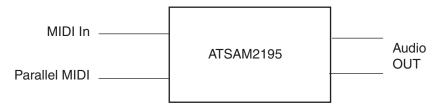

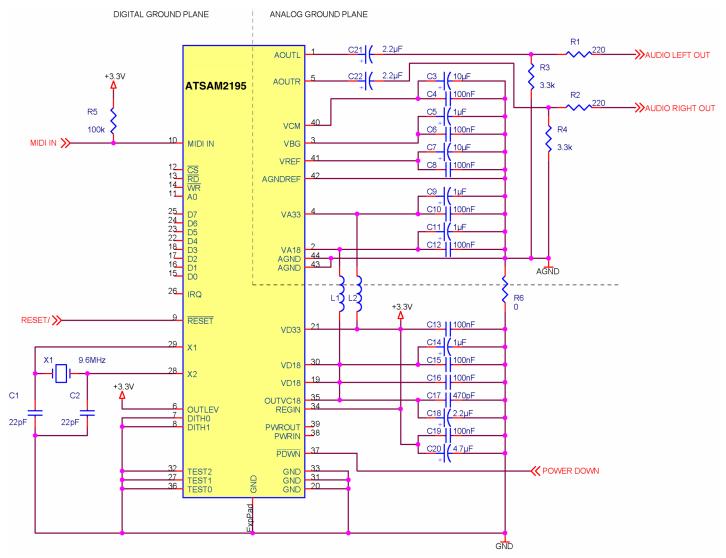

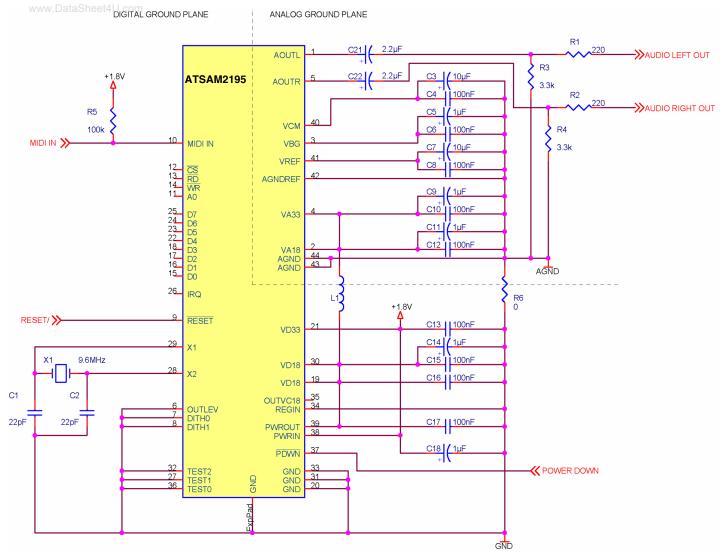

# 1. Typical Hardware Configuration

Figure 1-1. Typical Hardware Configuration

Audio Processing

ATSAM2195 Low-power Single Chip Synthesizer with Effects

6308A-DRMSD-10-May-07

### Pin Description 2.

#### Pins By Function – 44-lead QFN Package 2.1

#### Table 2-1. Power Supply Group

| Pin Name | Pin #           | Туре | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------|-----------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND      | 20, 31, 33      | PWR  | DIGITAL GROUND<br>All pins should be connected to a ground plane                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| GND      | exposed die pad | PWR  | DIGITAL GROUND<br>Ground supply; down bonded to the exposed die pad (heatsink). It is<br>recommended, but not obligatory, to connect this pad to a ground plane during<br>PCB layout                                                                                                                                                                                                                                                                                                                                                                                             |

| VD33     | 21              | PWR  | I/O POWER SUPPLY<br>This pin should be connected to a nominal 3.3V power for 3.3V single supply<br>applications.<br>This pin should be connected to a nominal 1.8V power for 1.8V single supply<br>applications                                                                                                                                                                                                                                                                                                                                                                  |

| VD18     | 19, 30          | PWR  | CORE POWER SUPPLY<br>These pins should be connected to nominal 1.8V.<br>3.3V single supply application: If the built-in regulator is used, then these pins<br>should be connected to the output of the regulator OUTVC18 (pin 35).<br>1.8V single supply application: If the built-in power switch is used for minimum<br>power down consumption, then all these pins should be connected to the output<br>of the power switch PWROUT (pin 39).                                                                                                                                  |

| AGND     | 43, 44          | PWR  | ANALOG GROUND<br>These pins should be connected to an analog ground plane                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| VA33     | 4               | PWR  | <ul> <li>DAC PERIPHERY ANALOG SUPPLY</li> <li>3.3V single supply application: This pin should be connected to a nominal 3.3V power through a serial inductor filter (better result) or a 10 ohm resistor.</li> <li>1.8V single supply application: This pin should be connected to a nominal 1.8V power through a serial inductor filter (better result) or a 10 ohm resistor.</li> </ul>                                                                                                                                                                                        |

| VA18     | 2               | PWR  | <ul> <li>DAC 1.8V ANALOG SUPPLY</li> <li>This pin should be connected to a clean 1.8V.</li> <li>3.3V single supply application: If the built-in regulator is used, then this pin should be connected to the output of the regulator OUTVC18 (pin 35) through a serial inductor filter (better result) or a 10 ohm resistor.</li> <li>1.8V single supply application: If the built-in power switch is used, then this pin should be connected to the output of the power switch PWROUT (pin 39) through a serial inductor filter (better result) or a 10 ohm resistor.</li> </ul> |

| REGIN    | 34              | PWR  | Regulator input<br>This pin should be connected to a nominal 3.3V power for 3.3V single supply<br>applications.<br>This pin should be grounded for 1.8V single supply applications                                                                                                                                                                                                                                                                                                                                                                                               |

| PWRIN    | 38              | PWR  | Power switch input.<br>This pin should be left not connected for 3.3V single supply applications.<br>This pin should connected to a 1.8V nominal power for 1.8V single supply<br>applications                                                                                                                                                                                                                                                                                                                                                                                    |

| Pin Name | Pin #                             | Туре | Function                                                                                                                                                                                                                                                                                   |

|----------|-----------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MIDI IN  | 10                                | IN   | Serial TTL MIDI IN. Connected to the built-in synthesizer at power-up or after MPU reset. Connected to the D0-D7 bus (read mode) when MPU switched to UART mode. This pin should be tied HIGH if not used.                                                                                 |

| D0-D7    | 15, 16, 17, 18,<br>22, 23, 24, 25 | I/O  | 8 bit bi-directional bus, under control of $\overline{CS}$ , $\overline{RD}$ , $\overline{WR}$ . These pins have a built-in pull down. They should be left unconnected if not used                                                                                                         |

| A0       | 11                                | IN   | Select data(0) or control(1) for write, data(0) or status(1) for read. This pin has a built-in pull-down. It should be left unconnected if not used.                                                                                                                                       |

| CS       | 12                                | IN   | Chip select, active low. This pin has a built-in pull up. It should be left unconnected if not used.                                                                                                                                                                                       |

| RD       | 13                                | IN   | Read, active low. When $\overline{CS}$ and $\overline{RD}$ are low, data(A0=0) or status(A0=1) is read on D0-D7. Read data is acknowledged on the rising edge of $\overline{RD}$ . This pin has a built-in pull up. It should be left unconnected if not used.                             |

| WR       | 14                                | IN   | Write, active low. When $\overline{\text{CS}}$ and $\overline{\text{WR}}$ are low, data (A0=0) or control (A0=1) is written from the D0-D7 bus to the ATSAM2195 on the rising edge of $\overline{\text{WR}}$ . This pin has a built-in pull up. It should be left unconnected if not used. |

| IRQ      | 26                                | OUT  | A rising edge indicates that a MIDI byte is available for read on D0-D7.<br>Acknowledged by reading the byte.                                                                                                                                                                              |

### Table 2-2. Serial MIDI, parallel MIDI (MPU-401)

### Table 2-3.Analog audio group

| Pin Name | Pin # | Туре | Function                                                                                                                       |

|----------|-------|------|--------------------------------------------------------------------------------------------------------------------------------|

| AGNDREF  | 42    | IN   | These pin is used as a reference by the internal DAC. It should be connected to a clean analog ground plane                    |

| VREF     | 41    | OUT  | Reference voltage. Generated on-chip. Should be stabilized by external capacitors 10 $\mu F$ // 100 nF to AGND.                |

| VCM      | 40    | OUT  | On-chip output stage common-mode voltage. Should be stabilized by external capacitors 10 $\mu F$ // 100 nF to AGND.            |

| VBG      | 3     | OUT  | Bandgap voltage. Can be stabilized by capacitors $1\mu F$ // 100 nF to AGND. Can be left unconnected for low-cost application. |

| AOUTL    | 1     | OUT  | Left channel audio output                                                                                                      |

| AOUTR    | 5     | OUT  | Right channel audio output                                                                                                     |

#### Table 2-4.Digital audio group

| Pin Name    | Pin # | Туре | Function                                                                                                                                                                       |

|-------------|-------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OUTLEV      | 6     | IN   | Selects the full scale output level for AOUTL and AOUTR.<br>OUTLEV = 0 for 1.1Vpp<br>OUTLEV = 1 for 2.2Vpp<br>If 1.8V single supply (VA33 = 1.8V), OUTLEV should be tied to 0. |

| DITH0-DITH1 | 7, 8  | IN   | Activate a dither signal to reduce eventual noise tones at the output. See Dither Modes Description.                                                                           |

# Table 2-5. Miscellaneous group

| Pin Name              | Pin #      | Туре | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------------|------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| X1-X2                 | 29, 28     | -    | 9.6 MHz crystal connection. An external 9.6 MHz clock can also be used on X1 (1.95Vpp max through 47 pF capacitor). X2 cannot be used to drive external circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| RESET                 | 9          | IN   | Reset input, active low. This is a Schmitt trigger input, allowing direct connection to an RC network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| OUTVC18               | 35         | PWR  | 3.3V to 1.8 V regulator output. When 3.3V single supply application this pin can be used to power VD18 pins, and VA18 pin through a serial inductor filter (better result) or a 10 ohm resistor. Decoupling capacitors 470 pF in parallel with 2.2 or 4.7 $\mu$ F must be connected between OUTVC18 and GND.                                                                                                                                                                                                                                                                                                                                         |

| PWROUT                | 39         | PWR  | Power switch output. When 1.8V single supply application this pin can be used to power VD18 pins, and VA18 pin through a serial inductor filter (better result) or a 10 ohm resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| PDWN                  | 37         | IN   | <ul> <li>Power down, active low. When power down is active, all digital outputs are set to logic level 0, D0-D7 bus is set in high Z, analog outputs decrease to 0V, the PLL and crystal oscillator are stopped.</li> <li>3.3V single supply application: If the built-in regulator is used then 1.8V supply is removed from the core. To exit from power down, PDWN must be set to VD33, then RESET applied. When unused this pin must be connected to VD33.</li> <li>1.8V single supply application: If the built-in power switch is used then 1.8V supply is removed from the core. To exit from power down, PDWN must be set to VD33.</li> </ul> |

| TEST0-TEST1-<br>TEST2 | 36, 27, 32 | IN   | Test pins. Should be grounded                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

### 2.2 Pinout By Pin Number - 44-lead QFN Package

|            | taSheet4U.com |

|------------|---------------|

| Table 2-6. | Pinout        |

| Pin# | Pin Name |

|------|----------|------|----------|------|----------|------|----------|

| 1    | AOUTL    | 12   | CS       | 23   | D5       | 34   | REGIN    |

| 2    | VA18     | 13   | RD       | 24   | D6       | 35   | OUTVC18  |

| 3    | VBG      | 14   | WR       | 25   | D7       | 36   | TEST0    |

| 4    | VA33     | 15   | D0       | 26   | IRQ      | 37   | PDWN     |

| 5    | AOUTR    | 16   | D1       | 27   | TEST1    | 38   | PWRIN    |

| 6    | OUTLEV   | 17   | D2       | 28   | X2       | 39   | PWROUT   |

| 7    | DITH0    | 18   | D3       | 29   | X1       | 40   | VCM      |

| 8    | DITH1    | 19   | VD18     | 30   | VD18     | 41   | VREF     |

| 9    | RESET    | 20   | GND      | 31   | GND      | 42   | AGNDREF  |

| 10   | MIDI IN  | 21   | VD33     | 32   | TEST2    | 43   | AGND     |

| 11   | A0       | 22   | D4       | 33   | GND      | 44   | AGND     |

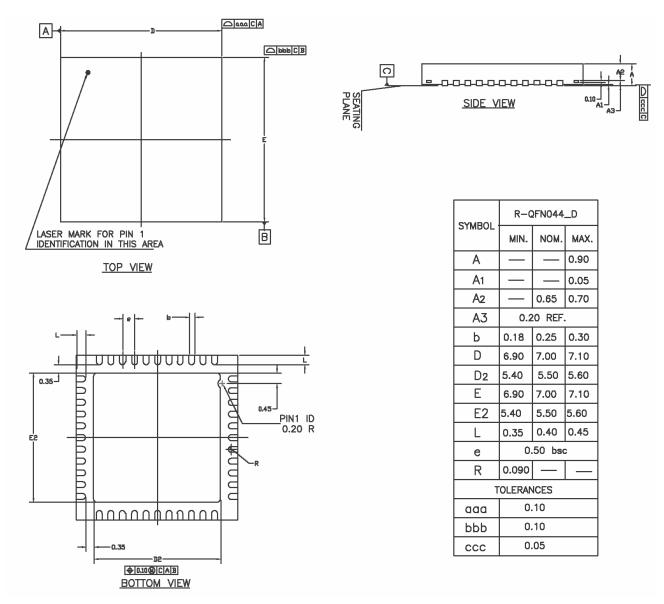

## 3. Mechanical Dimensions – 44-lead QFN Package

ww.DataSheet4U.com

Notes: 1. All package dimensions are in mm. 2. R-QFN044\_D - QFN

## 4. Marking

www.DataSheet4U.com

T Pin 1

### 5. Absolute Maximum Ratings

All voltages with respect to 0V, GND=0V.

#### Table 5-1. Absolute Maximum Ratings\*

| Temperature under bias55° C to +125° C                                         |

|--------------------------------------------------------------------------------|

| Storage Temperature65°C to +150°C                                              |

| Voltage on any Input Pins<br>except X10.3V to +VD33+0.3V                       |

| Voltage on X1                                                                  |

| Supply voltage (I/O) (VD33)0.3V to +3.6V                                       |

| Supply voltage (core) (VD18)0.3V to +1.95V                                     |

| Supply voltage (DAC analog 3.3V)<br>(VA33)0.3V to +3.6V                        |

| Supply voltage (DAC analog 1.8V)<br>(VA18)0.3V to +1.95V                       |

| Maximum IOL per I/O pin4 mA                                                    |

| Maximun IOH per I/O pin4 mA                                                    |

| Maximum Output current from PWROUT pin<br>(max duration = 1sec) (IPWRO)650 mA  |

| Maximum Output current from OUTVC18 pin<br>(max duration = 1sec) (IREGO)100 mA |

|                                                                                |

\*NOTICE: Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

e 5-2. Recommended Operating Conditions Table 5-2.

| Parameter                            | Symbol | Min  | Тур  | Max  | Unit |

|--------------------------------------|--------|------|------|------|------|

| Digital supply voltage: - OUTLEV = 1 | VD33   | 3    | 3.3  | 3.6  | V    |

| - OUTLEV = 0                         | VD33   | 1.65 | 1.8  | 1.95 | V    |

| Digital supply voltage               | VD18   | 1.65 | 1.8  | 1.95 | V    |

| Analog supply voltage: - OUTLEV = 1  | VA33   | 3    | 3.3  | 3.6  | V    |

| - OUTLEV = 0                         | VA33   | 1.65 | 1.8  | 1.95 | V    |

| Analog supply voltage                | VA18   | 1.65 | 1.8  | 1.95 | V    |

| Power switch supply                  | PWRIN  | 1.75 | 1.80 | 1.95 | V    |

| Regulator supply                     | REGIN  | 2.7  | 3.3  | 3.6  | V    |

| Power Switch output current          | IPWRO  | -    | -    | 217  | mA   |

| OUTVC18 output current               | IREGO  | -    | 60   | -    | mA   |

| Operating ambient temperature        | tA     | 0    | -    | +70  | °C   |

#### Digital Characteristics (TA=25°C, VD33=3.3V±10%, 1.65 V< VD18 < 1.95V) Table 5-3.

| Parameter                                            | Symbol | Min      | Тур | Max      | Unit |

|------------------------------------------------------|--------|----------|-----|----------|------|

| Low level input voltage (Except X1)                  | VIL    | -0.3     | -   | 0.8      | V    |

| High level input voltage (Except X1)                 | VIH    | 2        | -   | 3.6      | V    |

| Low level input voltage for X1                       | VIL    | -0.3     | -   | 0.3      | V    |

| High level input voltage for X1                      | VIH    | 1.2      | -   | VD18+0.3 | V    |

| Low level output voltage IOL=-2mA                    | VOL    | -        | -   | 0.4      | V    |

| High level output voltage IOH=2mA                    | VOH    | VD33-0.4 | -   | -        | V    |

| Power consumption (crystal freq.=9.6MHz)             | -      | -        | 75  |          | mW   |

| Power down supply current (using power switch)       | -      |          | <1  |          | μA   |

| Drop down from PWRIN to PWROUT<br>(at IPWRO = 180mA) | -      |          |     | 0.1      | v    |

| Voltage on OUTVC18 (at IREGO = 60mA)                 | VREGO  | 1.65     | 1.8 | 1.95     | V    |

www.DataSheet4U.com

Table 5-4.

Analog Characteristics (TA=25°C)

| Parameter                                               | Symbol  | Min  | Тур   | Max  | Unit    |

|---------------------------------------------------------|---------|------|-------|------|---------|

| Total Harmonic Distortion + Noise (at 0 dB, full scale) |         |      |       |      |         |

| VA33 = 3.3V, OUTLEV = 1                                 | THD + N | -    | -     | -80  | dB      |

| VA33 = 1.8V, OUTLEV = 0                                 | THD + N | -    | -     | -76  | dB      |

| Dynamic Range (A-Weighted)                              |         |      |       |      |         |

| VA33 = 3.3V, OUTLEV = 1                                 | DR      | 86   | -     | -    | dB      |

| VA33 = 1.8V, OUTLEV = 0                                 | DR      | 80   | -     | -    | dB      |

| Inter-channel isolation (1kHz)                          |         |      |       |      |         |

| VA33 = 3.3V, OUTLEV = 1                                 |         | 83   | -     | -    | dB      |

| VA33 = 1.8V, OUTLEV = 0                                 | -       | 80   |       |      | uБ      |

| Inter-channel gain mismatch                             | -       | -0.1 | -     | +01  | dB      |

| Gain drift                                              | -       | -    | ± 100 | -    | ppm/ °C |

| Full-scale output voltage                               |         |      |       |      |         |

| VA33 = 3.3V, OUTLEV = 1                                 | -       | 2.04 | 2.2   | 2.36 | Vpp     |

| VA33 = 1.8V or 3.3V, OUTLEV = 0                         | -       | 1.02 | 1.1   | 1.18 | Vpp     |

| VCM Maximum allowable DC current source                 | -       | -    | -     | 0.1  | mA      |

| VCM Nominal voltage                                     |         |      |       |      |         |

| VA33 = 3.3V, OUTLEV = 1                                 | -       | 1.38 | 1.5   | 1.58 | V       |

| VA33 = 1.8V or 3.3V, OUTLEV = 0                         | -       | 0.74 | 0.80  | 0.84 | V       |

| AC-Load resistance                                      | RL      | 3    | 4.7   |      | kΩ      |

| Load capacitance                                        | CL      | -    | 10    | 100  | pF      |

### Table 5-5.Filter Characteristics (TA=25°C)

| Parameter                                  | Symbol | Min   | Тур   | Max   | Unit    |

|--------------------------------------------|--------|-------|-------|-------|---------|

| Frequency response (10Hz – 17kHz)          | -      | -0.05 | -     | +0.05 | dB      |

| Passband                                   |        |       |       |       |         |

| to -0.1dB corner                           | PB     | 0     | -     | 17    | kHz     |

| to -6 dB corner                            | PB     | 0     | -     | 18.74 | kHz     |

| Stopband                                   | SB     |       | 20.49 |       | kHz     |

| Stopband attenuation (20.49kHz – 112.5kHz) | SA     | 65    | -     | -     | dB      |

| Group delay                                | GD     |       | 1.12  |       | ms      |

| Gain drift                                 | -      | -     | ± 100 | -     | ppm/ °C |

### 6. Timings

/ww.DataSheet4U.com

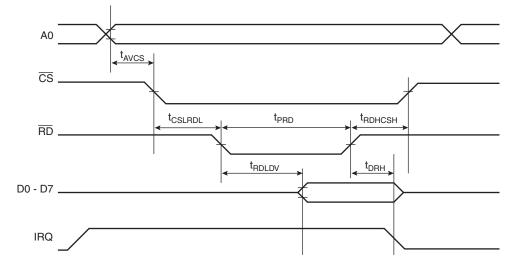

### 6.1 Slave 8-bit Parallel Interface

This interface is typically used to connect the chip to an host processor.

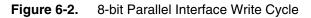

Figure 6-1. 8-bit Parallel Interface Read Cycle

#### Table 6-1. Timings

| J                                            |                     |     |     |     |      |

|----------------------------------------------|---------------------|-----|-----|-----|------|

| Parameter                                    | Symbol              | Min | Тур | Мах | Unit |

| Address valid to chip select low             | t <sub>AVCS</sub>   | 0   | -   | -   | ns   |

| Chip select low to RD low                    | t <sub>CSLRDL</sub> | 5   | -   | -   | ns   |

| $\overline{RD}$ high to $\overline{CS}$ high | t <sub>RDHCSH</sub> | 5   | -   | -   | ns   |

| RD pulse width                               | t <sub>PRD</sub>    | 50  | -   | -   | ns   |

| Data out valid from RD                       | t <sub>RDLDV</sub>  | -   | -   | 20  | ns   |

| Data out hold from RD                        | t <sub>DRH</sub>    | 5   | -   | 10  | ns   |

#### Table 6-1.Timings

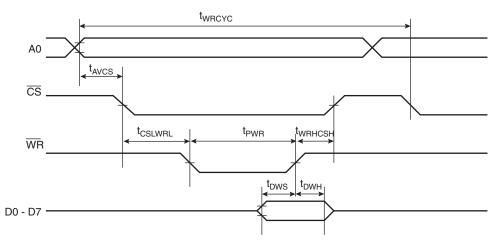

| Chip select low to $\overline{WR}$ low | t <sub>CSLRWRL</sub> | 5   | - | - | ns |

|----------------------------------------|----------------------|-----|---|---|----|

| WR high to CS high                     | t <sub>WRHCSH</sub>  | 5   | - | - | ns |

| WR pulse width                         | t <sub>PWR</sub>     | 50  | - | - | ns |

| Write data setup time                  | t <sub>DWS</sub>     | 10  | - | - | ns |

| Write data hold time                   | t <sub>DWH</sub>     | 0   | - | - | ns |

| Write cycle                            | t <sub>WRCYC</sub>   | 3.5 |   |   | μs |

Notes: 1. When data is pending on parallel port, the host should read it within 1 ms. If not, the parallel port is deactivated. Reactivating the port can be done with the following control sequence: 0FFh (Closed port), 03FFh (Open port).

2. For safe operation, write cycle time should not be lower than 3.5  $\mu s.$

### 7. Reset and Power Down

During power-up, the RESET input should be held low until the crystal oscillator and PLL are stabilized, which can take about 20 ms. A typical RC/diode power-up network can be used.

After RESET, the ATSAM2195 enters an initialization routine. It takes around 50 ms before a MIDI IN or MPU message can be processed.

Audio begins after 500 ms, maximum.

To enter power-down, Reset should be held low 500 ms min and then PDWN asserted low.

In Power-down mode, the crystal oscillator and PLL are stopped. The chip enters a deep power down sleep mode.

To exit power down, PDWN has to be asserted high, then RESET applied.

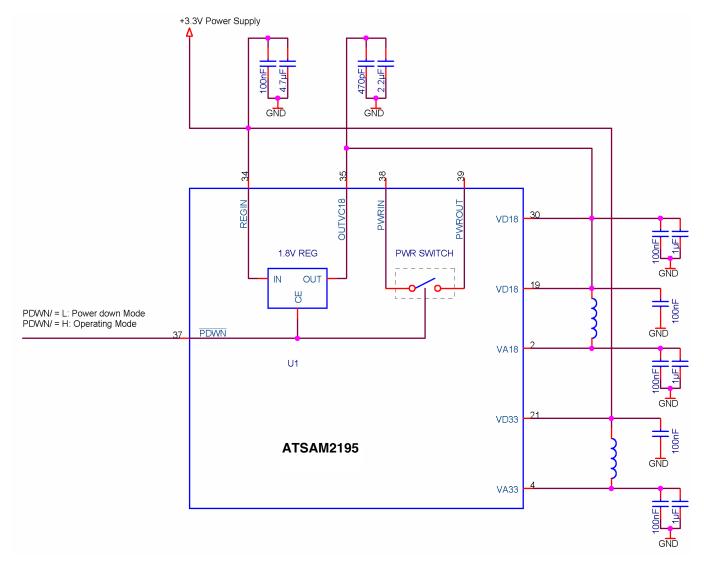

### 7.1 3.3V Single Supply Application

Power down mode is managed by the internal regulator. The equivalent schematic and standard connection is shown on the diagram below.

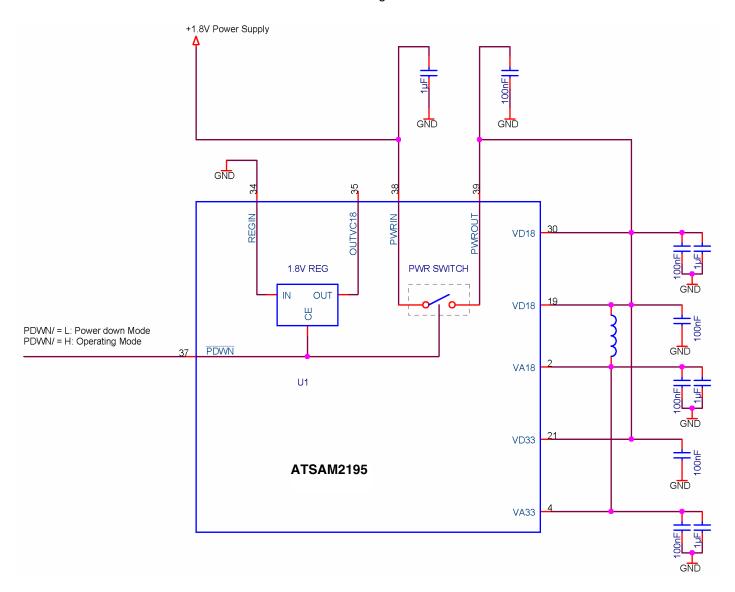

### 7.2 1.8V Single Supply Application

Power down mode is managed by the internal power switch. The equivalent schematic and standard connection is shown on the diagram below.

### 8. Dither Modes Description (Dithering Signal Programmability)

ww.DataSheet4U.com

Dithering is used to attenuate the so-called idle tones caused by correlation between DAC input signal and truncation noise. This correlation manifests as spurious signals in the audio band and hence can be perceived by the user. The addition of a random digital signal to the truncator input in the digital modulator has been proven to be very effective to reduce the presence of idle tones. However, this is actually a noisy signal so that its power must be traded-off with the required dynamic range. For better control, the ATSAM2195 allows programmability of the dithering signal power as shown below.

| dith[1:0] | Mode description              | Comments                                                              |

|-----------|-------------------------------|-----------------------------------------------------------------------|

| 00        | No dither                     |                                                                       |

| 01        | Dither signal power = -30dBFS | Minimum recommended dither.                                           |

| 10        | Dither signal power = -27dBFS | Typical value                                                         |

| 11        | Dither signal power = -24dBFS | Maximum recommended value. Above it dither noise may become dominant. |

### 9. System Design

ww.DataSheet4U.com

The schematics of this section are the reference designs for applications with ATSAM2195. The conformity with these schematics ensures the best performance.

### 9.1 3.3V Single Supply Application

# ATSAM2195

### 9.2 1.8V Single Supply Application

### 10. Recommended Board Layout

Like all HCMOS high integration ICs, following simple rules of board layout is mandatory for reliable operations:

• GND, VD33, VD18, VA33, VA18 distribution and decoupling

All GND, VD33, VD18, VA33, VA18 pins should be connected. A GND plane is strongly recommended below the ATSAM2195. The board GND, VD33, VD18 distribution should be in grid form. Recommended decoupling is 0.1  $\mu$ F at each VD33, VD18, VA33, VA18 pin of the IC with an additional 1 $\mu$ F-T between pins 30 and 31. Decoupling capacitors should be implemented close to the IC.

Crystal

The paths between the crystal and the ATSAM2195 should be short and shielded. The ground return from the crystal compensation capacitors should be pin 31.

Analog section

A specific AGND ground plane should be provided, which connects by a single trace to the GND ground. No digital signals should cross the AGND plane.

#### Headquarters

Atmel Corporation 2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 487-2600

### International

#### Atmel Asia

Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong Kong Tel: (852) 2721-9778 Fax: (852) 2722-1369

#### Atmel Europe

Le Krebs 8, rue Jean-Pierre Timbaud BP 309 78054 Saint-Quentin-en-Yvelines Cedex France Tel: (33) 1-30-60-70-00 Fax: (33) 1-30-60-71-11

#### Atmel Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

### Operations

Memory 2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

#### Microcontrollers

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

La Chantrerie BP 70602 44306 Nantes Cedex 3, France Tel: (33) 2-40-18-18-18 Fax: (33) 2-40-18-19-60

#### ASIC/ASSP/Smart Cards

Zone Industrielle 13106 Rousset Cedex, France Tel: (33) 4-42-53-60-00 Fax: (33) 4-42-53-60-01

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

Scottish Enterprise Technology Park Maxwell Building East Kilbride G75 0QR, Scotland Tel: (44) 1355-803-000 Fax: (44) 1355-242-743 **RF**/Automotive

Theresienstrasse 2 Postfach 3535 74025 Heilbronn, Germany Tel: (49) 71-31-67-0 Fax: (49) 71-31-67-2340

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

#### Biometrics

Avenue de Rochepleine BP 123 38521 Saint-Egreve Cedex, France Tel: (33) 4-76-58-47-50 Fax: (33) 4-76-58-47-60

Literature Requests www.atmel.com/literature

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL'S TERMS AND CONDI-TIONS OF SALE LOCATED ON ATMEL'S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDEN-TAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel's products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

© 2007 Atmel Corporation. All rights reserved. Atmel<sup>®</sup>, logo and combinations thereof, and others are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.