#### **Features**

- Eight DSPs and 24-bit Audio Router On-chip

- 32 kHz to 96 kHz Sampling Rate

- 16-bit Microcontroller On-chip

- Variety of I/Os, including SmartMedia® and DataFlash®

- Embedded RAM for Single Chip Operation (768 Kbits)

- · Warm Start Power-down

- 1µA Typical Deep Power-down, 0.5 mW/MIPS Typical Operating

- External Flash/ROM Capability

- Available in a 100-lead LQFP Package

- Ideal for Real-time Audio Applications

- Wavetable Synthesis

- MP3 Decoding

- Effect Processing (Reverb, Echo, Chorus, Equalizer)

- Filtering, Sampling Rate Conversion

- Typical Applications: Karaoke, Professional Audio, Cellular Phones, Musical Instruments, Consumer Electronics

### 1. Description

The ATSAM3308B is a member of the new ATSAM3000 family that uses the DSP array technology. The ATSAM3308B includes eight 24-bit DSPs, a 24-bit Audio Router and a general-purpose 16-bit on-chip CISC microcontroller. Its high performance and flexibility with 8-input/8-output channels enables implementation of audio applications in professional-quality sound production such as MP3 decoding with time stretch and pitch control, concurrent Wavetable synthesis, effect processing and digital mixing. A variety of I/Os, including external Wave ROM, SmartMedia<sup>®</sup> and DataFlash<sup>®</sup> are provided. Sampling rates up to 96 kHz at 24 bits are supported.

# Audio Processing

# ATSAM3308B Multi-purpose Audio DSP

6090D-DRMSD-12-Feb-07

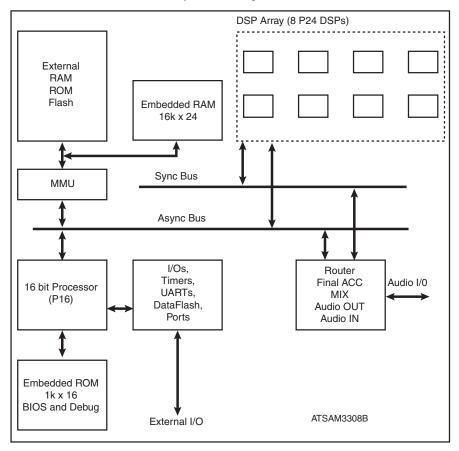

### 2. DSP Array Block Diagram

www.DataSheet4U.com

Figure 2-1. ATSAM3308B DSP Array Block Diagram

### 3. Functional Description

### 3.1 DSP Array

The ATSAM3308B includes eight on-chip DSPs.

Each DSP (P24) is built around a  $2k \times 24$  RAM and a  $1k \times 24$  ROM. The RAM contains both data and P24 instructions, the ROM contains typical coefficients such as FFT cosines and windowing. A P24 sends and receives audio samples through the Sync Bus. It can request external data such as compressed audio through the Async Bus. Each P24 RAM can be accessed through the Async Bus.

Each P24 is capable of typical MAC operation loops, including auto-indexing, bit reverse and butterfly (multiplication of complex numbers). It also includes specialized audio instructions such as state variable IIR filtering, envelope generation, linear interpolation and wavetable loop.

One P24 is sufficient for processing one channel of MP3 data pump, implementing a multi-tap delay line or a multi-tap transversal filter. A single P24 is also capable of generating twelve voices of wavetable sound at 32 kHz sampling rate (8 voices at 48 kHz), including sample cache, pitch control, 2nd order filter and two envelope generators.

#### 3.2 Sync Bus

www.DataSheet4U.com

The Sync Bus transfers data on a frame basis, typical frame rates being 32, 44.1, 48 or 96 kHz. Each frame is divided into 64 time slots. Each slot is divided into 4 bus cycles. Each P24 is assigned a hardwired time slot (8 to 63), during which it may provide 24-bit data to the bus (up to 4 data samples). Each P24 can read data on the bus at any time, allowing inter P24 communication at the current sampling rate. Slots 0 to 7 are reserved for a specific router DSP, which also handles audio out, audio in, and remix send.

#### 3.3 Async Bus

The Async Bus has 24-bit data inside the chip and 16-bit data outside.

The P16 processor normally masters the Async Bus; it can read/write the P24 memories and the external or embedded ROM/RAM. However, each P24 can request a bus master cycle for accessing external ROM/RAM or other P24 memories. This allows efficient intercommunication between several P24s on asynchronous block basis. Specific P24 instructions FLOAT and FIX convert fixed-point DSP data to floating-point 16 bits. This allows for 20-bit audio dynamic range when using 16-bit external memory.

#### 3.4 16-bit Processor

The P16 processor is widely used in ATSAM products. Using the P16 keeps large firmware investments from the ATSAM97xx series. A built-in ROM, connected to the P16 holds basic input/output software (BIOS) for peripherals such as UART, DataFlash, SmartMedia and MPU, as well as a debugger that uses a dedicated asynchronous serial line. The firmware can reside on external parallel ROM/Flash or it can be downloaded at power-up into the built-in 16k x 24 RAM from serial EEPROM, DataFlash, SmartMedia or host.

### 3.5 MMU (Memory Management Unit)

The MMU handles transfer requests between the external or embedded RAM/ROM, the P16 and the P24s through the Async Bus. The ATSAM3308B includes 16k x 24 RAM on chip.

#### 3.6 Router: Final ACC, MIX, Audio Out, Audio In

This block includes RAM (accessed through the Async Bus) that defines the routing from the Sync Bus to/from the Audio I/O or back to the Sync Bus (mix send). It takes care of mix and accumulation from Sync Bus samples. Eight channels of audio in and eight channels of audio out are provided (4-stereo in/out, I2S format). The stereo audio in channels may have a different sampling rate than the audio out channels. In this case, one (or more) P24 takes care of sampling rate conversion.

#### 3.7 I/O

The ATSAM3308B includes very versatile I/Os, that share common pins for reduced pin count and small IC footprint. Most I/Os, when not used for a specific function, remain available as firmware controlled general-purpose pins.

The following peripherals are included on chip:

- 2 x 8-bit timers

- 2 x 16-bit timers

- Parallel slave 8-bit port, MPU401 compatible

- Parallel master 8-bit port, for connection to SmartMedia and/or LCD display, switches, etc.

www.DataSheet4LL.com

- 2 x asynchronous bidirectional serial ports

- Synchronous serial slave port (SPI type host connection).

- SPI master bidirectional port for EEPROM or DataFlash connection.

- Firmware controlled I/O pins.

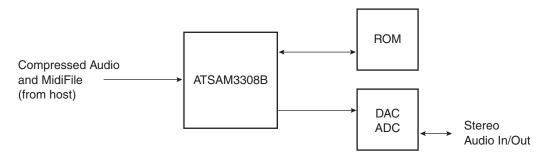

### 4. Typical Application Examples

### 4.1 Host-controlled MP3 + High Quality Wavetable Player

Figure 4-1. Host-controlled MP3 + High Quality Wavetable Player

- Concurrent MP3 + wavetable

- Legendary Dream® high quality wavetable sound

- Typical polyphony:

- 56 voices with effects (reverb, chorus, etc.) @48 kHz sampling rate

- MP3 decode + 32 voices with effects @48 kHz sampling rate

- External wavetable ROM/Flash choice from 4 Mbits to 128 Mbits

- Choice of host communication interfaces

- 8-bit parallel

- Asynchronous serial (MIDI)

- Synchronous serial (SPI)

- Built-in Standard Midi file player (SMF) dramatically reduces host load

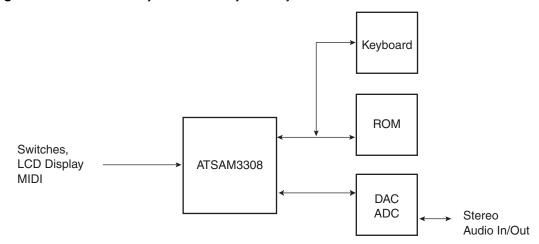

### 4.2 Musical Keyboard with Key Velocity

www.DataSheet4U.com

Figure 4-2. Musical Keyboard with Key Velocity

- Up to 64-voice polyphony with effects

- Choice of GM+ sampled sounds from 4 Mbits to 64 Mbits

- Maximum external memory addressing range: 128 Mbits

### 5. DSP Capacity and I/O Configuration

#### 5.1 DSP Considerations

The ATSAM3308B includes 8 x P24 DSPs. Table 5-1 below lists the performance achievable by the P24.

Table 5-1. P24 Performance

| Function                             | P24s Required |

|--------------------------------------|---------------|

| MP3 decode                           | 3             |

| 12-voice wavetable synthesis @32 kHz | 1             |

| 8-voice wavetable synthesis @48 kHz  | 1             |

| Stereo reverb and chorus @48 kHz     | 1             |

| Stereo 31-band equalizer @48 kHz     | 3             |

The ATSAM3308B runs firmware directly from an external ROM/Flash memory. It may also run firmware from local RAM, thus freeing many I/O pins, which can then be used for application dependent functions. The ATSAM3308B is the ideal choice when wavetable synthesis or many I/O pins are required.

#### 5.2 I/O Selection Considerations

I/Os are organized in groups, which can be mutually exclusive because they share the same IC pins (please refer to the pinout to identify the exclusions). The two main types of operation are host controlled and stand-alone.

#### 5.2.1 Host-controlled Operation

www.DataSheet4U.com There are three main possible ways of communication with a host processor:

- 8-bit parallel MPU type bidirectional interface signals: D7 D0, CS, WR, RD, A0, IRQ

- Asynchronous serial, MIDI\_IN and optionally MIDI\_OUT

- Synchronous serial signals: SDIN, SCLK, SYNC, INT

#### 5.2.2 Stand-alone Operation

Possible stand-alone modes are:

- Firmware into external ROM or Flash memory

- Firmware into external EEPROM or DataFlash

- Firmware into external SmartMedia. In this case, the firmware should reside in the SmartMedia reserved sectors starting at sector # 1.

#### 6. Pinout

#### 6.1 Pin Description

In the Pin Description table below:

- Identical sharing number indicates multifunction pins.

- Pd indicates a pin with built-in pull-down resistor.

- Pu indicates a pin with built-in pull-up resistor.

Table 6-1. Pinout by Pin Name

| Pin Name    | Pin Number                           | Туре | Sharing | Description                                                                                                                                                                                                 |

|-------------|--------------------------------------|------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND         | 9, 22, 30, 41, 56, 70,<br>75, 87, 97 | PWR  | _       | Digital ground. All of these pins should be returned to a ground plane.                                                                                                                                     |

| VC18        | 20, 47, 73, 99                       | PWR  | -       | Core power. All of these pins should be returned to nominal 1.8V or to PWROUT if the built-in power switch is used.                                                                                         |

| VC33        | 13, 50, 83                           | PWR  | _       | Periphery power. All these pins should be returned to nominal 3.3V.                                                                                                                                         |

| PWRIN       | 29                                   | PWR  | _       | Power switch input; should be returned to nominal 1.8V even if the power switch is not used.                                                                                                                |

| PWROUT      | 28                                   | PWR  | -       | Power switch output; should be connected to all VC18 pins if the power switch is used                                                                                                                       |

| D7 - D0     | 96, 95, 91, 90, 82,<br>81, 77, 76    | I/O  | 1       | Slave 8-bit interface data. Output if $\overline{CS}$ and $\overline{RD}$ are low (read from chip), input if $\overline{CS}$ and $\overline{WR}$ are low (write to chip). Type of data defined by A0 input. |

| 1/07 - 1/00 | 96, 95, 91, 90, 82,<br>81, 77, 76    | I/O  | 1       | SmartMedia data or other peripheral data                                                                                                                                                                    |

| P0.7 - P0.0 | 96, 95, 91, 90, 82,<br>81, 77, 76    | I/O  | 1       | General-purpose I/O; can be programmed individually as input or output.                                                                                                                                     |

| CLAD3 - 0   | 96, 95, 91, 90                       | In   | 1       | Optional bit clocks for digital audio input. Used for sampling rate conversion for external incoming digital audio such as AES/BEU or S/Pdif.                                                               |

Table 6-1.

Pinout by Pin Name (Continued)

| Pin Name  | Pin Number     | Туре | Sharing | Description                                                                                                                                                                           |  |  |

|-----------|----------------|------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| WSAD3 - 0 | 82, 81, 77, 76 | In   | 1       | Optional word selects for digital audio input. Used for sampling rate conversion for external incoming digital audio such as AES/BEU or S/Pdif.                                       |  |  |

| A0        | 98             | In   | 2       | Slave 8-bit interface address. Indicates data/status or data/ctrl transfetype ( $\overline{\text{CS}}/\overline{\text{RD}}$ , low or $\overline{\text{CS}}/\overline{\text{WR}}$ low) |  |  |

| SMPD      | 98             | In   | 2       | SmartMedia presence detect                                                                                                                                                            |  |  |

| P0.10     | 98             | In   | 2       | General-purpose input pin                                                                                                                                                             |  |  |

| SCLK      | 98             | In   | 2       | Serial slave synchronous interface input clock                                                                                                                                        |  |  |

| CS        | 100            | In   | 3       | Slave 8-bit interface chip select, active low.                                                                                                                                        |  |  |

| P0.11     | 100            | In   | 3       | General-purpose input pin                                                                                                                                                             |  |  |

| SYNC      | 100            | In   | 3       | Serial slave synchronous interface input sync signal                                                                                                                                  |  |  |

| WR        | 1              | In   | 4       | Slave 8-bit interface write, active low. D7 - D0 data is sampled by chip on WR rising edge if CS is low                                                                               |  |  |

| SMC       | 1              | In   | 4       | SmartMedia configuration. This pin is sensed after power-up. If found low, it is assumed that a SmartMedia connector is present. The built-in firmware will wait for SmartMedia SMPD. |  |  |

| P0.12     | 1              | In   | 4       | General-purpose input pin                                                                                                                                                             |  |  |

| RD        | 2              | In   | 5       | Slave 8-bit interface read, active low. D7 - D0 data is output when $\overline{\text{RD}}$ goes low and $\overline{\text{CS}}$ is low                                                 |  |  |

| RIB       | 2              | In   | 5       | SmartMedia Ready Busy/ status                                                                                                                                                         |  |  |

| P0.13     | 2              | In   | 5       | General-purpose input pin                                                                                                                                                             |  |  |

| IRQ       | 8              | Out  | 6       | Slave 8-bit interface interrupt request. High when data is ready to be transferred from chip to host. Reset by a read from host $(\overline{CS} = 0 \text{ and } \overline{RD} = 0)$  |  |  |

| SMRE      | 8              | Out  | 6       | SmartMedia read enable (RE), active low                                                                                                                                               |  |  |

| FS0       | 8              | In   | 6       | Frequency sense, sensed at power up. Together with FS1, allows the firmware to know the operating frequency of the chip (see FS1).                                                    |  |  |

| P0.8      | 8              | I/O  | 6       | General-purpose I/O pin                                                                                                                                                               |  |  |

| INT       | 8              | Out  | 6       | Serial slave synchronous interface data request, active low.                                                                                                                          |  |  |

| MIDI_IN   | 17             | In   | 7       | Serial MIDI in                                                                                                                                                                        |  |  |

| P0.14     | 17             | In   | 7       | General-purpose input pin                                                                                                                                                             |  |  |

| SDIN      | 17             | In   | 7       | Serial slave synchronous interface input data                                                                                                                                         |  |  |

| MIDI_OUT  | 18             | Out  | 8       | Serial MIDI out                                                                                                                                                                       |  |  |

| FS1       | 18             | In   | 8       | Frequency sense, sensed at power up. FS1/FS0 allow firmware to know operating frequency of chip as follows:  00 6.9552 MHz  01 9.6 MHz  10 11.2896 MHz  11 12.288 MHz                 |  |  |

| P0.9      | 18             | I/O  | 8       | General-purpose I/O                                                                                                                                                                   |  |  |

| DABD3 - 0 | 67, 66, 65, 64 | Out  | _       | Four stereo channels of digital audio output, I2S format                                                                                                                              |  |  |

Table 6-1.

Pinout by Pin Name (Continued)

| Pin Name        | Pin Number                                                           | Туре     | Sharing | Description                                                                                                                                                                                                                                              |

|-----------------|----------------------------------------------------------------------|----------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLBD            | 6                                                                    | Out      | -       | Audio bit clock for DABD3 - 0. Audio bit clock for DAAD3 - 0 if the corresponding CLAD3 - 0 is not used.                                                                                                                                                 |

| WSBD            | 7                                                                    | Out      | -       | Audio left/right channel select for DABD3 - 0. Audio left/right channel for DAAD3 - 0 if the corresponding WSAD3 - 0 is not used.                                                                                                                        |

| CKOUT           | 5                                                                    | Out      | 1       | External DAC/Codec master clock. Same frequency as X2 pin. Can be programmed to be 128xFs, 192xFs, 256xFs, 384xFs, where Fs is the DAC/Codec sampling rate.                                                                                              |

| DAAD0           | 54                                                                   | ln       | 9       | Stereo audio data input, I2S format. Can operate on CLBD master rate or CLAD0 external rate when sampling rate conversion is requested.                                                                                                                  |

| P0.15           | 54                                                                   | In       | 9       | General-purpose input pin                                                                                                                                                                                                                                |

| DAAD3 - 1       | 60, 59, 55                                                           | In<br>Pd | -       | Three additional channels of stereo audio input, I2S format. Can individually operate on CLBD master rate or corresponding CLAD3 - 1 when sampling rate conversion is requested.  DAAD3 - 1 have built-in pull-downs. They may be left open if not used. |

| MUTE            | 19                                                                   | I/O      | 10      | External DAC/Codec Mute. Sensed at power up. If found high, then MUTE becomes an active high output. If found low, then MUTE becomes an active low output.                                                                                               |

| P1.6            | 19                                                                   | I/O      | 10      | General-purpose I/O pin                                                                                                                                                                                                                                  |

| WA21            | 45                                                                   | Out      | 11      | External memory address bit, extension to 64 Mbits                                                                                                                                                                                                       |

| SMCE            | 45                                                                   | Out      | 11      | SmartMedia chip enable (CE), active low                                                                                                                                                                                                                  |

| P1.5            | 45                                                                   | I/O      | 11      | General-purpose I/O pin                                                                                                                                                                                                                                  |

| WA20            | 44                                                                   | Out      | 12      | External memory address bit, extension to 32 Mbits                                                                                                                                                                                                       |

| SMALE           | 44                                                                   | Out      | 12      | SmartMedia address latch enable (ALE)                                                                                                                                                                                                                    |

| P1.4            | 44                                                                   | I/O      | 12      | General-purpose I/O pin                                                                                                                                                                                                                                  |

| WA19            | 43                                                                   | Out      | 13      | External memory address bit, extension to 16 Mbits                                                                                                                                                                                                       |

| SMWE            | 43                                                                   | Out      | 13      | SmartMedia write enable (WE), active low                                                                                                                                                                                                                 |

| P1.3            | 43                                                                   | I/O      | 13      | General-purpose I/O pin                                                                                                                                                                                                                                  |

| WA18            | 42                                                                   | Out      | 14      | External memory address bit, extension to 8 Mbits                                                                                                                                                                                                        |

| SMCLE           | 42                                                                   | Out      | 14      | SmartMedia command latch enable (CLE)                                                                                                                                                                                                                    |

| P1.2            | 42                                                                   | I/O      | 14      | General-purpose I/O pin                                                                                                                                                                                                                                  |

| WA17 –<br>WA16  | 58, 57                                                               | Out      | 15      | External memory address bits, extension to 2 and 4 Mbits                                                                                                                                                                                                 |

| P1.1 – P1.0     | 58, 57                                                               | I/O      | 15      | General-purpose I/O pins                                                                                                                                                                                                                                 |

| WA15 –<br>WA0   | 53, 51, 40, 39, 38,<br>37, 36, 27, 26, 21,<br>16, 15, 14, 12, 11, 10 | Out      | 16      | External memory address bits, up to 1 MBits (64K x 16)                                                                                                                                                                                                   |

| P2.15 –<br>P2.0 | 53, 51, 40, 39, 38,<br>37, 36, 27, 26, 21,<br>16, 15, 14, 12, 11, 10 | I/O      | 16      | General-purpose I/O pins                                                                                                                                                                                                                                 |

Table 6-1.

Pinout by Pin Name (Continued)

| Pin Name        | Pin Number                                                              | Туре      | Sharing | Description                                                                                                                                                                                                                                                                                      |

|-----------------|-------------------------------------------------------------------------|-----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WD15 –<br>WD0   | 94, 93, 92, 89, 88,<br>86, 85, 84, 80, 79,<br>78, 69, 68, 63, 62,<br>61 | I/O       | 17      | External memory data                                                                                                                                                                                                                                                                             |

| P3.15 –<br>P3.0 | 94, 93, 92, 89, 88,<br>86, 85, 84, 80, 79,<br>78, 69, 68, 63, 62,<br>61 | I/O       | 17      | General-purpose I/O pins                                                                                                                                                                                                                                                                         |

| WCS1            | 3                                                                       | Out       | 18      | External memory chip select 1, active low. Pre-decode for an external RAM/Flash/ROM at address 200:0000H.                                                                                                                                                                                        |

| P1.10           | 3                                                                       | I/O       | 18      | General-purpose I/O pin                                                                                                                                                                                                                                                                          |

| WCS0            | 4                                                                       | Out       | 19      | External memory chip select 2, active low. Pre-decode for an external RAM/Flash/ROM at address 000:0000H                                                                                                                                                                                         |

| P1.9            | 4                                                                       | I/O       | 19      | General-purpose I/O pin                                                                                                                                                                                                                                                                          |

| WOE             | 48                                                                      | Out       | 20      | External memory output enable, active low                                                                                                                                                                                                                                                        |

| P1.8            | 48                                                                      | I/O       | 20      | General-purpose I/O pin                                                                                                                                                                                                                                                                          |

| WWE             | 49                                                                      | Out       | 21      | External memory write enable, active low                                                                                                                                                                                                                                                         |

| P1.7            | 49                                                                      | I/O       | 21      | General-purpose I/O pin                                                                                                                                                                                                                                                                          |

| DFCS            | 23                                                                      | Out       | -       | DataFlash chip select                                                                                                                                                                                                                                                                            |

| DFSI            | 25                                                                      | Out       | -       | DataFlash serial input (to DataFlash)                                                                                                                                                                                                                                                            |

| DFSO            | 32                                                                      | In<br>Pd  | -       | DataFlash serial output (from DataFlash). This pin has a built-in pulldown. It may be left open if not used.                                                                                                                                                                                     |

| DFSCK           | 24                                                                      | Out       | -       | DataFlash data clock                                                                                                                                                                                                                                                                             |

| P1.15           | 46                                                                      | I/O<br>Pu | -       | General-purpose I/O pin. This pin has built-in pull-up. It may be left open if not used.                                                                                                                                                                                                         |

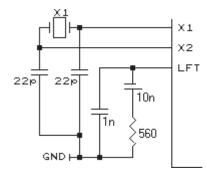

| X1 – X2         | 72,71                                                                   | -         | -       | External crystal connection. Standard frequencies are 6.9552 MHz, 9.6 MHz, 11.2896 MHz, 12.288 MHz. Max frequency is 12.5 MHz. An external clock (max. 1.8 $V_{\rm PP}$ ) can be connected to X1 using AC coupling (22 pF). A built-in PLL multiplies the clock frequency by 4 for internal use. |

| LFT             | 74                                                                      | -         | -       | PLL decoupling RCR filter                                                                                                                                                                                                                                                                        |

| RESET           | 33                                                                      | In        | -       | Master reset Schmitt trigger input, active low. RESET should be held low during at least 10 ms after power is applied. On the rising edge of RESET, the chip enters an initialization routine, which may involve firmware download from an external SmartMedia, DataFlash or host.               |

| STIN            | 34                                                                      | In<br>Pd  | -       | Serial test input. This is a 57.6 Kbaud asynchronous input used for firmware debugging. This pin is tested at power-up. The built-in debugger starts if STIN is found high. STIN has a built-in pull-down. It should be grounded or left open for normal operation.                              |

Table 6-1.

Pinout by Pin Name (Continued)

| Pin Name | Pin Number | Туре     | Sharing | Description                                                                                                                                                                                                                                                                                                                                                                                           |

|----------|------------|----------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STOUT    | 35         | Out      | -       | Serial test output. 57.6 Kbaud async output used for firmware debugging.                                                                                                                                                                                                                                                                                                                              |

| PDWN     | 31         | In       | -       | Power down input, active low. High level on this pin is typ. VC18. When PDWN is low, the oscillator and PLL are stopped, the power switch opens, and the chip enters a deep sleep mode (1 µA typ. consumption when power switch is used). To exit from power down, PDWN has to be set high then RESET applied. Alternate programmable power-downs are available which allow warm restart of the chip. |

| TEST     | 52         | In<br>Pd | -       | Test input. Should be grounded or left open.                                                                                                                                                                                                                                                                                                                                                          |

### 6.2 Pinout by Pin Number

www.DataSheet4U.com

Table 6-2. ATSAM3308B Pinout by Pin Number

| Pin<br># | Pin Name                 | Pin<br># | Pin Name        | Pin<br># | Pin Name    | Pin<br># | Pin Name              |

|----------|--------------------------|----------|-----------------|----------|-------------|----------|-----------------------|

| 1        | WR SMC P0.12             | 26       | WA7 P2.7        | 51       | WA14 P2.14  | 76       | D0 I/O0 P0.0 WSAD0    |

| 2        | RD RIB P0.13             | 27       | WA8 P2.8        | 52       | TEST        | 77       | D1 I/O1 P0.1 WSAD1    |

| 3        | WCS1 P1.10               | 28       | PWROUT          | 53       | WA15 P2.15  | 78       | WD5 P3.5              |

| 4        | WCS0 P1.9                | 29       | PWRIN           | 54       | DAAD0 P0.15 | 79       | WD6 P3.6              |

| 5        | CKOUT                    | 30       | GND             | 55       | DAAD1       | 80       | WD7 P3.7              |

| 6        | CLBD                     | 31       | PDWN            | 56       | GND         | 81       | D2 I/O2 P0.2 WSAD2    |

| 7        | WSBD                     | 32       | DFSO            | 57       | WA16 P1.0   | 82       | D3 I/O3 P0.3 WSAD3    |

| 8        | IRQ INT SMRE FS0<br>P0.8 | 33       | RESET           | 58       | WA17 P1.1   | 83       | VC33                  |

| 9        | GND                      | 34       | STIN            | 59       | DAAD2       | 84       | WD8 P3.8              |

| 10       | WA0 P2.0                 | 35       | STOUT           | 60       | DAAD3       | 85       | WD9 P3.9              |

| 11       | WA1 P2.1                 | 36       | WA9 P2.9        | 61       | WD0 P3.0    | 86       | WD10 P3.10            |

| 12       | WA2 P2.2                 | 37       | WA10 P2.10      | 62       | WD1 P3.1    | 87       | GND                   |

| 13       | VC3                      | 38       | WA11 P2.11      | 63       | WD2 P3.2    | 88       | WD11 P3.11            |

| 14       | WA3 P2.3                 | 39       | WA12 P2.12      | 64       | DABD0       | 89       | WD12 P3.12            |

| 15       | WA4 P2.4                 | 40       | WA13 P2.13      | 65       | DABD1       | 90       | D4 I/O4 P0.4 CLAD0    |

| 16       | WA5 P2.5                 | 41       | GND             | 66       | DABD2       | 91       | D5 I/O5 P0.5 CLAD1    |

| 17       | MIDI_IN P0.14 SDIN       | 42       | WA18 SMCLE P1.2 | 67       | DABD3       | 92       | WD13 P3.13            |

| 18       | MIDI_OUT FS1 P0.9        | 43       | WA19 SMWE P1.3  | 68       | WD3 P3.3    | 93       | WD14 P3.14            |

| 19       | MUTE P1.6                | 44       | WA20 SMALE P1.4 | 69       | WD4 P3.4    | 94       | WD15 P3.15            |

| 20       | VC18                     | 45       | WA21 SMCE P1.5  | 70       | GND         | 95       | D6 I/O6 P0.6 CLAD2    |

| 21       | WA6 P2.6                 | 46       | P1.15           | 71       | X2          | 96       | D7 I/O7 P0.7 CLAD3    |

| 22       | GND                      | 47       | VC18            | 72       | X1          | 97       | GND                   |

| 23       | DFCS                     | 48       | WOE P1.8        | 73       | VC18        | 98       | A0 SMPD P0.10<br>SCLK |

| 24       | DFSCK                    | 49       | WWE P1.7        | 74       | LFT         | 99       | VC18                  |

| 25       | DFSI                     | 50       | VC33            | 75       | GND         | 100      | CS P0.11 SYNC         |

### 7. Marking

www.DataSheet4U.com

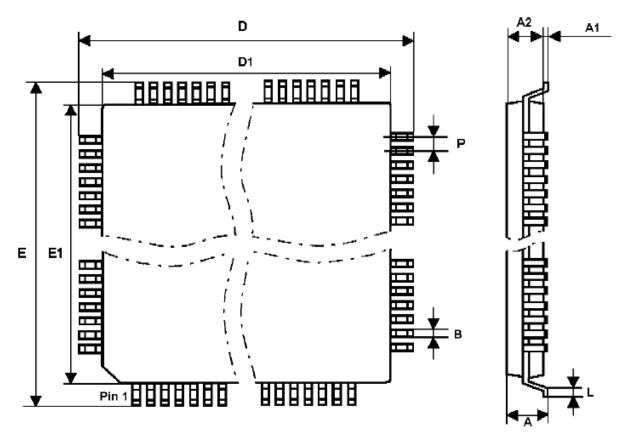

### 8. Mechanical Dimensions

Figure 8-1. Thin Plastic 100-lead Quad Flat Pack (LQFP100)

www.DataSheet4LLcom

Table 8-1.Package Dimensions in mm

| Denomination | Min  | Nom   | Max  |

|--------------|------|-------|------|

| А            | 1.40 | 1.50  | 1.60 |

| A1           | 0.05 | 0.10  | 0.15 |

| A2           | 1.35 | 1.40  | 1.45 |

| L            | 0.45 | 0.60  | 0.75 |

| D            |      | 14.00 |      |

| D1           |      | 12.00 |      |

| Е            |      | 14.00 |      |

| E1           |      | 12.00 |      |

| Р            |      | 0.40  |      |

| В            | 0.13 | 0.18  | 0.23 |

### 9. Electrical Characteristics

9.1 Absolute Maximum Ratings (\*)

| Ambient Temperature (power applied)40°C to 85°C | *NOTICE: Stresses beyond those listed under "Absolute<br>Maximum Ratings" may cause permanent dam-     |

|-------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| Storage Temperature65° C to 150° C              | age to the device. This is a stress rating only and functional operation of the device at these or any |

| Voltage on any pin                              | other conditions beyond those indicated in the                                                         |

| X1, LFT0.3 to V <sub>C18</sub> + 0.3V           | Recommended Operating Conditions of this                                                               |

| Others0.3 to V <sub>C33</sub> + 0.3V            | specification is not implied. Exposure to absolute maximum rating conditions for extended periods      |

| Supply Voltage                                  | may affect device reliability.                                                                         |

| V <sub>C18</sub> 0.3V to 1.95V                  | •                                                                                                      |

| V <sub>C3</sub> 0.3V to 3.6V                    |                                                                                                        |

| Maximum IOL per I/O pin 4 mA                    |                                                                                                        |

### 9.2 Recommended Operating Conditions

Table 9-1.

Recommended Operating Conditions

| Symbol           | Parameter                     | Min  | Тур | Max                  | Unit |

|------------------|-------------------------------|------|-----|----------------------|------|

| V <sub>C18</sub> | Supply voltage                | 1.65 | 1.8 | 1.95                 | V    |

| V <sub>C33</sub> | Supply voltage (1)            | 3    | 3.3 | VC18 +<br>1.5<br>3.6 | V    |

| PWRIN            | Supply voltage PWRIN pin      | 1.75 | 1.9 | 1.95                 | V    |

| T <sub>A</sub>   | Operating ambient temperature | 0    | -   | 70                   | °C   |

Note: 1. Operation at lower V<sub>C33</sub> values down to V<sub>C18</sub> is possible, however external timing may be impaired. Contact Atmel in case of use of these circuits with V<sub>C33</sub> outside the recommended operating range.

### 9.3 DC Characteristics

www.DataSheet4U.com

**Table 9-2.** DC Characteristics (T  $_A$  = 25°C, V $_{C18}$  =1.8V ± 10%, V $_{C33}$  = 3.3V ± 10%)

| Symbol           | Parameter                                                                                                    | Min  | Тур | Max                    | Unit |

|------------------|--------------------------------------------------------------------------------------------------------------|------|-----|------------------------|------|

| V <sub>IL</sub>  | Low level input voltage                                                                                      | -0.3 | -   | 1.0                    | V    |

| V <sub>IH</sub>  | High level input voltage, except X1, PDWN                                                                    | 2.3  | -   | V <sub>C33</sub> + 0.3 | V    |

| V <sub>IH</sub>  | High level input voltage X1, PDWN                                                                            | 1.2  | -   | V <sub>C18</sub> + 0.3 | V    |

| V <sub>OL</sub>  | Low level output voltage IOL = -2 mA                                                                         | -    | -   | 0.4                    | V    |

| V <sub>OH</sub>  | High level output voltage IOH = 2 mA                                                                         | 2.9  | -   | -                      | V    |

| I <sub>CC1</sub> | VC18 power supply current (crystal freq.=11.2896 MHz, all 8 P24s running)                                    | -    | 63  | -                      | mA   |

| I <sub>CC2</sub> | VC18 power supply current<br>(crystal freq. = 11.2896 MHz, all P24s stopped)                                 | -    | 22  | -                      | mA   |

| I <sub>CC3</sub> | VC18 power supply current<br>(crystal freq. = 11.2896 MHz, all P24 stopped, warm start<br>power-down active) | -    | 4   | -                      | mA   |

| I <sub>CC4</sub> | VC18 deep power down supply current (using power switch)                                                     | -    | 1   | 10                     | μΑ   |

| PU/PD            | Built-in pull-up/pull-down resistor                                                                          | 10   | -   | 56                     | kΩ   |

### 10. Peripherals and Timings

www.DataSheet4U.com

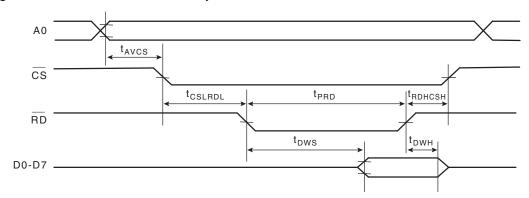

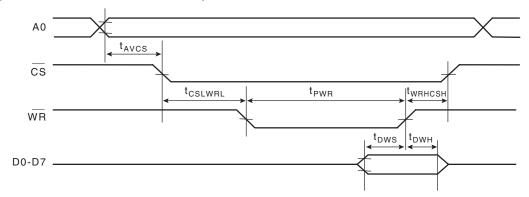

#### 10.1 8-bit Slave Parallel Interface

The Slave Parallel Interface is typically used to connect the chip to a host processor.

Pins used: D7 - D0 (I/O), A0 (Input), WR (Input), RD (Input), IRQ (Output).

#### **10.1.1 Timings**

Figure 10-1. Host Interface Read Cycle

Figure 10-2. Host Interface Write Cycle

Table 10-1. Timing Parameters

| Symbol               | Parameter                        | Min | Тур | Max | Unit |

|----------------------|----------------------------------|-----|-----|-----|------|

| t <sub>AVCS</sub>    | Address valid to chip select low | 0   | -   | -   | ns   |

| t <sub>CSLRDL</sub>  | Chip select low to RD low        | 5   | -   | -   | ns   |

| t <sub>RDHCSH</sub>  | RD high to CS high               | 5   | -   | -   | ns   |

| t <sub>PRD</sub>     | RD pulse width                   | 50  | -   | -   | ns   |

| t <sub>RDLDV</sub>   | Data out valid from RD           | -   | -   | 20  | ns   |

| t <sub>DRH</sub>     | Data out hold from RD            | 5   | -   | 10  | ns   |

| t <sub>CSLRWRL</sub> | Chip select low to WR low        | 5   | -   | -   | ns   |

| t <sub>wrhcsh</sub>  | WR high to CS high               | 5   | -   | -   | ns   |

Table 10-1. Timing Parameters (Continued)

www.DataSheet4U.com

| Symbol           | Parameter             | Min | Тур | Max | Unit |

|------------------|-----------------------|-----|-----|-----|------|

| t <sub>PWR</sub> | WR pulse width        | 50  | -   | -   | ns   |

| t <sub>DWS</sub> | Write data setup time | 10  | -   | -   | ns   |

| t <sub>DWH</sub> | Write data hold time  | 0   | -   | -   | ns   |

#### 10.1.2 IO Status Register

| 7  | 6  | 5 | 4 | 3 | 2 | 1 | 0 |

|----|----|---|---|---|---|---|---|

| TE | RF | Х | Х | Х | X | X | Х |

Status register is read when A0 = 1,  $\overline{RD} = 0$ ,  $\overline{CS} = 0$ .

#### • TE: Transmit Empty

If 0, data from ATSAM3308B to host is pending and IRQ is high. Reading the data at A0 = 0 will set TE to 1 and clear IRQ.

#### · RF: Receiver full

If 0, then ATSAM3308B is ready to accept DATA from host.

Note: If status bit RF is not checked by host, write cycle time should not be lower than 3 µs.

#### 10.2 SmartMedia and Other Peripheral Interfaces

The SmartMedia and Other Peripheral Interface is a master 8-bit parallel interface that provides connection to SmartMedia or other peripherals such as LCD screens.

Pins used: I/O7 - I/O0 (I/O), SMPD (input) SMCE, SMALE, SMCLE, SMRE, SMWE (outputs)

All of these pins are fully under firmware control, therefore timing compatibility is ensured by firmware only.

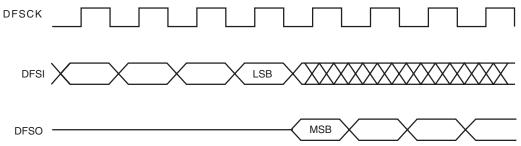

#### 10.3 EEPROM/DataFlash Interface

The EEPROM/DataFlash interface is a master synchronous serial interface, operating in SPI mode 0.

Pins used: DFCS, DFSI, DFSCK (outputs), DFSO (input)

The DFSCK frequency is firmware programmable from fck to fck/64, where fck is the crystal frequency. Thus a large variety of EEPROM/DataFlash devices can be accommodated.

Please refer to Atmel DataFlash datasheets for accurate SPI mode 0 timing.

Figure 10-3. DataFlash Interface Typical Timing

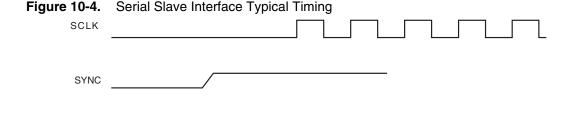

#### 10.4 Serial Slave Synchronous Interface

www.DataSheet4U.com

The ATSAM3308B can be controlled by an external host processor through this unidirectional serial interface. However, no firmware can be downloaded at power-up through this interface. Therefore an external ROM/Flash/EEPROM is required.

Pins used: SCLK, SYNC, SDIN (input) INT (output)

Data is shifted into MSB first. The IC samples an incoming SDIN bit on the rising edge of SCLK, therefore the host should change SDIN on the negative SCLK edge.

SYNC allows initial synchronization. The rising edge of SYNC, which should occur with SCLK low, indicates that SDIN will hold MSB data on the next rising SCLK.

The data is stored internally into a 256 byte FIFO.

When the FIFO count is below 64, the  $\overline{\text{INT}}$  output goes low. This allows the host processor to send data in burst mode.

The maximum SCLK frequency is fck (fck being the crystal frequency). The minimum time between two bytes is 64 fck periods.

The contents of the SDIN data are defined by the firmware.

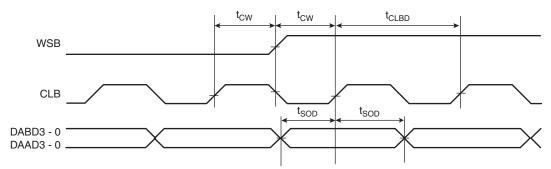

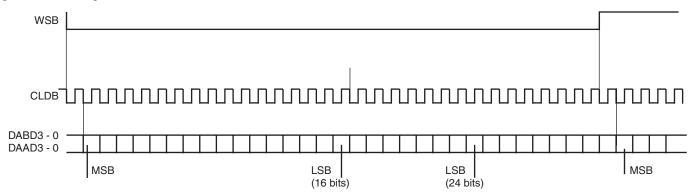

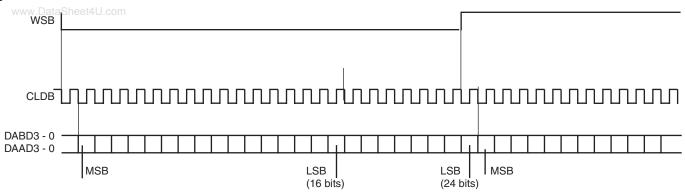

#### 10.5 Digital Audio

Pins used: CLBD (output), WSBD (output) DABD3 - 0 (outputs) DAAD3 - 0 (inputs)

Optionally: CLAD3 - 0 (inputs), WSAD3 - 0 (inputs)

SDIN

The ATSAM3308B allows for 8 digital audio output channels and 8 digital audio input channels. All audio channels are normally synchronized on single clocks CLBD, WSBD which are derived from the IC crystal oscillator. However, as a firmware option, the DAAD3 - 0 inputs can be synchronized with incoming CLAD3 - 0 and WSAD3 - 0 signals. In this case, the incoming sampling frequencies must be lower or equal to the chip sampling frequency.

The digital audio timing follows the I2S standard, with up to 24 bits per sample

Figure 10-5. Digital Audio Timing

www.DataSheet4U.com

**Table 10-2.** Digital Audio Timing Parameters

| Symbol            | Parameter                          | Min                 | Тур                | Max | Unit |

|-------------------|------------------------------------|---------------------|--------------------|-----|------|

| t <sub>CW</sub>   | CLBD rising to WSBD change         | t <sub>C</sub> - 10 | -                  | -   | ns   |

| t <sub>SOD</sub>  | DABD valid prior/after CLBD rising | t <sub>C</sub> - 10 | -                  | -   | ns   |

| t <sub>CLBD</sub> | CLBD cycle time                    | -                   | 2 * t <sub>C</sub> | -   | ns   |

$t_{\text{C}}$  is related to  $t_{\text{CK}}\text{,}$  the crystal period at X1 as follows:

Table 10-3. Sample Frequency

| Sample<br>Frequency WSBD  | Typical Sample<br>Frequency | t <sub>C</sub>      | CLBD/WSBD<br>Frequency Ratio |

|---------------------------|-----------------------------|---------------------|------------------------------|

| 1/(t <sub>CK</sub> * 128) | 96 kHz                      | t <sub>CK</sub>     | 64                           |

| 1/(t <sub>CK</sub> * 192) | 64 kHz                      | 2 * t <sub>CK</sub> | 48                           |

| 1/(t <sub>CK</sub> * 256) | 48 kHz                      | 2 * t <sub>CK</sub> | 64                           |

| 1/(t <sub>CK</sub> * 384) | 32 kHz                      | 4 * t <sub>CK</sub> | 48                           |

The choice of sample frequency is done by firmware.

Figure 10-6. Digital Audio Frame Format, 128 x Fs and 256 x Fs Modes

**Figure 10-7.** 192 x Fs and 384 x Fs Modes

#### 10.6 Serial MIDI\_IN and MIDI\_OUT

The serial MIDI IN and OUT signals are asynchronous signals following the MIDI transmission standard:

• Baud rate: 31.25 kHz

• Format: start, 8 data bits, 1 stop

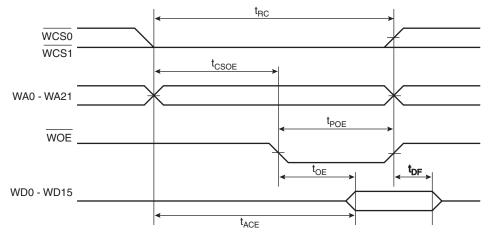

### 10.7 External Memory

Pins used: WA21 - WA0 (address out), WD15 - WD0 (data bi-directional)  $\overline{WCS0}$ ,  $\overline{WCS1}$  (predecodes out)  $\overline{WOE}$  (output enable)  $\overline{WWE}$  (write)

When using all address bits, the maximum addressing range is two pages ( $\overline{WCS0}$ ,  $\overline{WCS1}$ ) of 4M words (total = 16 Mbytes).

Figure 10-8. ROM/Flash Read Cycle

Table 10-4. External Memory Parameters

| Symbol            | Parameter                                  | Min                         | Тур                  | Max                      | Unit |

|-------------------|--------------------------------------------|-----------------------------|----------------------|--------------------------|------|

| t <sub>RC</sub>   | Read cycle time                            | -                           | 5 * p <sub>LCK</sub> | -                        | ns   |

| t <sub>CSOE</sub> | Chip select low/address valid to WOE low   | 2 * p <sub>LCK</sub> - 5    | -                    | 2 * p <sub>LCK</sub> + 5 | ns   |

| t <sub>POE</sub>  | Output enable pulse width                  | -                           | 3 * p <sub>LCK</sub> | -                        | ns   |

| t <sub>ACE</sub>  | Chip select/address access time            | 4.5 * p <sub>LCK</sub> - 10 | -                    | -                        | ns   |

| t <sub>OE</sub>   | Output enable access time                  | 2.5 * p <sub>LCK</sub> - 10 | -                    | -                        | ns   |

| t <sub>DF</sub>   | Chip select or WOE high to input data Hi-Z | 0                           | -                    | 2 * p <sub>LCK</sub> - 5 | ns   |

Note: 1. A built-in PLL multiplies the crystal clock frequency by 4 for internal use.  $p_{LCK}$  is the period of the internal clock generated by PLL.  $p_{LCK} = t_{CK}/4$ . Typical value with crystal 12.288 MHz is  $p_{LCK} = 20$  ns.

2. Memory access time should be lower than  $t_{ACE}$  min. Typical value with crystal 12.288 MHz is 80 ns.

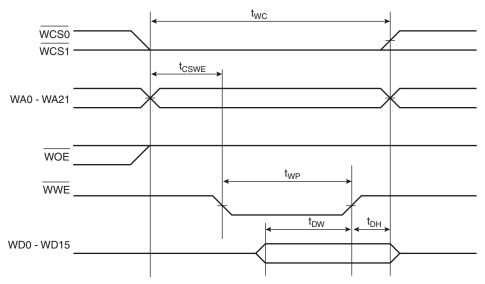

Figure 10-9. External RAM/Flash Write Timing

Table 10-5. External Flash Timing Parameters

| Symbol            | Parameter                                                                          | Min                        | Тур                    | Max                      | Unit |

|-------------------|------------------------------------------------------------------------------------|----------------------------|------------------------|--------------------------|------|

| t <sub>WC</sub>   | Write cycle time                                                                   | -                          | 5 * p <sub>LCK</sub>   | -                        | ns   |

| t <sub>CSWE</sub> | Write enable low from $\overline{\text{CS}}$ or Address or $\overline{\text{WOE}}$ | 2 * p <sub>LCK</sub> - 5   | -                      | 2 * p <sub>LCK</sub> + 5 | ns   |

| t <sub>WP</sub>   | Write pulse width                                                                  | -                          | 2.5 * p <sub>LCK</sub> | -                        | ns   |

| t <sub>DW</sub>   | Data out setup time                                                                | 2.5 * p <sub>LCK</sub> - 5 | -                      | -                        | ns   |

| t <sub>DH</sub>   | Data out hold time                                                                 | 0.5 * p <sub>LCK</sub>     | -                      | -                        | ns   |

#### 11. Reset and Power-down

www.DataSheet4U.con

During power up, the  $\overline{\text{RESET}}$  input should be held low until the crystal oscillator and PLL are stabilized, which takes max. 10 ms.

After the low to high transition of  $\overline{RESET}$ , the following happens:

- All P24s enter an idle state.

- P16 program execution starts in built-in ROM.

The power-up sequence is as follows:

- STIN is sensed. If HIGH, then the built-in debugger is started.

- Addresses 0 & 1 from external ROM are checked. If "DR" is read, then control is transferred to address 400H from external ROM.

- SMC is sensed. If LOW, then the built-in loader waits for SmartMedia presence detect (SMPD). When detected, the firmware is down loaded from SmartMedia reserved sector 1 and started.

- An attempt is made to read the first two bytes of an external EEPROM or DataFlash. If "DR" is read, then the built-in loader loads the firmware from the external EEPROM/DataFlash and starts it.

- Firmware download from a host processor is assumed.

- 1. The 0ACh byte is written to the host, this raises IRQ. The host can recognize that the chip is ready to accept program download. Higher speed transfer can be reached by polling the parallel interface status ( $\overline{CS} = 0$ , AO = 1,  $\overline{RD} = 0$ ).

- 2. The host sends the firmware size (in words) on two bytes (Low byte first).

- 3. The host sends the ATSAM3308B firmware. The firmware should begin with string "DR".

- 4. The 0ACh byte is written to the host, this raises IRQ. The host can recognize that the chip has accepted the firmware.

- ATSAM3308B starts the firmware.

If  $\overline{\text{PDWN}}$  is asserted low, then the crystal oscillator and PLL will be stopped. If the power switch is used, then the chip enters a deep power down sleep mode, as power is removed from the core. To exit power down,  $\overline{\text{PDWN}}$  has to be asserted high, then  $\overline{\text{RESET}}$  applied.

Other power reduction features allowing warm restart are controlled by firmware:

- P24s can be individually stopped.

- The clock frequency can be internally divided by 256.

### 12. Recommended Board Layout

www.DataSheet4U.com

Like all HCMOS high integration ICs, following simple rules of board layout is mandatory for reliable operations:

• GND, VC33, VC18 distribution, decoupling

All GND, VC33, VC18 pins should be connected. A GND plane is strongly recommended. The board GND + VC33 distribution should be in grid form.

Recommended VC18 decoupling is 0.1  $\mu$ F at each corner of the IC with an additional 10  $\mu$ F decoupling close to the crystal. VC33 requires a single 0.1  $\mu$ F decoupling.

· Crystal, LFT

The paths between the crystal, the crystal compensation capacitors, the LFT filter R-C-R and the IC should be short and shielded. The ground return from the compensation capacitors and LFT filter should be the GND plane from the IC.

#### Buses

Parallel layout from D0 - D7 and WA0 - WA21/WD0 - WD15 should be avoided. The D0 - D7 bus is an asynchronous type bus. Even on short distances, it can induce pulses on WA0 - WA21/WD0 - WD15 which can corrupt address and/or data on these buses.

A ground plane should be implemented below the D0 - D7 bus that connects both to the host and to the IC GND.

A ground plane should be implemented below the WA0 - WA21/WD0 - WD15 bus that connects both to the ROM/Flash grounds and to the IC.

Analog Section

A specific AGND ground plane should be provided, which connects by a single trace to the GND ground. No digital signals should cross the AGND plane. Refer to the Codec vendor recommended layout for correct implementation of the analog section.

## 13. Recommended Crystal Compensation and LFT Filter

www.DataSheet4U.com

Figure 13-1. Recommended Crystal Compensation and LFT Filter

### 14. Product Development and Debugging

www.DataSheet4U.com

Atmel provides an integrated product development and debugging tool SamVS. SamVS runs under Windows® (98, ME, 2000, XP). Within the environment, it is possible to:

- Edit

- Assemble

- Debug on real target (In-circuit Emulation)

- Program Flash, Dataflash, EEPROM, SmartMedia on target.

Two dedicated IC pins, STIN and STOUT allow running firmware directly into the target using standard PC COM port communication at 57.6 Kbauds. Thus time-to-market is optimized by testing directly on the final prototype.

A library of frequently used functions is available, such as:

- Wavetable synthesis

- Reverb/Chorus

- MP3 decode

- 31-band equalizer

- Parametric equalizer

Atmel engineers are available to study customer-specific applications.

# 15. Revision History www.DataSheet4U.com

### Table 15-1. Revision History

| Document Ref. | Comments                                                                                                                                                                                                                                                                                                 | Change<br>Request |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 6090A         | First issue                                                                                                                                                                                                                                                                                              |                   |

| 6090B         | Corrected description of RESET pin in Table 6-1.                                                                                                                                                                                                                                                         | 1042              |

| 6090C         | Changed all references TQFP to LQFP. Changed pin name for Pin No. 8 in Table 6-2, "ATSAM3308B Pinout by Pin Number," on page 11.                                                                                                                                                                         | 2641              |

| 6090D         | Changed all references ATSAM3308 to ATSAM3308B. Added Section 7. "Marking" on page 12. Updated Table 10-4, "External Memory Parameters," on page 20 and Table 10-5, "External Flash Timing Parameters," on page 20. Updated note <sup>(2)</sup> in Table 10-4, "External Memory Parameters," on page 20. |                   |

www.DataSheet4U.com

#### **Atmel Corporation**

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311

Fax: 1(408) 487-2600

#### Regional Headquarters

#### Europe

Atmel Sarl

Route des Arsenaux 41 Case Postale 80 CH-1705 Fribourg Switzerland

Tel: (41) 26-426-5555 Fax: (41) 26-426-5500

#### Asia

Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong Kong

Tel: (852) 2721-9778 Fax: (852) 2722-1369

#### Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan

Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

#### **Atmel Operations**

#### Memory

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

#### Microcontrollers

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

La Chantrerie BP 70602

44306 Nantes Cedex 3, France Tel: (33) 2-40-18-18

Fax: (33) 2-40-18-19-60

#### ASIC/ASSP/Smart Cards

Zone Industrielle 13106 Rousset Cedex, France Tel: (33) 4-42-53-60-00

Fax: (33) 4-42-53-60-01

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA

Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

Scottish Enterprise Technology Park Maxwell Building

East Kilbride G75 0QR, Scotland

Tel: (44) 1355-803-000 Fax: (44) 1355-242-743

#### RF/Automotive

Theresienstrasse 2 Postfach 3535 74025 Heilbronn, Germany Tel: (49) 71-31-67-0

Fax: (49) 71-31-67-2340

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA

Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

#### **Biometrics**

Avenue de Rochepleine BP 123

38521 Saint-Egreve Cedex, France

Tel: (33) 4-76-58-47-50 Fax: (33) 4-76-58-47-60

Literature Requests

www.atmel.com/literature

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL'S TERMS AND CONDITIONS OF SALE LOCATED ON ATMEL'S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel's products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

© 2007 Atmel Corporation. All rights reserved. Atmel<sup>®</sup>, logo and combinations thereof, Everywhere You Are<sup>®</sup>, Dream<sup>®</sup>, DataFlash<sup>®</sup> and others are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Windows<sup>®</sup> and others are the registered trademarks or trademarks of Microsoft Corporation in the US and/or other countries. Other terms and product names may be the trademarks of others.