# Atmel SAM4SP32A

# **CORTEX-M4 PRIME SoC**

# PRELIMINARY DATASHEET

### **Features**

- Core

- ARM® Cortex<sup>™</sup>-M4 with a 2Kbytes cache running at 120MHz

- Memory Protection Unit (MPU)

- DSP Instruction Set

- Thumb®-2 instruction set

- Memories

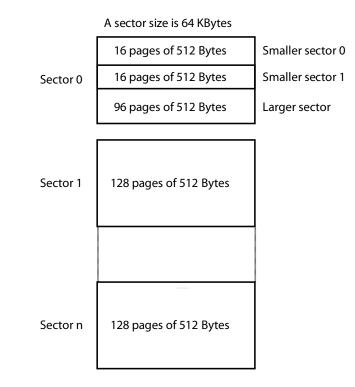

- 2048 Kbytes embedded Flash with optional dual bank and cache memory

- 160 Kbytes embedded SRAM

- 16 Kbytes ROM with embedded boot loader routines (UART, USB) and IAP routines

- System

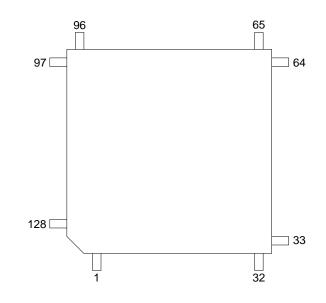

- Embedded voltage regulator for single supply operation

- Power-on-Reset (POR), Brown-out Detector (BOD) and Watchdog for safe operation

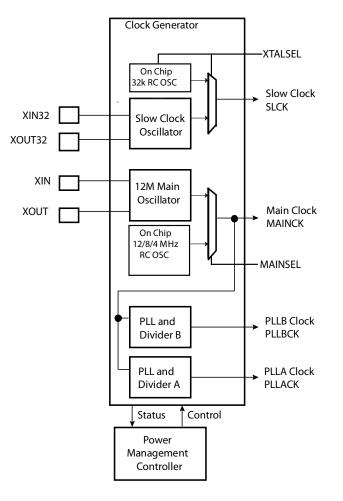

- Quartz or ceramic resonator oscillators: 3 to 20 MHz main power with Failure Detection and optional low-power 32.768 kHz for RTC or device clock

- RTC with Gregorian and Persian Calendar mode, waveform generation in low power modes

- RTC clock calibration circuitry for 32.768 kHz crystal frequency compensation

- High precision 8/12 MHz factory trimmed internal RC oscillator with 4 MHz default frequency for device startup. In-application trimming access for frequency adjustment

- Slow Clock Internal RC oscillator as permanent low-power mode device clock

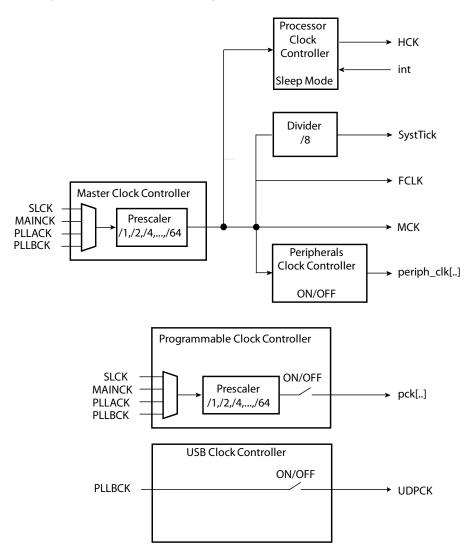

- Two PLLs up to 240 MHz for device clock and for USB

- Temperature Sensor

- Up to 22 Peripheral DMA (PDC) Channels

- Low Power Modes

- Sleep and Backup Modes, down to 1 µA in Backup Mode

- Ultra low-power RTC

- Peripherals

- USB 2.0 Device: 12 Mbps, 2668 byte FIFO, up to 8 bidirectional Endpoints. On-Chip Transceiver

- 2 USARTs with ISO7816, IrDA ®, RS-485, Manchester and Modem Mode

- Two 2-wire UARTs

- 2 Two Wire Interface (I2C compatible), 1 Synchronous Serial Controller (SSC)

- 2 Three-Channel 16-bit Timer/Counter with capture, waveform, compare and PWM mode. Quadrature Decoder Logic and 2-bit Gray Up/Down Counter for Stepper Motor

- 4-channel 16-bit PWM with Complementary Output, Fault Input, 12-bit Dead Time Generator Counter

- 32-bit Real-time Timer and RTC with calendar and alarm features

- One Analog Comparator with flexible input selection

- 32-bit Cyclic Redundancy Check Calculation Unit (CRCCU)

- Write Protected Registers

- I/O

- Up to 38 I/O lines with external interrupt capability (edge or level sensitivity), debouncing, glitch filtering and on-die Series Resistor Termination

- Three 32-bit Parallel Input/Output Controllers, Peripheral DMA assisted Parallel Capture Mode

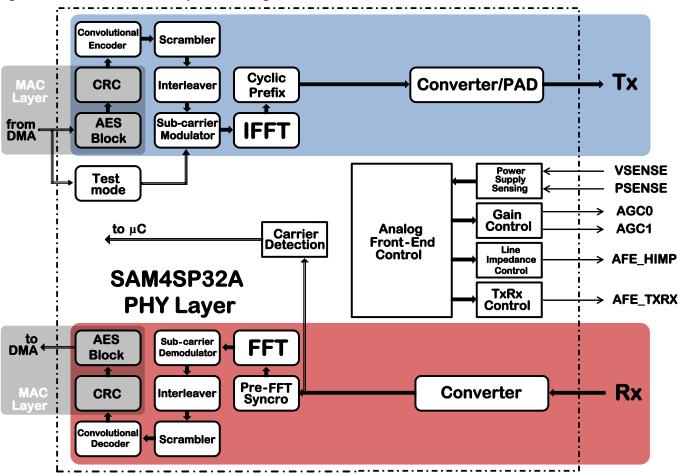

- PRIME PLC Modem

- Power Line Carrier Modem for 50 and 60 Hz mains

- 97-carrier OFDM PRIME compliant

- Baud rate Selectable: 21400 to 128600 bps

- Differential BPSK, QPSK, 8-PSK modulations

- Automatic Gain Control and signal amplitude tracking

- Embedded on-chip DMAs

- Media Access Control

- Viterbi decoding and CRC PRIME compliant

- 128-bit AES encryption

- Channel sensing and collision pre-detection

- Package

- 128-Lead LQFP

- Pb-free and RoHS compliant

- Typical Applications

- PRIME Smart Meters

- PRIME Data Concentrator

### **Description**

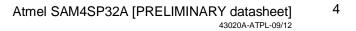

The SAM4SP32A is a new evolution of SAM4SD32 Flash microcontroller based on the high performance 32-bit ARM Cortex-M4 RISC processor with a PRIME Power Line Communication Modem SoC integrated.

The SAM4SP32A operates at a maximum speed of 120 MHz and features with a 2048 Kbytes of Flash, with optional dual bank implementation and 2Kbytes of cache memory, 160 Kbytes of SRAM, and 32Kbytes embedded SRAM memory available for PRIME specification requirements.

The peripheral set mainly includes a Certified PRIME Power line communication transceiver with a featured Class D power amplifier and a set of hardware accelerators blocks to execute the heavy tasks of the PRIME protocol without the interruption of the Cortex-M4 CPU. Furthermore, the SAM4SP32A includes a Full Speed USB Device port with embedded transceiver, , 2x USARTs, 2x UARTs, 2x TWIs, an I2S, as well as 1 PWM timer, 2x three channel general-purpose 16-bit timers (with stepper motor and quadrature decoder logic support), an RTC, a Synchronous Serial Controller (SSC) and an analog comparator.

The Atmel SAM4SP32A SoC device combines robust and high performances PRIME PLC Modem with a powerfull Cortex-M4 microcontroller with the best ratio in terms of reduced power consumption, processing power and peripheral set. This enables the SAM4SP32A to sustain a wide range of applications including PRIME Smart Grid and data concentrator solutions.

SAM4SP32A operates from 3.0V to 3.6V

# **Table of Contents**

| 1. | Bloc  | k Diagra       | am          |                                        | . 8 |

|----|-------|----------------|-------------|----------------------------------------|-----|

| 2. |       | 0              |             |                                        |     |

|    | 2.1   |                |             | ckage Outline                          |     |

|    | 2.2   | 128-Lea        | id LQFP Pi  | nout                                   | 10  |

| 3. | Sign  | al Desc        | ription     |                                        | 11  |

| 4. | Pin [ | Descript       | ion         |                                        | 15  |

| 5. | Powe  | er Cons        | ideration   | 5                                      | 26  |

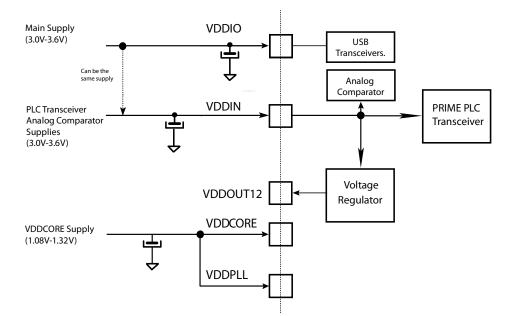

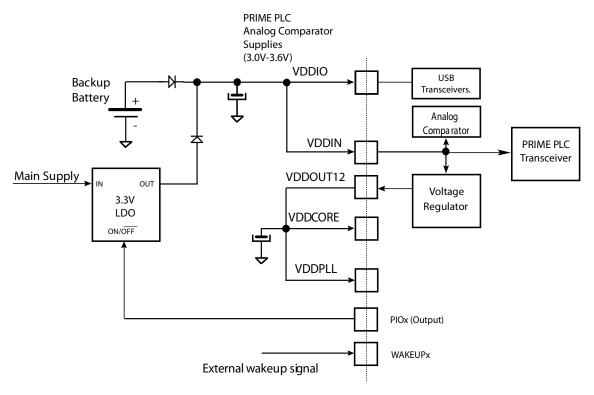

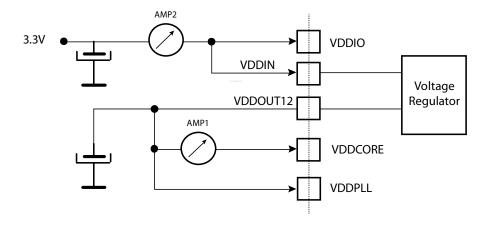

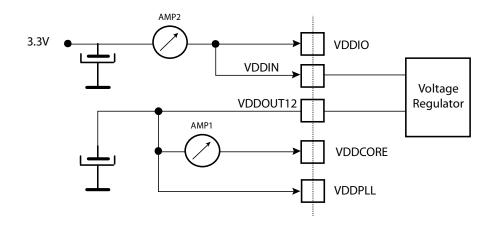

|    | 5.1   |                |             |                                        |     |

|    | 5.2   |                |             |                                        |     |

|    | 5.3   |                | 0           | chematics                              |     |

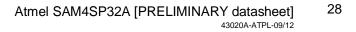

|    | 5.4   |                |             |                                        |     |

|    | 5.5   |                |             |                                        |     |

|    |       | 5.5.1          |             | ode                                    |     |

|    |       | 5.5.2          |             | 3                                      |     |

|    |       | 5.5.3<br>5.5.4 |             | de<br>r Mode Summary Table             |     |

|    | 5.6   |                |             |                                        |     |

|    | 5.7   |                |             |                                        |     |

| _  |       |                | ·           |                                        |     |

| 6. | Input | •              |             |                                        |     |

|    | 6.1   |                |             | O Lines                                |     |

|    | 6.2   | System         |             |                                        |     |

|    |       | 6.2.2          |             | e JTAG Debug Port (SWJ-DP) Pins        |     |

|    | 6.3   |                |             |                                        |     |

|    | 6.4   |                |             |                                        |     |

|    | 6.5   | ERASE          | Pin         |                                        | 36  |

| 7. | Proc  | essor a        | nd Archit   | ecture                                 | 37  |

|    | 7.1   | ARM Co         | ortex-M4 Pr | ocessor                                | 37  |

|    | 7.2   | APB/AH         | IB Bridge   |                                        | 37  |

|    | 7.3   |                | 0           |                                        |     |

|    | 7.4   | Matrix S       | Slaves      |                                        | 37  |

|    | 7.5   | Master t       | to Slave Ac | cess                                   | 38  |

|    | 7.6   | Periphe        | rical DMA ( | Controller                             | 38  |

|    | 7.7   | Debug a        | and Test Fe | atures                                 | 39  |

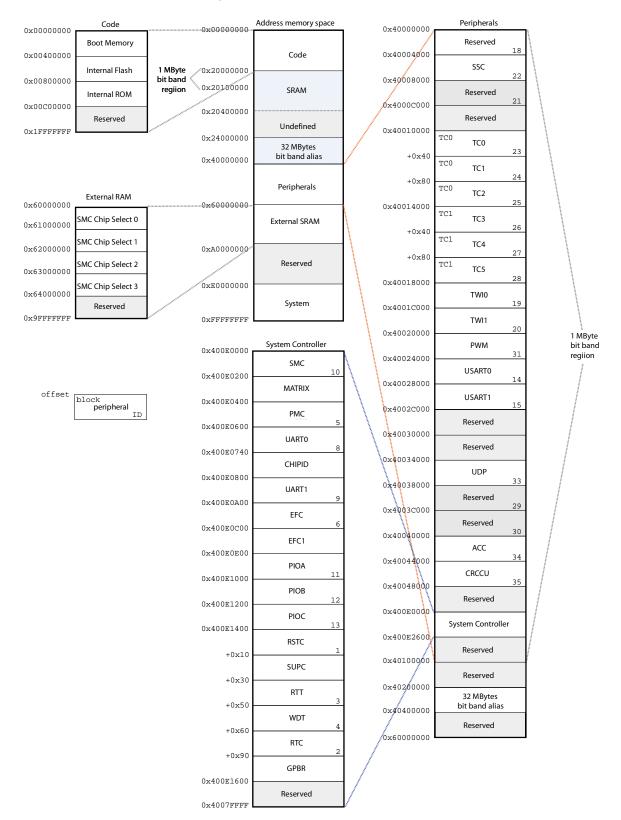

| 8. | SAM   | 4SP32/         | A Produc    | t Mapping                              | 40  |

|    |       |                |             |                                        |     |

| 9. |       |                |             | ······································ |     |

|    | 9.1   |                |             | es                                     |     |

|    |       | 9.1.1          |             | RAM                                    |     |

|    |       | 9.1.2<br>9.1.3 |             | OM<br>d Flash                          |     |

|    |       | 9.1.3          | 9.1.3.1     | Flash Overview                         |     |

|    |       |                | 9.1.3.1     | Enhanced Embedded Flash Controller     |     |

|    |       |                | 9.1.3.2     | Flash Speed                            |     |

|    |       |                | 9.1.3.4     | Lock Regions                           |     |

|    |       |                | 9.1.3.5     | Security Bit Feature                   |     |

|    |       |                | 9.1.3.6     | Calibration Bits                       |     |

|    |       |                | 9.1.3.7     | Unique Identifier                      |     |

|    |       |                | 9.1.3.8     | User Signature                         | 44  |

|    |       |                | 9.1.3.9     | Fast Flash Programming Interface       | 44  |

|     |                                                                                      |                                                                                                                                       | 9.1.3.10                                                                                                     | SAM-BA Boot                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                              |

|-----|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

|     |                                                                                      | 9.1.4                                                                                                                                 | 9.1.3.11<br>Boot Strat                                                                                       | GPNVM Bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                              |

|     |                                                                                      |                                                                                                                                       |                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                              |

| 10. | Syste                                                                                |                                                                                                                                       |                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                              |

|     | 10.1                                                                                 |                                                                                                                                       |                                                                                                              | and Peripherals Mapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                              |

|     | 10.2                                                                                 |                                                                                                                                       |                                                                                                              | rownout and Supply Monitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                              |

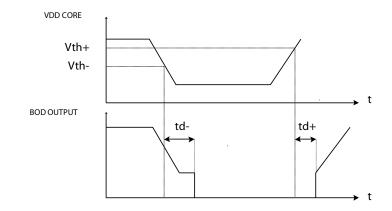

|     |                                                                                      | 10.2.1<br>10.2.2                                                                                                                      | Power-On<br>Brownout                                                                                         | -Reset<br>Detector on VDDCORE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 47<br>47                                                                                                                                     |

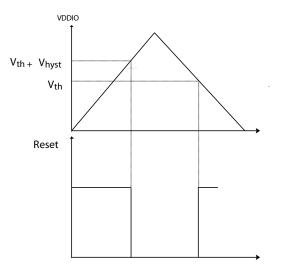

|     |                                                                                      | 10.2.3                                                                                                                                |                                                                                                              | pnitor on VDDIO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                              |

|     | 10.3                                                                                 |                                                                                                                                       |                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                              |

|     | 10.4                                                                                 |                                                                                                                                       |                                                                                                              | SUPC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                              |

|     | 10.5<br>10.6                                                                         |                                                                                                                                       |                                                                                                              | nt Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                              |

|     | 10.0                                                                                 |                                                                                                                                       | •                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                              |

|     | 10.8                                                                                 |                                                                                                                                       |                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                              |

|     | 10.9                                                                                 | Real Tir                                                                                                                              | ne Timer                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 50                                                                                                                                           |

|     |                                                                                      |                                                                                                                                       |                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                              |

|     |                                                                                      |                                                                                                                                       |                                                                                                              | Backup Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                              |

|     |                                                                                      |                                                                                                                                       |                                                                                                              | iterrupt Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                              |

|     |                                                                                      |                                                                                                                                       |                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                              |

|     |                                                                                      |                                                                                                                                       |                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                              |

|     | 10.16                                                                                | Periphe                                                                                                                               | ral Identifie                                                                                                | rs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 53                                                                                                                                           |

|     | 10.17                                                                                |                                                                                                                                       | 0                                                                                                            | Iultiplexing on I/O Lines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                              |

|     |                                                                                      |                                                                                                                                       |                                                                                                              | oller A Multiplexing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                              |

|     |                                                                                      |                                                                                                                                       |                                                                                                              | oller B Multiplexing<br>oller C Multiplexing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                              |

|     |                                                                                      |                                                                                                                                       |                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                              |

| 11. | Emb                                                                                  |                                                                                                                                       | Periphera                                                                                                    | Is Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 56                                                                                                                                         |

|     |                                                                                      |                                                                                                                                       |                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                              |

|     | 11.1                                                                                 |                                                                                                                                       |                                                                                                              | (TWI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                              |

|     | 11.2                                                                                 | Universa                                                                                                                              | al Asynchro                                                                                                  | (TWI)<br>nous Receiver Transceiver (UART)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 56                                                                                                                                           |

|     | 11.2<br>11.3                                                                         | Universa<br>USART                                                                                                                     | al Asynchro                                                                                                  | (TWI)<br>onous Receiver Transceiver (UART)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 56<br>56                                                                                                                                     |

|     | 11.2                                                                                 | Universa<br>USART<br>Synchro                                                                                                          | al Asynchro<br>mous Seria                                                                                    | (TWI)<br>nous Receiver Transceiver (UART)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 56<br>56<br>57                                                                                                                               |

|     | 11.2<br>11.3<br>11.4                                                                 | Universa<br>USART<br>Synchro<br>Timer C<br>Pulse W                                                                                    | al Asynchro<br>mous Seria<br>ounter (TC)<br>/idth Modula                                                     | (TWI)<br>onous Receiver Transceiver (UART)<br>I Controller (SSC)<br>)<br>ation Controller (PWM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 56<br>56<br>57<br>57<br>57                                                                                                                   |

|     | 11.2<br>11.3<br>11.4<br>11.5<br>11.6<br>11.7                                         | Universa<br>USART<br>Synchro<br>Timer C<br>Pulse W<br>USB De                                                                          | al Asynchro<br>mous Seria<br>ounter (TC)<br>/idth Modula<br>vice Port (L                                     | (TWI)<br>onous Receiver Transceiver (UART)<br>I Controller (SSC)<br>).<br>ation Controller (PWM)<br>JDP).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 56<br>56<br>57<br>57<br>57<br>58                                                                                                             |

|     | 11.2<br>11.3<br>11.4<br>11.5<br>11.6<br>11.7<br>11.8                                 | Universa<br>USART<br>Synchro<br>Timer C<br>Pulse W<br>USB De<br>Analog                                                                | al Asynchro<br>onous Seria<br>ounter (TC)<br>/idth Modula<br>vvice Port (L<br>Comparator                     | (TWI)<br>onous Receiver Transceiver (UART)<br>I Controller (SSC)<br>)<br>ation Controller (PWM)<br>JDP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 56<br>56<br>57<br>57<br>57<br>58<br>58                                                                                                       |

|     | 11.2<br>11.3<br>11.4<br>11.5<br>11.6<br>11.7<br>11.8<br>11.9                         | Universa<br>USART<br>Synchro<br>Timer C<br>Pulse W<br>USB De<br>Analog O<br>Cyclic R                                                  | al Asynchro<br>onous Seria<br>ounter (TC)<br>/idth Modula<br>vice Port (L<br>Comparator<br>tedundancy        | (TWI)<br>onous Receiver Transceiver (UART)<br>I Controller (SSC)<br>ation Controller (PWM)<br>JDP)<br>r<br>v Check Calculation Unit (CRCCU)                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 56<br>56<br>57<br>57<br>57<br>58<br>58<br>59                                                                                                 |

|     | 11.2<br>11.3<br>11.4<br>11.5<br>11.6<br>11.7<br>11.8<br>11.9                         | Universa<br>USART<br>Synchro<br>Timer C<br>Pulse W<br>USB De<br>Analog O<br>Cyclic R                                                  | al Asynchro<br>onous Seria<br>ounter (TC)<br>/idth Modula<br>vice Port (L<br>Comparator<br>tedundancy        | (TWI)<br>onous Receiver Transceiver (UART)<br>I Controller (SSC)<br>)<br>ation Controller (PWM)<br>JDP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 56<br>56<br>57<br>57<br>57<br>58<br>58<br>59                                                                                                 |

| 12. | 11.2<br>11.3<br>11.4<br>11.5<br>11.6<br>11.7<br>11.8<br>11.9<br>11.10                | Universa<br>USART<br>Synchro<br>Timer C<br>Pulse W<br>USB De<br>Analog<br>Cyclic R<br>PLC Bri                                         | al Asynchro<br>onous Seria<br>ounter (TC)<br>/idth Modula<br>vice Port (L<br>Comparator<br>edundancy<br>gde  | (TWI)<br>onous Receiver Transceiver (UART)<br>I Controller (SSC)<br>ation Controller (PWM)<br>JDP)<br>r<br>v Check Calculation Unit (CRCCU)                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 56<br>57<br>57<br>57<br>57<br>58<br>58<br>59<br>59                                                                                           |

| 12. | 11.2<br>11.3<br>11.4<br>11.5<br>11.6<br>11.7<br>11.8<br>11.9<br>11.10                | Universa<br>USART<br>Synchro<br>Timer C<br>Pulse W<br>USB De<br>Analog<br>Cyclic R<br>PLC Bri<br>ME PLC                               | al Asynchro<br>onous Seria<br>ounter (TC)<br>/idth Modula<br>wice Port (L<br>Comparator<br>dedundancy<br>gde | (TWI)<br>onous Receiver Transceiver (UART)<br>I Controller (SSC)<br>ation Controller (PWM)<br>JDP)<br>JDP)<br>r.<br>c Check Calculation Unit (CRCCU)<br>iver<br>IE PHY Layer                                                                                                                                                                                                                                                                                                                                                                                                                       | 56<br>57<br>57<br>57<br>58<br>58<br>59<br>59<br>60<br>61                                                                                     |

| 12. | 11.2<br>11.3<br>11.4<br>11.5<br>11.6<br>11.7<br>11.8<br>11.9<br>11.10<br><b>PRIM</b> | Universa<br>USART<br>Synchro<br>Timer C<br>Pulse W<br>USB De<br>Analog<br>Cyclic R<br>PLC Bri<br>ME PLC                               | al Asynchro<br>onous Seria<br>ounter (TC)<br>/idth Modula<br>vice Port (L<br>Comparator<br>tedundancy<br>gde | (TWI)<br>onous Receiver Transceiver (UART)<br>I Controller (SSC)<br>ation Controller (PWM)<br>JDP)<br>JDP)<br>c Check Calculation Unit (CRCCU)<br>c Check Calculation Unit (CRCCU)<br>iver<br>IE PHY Layer                                                                                                                                                                                                                                                                                                                                                                                         | 56<br>57<br>57<br>57<br>57<br>58<br>58<br>59<br>59<br>60<br>61<br>61                                                                         |

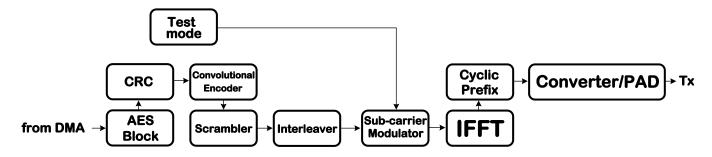

| 12. | 11.2<br>11.3<br>11.4<br>11.5<br>11.6<br>11.7<br>11.8<br>11.9<br>11.10<br><b>PRIM</b> | Universa<br>USART.<br>Synchro<br>Timer C<br>Pulse W<br>USB De<br>Analog<br>Cyclic R<br>PLC Bri<br><b>/E PLC</b><br>SAM4SI             | al Asynchro<br>onous Seria<br>ounter (TC)<br>/idth Modula<br>vice Port (L<br>Comparator<br>tedundancy<br>gde | (TWI)<br>onous Receiver Transceiver (UART)<br>I Controller (SSC)<br>ation Controller (PWM)<br>JDP)<br>JDP)<br>check Calculation Unit (CRCCU)<br>check Calculation Unit (CRCCU)<br>iver<br>IE PHY Layer<br>32A PHY Layer<br>Transmission and Reception branches                                                                                                                                                                                                                                                                                                                                     | 56<br>57<br>57<br>57<br>57<br>58<br>58<br>59<br>59<br>60<br>61<br>61<br>62                                                                   |

| 12. | 11.2<br>11.3<br>11.4<br>11.5<br>11.6<br>11.7<br>11.8<br>11.9<br>11.10<br><b>PRIM</b> | Universa<br>USART.<br>Synchro<br>Timer C<br>Pulse W<br>USB De<br>Analog<br>Cyclic R<br>PLC Bri<br><b>/E PLC</b><br>SAM4SI             | al Asynchro<br>onous Seria<br>ounter (TC)<br>/idth Modula<br>vice Port (L<br>Comparator<br>tedundancy<br>gde | (TWI)<br>onous Receiver Transceiver (UART)<br>I Controller (SSC)<br>ation Controller (PWM)<br>JDP)<br>JDP)<br>c Check Calculation Unit (CRCCU)<br>c Check Calculation Unit (CRCCU)<br>iver<br>ZA PHY Layer<br>32A PHY Layer<br>Transmission and Reception branches<br>Carrier Detection                                                                                                                                                                                                                                                                                                            | 56<br>57<br>57<br>57<br>57<br>57<br>58<br>59<br>59<br>60<br>61<br>61<br>62<br>62                                                             |

| 12. | 11.2<br>11.3<br>11.4<br>11.5<br>11.6<br>11.7<br>11.8<br>11.9<br>11.10<br><b>PRIM</b> | Universa<br>USART.<br>Synchro<br>Timer C<br>Pulse W<br>USB De<br>Analog<br>Cyclic R<br>PLC Bri<br><b>/E PLC</b><br>SAM4SI             | al Asynchro<br>onous Seria<br>ounter (TC)<br>/idth Modula<br>vice Port (L<br>Comparator<br>tedundancy<br>gde | (TWI)<br>onous Receiver Transceiver (UART)<br>I Controller (SSC)<br>ation Controller (PWM)<br>JDP)<br>JDP)<br>r<br>Check Calculation Unit (CRCCU)<br>iver<br>iver<br>ZA PHY Layer<br>32A PHY Layer<br>Transmission and Reception branches<br>Carrier Detection<br>Analog Front End control<br>Power Supply Sensing: VSENSE and PSENSE                                                                                                                                                                                                                                                              | 56<br>57<br>57<br>57<br>57<br>58<br>58<br>59<br>60<br>61<br>61<br>62<br>62<br>63<br>63                                                       |

| 12. | 11.2<br>11.3<br>11.4<br>11.5<br>11.6<br>11.7<br>11.8<br>11.9<br>11.10<br><b>PRIM</b> | Universa<br>USART.<br>Synchro<br>Timer C<br>Pulse W<br>USB De<br>Analog<br>Cyclic R<br>PLC Bri<br><b>/E PLC</b><br>SAM4SI             | al Asynchro<br>onous Seria<br>ounter (TC)<br>/idth Modula<br>vice Port (L<br>Comparator<br>tedundancy<br>gde | (TWI)<br>onous Receiver Transceiver (UART)<br>I Controller (SSC)<br>ation Controller (PWM)<br>JDP)<br>JDP)<br>r<br>c Check Calculation Unit (CRCCU)<br>iver<br>iver<br>ZA PHY Layer<br>32A PHY Layer<br>Transmission and Reception branches<br>Carrier Detection<br>Analog Front End control<br>Power Supply Sensing: VSENSE and PSENSE<br>Gain Control                                                                                                                                                                                                                                            | 56<br>57<br>57<br>57<br>57<br>58<br>58<br>58<br>59<br>60<br>61<br>61<br>62<br>63<br>63<br>64                                                 |

| 12. | 11.2<br>11.3<br>11.4<br>11.5<br>11.6<br>11.7<br>11.8<br>11.9<br>11.10<br><b>PRIM</b> | Universa<br>USART.<br>Synchro<br>Timer C<br>Pulse W<br>USB De<br>Analog<br>Cyclic R<br>PLC Bri<br><b>/E PLC</b><br>SAM4SI             | al Asynchro<br>onous Seria<br>ounter (TC)<br>/idth Modula<br>vice Port (L<br>Comparator<br>tedundancy<br>gde | (TWI)<br>onous Receiver Transceiver (UART)<br>I Controller (SSC)<br>ation Controller (PWM)<br>JDP)<br>JDP)<br>r<br>Check Calculation Unit (CRCCU)<br>iver<br>Check Calculation Unit (CRCCU)<br>Transmission and Reception branches<br>Carrier Detection<br>Analog Front End control<br>Power Supply Sensing: VSENSE and PSENSE<br>Gain Control<br>Line Impedance Control                                                                                                                                                                                                                           | 56<br>57<br>57<br>57<br>57<br>58<br>58<br>59<br>59<br>60<br>61<br>61<br>62<br>62<br>63<br>63<br>64<br>64                                     |

| 12. | 11.2<br>11.3<br>11.4<br>11.5<br>11.6<br>11.7<br>11.8<br>11.9<br>11.10<br><b>PRIM</b> | Universa<br>USART.<br>Synchro<br>Timer C<br>Pulse W<br>USB De<br>Analog<br>Cyclic R<br>PLC Bri<br><b>/E PLC</b><br>SAM4SI             | Al Asynchro<br>onous Seria<br>ounter (TC)<br>/idth Modula<br>vice Port (L<br>Comparator<br>dedundancy<br>gde | (TWI)<br>onous Receiver Transceiver (UART)<br>I Controller (SSC)<br>ation Controller (PWM)<br>JDP)<br>JDP)<br>r<br>c Check Calculation Unit (CRCCU)<br>iver<br><br>iver<br><br>ZA PHY Layer<br>32A PHY Layer<br>Transmission and Reception branches<br>Carrier Detection<br>Analog Front End control<br>Power Supply Sensing: VSENSE and PSENSE<br>Gain Control<br>Line Impedance Control<br>TxRx Control<br>meters                                                                                                                                                                                | 56<br>57<br>57<br>57<br>57<br>58<br>59<br>59<br>60<br>61<br>61<br>62<br>63<br>63<br>64<br>64<br>65<br>65                                     |

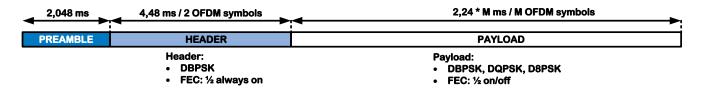

| 12. | 11.2<br>11.3<br>11.4<br>11.5<br>11.6<br>11.7<br>11.8<br>11.9<br>11.10<br><b>PRIM</b> | Universa<br>USART,<br>Synchro<br>Timer C<br>Pulse W<br>USB De<br>Analog O<br>Cyclic R<br>PLC Bri<br><b>/E PLC</b><br>SAM4SI<br>12.1.1 | al Asynchro<br>onous Seria<br>ounter (TC)<br>/idth Modula<br>vice Port (L<br>Comparator<br>tedundancy<br>gde | (TWI)<br>onous Receiver Transceiver (UART)<br>I Controller (SSC)<br>ation Controller (PWM)<br>JDP)<br>JDP)<br>r<br>Check Calculation Unit (CRCCU)<br>iver<br>Check Calculation Unit (CRCCU)<br>iver<br>Physical control CRCCU<br><br>Analog Front End control branches<br>Carrier Detection<br>Analog Front End control<br>Power Supply Sensing: VSENSE and PSENSE<br>Gain Control<br>Line Impedance Control<br>TxRx Control<br>meters<br>cocal Data Unit (PPDU) Format                                                                                                                            | 56<br>57<br>57<br>57<br>57<br>58<br>59<br>59<br>60<br>61<br>62<br>63<br>63<br>64<br>64<br>65<br>65<br>66                                     |

| 12. | 11.2<br>11.3<br>11.4<br>11.5<br>11.6<br>11.7<br>11.8<br>11.9<br>11.10<br><b>PRIM</b> | Universa<br>USART,<br>Synchro<br>Timer C<br>Pulse W<br>USB De<br>Analog O<br>Cyclic R<br>PLC Bri<br><b>/E PLC</b><br>SAM4SI<br>12.1.1 | al Asynchro<br>onous Seria<br>ounter (TC)<br>/idth Modula<br>vice Port (L<br>Comparator<br>tedundancy<br>gde | (TWI)<br>onous Receiver Transceiver (UART)<br>I Controller (SSC)<br>ation Controller (PWM)<br>JDP)<br>JDP)<br>r<br>Check Calculation Unit (CRCCU)<br>iver<br>Check Calculation Unit (CRCCU)<br>iver<br>Physical control CRCCU<br>iver<br>Analog Front End control branches<br>Carrier Detection<br>Analog Front End control<br>Power Supply Sensing: VSENSE and PSENSE<br>Gain Control<br>Line Impedance Control<br>TxRx Control<br>meters<br>cocal Data Unit (PPDU) Format                                                                                                                        | 56<br>57<br>57<br>57<br>58<br>58<br>59<br>59<br>60<br>61<br>62<br>63<br>63<br>63<br>64<br>65<br>65<br>66<br>66                               |

| 12. | 11.2<br>11.3<br>11.4<br>11.5<br>11.6<br>11.7<br>11.8<br>11.9<br>11.10<br><b>PRIM</b> | Universa<br>USART,<br>Synchro<br>Timer C<br>Pulse W<br>USB De<br>Analog O<br>Cyclic R<br>PLC Bri<br><b>/E PLC</b><br>SAM4SI<br>12.1.1 | al Asynchro<br>onous Seria<br>ounter (TC)<br>/idth Modula<br>vice Port (L<br>Comparator<br>tedundancy<br>gde | (TWI)<br>onous Receiver Transceiver (UART)<br>I Controller (SSC)<br>ation Controller (PWM)<br>JDP)<br>JDP)<br>r<br>Check Calculation Unit (CRCCU)<br>iver<br>Check Calculation Unit (CRCCU)<br>iver<br>Physical control CRCCU<br>iver<br>Analog Front End control branches<br>Carrier Detection<br>Analog Front End control<br>Power Supply Sensing: VSENSE and PSENSE<br>Gain Control<br>Line Impedance Control<br>TxRx Control<br>Deters<br>cocal Data Unit (PPDU) Format                                                                                                                        | 56<br>57<br>57<br>57<br>58<br>58<br>59<br>59<br>60<br>61<br>62<br>63<br>63<br>63<br>64<br>65<br>66<br>66<br>68                               |

| 12. | 11.2<br>11.3<br>11.4<br>11.5<br>11.6<br>11.7<br>11.8<br>11.9<br>11.10<br><b>PRIM</b> | Universa<br>USART,<br>Synchro<br>Timer C<br>Pulse W<br>USB De<br>Analog O<br>Cyclic R<br>PLC Bri<br><b>/E PLC</b><br>SAM4SI<br>12.1.1 | al Asynchro<br>onous Seria<br>ounter (TC)<br>/idth Modula<br>vice Port (L<br>Comparator<br>tedundancy<br>gde | (TWI)<br>onous Receiver Transceiver (UART)<br>I Controller (SSC)<br>ation Controller (PWM)<br>JDP)<br>v Check Calculation Unit (CRCCU)<br>v Check Calculation Unit (CRCCU)<br>iver<br>iver<br>22A PHY Layer<br>32A PHY Layer<br>Transmission and Reception branches<br>Carrier Detection<br>Analog Front End control<br>Power Supply Sensing: VSENSE and PSENSE<br>Gain Control<br>Line Impedance Control<br>TxRx Control<br>Deters<br>Deters<br>Deters<br>Deters<br>PHY_SFR Register<br>SYS_CONFIG Register                                                                                       | 56<br>57<br>57<br>57<br>57<br>58<br>59<br>59<br>60<br>61<br>62<br>62<br>63<br>63<br>64<br>65<br>66<br>68<br>68<br>68<br>69                   |

| 12. | 11.2<br>11.3<br>11.4<br>11.5<br>11.6<br>11.7<br>11.8<br>11.9<br>11.10<br><b>PRIM</b> | Universa<br>USART,<br>Synchro<br>Timer C<br>Pulse W<br>USB De<br>Analog O<br>Cyclic R<br>PLC Bri<br><b>/E PLC</b><br>SAM4SI<br>12.1.1 | al Asynchro<br>onous Seria<br>ounter (TC)<br>/idth Modula<br>vice Port (L<br>Comparator<br>tedundancy<br>gde | (TWI)<br>onous Receiver Transceiver (UART)<br>I Controller (SSC)<br>ation Controller (PWM)<br>JDP)<br>or Check Calculation Unit (CRCCU)<br>iver<br>Check Calculation Unit (CRCCU)<br>iver<br>iver<br>22A PHY Layer<br>32A PHY Layer<br>Transmission and Reception branches<br>Carrier Detection<br>Analog Front End control<br>Power Supply Sensing: VSENSE and PSENSE<br>Gain Control<br>Line Impedance Control<br>TxRx Control<br>Line Impedance Control<br>TxRx Control<br>Detal Data Unit (PPDU) Format<br>ice Specification<br>PHY_SFR Register<br>SYS_CONFIG Register<br>PHY_CONFIG Register | 56<br>57<br>57<br>57<br>58<br>58<br>59<br>59<br>61<br>62<br>62<br>63<br>63<br>64<br>65<br>65<br>66<br>68<br>68<br>68<br>70                   |

| 12. | 11.2<br>11.3<br>11.4<br>11.5<br>11.6<br>11.7<br>11.8<br>11.9<br>11.10<br><b>PRIM</b> | Universa<br>USART,<br>Synchro<br>Timer C<br>Pulse W<br>USB De<br>Analog O<br>Cyclic R<br>PLC Bri<br><b>/E PLC</b><br>SAM4SI<br>12.1.1 | al Asynchro<br>onous Seria<br>ounter (TC)<br>/idth Modula<br>vice Port (L<br>Comparator<br>tedundancy<br>gde | (TWI)<br>onous Receiver Transceiver (UART)<br>I Controller (SSC)<br>ation Controller (PWM)<br>JDP)<br>v Check Calculation Unit (CRCCU)<br>v Check Calculation Unit (CRCCU)<br>iver<br>iver<br>22A PHY Layer<br>32A PHY Layer<br>Transmission and Reception branches<br>Carrier Detection<br>Analog Front End control<br>Power Supply Sensing: VSENSE and PSENSE<br>Gain Control<br>Line Impedance Control<br>TxRx Control<br>Deters<br>Deters<br>Deters<br>Deters<br>PHY_SFR Register<br>SYS_CONFIG Register                                                                                       | 56<br>57<br>57<br>57<br>57<br>58<br>59<br>59<br>60<br>61<br>61<br>62<br>63<br>63<br>63<br>64<br>65<br>66<br>66<br>68<br>68<br>69<br>70<br>71 |

|      |                  | 12.1.5.6               | ATT_SIGNAL Register                                       |      |

|------|------------------|------------------------|-----------------------------------------------------------|------|

|      |                  | 12.1.5.7               | TX_TIME Registers                                         |      |

|      |                  | 12.1.5.8               | TIMER_FRAME Registers                                     |      |

|      |                  | 12.1.5.9               | TIMER_BEACON_REF Registers                                |      |

|      |                  |                        | RX_LEVEL Registers                                        |      |

|      |                  | 12.1.5.11              | _ 0                                                       |      |

|      |                  | 12.1.5.12              |                                                           |      |

|      |                  | 12.1.5.13              |                                                           | . 80 |

|      |                  | 12.1.5.14              | CINR_MIN Register                                         |      |

|      |                  | 12.1.5.15              | _ 0                                                       |      |

|      |                  |                        | EVM_HEADER Registers                                      | 8/   |

|      |                  | 12.1.5.17              | EVM_PAYLOAD Registers                                     | 85   |

|      |                  | 12.1.5.19              |                                                           |      |

|      |                  |                        | EVM_PAYLOAD_ACUM Registers                                | 87   |

|      |                  |                        | RMS_CALC Register                                         |      |

|      |                  |                        | VSENSE_CONFIG Register                                    |      |

|      |                  | 12.1.5.23              |                                                           | 90   |

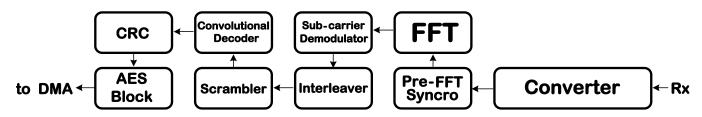

|      |                  | 12.1.5.24              | TTRANS Register                                           |      |

|      |                  |                        | AGC0_KRSSI Register                                       |      |

|      |                  |                        | AGC1 KRSSI Register                                       |      |

|      |                  | 12.1.5.27              |                                                           |      |

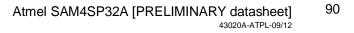

|      |                  |                        | ZERO_CROSS_CONFIG Register                                |      |

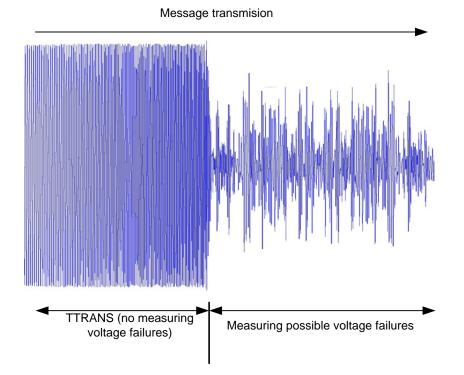

|      |                  |                        | PSENSECYCLES Registers                                    |      |

|      |                  | 12.1.5.30              |                                                           |      |

|      |                  | 12.1.5.31              | PMAX Registers                                            | 98   |

|      |                  | 12.1.5.32              | TRANS_PSENSE Register<br>P_TH Registers                   | 100  |

|      |                  | 12.1.5.33              |                                                           |      |

|      |                  |                        | NUMCYCLES Register                                        | 101  |

|      |                  |                        | A_NUMMILIS Register                                       |      |

|      |                  | 12.1.5.37              | -                                                         |      |

|      |                  |                        | AFE_CTL Register 1                                        |      |

|      |                  |                        | R Registers1                                              |      |

|      |                  | 12.1.5.40              | PHY_ERRORS Registers 1                                    | 107  |

|      |                  | 12.1.5.41              |                                                           | 108  |

|      |                  |                        | AGC_CONFIG Register 1                                     |      |

|      |                  |                        | SAT_TH Registers 1                                        |      |

|      |                  |                        | AGC1_TH Registers 1                                       |      |

|      |                  | 12.1.5.45              |                                                           | 113  |

| 10.0 | 0 4 4 4 4 0      |                        | AGC_PADS Register                                         |      |

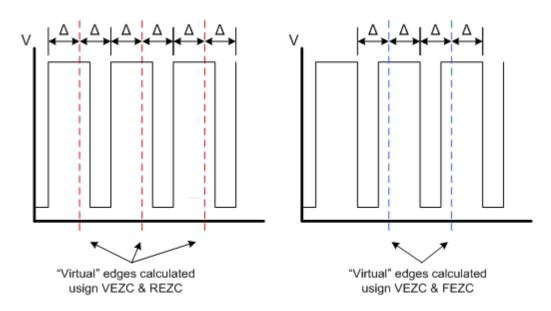

| 12.2 |                  |                        | Layer                                                     |      |

|      | 12.2.1           |                        | dundancy Check (CRC)                                      |      |

|      | 12.2.2<br>12.2.3 |                        | Encryption Standard (AES)1<br>r Registers                 |      |

|      | 12.2.3           | 12.2.3.1               | SNA Registers                                             |      |

|      |                  | 12.2.3.1               | VITERBI_BER_HARD Register 1                               |      |

|      |                  | 12.2.3.3               | VITERBI_BER_SOFT Register1                                |      |

|      |                  | 12.2.3.4               | ERR_CRC32_MAC Registers 1                                 |      |

|      |                  | 12.2.3.5               | ERR_CRC8_MAC Registers 1                                  |      |

|      |                  | 12.2.3.6               | ERR_CRC8_AES Registers 1                                  |      |

|      |                  | 12.2.3.7               | ERR_CRC8_MAC_HD Registers 1                               | 124  |

|      |                  | 12.2.3.8               | ERR_CRC8_PHY Registers1                                   | 125  |

|      |                  | 12.2.3.9               | FALSE_DET_CONFIG Register 1                               |      |

|      |                  | 12.2.3.10              |                                                           |      |

|      |                  | 12.2.3.11              | MAX_LEN_DBPSK Register                                    |      |

|      |                  | 12.2.3.12              | MAX_LEN_DBPSK_VTB Register 1                              |      |

|      |                  | 12.2.3.13              | MAX_LEN_DQPSK Register 1<br>MAX_LEN_DQPSK_VTB Registers 1 | 130  |

|      |                  | 12.2.3.14<br>12.2.3.15 |                                                           |      |

|      |                  | 12.2.3.15              |                                                           |      |

|      |                  | 12.2.3.10              |                                                           |      |

|      |                  |                        | AES_DATA_IN Registers 1                                   |      |

|      |                  |                        | AES_DATA_OUT Registers 1                                  |      |

|      |                  |                        |                                                           |      |

|          |                  | 12.2.3.20 KEY_PERIPH Registers                                                              | 137 |

|----------|------------------|---------------------------------------------------------------------------------------------|-----|

|          |                  | 12.2.3.21 KEY_PHY Registers                                                                 |     |

|          |                  | 12.2.3.22 AES_SFR Register                                                                  | 139 |

|          |                  |                                                                                             |     |

| 13. Ele  |                  | haracteristics                                                                              |     |

| 13.1     | Absolut          | e Maximum Ratings                                                                           | 140 |

| 13.2     | DC Cha           | aracteristics                                                                               | 141 |

| 13.3     | Power (          | Consumption                                                                                 | 148 |

|          | 13.3.1           | Backup Mode Current Consuption                                                              | 148 |

|          |                  | 13.3.1.1 Configuration A                                                                    |     |

|          |                  | 13.3.1.2 Configuration B                                                                    |     |

|          | 13.3.2           | Sleep and Wait Mode Current Consumption                                                     |     |

|          |                  | 13.3.2.1 Sleep Mode                                                                         |     |

|          |                  | 13.3.2.2 Wait Mode                                                                          | 151 |

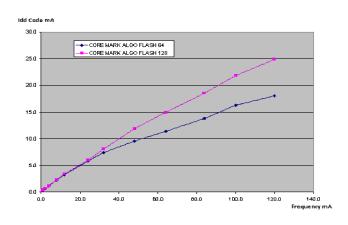

|          | 13.3.3           | Active Mode Power Consumption                                                               |     |

| 40.4     | 13.3.4           | Peripheral Power Consumption in Active Mode                                                 |     |

| 13.4     |                  | or Characteristics                                                                          |     |

|          | 13.4.1           | 32 kHz RC Oscillator Characteristics                                                        |     |

|          | 13.4.2           | 4/8/12 MHz RC Oscillators Characteristics                                                   |     |

|          | 13.4.3           | 32.768 kHz Crystal Oscillator Characteristics                                               |     |

|          | 13.4.4<br>13.4.5 | 32.768 kHz Crystal Characteristics                                                          |     |

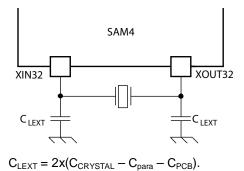

|          | 13.4.5           | 3 to 20 MHz Crystal Oscillator Characteristics                                              |     |

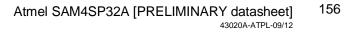

|          | 13.4.0           | 3 to 20 MHz Crystal Characteristics<br>Crystal Oscillator Design Considerations Information | 161 |

|          | 13.4.7           | 13.4.7.1 Choosing a Crystal                                                                 |     |

|          |                  | 13.4.7.2 Printed Circuit Board (PCB)                                                        | 161 |

| 13.5     | PLLA, F          | PLLB Characteristics                                                                        |     |

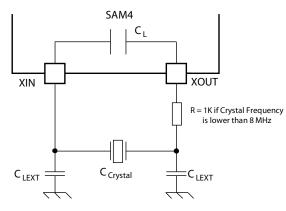

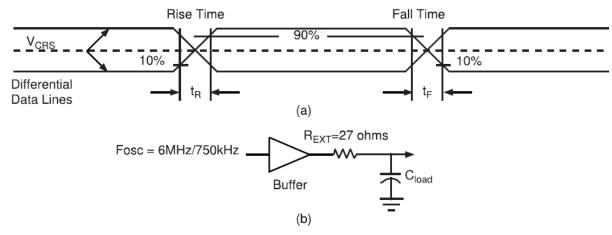

| 13.6     |                  | ansceiver Characteristics                                                                   |     |

| 1010     | 13.6.1           | Typical Connections                                                                         |     |

|          | 13.6.2           | Electrical Characteristics                                                                  |     |

|          | 13.6.3           | Switching Characteristics                                                                   |     |

| 13.7     | Analog           | Comparator Characteristics                                                                  | 165 |

| 13.8     |                  | rature Sensor                                                                               |     |

| 13.9     |                  | aracteristics                                                                               |     |

|          | 13.9.1           | Master Clock Characteristics                                                                |     |

|          | 13.9.2           | I/O Characteristics                                                                         |     |

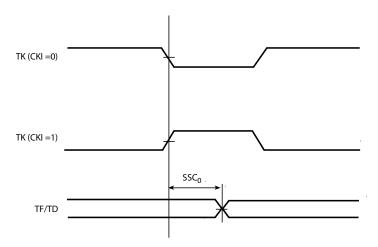

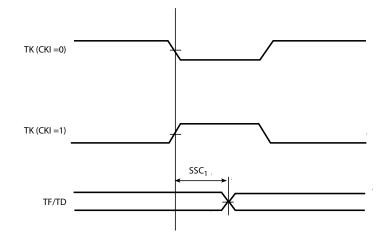

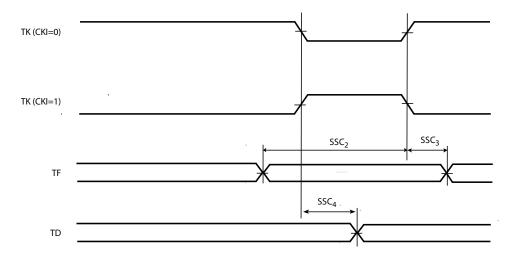

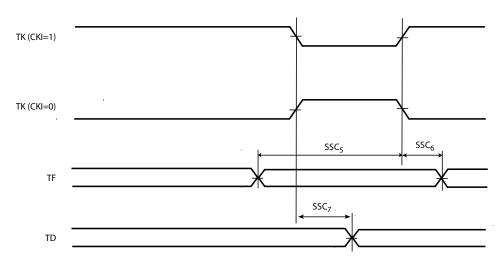

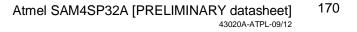

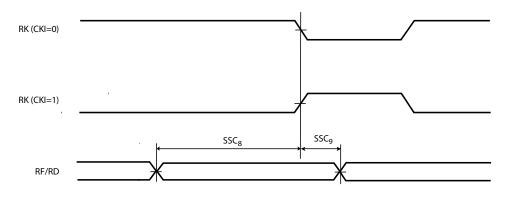

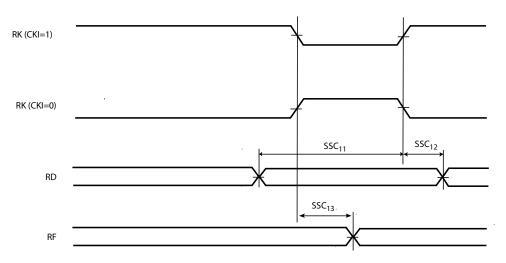

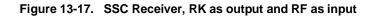

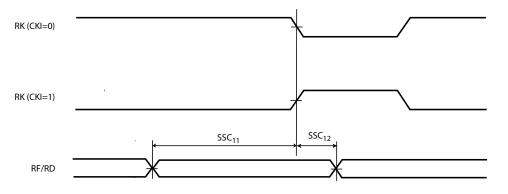

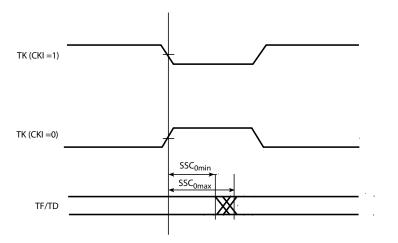

|          | 13.9.3           | SSC Timings                                                                                 |     |

|          |                  | 13.9.3.2 SSC Timings                                                                        |     |

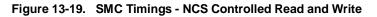

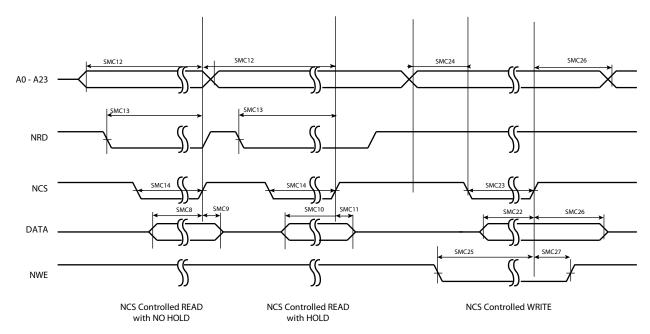

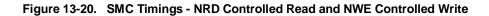

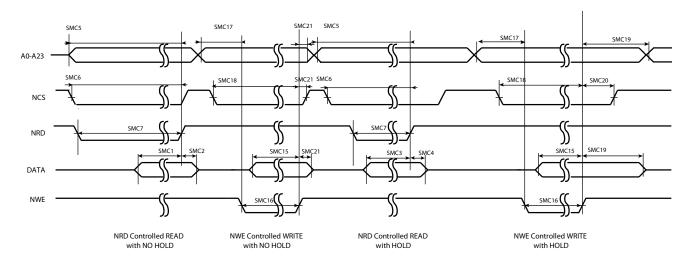

|          | 13.9.4           | SMC Timings                                                                                 |     |

|          |                  | 13.9.4.1 Read Timings                                                                       |     |

|          |                  | 13.9.4.2 Write Timings                                                                      |     |

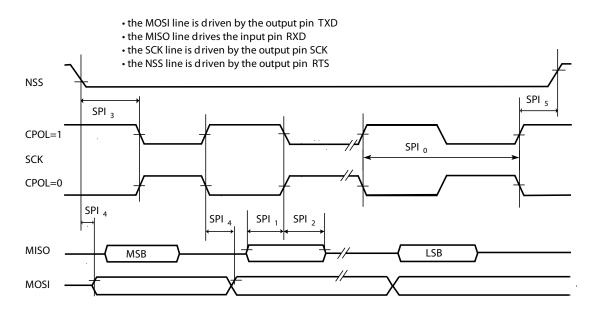

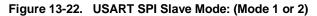

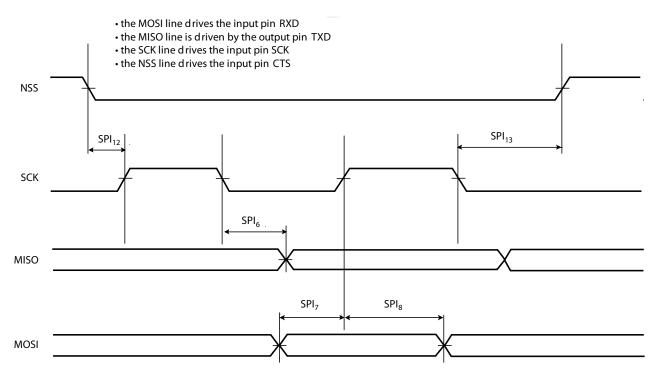

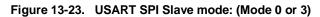

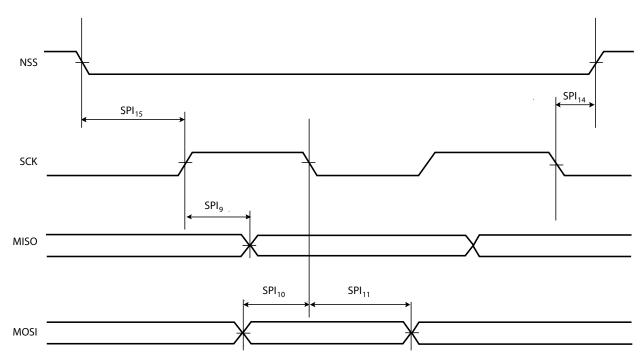

|          | 13.9.5           | USART in SPI Mode Timings                                                                   |     |

|          |                  | 13.9.5.2 USART SPI TImings                                                                  |     |

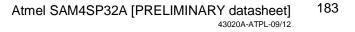

|          | 13.9.6           | Two-wire Serial Interface Characteristics                                                   |     |

| 40.4     | 13.9.7           | Embedded Flash Characteristics                                                              |     |

| 13.1     | 0 Recomi         | mended Operating Conditions                                                                 | 189 |

| 14 Mar   | haniaal          | Characteristics                                                                             | 100 |

| 14.10180 | Jianical         | UIIaIaUICII31163                                                                            | 190 |

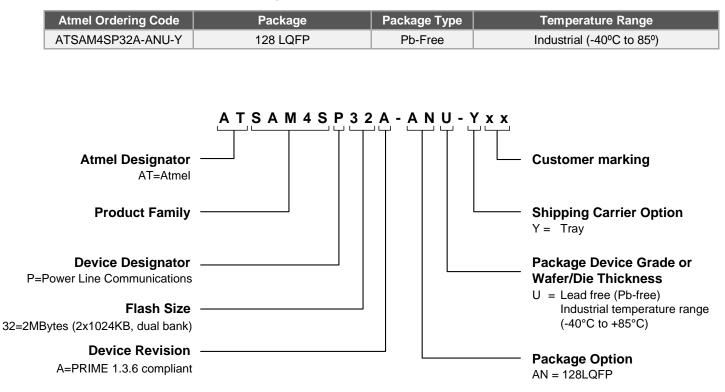

| 15. Ord  | ering Inf        | formation                                                                                   | 191 |

| 16. Rev  | ision Hi         | story                                                                                       | 192 |

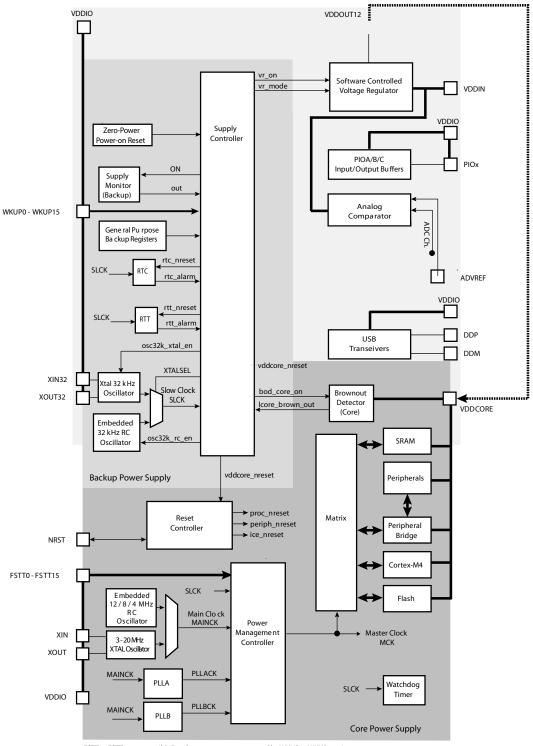

# 1. Block Diagram

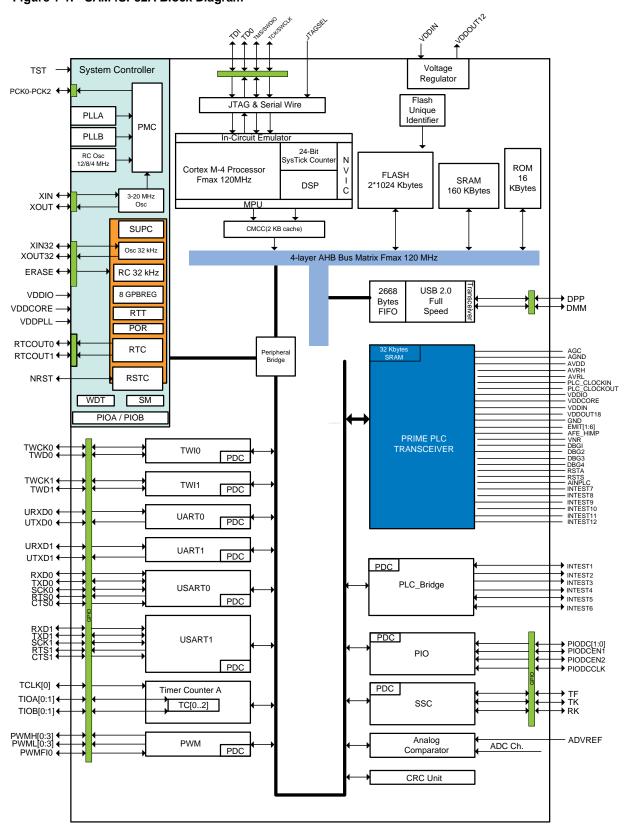

# 2. Package and Pinout

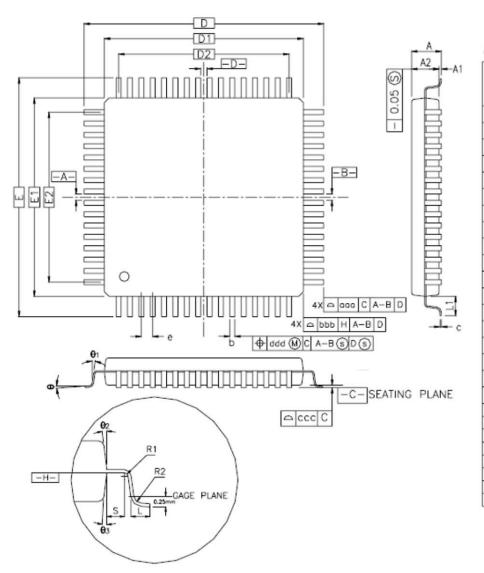

# 2.1 **128-Lead LQFP Package Outline**

Figure 2-1. Orientation of the 128-Lead Package

# 2.2 128-Lead LQFP Pinout

### Table 2-1. SAM4SP32A 128-Lead LQFP pinout

| 1  | ADVREF      | 33 | PC0                     | 65 | INTEST7     | 97  | TDO/TRACESWO/<br>PB5 |

|----|-------------|----|-------------------------|----|-------------|-----|----------------------|

| 2  | GND         | 34 | GND                     | 66 | INTEST10    | 98  | DBG0                 |

| 3  | GND         | 35 | VDDIO                   | 67 | INTEST12    | 99  | JTAGSEL              |

| 4  | AGC         | 36 | PA16/PGMD4              | 68 | INTEST11    | 100 | DBG1                 |

| 5  | GND         | 37 | NC                      | 69 | TDI/PB4     | 101 | DBG2                 |

| 6  | VDDIO       | 38 | PA15/PGMD3              | 70 | VDDIO       | 102 | GND                  |

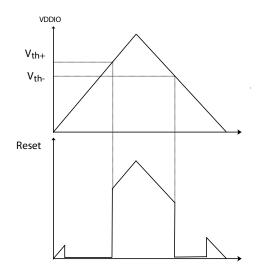

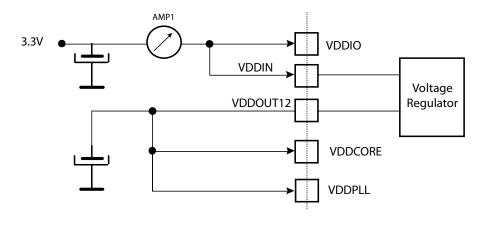

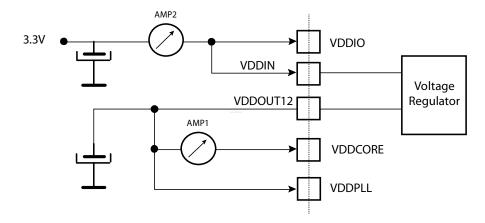

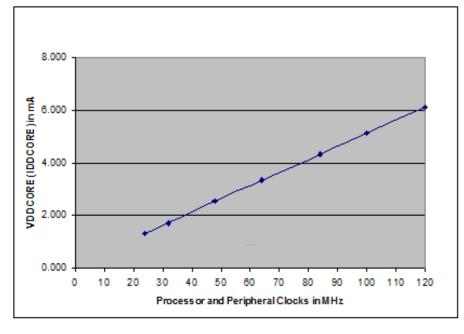

| 7  | AGND        | 39 | INTEST1                 | 71 | PA6/PGMNOE  | 103 | VDDIO                |