# 0.06-4.2GHz SP2T Switch for 3G/4G/5G N78 TRX

### **FEATURES**

- Broadband frequency range: 0.06 to 4.2 GHz

- Low insertion loss: 0.4dB typical @ 2.7 GHz

- High isolation: >23dB @ 2.7 GHz

- Integrated logic

- Small DFN (6-pin, 1.1mm x 0.7 mm x 0.55 mm) package (MSL1, 260 °C per JEDEC J-STD-020)

### **APPLICATIONS**

- Cellular 3G/4G/5G N78 TRX

- Cellular modems, tablets and USB Devices

- Other RF front-end modules

### **GENERAL DESCRIPTION**

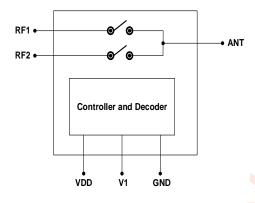

The AW13412 is a SP2T switch with low insertion loss and high Isolation. It can be used to support band switching and mode switching for cellular 3G/4G, data cards and tablets.

The symmetrical design of internal ports makes it convenient for PCB routing and adjustment of receiving and transmitting signals. The band/mode switching is realized by the GPIO pins as referenced in the chip block diagram and the control logic.

The AW13412 is provided in a compact DFN 1.1mm x 0.7mm x 0.55mm-6L package.

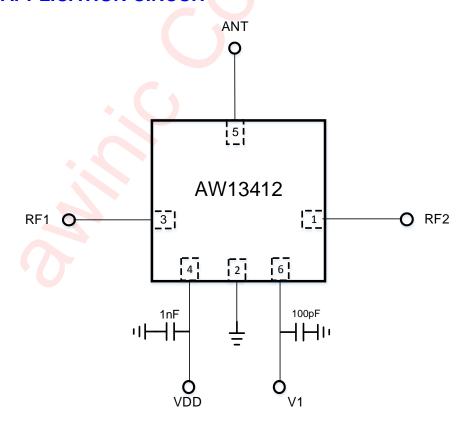

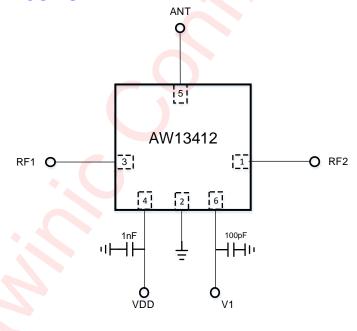

### TYPICAL APPLICATION CIRCUIT

Figure 1 Typical Application Circuit of AW13412

All trademarks are the property of their respective owners.

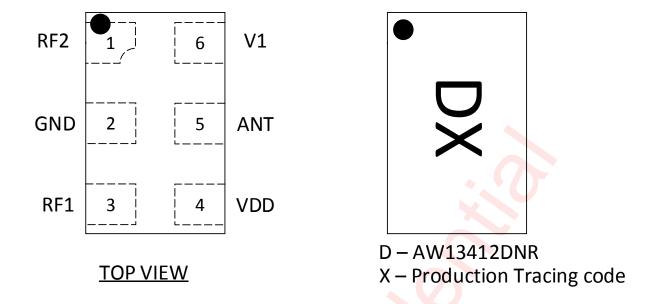

# PIN CONFIGURATION AND TOP MARK

Figure 2 Pin Configuration and Top Mark

## **PIN DEFINITION**

| No. | NAME | DESCRIPTION          |

|-----|------|----------------------|

| 1   | RF2  | RF I/O path 2        |

| 2   | GND  | Ground               |

| 3   | RF1  | RF I/O path 1        |

| 4   | VDD  | DC power supply      |

| 5   | ANT  | Antenna port         |

| 6   | V1   | DC control voltage 1 |

# **FUNCTIONAL BLOCK DIAGRAM**

Figure 3 FUNCTIONAL BLOCK DIAGRAM

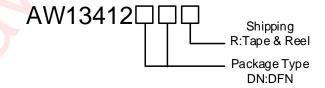

# **ORDERING INFORMATION**

| Part Number | Temperature | Package                   | Marking | Moisture<br>Sensitivity<br>Level | Environmental<br>Information | Delivery<br>Form                |

|-------------|-------------|---------------------------|---------|----------------------------------|------------------------------|---------------------------------|

| AW13412DNR  | -40°C∼85°C  | DFN<br>1.1mmX0.7mm<br>-6L | D       | MSL1                             | ROHS+HF                      | 3000 units/<br>Tape and<br>Reel |

# **ABSOLUTE MAXIMUM RATINGS**(NOTE1)

| PARAMETER                     | RANGE              |                |  |  |

|-------------------------------|--------------------|----------------|--|--|

| Supply Voltage Ran            | ge VDD             | 1.8V to 3.3V   |  |  |

| Control Voltage Range         | V1                 | 0V to 3.3V     |  |  |

| RF input power(RF             | 1/RF2)             | 34dBm          |  |  |

| Operating Free-air Tempe      | erature Range      | -40°C to 85°C  |  |  |

| Storage Temperatur            | e T <sub>STG</sub> | -65°C to 150°C |  |  |

| Lead Temperature (Solderin    | 260°C              |                |  |  |

| Reflow times                  | ≥3                 |                |  |  |

|                               | ESD (NOTE 2)       |                |  |  |

| HBM (ANSI/ESDA/JEDEC          | ±1000V             |                |  |  |

| CDM (JEDEC EIA/JESE           | ±500V              |                |  |  |

| Latch up (JEDEC STANDARD NO.7 | 8E SEPTEMBER 2016) | 100mA          |  |  |

NOTE1: Conditions out of those ranges listed in "absolute maximum ratings" may cause permanent damages to the device. In spite of the limits above, functional operation conditions of the device should within the ranges listed in "recommended operating conditions". Exposure to absolute-maximum-rated conditions for prolonged periods may affect device reliability.

NOTE2: The human body model is a 100pF capacitor discharged through a 1.5k $\Omega$  resistor into each pin.

Test method: ESDA/JEDEC JS-001

### **ELECTRICAL CHARACTERISTICS**

VDD=2.8V, V1=0/1.8V, PIN=0dBm,  $TOP=+25^{\circ}C$ ,  $Z_0=50\Omega$ . (unless otherwise noted)

| PARAMETER        |                          | TEST CONDITION                                                                          | MIN       | TYP  | MAX         | UNIT |  |  |

|------------------|--------------------------|-----------------------------------------------------------------------------------------|-----------|------|-------------|------|--|--|

| DC Specif        | ications                 |                                                                                         |           |      |             |      |  |  |

| VDD              | Supply Voltage           |                                                                                         | 1.8       | 2.8  | 3.1         | V    |  |  |

| IDD              | Supply Current           |                                                                                         |           | 24   |             | μΑ   |  |  |

| VCTL_H<br>VCTL_L | Control Voltage High Low |                                                                                         | 1.35<br>0 | 1.8  | 3.3<br>0.45 | V    |  |  |

| ICTL             | Control Current          | VCTL = 1.8V                                                                             | -1        | -0.1 |             | μΑ   |  |  |

| tPUP             | Power Up Setting Time    | 50% of VDD voltage to<br>90% of final RF power,<br>switching between<br>RF1/2           |           |      | 10          | μS   |  |  |

| tON              | Turn-on Switching Time   | 50% of final control<br>voltage to 90% of final<br>RF power, switching<br>between RF1/2 |           | 0.5  | 1.2         | μS   |  |  |

| RF Specif        | RF Specifications        |                                                                                         |           |      |             |      |  |  |

|                    | PARAMETER                                    | TEST CONDITION                                            | MIN                  | TYP                                  | MAX                        | UNIT                       |

|--------------------|----------------------------------------------|-----------------------------------------------------------|----------------------|--------------------------------------|----------------------------|----------------------------|

| IL                 | Insertion loss(ANT pin to<br>RF1/RF2)        | 0.06-0.1G<br>0.1-1.0G<br>1.0-2.0G<br>2.0-2.7G<br>2.7-4.2G |                      | 0.24<br>0.26<br>0.28<br>0.35<br>0.65 | 0.3<br>0.4<br>0.45<br>0.50 | dB<br>dB<br>dB<br>dB<br>dB |

| ISO                | Isolation (ANT pin to RF1/RF2)               | 0.06-0.1G<br>0.1-1.0G<br>1.0-2.0G<br>2.0-2.7G<br>2.7-4.2G | 37<br>33<br>27<br>23 | 39<br>35<br>31<br>26<br>19           |                            | 8 8 8 8<br>8 8 8           |

| RL                 | Input return loss (ANT pin to<br>RF1/RF2)    | 0.06-0.1G<br>0.1-1.0G<br>1.0-2.0G<br>2.0-2.7G<br>2.7-4.2G | 30<br>23<br>20<br>18 | 32<br>27<br>22<br>20<br>11           |                            | 8 8 8 8<br>8 8 8           |

| 2fo                | Second harmonics (ANT pin to RF1/RF2)        | PIN=+26dBm,<br>0.06-4.2GHz                                |                      | 85                                   |                            | dBc                        |

| 3fo                | Third harmonics (ANT pin to RF1/RF2)         | PIN=+26dBm,<br>0.06-4.2GHz                                |                      | 88                                   |                            | dBc                        |

| P <sub>0.1dB</sub> | 0.1dB Compression Point (ANT pin to RF1/RF2) | 0.06GHz-4.2GHz                                            |                      | 33                                   |                            | dBm                        |

| IIP3               | 3 <sup>rd</sup> Order Input Intercept Point  | @ 2.0GHz,<br>PIN=+26dBm,<br>Δf=1MHz                       |                      | 57                                   |                            | dBm                        |

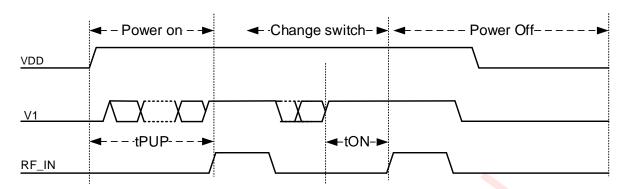

# TIMING DIAGRAM (POWER ON AND OFF SEQUENCE)

It is very important that the user adheres to the correct power-on/off sequence in order to avoid damaging the device. The control signal V1 should be set to 0V unless VDD is set in the operating voltage range.

### Power ON:

- 1) Apply voltage supply --- VDD

- 2) Set Controls---V1

- 3) Apply RF input

Change switch position from one RF port to another:

- 1) Remove RF input

- 2) Change control voltages V1 to set the switch to desired RF port

- 3) Apply RF input

### Power OFF:

- 1) Remove RF input

- 2) Remove control voltages-V1

- 3) Remove VDD input

Figure 6 Power on/Change switch/Power off sequence

# **AW13412 CONTROL LOGIC**

| State | Active Path | V1 |

|-------|-------------|----|

| 0     | ANT to RF1  | 0  |

| 1     | ANT to RF2  | 1  |

# **APPLICATION CIRCUITS**

Figure 6 AW13412 EVB Schematic

Figure 6 AW13412 EVB

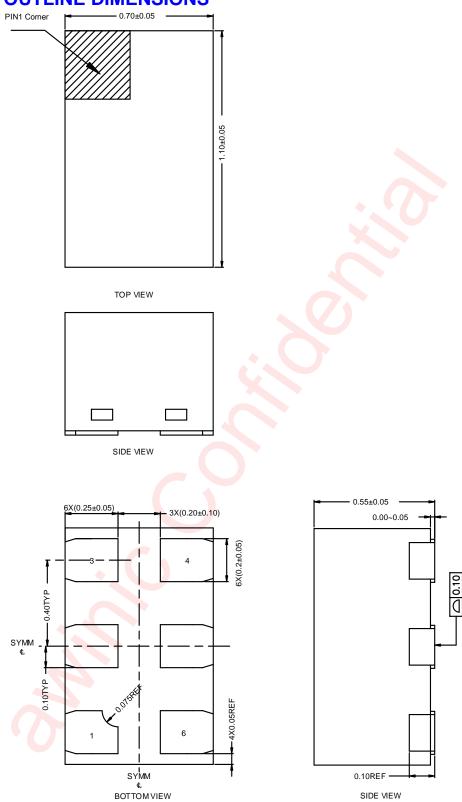

# **PACKAGE OUTLINE DIMENSIONS**

UNIT:MM

Figure 7 Package Outline

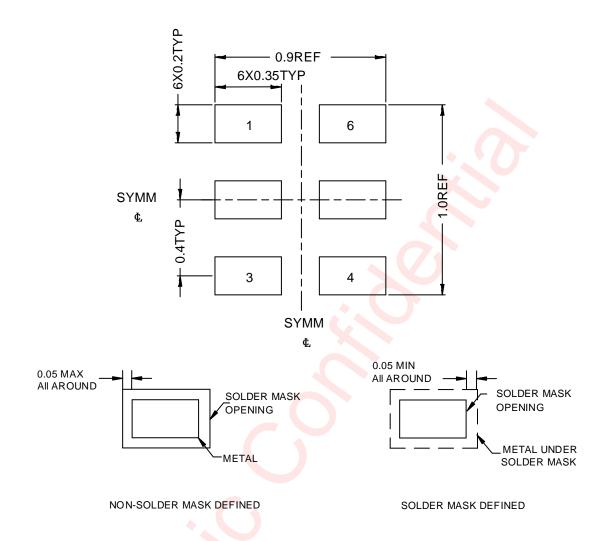

# **LAND PATTERN DATA**

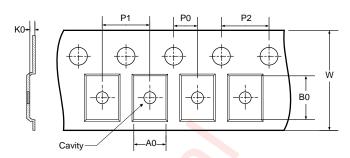

### TAPE AND REEL INFORMATION

# REEL DIMENSIONS D1 D0

### TAPE DIMENSIONS

- A0: Dimension designed to accommodate the component width

- B0: Dimension designed to accommodate the component length

- K0: Dimension designed to accommodate the component thickness

- W: Overall width of the carrier tape

- P0: Pitch between successive cavity centers and sprocket hole

- P1: Pitch between successive cavity centers

- P2: Pitch between sprocket hole

- D1: Reel Diameter

- D0: Reel Width

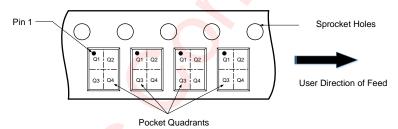

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

### All dimensions are nominal

| D1<br>(mm) | D0<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P0<br>(mm) | P1<br>(mm) | P2<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |  |

|------------|------------|------------|------------|------------|------------|------------|------------|-----------|------------------|--|

| 178        | 8.4        | 0.82       | 1.22       | 0.66       | 2          | 2          | 4          | 8         | Q1               |  |

Figure 8-1 Tape and Reel

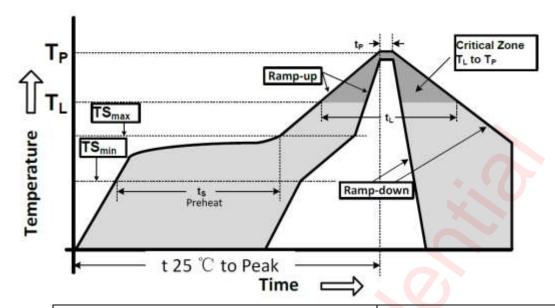

# **REFLOW**

| Reflow Note                             | Spec             |

|-----------------------------------------|------------------|

| Ramp-up rate (TSmax to Tp)              | 3°C/second max.  |

| Preheat temperature (Tsmin to Tsmax)    | 150°C to 200°C   |

| Preheat time (ts)                       | 60 – 180 seconds |

| Time above TL, 217°C (tL)               | 60 – 150 seconds |

| Peak temperature (Tp)                   | 260°C            |

| Time within 5°C of peak temperature(tp) | 20 – 40 seconds  |

| Ramp-down rate                          | 6°C/second max.  |

| Time 25°C to peak temperature           | 8 minutes max.   |

# **REVISION HISTORY**

| Vision | Date     | Change Record                                                                                                                  |  |

|--------|----------|--------------------------------------------------------------------------------------------------------------------------------|--|

| V1.0   | Aug 2017 | Officially Released                                                                                                            |  |

| V1.1   | Nov 2017 | Change datasheet template                                                                                                      |  |

| V1.2   | Oct 2018 | Change:  1. Pin1 marker  2. POD  3. Tape and reel information  4. Typical Application Circuit  5. T <sub>STG</sub> 6. Latch up |  |

| V1.3   | Mar 2019 | Change the spec IL                                                                                                             |  |

| V1.4   | Mar 2019 | <ol> <li>Change the spec IL and features of IL</li> <li>Change maximum VDD to 3.3 V</li> </ol>                                 |  |

| V1.5   | Jun 2019 | Change the spec IL and features of IL     Change the spec ISO and features of ISO                                              |  |

| V1.6   | Mar 2020 | Update 4GHz specification     Change the tON and IDD、ICTL specification                                                        |  |

| V1.7   | Jun 2020 | Change the spec VDD     Update the time of application                                                                         |  |

| V1.8   | Jun 2020 | 1. Change the spec VDD                                                                                                         |  |

| V1.9   | Jul 2020 | <ol> <li>Update 60MHz to 100MHz specification</li> <li>Change the spec P<sub>0.1dB</sub></li> </ol>                            |  |

| V2.0   | Mar 2021 | 1. Update to 4.2GHz specification                                                                                              |  |

### **DISCLAIMER**

Information in this document is believed to be accurate and reliable. However, Shanghai AWINIC Technology Co., Ltd (AWINIC Technology) does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.

AWINIC Technology reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. Customers shall obtain the latest relevant information before placing orders and shall verify that such information is current and complete. This document supersedes and replaces all information supplied prior to the publication hereof.

AWINIC Technology products are not designed, authorized or warranted to be suitable for use in medical, military, aircraft, space or life support equipment, nor in applications where failure or malfunction of an AWINIC Technology product can reasonably be expected to result in personal injury, death or severe property or environmental damage. AWINIC Technology accepts no liability for inclusion and/or use of AWINIC Technology products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

Applications that are described herein for any of these products are for illustrative purposes only. AWINIC Technology makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

All products are sold subject to the general terms and conditions of commercial sale supplied at the time of order acknowledgement.

Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

Reproduction of AWINIC information in AWINIC data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. AWINIC is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of AWINIC components or services with statements different from or beyond the parameters stated by AWINIC for that component or service voids all express and any implied warranties for the associated AWINIC component or service and is an unfair and deceptive business practice. AWINIC is not responsible or liable for any such statements.