# Inductorless, Dual Channel 1.0A Flash LED Driver

#### **FEATURES**

- Dual Independent 1.0A LED1/LED2 Current Source

- Flash: 3.91mA~1.0A, 256 levels 3.91mA/level

- Torch: 1.46mA~375mA, 256 levels 1.46mA/level

- > Flash Timeout: 40ms~1.6s, 16 levels

- Optimized Flash LED Current During Low Battery Conditions (IVFM)

- Hardware Strobe Enable (STROBE)

- 400kHz I<sup>2</sup>C: AW36423 (I<sup>2</sup>C Address=0x63)

- 0.4mm Pitch, FCQFN-10L Package

# **APPLICATION**

Smartphone Camera Flash

#### **GENERAL DESCRIPTION**

The AW36423 is a inductorless dual channel 1.0A flash LED driver that provides a high level of adjustability within a ultra-small solution size. The AW36423 includes two current sources which is controlled independently by I<sup>2</sup>C-compatible interface. The AW36423 provides IVFM protection mode to prevent system reset or shutdown under low battery condition.

The AW36423 is controlled via an I<sup>2</sup>C-compatible interface. The main features of the AW36423 include: flash / torch / IR current, flash timeout duration and IVFM. The AW36423 also provides hardware flash pin (STROBE) to control flash event.

The device operates over a -40°C to +85°C ambient temperature range.

The AW36423 is available in small 0.4mm pitch 1.6mm×1.2mm FCQFN-10L package.

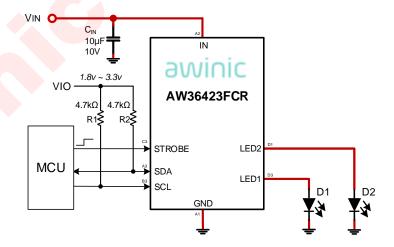

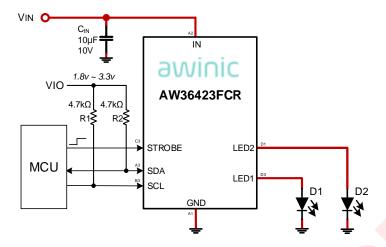

#### TYPICAL APPLICATION CIRCUIT

Fig 1 Typical Application Circuit of AW36423

All trademarks are the property of their respective owners.

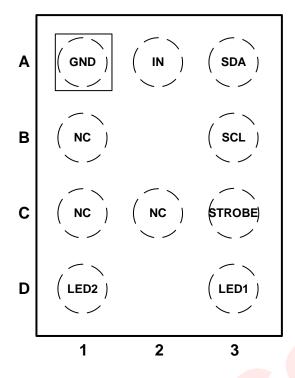

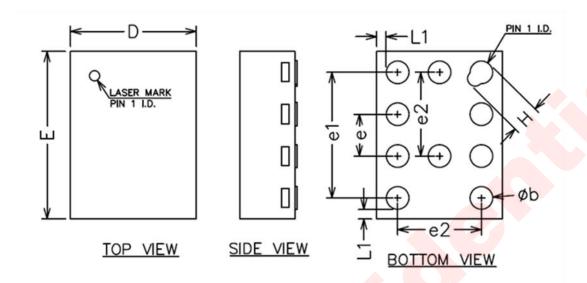

# PIN CONFIGURATION AND TOP MARK

# AW36423FCR Pin Configuration (Top View)

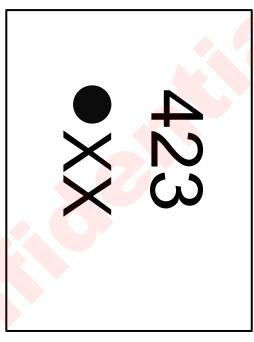

# AW36423FCR Top Mark (Top View)

423 – AW36423FCR XX – Manufacture Tracking Code

Fig 2 Pin Configuration and Top Mark

#### **PIN DEFINITION**

| No.   | NAME   | TYPE   | DESCRIPTION                                                                                                                                       |

|-------|--------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| A1    | GND    | Ground | Ground                                                                                                                                            |

| A2    | IN     | Power  | Input voltage connection. Connect IN to GND with a $10\mu F$ or larger ceramic capacitor.                                                         |

| А3    | SDA    | I/O    | Serial data input/output of the I <sup>2</sup> C interface.                                                                                       |

| B1    | NC     | I/O    | No Connect. Must be floating, for chip test.                                                                                                      |

| В3    | SCL    | I/O    | Serial clock input of the I <sup>2</sup> C interface.                                                                                             |

| C1,C2 | NC     | I/O    | No Connect. Must be floating, for chip test.                                                                                                      |

| C3    | STROBE | I/O    | Active high hardware flash enable. Drive STROBE high to turn on Flash pulse. Internal pull down resistor of $300 k\Omega$ between STROBE and GND. |

| D1    | LED2   | Power  | High-side current source output for flash LED2.                                                                                                   |

| D3    | LED1   | Power  | High-side current source output for flash LED1.                                                                                                   |

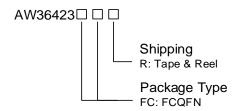

# **ORDERING INFORMATION**

| Part Number | Temperature | Package   | Marking Moisture Sensitivity Level Environmental Information |      | Delivery Form |                              |

|-------------|-------------|-----------|--------------------------------------------------------------|------|---------------|------------------------------|

| AW36423FCR  | -40°C∼85°C  | FCQFN-10L | 423                                                          | MSL1 | ROHS+HF       | 3000 units/<br>Tape and Reel |

# **AWINIC FLASH LED DRIVER SERIES**

| Product | Channels | Туре            | Description                                                  | Package |

|---------|----------|-----------------|--------------------------------------------------------------|---------|

| AW3644  | 2        | Boost           | High Efficiency, Dual Independent 1.5A Flash LED Driver      | CSP-12  |

| AW36414 | 2        | Boost           | High Efficiency, Dual Independent 1.5A Flash LED Driver      | CSP-12  |

| AW3643  | 2        | Boost           | High Efficiency, Dual 1.5A Flash LED Driver                  | CSP-12  |

| AW36413 | 2        | Boost           | High Efficiency, Dual 1.5A Flash LED Driver                  | CSP-12  |

| AW3648  | 1        | Boost           | High Efficiency, 1.5A Flash LED Driver                       | CSP-12  |

| AW3641E | 1        | Charge<br>Pump  | Flash Current & Flash Timer Programmable 1A Flash LED Driver | DFN-10  |

| AW3640  | 1        | Current<br>Sink | 200mA 1-Wire Configurable Front Flash LED Driver             | DFN-6   |

| AW36402 | 1        | Current<br>Sink | 200mA 1-wire Configurable Front Flash LED Driver             | DFN-6   |

| AW36404 | 1        | Current<br>Sink | 400mA 1-wire Configurable Front Flash LED Driver             | DFN-8   |

| AW36406 | 1        | Current<br>Sink | 600mA PWM Configurable Front Flash LED Driver                | DFN-8   |

# **TYPICAL APPLICATION CIRCUITS**

Fig 3 AW36423 Application Circuit

#### **Notice for Typical Application Circuits:**

- 1. Please place  $C_{\text{IN}}$  as close to the chip as possible.

- 2. For the sake of driving capability, the power lines, and the connection lines of LED should be short and wide as possible.

# **ABSOLUTE MAXIMUM RATINGS**(NOTE1)

| PARA                                     | Range                     | Unit                           |              |

|------------------------------------------|---------------------------|--------------------------------|--------------|

| IN, LED1, LED2                           |                           | -0.3 to 6                      | V            |

| SCL, SDA, STROBE                         |                           | -0.3 to (V <sub>IN</sub> +0.3) | V            |

| Continuous power dissipation             |                           | Internally limited             |              |

| Max Junction Temperature T <sub>JM</sub> | NX                        | 155                            | $\mathbb{C}$ |

| Storage Temperature T <sub>STG</sub>     |                           | -65 to 150                     | $\mathbb{C}$ |

| Maximum lead temperature (so             | ldering)                  | 260                            | $^{\circ}$   |

| Junction to Ambient Thermal R            | esistance θ <sub>JA</sub> | 92                             | °C/W         |

|                                          | НВМ                       | ±2000                          | V            |

| ESD, All Pins <sup>(NOTE2)</sup>         | MM                        | ±200                           | V            |

|                                          | CDM                       | ±2000                          | V            |

| Latch-Up<br>JESD78D                      |                           | +IT: +350<br>-IT: -350         | mA           |

# RECOMMENDED OPERATING CONDITIONS

| PARAMETERS                             | Range      | Unit          |

|----------------------------------------|------------|---------------|

| V <sub>IN</sub>                        | 2.7 to 5.5 | V             |

| Junction temperature (T <sub>J</sub> ) | -40 to 125 | ${\mathbb C}$ |

| Ambient temperature (T <sub>A</sub> )  | -40 to 85  | ${\mathbb C}$ |

NOTE1: Conditions out of those ranges listed in "absolute maximum ratings" may cause permanent damages to the device. In spite of the limits above, functional operation conditions of the device should within the ranges listed in "recommended operating conditions". Exposure to absolute-maximum-rated conditions for prolonged periods may affect device reliability.

NOTE2: The human body model is a 100pF capacitor discharged through a 1.5k $\Omega$  resistor into each pin. Test method: MIL-STD-883J Method 3015.9

# **ELECTRICAL CHARACTERISTICS**

Typical limits tested at  $T_A$ =25  $^{\circ}$ C. Minimum and maximum limits apply over the full operating ambient temperature range(-40  $^{\circ}$ C $\leq$ T<sub>A</sub> $\leq$ 85  $^{\circ}$ C). Unless otherwise specified, V<sub>IN</sub>=3.8V.

| Symbol                 | Description                                                    | Test Condition             | Min  | Тур   | Max             | Unit |  |  |

|------------------------|----------------------------------------------------------------|----------------------------|------|-------|-----------------|------|--|--|

| Vin Supply             |                                                                |                            |      |       |                 |      |  |  |

| V <sub>IN</sub>        | Input Operating Range                                          |                            | 2.7  |       | 5.5             | V    |  |  |

| I <sub>SB</sub>        | Standby Supply Current                                         | 2.7V≤VIN≤5.5V, SCL=SDA=0V  |      | 1     | 2               | μΑ   |  |  |

| IQ                     | Quiescent Supply Current                                       |                            |      | 0.2   | 0.5             | mA   |  |  |

| 11//10                 | Under Voltage Lockout                                          | Falling V <sub>IN</sub>    |      | 2.5   |                 | V    |  |  |

| UVLO                   | Threshold                                                      | Rising V <sub>IN</sub>     |      | 2.6   |                 | V    |  |  |

| Current So             | ource Specifications                                           |                            |      |       |                 |      |  |  |

| 1                      | O A                                                            | Flash Code=0xFF=1.0A       | -10% | 1     | 10%             | Α    |  |  |

| I <sub>LED1/2</sub>    | Current Source Accuracy                                        | Torch Code=0x7F=187.5mA    | -10% | 187.5 | 10%             | mA   |  |  |

| V <sub>HR_LED1/2</sub> | Headrage Voltage of LED4/2                                     | Flash Code=0xFF=1.0A       |      | 200   | 300             | mV   |  |  |

|                        | Headroom Voltage of LED1/2                                     | Torch Code=0x7F=187.5mA    |      | 50    | 75              | mV   |  |  |

| T <sub>FLASH</sub>     | Flash Time-out Duration                                        | Reg 0x0B, bits[3:0]="1010" | -5%  | 600   | 5%              | ms   |  |  |

| V <sub>IVFM</sub>      | Input Voltage Flash Monitor Trip<br>Threshold                  | Reg 0x02, bits[3:1]="000"  | -3%  | 2.9   | 3%              | V    |  |  |

| _                      | Thermal Shutdown Threshold                                     |                            |      | 155   |                 |      |  |  |

| $T_{SD}$               | Thermal Shutdown Hysteresis                                    |                            |      | 20    |                 | °C   |  |  |

| I <sup>2</sup> C-Compa | tible Interfa <mark>ce</mark> Spe <mark>cification</mark> s(SC | L,SDA)                     |      |       |                 |      |  |  |

| V <sub>IL</sub>        | Input Logic Low                                                |                            | 0    |       | 0.4             | V    |  |  |

| V <sub>IH</sub>        | Input Logic High                                               |                            | 1.2  |       | V <sub>IN</sub> | V    |  |  |

| V <sub>OL</sub>        | Output Logic Low                                               | I <sub>LOAD</sub> =3mA     |      |       | 0.4             | V    |  |  |

| STROBE V               | oltage Specifications                                          |                            |      | 1     | ,               |      |  |  |

| V <sub>IL</sub>        | Input Logic Low                                                |                            | 0    |       | 0.4             | V    |  |  |

| VIH                    | Input Logic High                                               |                            | 1.2  |       | V <sub>IN</sub> | V    |  |  |

| R <sub>PD</sub>        | Internal Pull Down Resistors                                   |                            |      | 300   |                 | kΩ   |  |  |

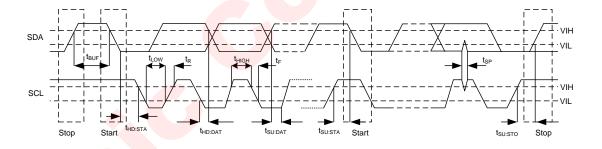

# I<sup>2</sup>C INTERFACE TIMING

| Symbol                | Description                               |          | Min | Тур | Max | Units |

|-----------------------|-------------------------------------------|----------|-----|-----|-----|-------|

| F <sub>SCL</sub>      | Interface Clock Frequency                 |          |     |     | 400 | kHz   |

| _                     | Daglitak Timo                             | SCL      |     | 200 |     | ns    |

| T <sub>DEGLITCH</sub> | Deglitch Time                             | SDA      |     | 250 |     | ns    |

| T <sub>HD:STA</sub>   | (Repeat-Start) Start Condition Hold Time  |          | 0.6 |     |     | μs    |

| T <sub>LOW</sub>      | Low Level Width of SCL                    |          |     |     |     | μs    |

| T <sub>HIGH</sub>     | High Level Width of SCL                   |          |     |     |     | μs    |

| T <sub>SU:STA</sub>   | (Repeat-Start) Start Condition Setup Time |          | 0.6 |     |     | μs    |

| T <sub>HD:DAT</sub>   | Data Hold Time                            |          | 0   |     |     | μs    |

| T <sub>SU:DAT</sub>   | Data Setup Time                           | <u> </u> | 0.1 |     |     | μs    |

| T <sub>R</sub>        | Rising Time of SDA And SCL                |          |     |     | 0.3 | μs    |

| T <sub>F</sub>        | Falling Time of SDA And SCL               |          |     |     | 0.3 | μs    |

| T <sub>SU:STO</sub>   | Stop Condition Setup Time                 |          |     |     |     | μs    |

| T <sub>BUF</sub>      | Time Between Start and Stop Condition     |          | 1.3 |     |     | μs    |

Fig 4 I<sup>2</sup>C INTERFACE TIMING

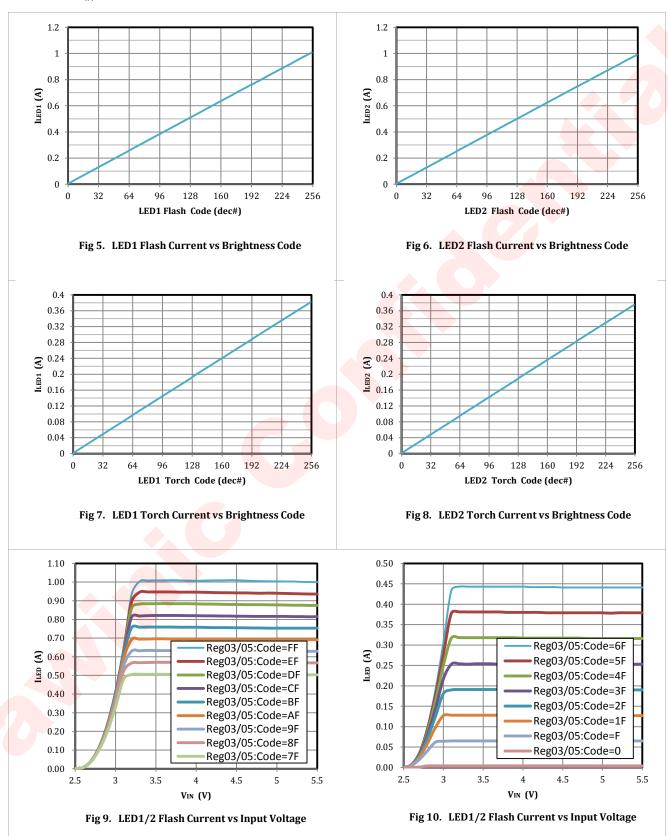

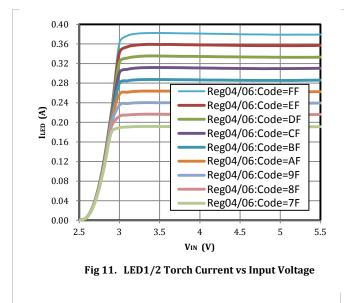

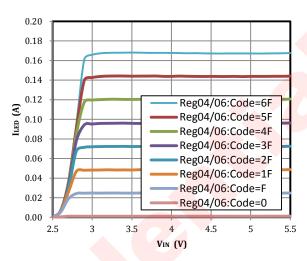

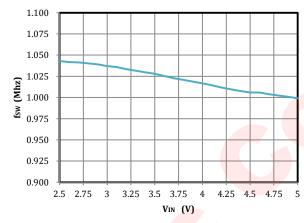

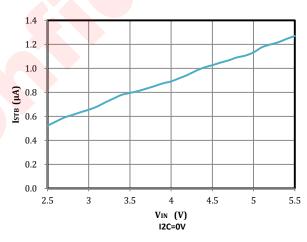

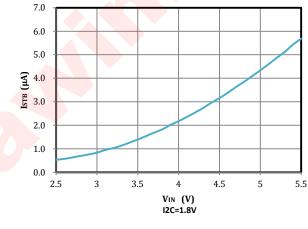

#### TYPICAL CHARACTERISTICS

Ta=25°C, V<sub>IN</sub>=3.8V, VLED=2.9V @ 375mA, IVFM=Off, unless otherwise noted .

#### Typical Characteristics (continued)

Ta=25°C,  $V_{IN}$ =3.8V, VLED=2.9V @ 375mA, IVFM=Off, unless otherwise noted .

Fig 12. LED1/2 Torch Current vs Input Voltage

Fig 13. Oscillator Frequency vs Input Voltage

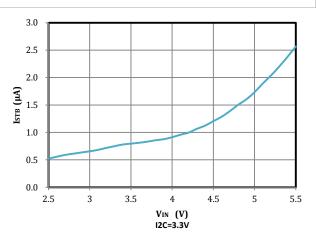

Fig 14. Standby Current vs Input Voltage

Fig 15. Standby Current vs Input Voltage

Fig 16. Standby Current vs Input Voltage

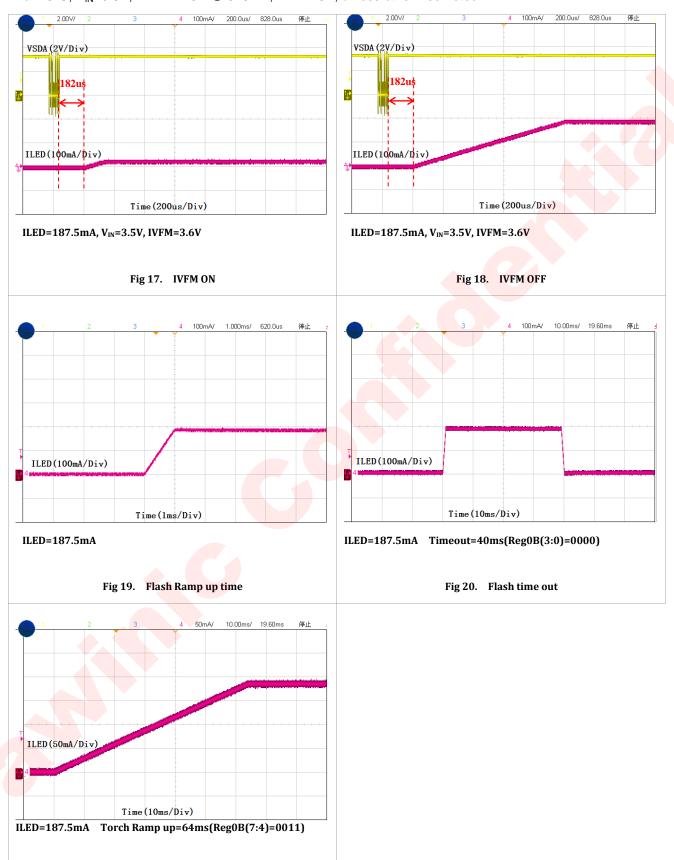

#### Typical Characteristics (continued)

Ta=25°C,  $V_{\text{IN}}$ =3.8V, VLED=2.9V @ 375mA, IVFM=Off, unless otherwise noted .

Fig 21. Torch Ramp up time

#### **DETAILED FUNCTIONAL DESCRIPTION**

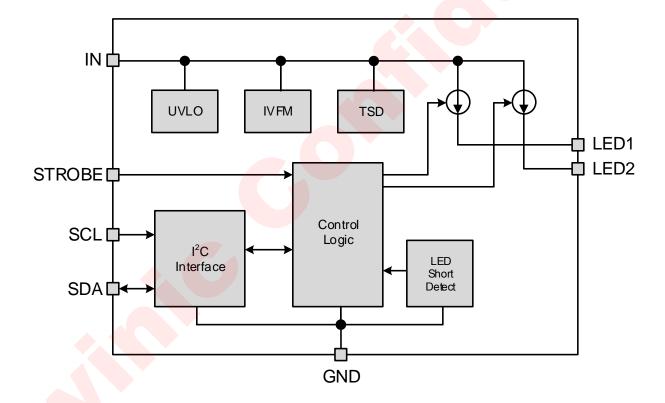

The AW36423 is a high-power Dual-channel LED flash driver capable of delivering up to 1.0A in either of the two source LEDs over the 2.7V to 5.5V input voltage range.

The device has one logic input for a hardware flash enable(STROBE). This logic input has an internal  $300k\Omega(typical)$  pull-down resistor to GND.

The device is controlled via an I<sup>2</sup>C-compatible interface which includes adjustment of the Flash and Torch current levels, changing the Flash Timeout Duration and IVFM level. Additionally, there are flag and status bits that indicate flash current timeout, LED over-temperature condition, LED failure (short), device thermal shutdown, and V<sub>IN</sub> under-voltage conditions.

#### **FUNCTION BLOCK DIAGRAM**

#### **FEATURE DESCRIPTION**

#### **FLASH MODE**

In Flash Mode, the LED current sources (LED1/2) provide 256 target current levels from 3.9mA to 1.0A. The Flash currents are adjusted via the LED1 and LED2 Flash Brightness Registers. Flash mode is activated by the Enable Register(setting M1, M0 to '11'), or by pulling the STROBE pin HIGH when the pin is enabled (Enable Register). Once the Flash sequence is activated, the current sources (LED1/2) ramp up to the programmed Flash current by stepping through all current steps until the programmed current is reached.

When the device is enabled in Flash Mode through the Enable Register, all mode bits in the Enable Register are cleared after a flash timeout event.

#### TORCH MODE

In Torch mode, the LED current sources (LED1/2) provide 256 target current levels from 1.46mA to 375mA. The Torch currents are adjusted via the LED1 and LED2 Torch Brightness Registers. Torch mode is activated by the Enable Register (setting M1, M0 to '10'). Once the TORCH sequence is activated, the active current sources (LED1/2) ramp up to the programmed Torch current by stepping through all current steps until the programmed current is reached. The rate at which the current ramps is determined by the value chosen in the Flash & Torch Timing Register (0x0B 7:4). Torch Mode is not affected by Flash Timeout.

#### IR MODE

In IR Mode, the target LED current is equal to the value stored in the LED1 and LED2 Flash Brightness Registers. When IR mode is enabled (setting M1, M0 to '01'), toggling the STROBE pin enables and disables the LED1/2 current sources(if enabled). The strobe pin can only be set to be Level sensitive, meaning all timing of the IR pulse is externally controlled. In IR Mode, the current sources do not ramp the LED outputs to the target. The current transitions immediately from off to on and then on to off.

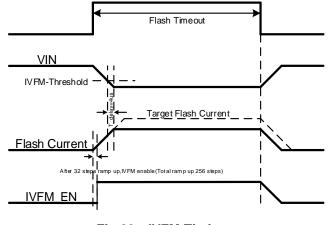

#### INPUT VOLTAGE FLASH MONITOR (IVFM)

The AW36423 has the ability to adjust the flash current based upon the voltage level present at the IN pin utilizing the Input Voltage Flash Monitor (IVFM). The adjustable threshold ranges from 2.9 V to 3.6 V in 100mV steps, with hold mode. The IVFM threshold are controlled by bits[3:0] in the IVFM Register(0x02). The Flags Register has the IVFM flag bit set when the input voltage crosses the IVFM threshold value and after 4us deglitch delay. Additionally, the IVFM threshold sets the input voltage boundary that forces the AW36423 to either stop ramping the flash current after 32 steps ramp up during the startup.

Fig 22 IVFM Timing

#### **FLASH TIMEOUT**

The Flash Timeout period sets the maximum time of one flash event, whether a flash stop command is received or not. The AW36423 has 16 timeout levels ranging from 40ms to 1.6s (see Flash & Torch TIMING CONFIGURATION REGISTER (0X0B) for more detail). Flash Timeout applies to both Flash and IR modes, The mode bits are cleared and bit[0] is set in the Flags register(0x0F) upon a Flash Timeout. This fault flag can be reset to '0' by reading back the Flags Register (0x0F), or by removing power to the AW36423.

#### **UNDERVOLTAGE LOCKOUT (UVLO)**

The AW36423 has an internal comparator that monitors the voltage at IN and forces the AW36423 into standby when the input voltage drops to 2.5 V. If the UVLO monitor threshold is tripped, the UVLO flag bit is set in the Flags Register (0x0F). If the input voltage rises above 2.5 V, the AW36423 is not available for operation until there is an I<sup>2</sup>C read of the Flags Register (0x0F). Upon a read, the Flags register is cleared, and normal operation can resume if the input voltage is greater than 2.5 V.

#### LED SHORT FAULT

The LED Short Fault flags read back a '1' if the device is active in Flash or Torch or IR mode and either active LED output experiences a short condition. An LED short condition is determined if the voltage at LED1 or LED2 goes below 500mV (typ.) while the device is in Flash or Torch or IR mode. There is a deglitch time of 256µs before the LED Short Fault flag is valid. The mode bits are cleared upon an LED short fault. The AW36423 is not available for operation until the LED Short Fault flags is cleared. The LED Short Faults can be reset to '0' by reading back the Flags Register (0x0F), or by removing power to the AW36423.

#### THERMAL SHUTDOWN (TSD)

When the AW36423 die temperature reaches 155°C, the thermal shutdown detection circuit is trips, forcing the AW36423 into standby and writing a '1' to the Thermal Shutdown Fault flag of the Flags Register (0x0F). The AW36423 is only allowed to restart after the Thermal Shutdown Fault flag is cleared. The Thermal Shutdown Faults can be reset to '0' by reading back the Flags Register (0x0F), or by removing power to the AW36423. Upon restart, if the die temperature is still above 155°C, the AW36423 resets the Fault flag and re-enters standby.

#### **PROGRAMMING**

#### **PC INTERFACE**

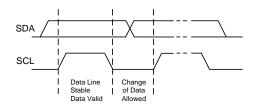

#### Data Validation

When SCL is high level, SDA level must be constant. SDA can be changed only when SCL is low level.

Fig 23 Data Validation Diagram

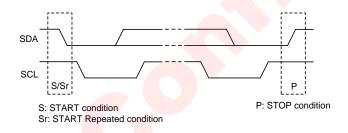

# **fC** Start/Stop

I<sup>2</sup>C start: SDA changes form high level to low level when SCL is high level.

I<sup>2</sup>C stop: SDA changes form low level to high level when SCL is high level.

Fig 24 Start and Stop Conditions

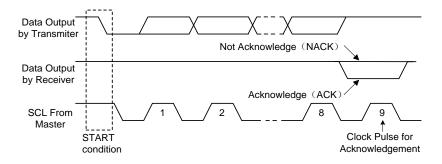

#### ACK (Acknowledgement)

ACK means the successful transfer of I<sup>2</sup>C bus data. After master sends 8bits data, SDA must be released; SDA is pulled to GND by slave device when slave acknowledges.

When master reads, slave device sends 8bit data, releases the SDA and waits for ACK from master. If ACK is send and I<sup>2</sup>C stop is not send by master, slave device sends the next data. If ACK is not send by master, slave device stops to send data and waits for I<sup>2</sup>C stop.

Fig 25 Acknowledgement Diagram

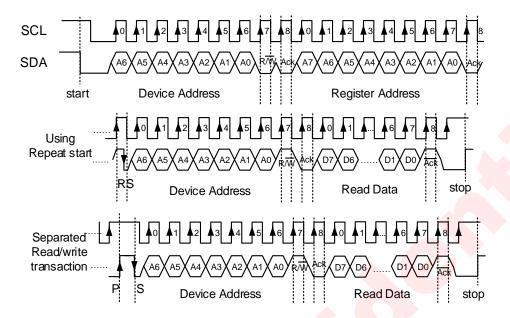

#### Write Cycle

One data bit is transferred during each clock pulse. Data is sampled during the high state of the serial clock (SCL). Consequently, throughout the clock's high period, the data should remain stable. Any changes on the SDA line during the high state of the SCL and in the middle of a transaction, aborts the current transaction. New data should be sent during the low SCL state. This protocol allows a single data line to transfer both command/control information and data using the synchronous serial clock.

Each data transaction is composed of a Start Condition, a number of byte transfers (set by the software) and a Stop Condition to terminate the transaction. Every byte written to the SDA bus must be 8 bits long and is transferred with the most significant bit first. After each byte, an Acknowledge signal must follow.

In a write process, the following steps should be followed:

- Master device generates START condition. The "START" signal is generated by lowering the SDA signal while the SCL signal is high.

- 2) Master device sends slave address (7-bit) and the data direction bit (R/W = 0).

- 3) Slave device sends acknowledge signal if the slave address is correct.

- 4) Master sends control register address (8-bit)

- 5) Slave sends acknowledge signal

- 6) Master sends data byte to be written to the addressed register

- 7) Slave sends acknowledge signal

- 8) If master will send further data bytes the control register address will be incremented by one after acknowledge signal (repeat step 6, 7)

- 9) Master generates STOP condition to indicate write cycle end

Fig 26 I<sup>2</sup>C Write Timing

#### Read Cycle

In a read cycle, the following steps should be followed:

- 1) Master device generates START condition

- 2) Master device sends slave address (7-bit) and the data direction bit (R/W = 0).

- 3) Slave device sends acknowledge signal if the slave address is correct.

- 4) Master sends control register address (8-bit)

- 5) Slave sends acknowledge signal

- 6) Master generates STOP condition followed with START condition or REPEAT START condition

- 7) Master device sends slave address (7-bit) and the data direction bit (R/W = 1).

- 8) Slave device sends acknowledge signal if the slave address is correct.

- 9) Slave sends data byte from addressed register.

- 10) If the master device sends acknowledge signal, the slave device will increase the control register

address by one, then send the next data from the new addressed register.

11) If the master device generates STOP condition, the read cycle is ended.

Fig 27 I<sup>2</sup>C Read Timing

# **REGISTER CONFIGURATION**

# **REGISTER LIST**

| Register name                  | Address(HEX) | Read/Write | Default Value |

|--------------------------------|--------------|------------|---------------|

| Chip ID Register               | 0x00         | Read       | 0x17          |

| Enable Register                | 0x01         | Read/Write | 0x00          |

| IVFM Register                  | 0x02         | Read/Write | 0xE1          |

| LED1 Flash Brightness Register | 0x03         | Read/Write | 0x7F          |

| LED1 Torch Brightness Register | 0x04         | Read/Write | 0x7F          |

| LED2 Flash Brightness Register | 0x05         | Read/Write | 0x7F          |

| LED2 Torch Brightness Register | 0x06         | Read/Write | 0x7F          |

| Flash & Torch Timing Register  | 0x0B         | Read/Write | 0x1A          |

| Flags Register                 | 0x0F         | Read       | 0x00          |

| Device ID Register             | 0x10         | Read       | 0x81          |

#### REGISTER DETAILED DESCRIPTION

#### ♦ Chip ID Register (0x00), default(0x17)

| Bit 7           | Bit 7 Bit 6 Bit 5  |  | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-----------------|--------------------|--|-------|-------|-------|-------|-------|

| Chip ID: "000   | 1 0111"            |  |       |       |       |       |       |

| Write 55H To Re | eset All Registers |  |       |       |       |       |       |

#### Enable Register (0x01), default(0x00)

| Bit 7                                                                   | Bit 6                                                    | Bit 5                                                                   | Bit 4 | Bit 3 | Bit 2 | Bit 1                                     | Bit 0                                     |

|-------------------------------------------------------------------------|----------------------------------------------------------|-------------------------------------------------------------------------|-------|-------|-------|-------------------------------------------|-------------------------------------------|

| Strobe Type<br>0=Level<br>Triggered<br>(Default)<br>1=Edge<br>Triggered | Strobe<br>Enable<br>0=Disabled<br>(Default)<br>1=Enabled | Mode Bits: M1,<br>00=Standby (De<br>01=IR Drive<br>10=Torch<br>11=Flash |       | RFU   | RFU   | UED2 Enable<br>0=OFF<br>(Default)<br>1=ON | LED1 Enable<br>0=OFF<br>(Default)<br>1=ON |

#### Note:

In Edge or Level Strobe Mode, it is recommended that the trigger pulse width be set greater than 1ms to ensure proper turn-on of the device.

#### ♦ IVFM Register (0x02), default(0xE1)

| Bit 7 | Bit 6 | Bit 5                                                                       | Bit 4                                      | Bit 3                                                                                                                  | Bit 2 | Bit 1 | Bit 0                                               |

|-------|-------|-----------------------------------------------------------------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-------|-------|-----------------------------------------------------|

| RFU   | RFU   | LED1/2 Pin<br>Short Fault<br>Detect<br>0=Disabled<br>1=Enabled<br>(Default) | UVLO Enable 0=Disabled (Default) 1=Enabled | IVFM Levels<br>000=2.9 V (I<br>001=3.0 V<br>010=3.1 V<br>011=3.2 V<br>100=3.3 V<br>101=3.4 V<br>110=3.5 V<br>111=3.6 V |       |       | IVFM Enable<br>0=Disabled<br>1=Enabled<br>(Default) |

####

| Bit 7                         | Bit 6           | Bit 5       | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------------------------------|-----------------|-------------|-------|-------|-------|-------|-------|

|                               | ightness Levels |             |       |       |       |       |       |

| I <sub>FLASH</sub> (mA)≈(Brig | htness Code*3.9 | 1mA)+3.91mA |       |       |       |       |       |

| 00000000=3.91                 | mA              |             |       |       |       |       |       |

| 01111111=500                  | mA (Default)    |             |       |       |       |       |       |

| 4444444 4 0                   | •               |             |       |       |       |       |       |

| 11111111=1.0 /                | 4               |             |       |       |       |       |       |

#### LED1 Torch Brightness Register (0x04), default(0x7F)

| Bit 7                                                                                | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|--------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|

| LED1 Torch Brightness Levels I <sub>TORCH</sub> (mA)≈(Brightness Code*1.46mA)+1.46mA |       |       |       |       |       |       |       |

| 0000000=1.46 mA<br>                                                                  |       |       |       |       |       |       |       |

| 01111111=187.<br><br>11111111=375                                                    | ,     |       |       |       |       |       |       |

#### ♦ LED2 Flash Brightness Register (0x05), default(0x7F)

| Bit 7                                                                                | Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------|-------------------------------------|--|--|--|--|--|--|

| LED2 Flash Brightness Levels I <sub>FLASH</sub> (mA)≈(Brightness Code*3.91mA)+3.91mA |                                     |  |  |  |  |  |  |

| 00000000=3.91                                                                        | mA                                  |  |  |  |  |  |  |

| 01111111=500                                                                         | mA (Default)                        |  |  |  |  |  |  |

| 11111111=1.0                                                                         | A                                   |  |  |  |  |  |  |

#### ♦ LED2 Torch Brightness Register (0x06), default(0x7F)

| Bit 7                                                             | Bit 6                                | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------------------------------------------------------------------|--------------------------------------|-------|-------|-------|-------|-------|-------|

|                                                                   | rightness Levels<br>ghtness Code*1.4 |       |       |       |       |       |       |

| 00000000=1.46 mA<br>01111111=187.5 mA (Default)<br>1111111=375 mA |                                      |       |       |       |       |       |       |

# → Flash & Torch Timing Register (0x0B) , default(0x1A)

| Bit 7         Bit 6         Bit 5         Bit 4         Bit 3         Bit 2         Bit 1         Bit 0           Torch Current Ramp time           0000=No Ramp         0001=1 ms (Default)         0000=40 ms         0000=40 ms           0011=32 ms         0011=160 ms         0010=120 ms         0011=160 ms           0100=128 ms         0100=200 ms         0100=200 ms         0101=240 ms           0110=384 ms         0110=280 ms         0110=280 ms         0111=320 ms           1000=768 ms         1000=360 ms         1001=400 ms         1001=400 ms           1011=1536 ms         1010=600 ms (Default)         1011=800 ms         1100=1000 ms           1101=2048 ms         1101=1200 ms         1101=1200 ms         1101=1200 ms           1110=2048 ms         1110=1400 ms         1110=1400 ms |                                                                                                                                                                                                                     |       |       |       |                                                                                                                                                                                                                 |           |       |       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------|-------|

| 0000=No Ramp       0000=40 ms         0001=32 ms       0001=80 ms         0011=64 ms       0010=120 ms         0010=128 ms       0011=160 ms         0100=200 ms       0100=200 ms         0101=240 ms       0101=240 ms         0111=512 ms       0110=280 ms         0100=768 ms       0101=30 ms         1001=400 ms       1001=400 ms         1011=1536 ms       1011=800 ms         1100=1792 ms       1100=1000 ms         1101=2048 ms       1101=1200 ms                                                                                                                                                                                                                                                                                                                                                               | Bit 7                                                                                                                                                                                                               | Bit 6 | Bit 5 | Bit 4 | Bit 3                                                                                                                                                                                                           | Bit 2     | Bit 1 | Bit 0 |

| 1111=2048 ms 1111=1600 ms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0000=No Ramp<br>0001=1 ms (D<br>0010=32 ms<br>0011=64 ms<br>0100=128 ms<br>0101=256 ms<br>0110=384 ms<br>0111=512 ms<br>1000=768 ms<br>1001=1024 ms<br>1011=1536 ms<br>1010=1792 ms<br>1101=2048 ms<br>1110=2048 ms | •     |       |       | 0000=40 ms<br>0001=80 ms<br>0010=120 ms<br>0011=160 ms<br>0100=200 ms<br>0101=240 ms<br>0110=280 ms<br>0111=320 ms<br>1000=360 ms<br>1001=400 ms<br>1011=800 ms<br>1100=1000 ms<br>1101=1200 ms<br>1110=1400 ms | (Default) |       |       |

# ♦ Flags Register (0x0F), default(0x00)

| Bit 7                     | Bit 6             | Bit 5 | Bit 4 | Bit 3               | Bit 2               | Bit 1                              | Bit 0      |

|---------------------------|-------------------|-------|-------|---------------------|---------------------|------------------------------------|------------|

| Flash<br>Time-Out<br>Flag | IVFM Trip<br>Flag | RFU   | RFU   | LED2 Short<br>Fault | LED1 Short<br>Fault | Thermal<br>Shutdown<br>(TSD) Fault | UVLO Fault |

# Device ID Register (0x10), default(0x81)

| Bit 7                  | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|------------------------|-------|-------|-------|-------|-------|-------|-------|

| Device ID: "1000 0001" |       |       |       |       |       |       |       |

#### **PCB LAYOUT**

#### LAYOUT GUIDELINES

The PCB layout of the high-power inductorless dual channel LED driver AW36423 is important. The following steps should be used as a reference to ensure the device is stable and maintains proper LED current regulation across its intended operating voltage and current range.

- 1. Place CIN on the top layer (same layer as the AW36423) and as close to the device as possible. The input capacitor conducts the driver currents during LED1 and LED2 turn on and can detect current spikes over 2.0A in amplitude. Connecting the input capacitor through short, wide traces to both the IN and GND pins reduces the inductive voltage spikes that occur during switching which can corrupt the VIN line.

- 2. For LED1 and LED2, terminate the Flash LED cathodes directly to the GND pin of the AW36423. If possible, route the LED returns with a dedicated path so as to keep the high amplitude LED currents out of the GND plane. For Flash LEDs that are routed relatively far away from the AW36423, a good approach is to sandwich the forward and return current paths over the top of each other on two layers. This helps reduce the inductance of the LED current paths.

- 3. To optimize the VIN operation range, the IN and GND wire should as short and wide as possible to reduce the series resistor. Meanwhile, To optimize the heat dissipation performance, the GND pins should be connected to the PCB ground plane using as many vias as possible.

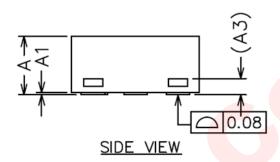

# **PACKAGE DESCRIPTION**

# COMMON DIMENSIONS (UNITS OF MEASURE=MILLIMETER)

| SYMBOL | MIN NOM MAX        |         |  |  |  |  |

|--------|--------------------|---------|--|--|--|--|

| Α      | 0.50               | 0.60    |  |  |  |  |

| A1     | 0.00               | 0.05    |  |  |  |  |

| A3     |                    | 0.15REF |  |  |  |  |

| b      | 0.17 0.22 0.27     |         |  |  |  |  |

| D      | 1.10   1.20   1.30 |         |  |  |  |  |

| Ε      | 1.50 1.60 1.70     |         |  |  |  |  |

| е      | 0.40REF            |         |  |  |  |  |

| e1     | 1.20REF            |         |  |  |  |  |

| e2     | 0.80REF            |         |  |  |  |  |

| Н      | 0.27REF            |         |  |  |  |  |

| L1     | 0.09REF            |         |  |  |  |  |

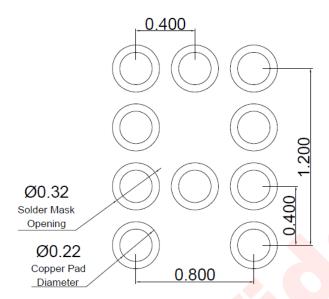

# **LAND PATTERN**

Dimensions are all in millimeters

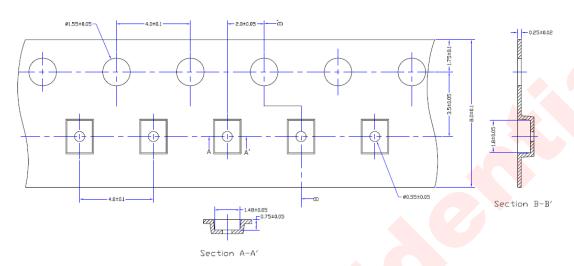

# TAPE AND REEL INFORMATION

# **Carrier Tape**

#### NOTES:

- NOTES:

1.10 procket hole pitch cumulative tolerance ±0.2

2.The meander of the tape is assumed with 1mm or less every 100mm between 250mm

3.MATERIAL:CONDUCTIVE POYSTYRENE

4.ALL DIMS IN MM

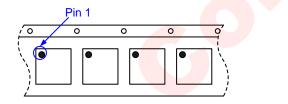

#### Pin 1 direction

User Direction of Feed

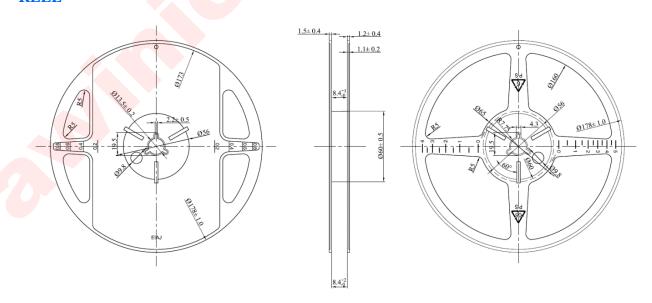

#### REEL

Unit: mm

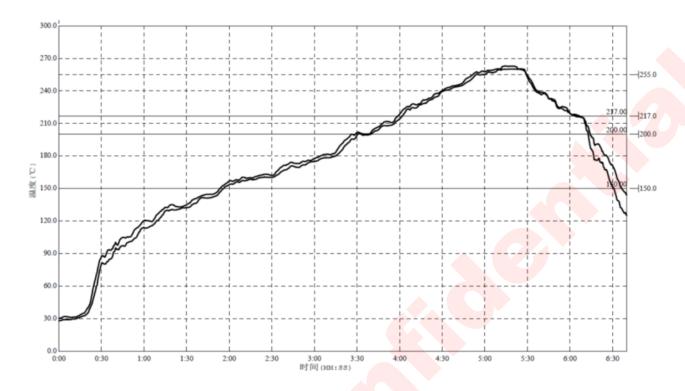

# **REFLOW PROFILE**

| Reflow Note                                 | Spec          |  |  |

|---------------------------------------------|---------------|--|--|

| Average ramp-up rate (217°C to peak)        | Max. 3°C /sec |  |  |

| Time of Preheat temp. (from 150°C to 200°C) | 60-120sec     |  |  |

| Time to be maintained above 217°C           | 60-150sec     |  |  |

| Peak Temperature                            | >260°C        |  |  |

| Time within 5°C of actual peak temp         | 20-40sec      |  |  |

| Ramp-d <mark>ow</mark> n rate               | Max. 6°C /sec |  |  |

| Time from 25°C to peak temp                 | Max. 8min     |  |  |

# **REVISION HISTORY**

| Version | Date     | Change Record                                                  |  |

|---------|----------|----------------------------------------------------------------|--|

| V1.0    | Oct 2017 | Product Datasheet V1.0 Released                                |  |

| V1.1    | Apr 2018 | Product Datasheet V1.1 Releasedadd V <sub>HR</sub> (max) value |  |

| V1.2    | Aug 2018 | Correction Device ID Register (0x10): Device ID=10000001(0x81) |  |

| V1.3    | Sep 2018 | Correction NC pin definition Correction Package: FCQFN-10L     |  |

#### **DISCLAIMER**

Information in this document is believed to be accurate and reliable. However, Shanghai AWINIC Technology Co., Ltd (AWINIC Technology) does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.

AWINIC Technology reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. Customers shall obtain the latest relevant information before placing orders and shall verify that such information is current and complete. This document supersedes and replaces all information supplied prior to the publication hereof.

AWINIC Technology products are not designed, authorized or warranted to be suitable for use in medical, military, aircraft, space or life support equipment, nor in applications where failure or malfunction of an AWINIC Technology product can reasonably be expected to result in personal injury, death or severe property or environmental damage. AWINIC Technology accepts no liability for inclusion and/or use of AWINIC Technology products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

Applications that are described herein for any of these products are for illustrative purposes only. AWINIC Technology makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

All products are sold subject to the general terms and conditions of commercial sale supplied at the time of order acknowledgement.

Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

Reproduction of AWINIC information in AWINIC data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. AWINIC is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of AWINIC components or services with statements different from or beyond the parameters stated by AWINIC for that component or service voids all express and any implied warranties for the associated AWINIC component or service and is an unfair and deceptive business practice. AWINIC is not responsible or liable for any such statements.