# White LED Driver with PWM Brightness Control in Small Package

# **FEATURES**

- 1% PWM dimming current accuracy ±20%

- Support 0.3% PWM dimming(VFB.TYP=0.6mV)

- PWM control input for CABC operation

- 1.1MHz Switching Frequency

- 38V Over-voltage Protection for up to 10 LEDs in Series

- Innovative CDC Output Drive Technology, Significantly Improve EMI Performance

- 200mV Reference Voltage

- 2.7V to 5.5V Input Voltage Range

- Over-current and Over-temperature Protection

- Built-in Soft-start Limits Inrush Current

- Ultra Small 2mm\*2mm TDFN-6L package

### **APPLICATIONS**

- Mobile Phones

- Portable Media Players

- PDAs

- GPS Receivers

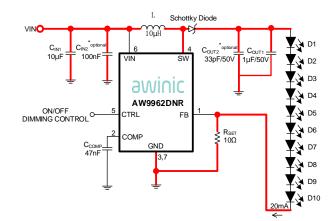

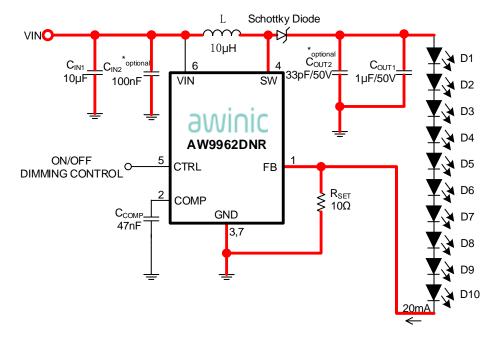

# **TYPICAL APPLICATION CIRCUIT**

Figure 1 Typical Application Circuit of AW9962

All trademarks are the property of their respective owners

1

### **GENERAL DESCRIPTION**

The AW9962 is a white LED driver with integrated boost converter. With an internal 40V switch FET, the AW9962 drives up a string of up to 10 LEDs in series. The boost converter runs at 1.1MHz fixed switching frequency to reduce output ripple, improve conversion efficiency, and allows for the use of small external components.

The default white LED current is set with the external sense resistor  $R_{SET}$ , and the feedback voltage is regulated to 200mV, as shown in the typical application. During the operation, a pulse width modulation (PWM) signal can be applied to the CTRL pin through which the duty cycle determines the feedback reference voltage.

AW9962 integrates built-in soft-start function to minimize the power supply inrush current. AW9962 also integrates over-current protection , LED open protection and over temperature protection(OTP) to prevent chip from entering abnormal operating conditions.

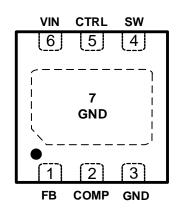

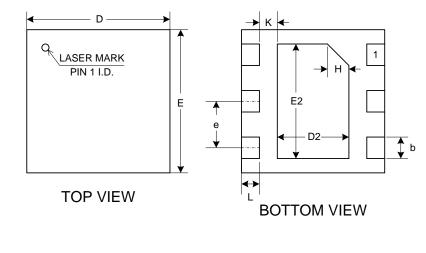

### **PIN CONFIGURATION AND TOP MARK**

AW9962DNR TOP VIEW

AW9962DNR MARKING

AL62—AW9962DNR XXXX—Manufacture Data Code

### **PIN DEFINITION**

| No. | NAME | DESCRIPTION                                                                                                                                                       |

|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | FB   | Feedback pin for current. Connect the sense resistor from FB to GND.                                                                                              |

| 2   | COMP | Output of the transconductance error amplifier. Connect an external capacitor to this pin to compensate the regulator.                                            |

| 3   | GND  | Ground.                                                                                                                                                           |

| 4   | SW   | This is the switching node of the IC. Connect the inductor between the VIN and SW pin. This pin is also used to sense the output voltage for open LED protection. |

| 5   | CTRL | Control pin of the boost regulator. It is a pin which can be used for PWM digital dimming.                                                                        |

| 6   | VIN  | The input supply pin for the IC. Connect VIN to a supply voltage between 2.7V and 5.5V.                                                                           |

| 7   | GND  | Exposed pad should be soldered to PCB board and Connected to GND.                                                                                                 |

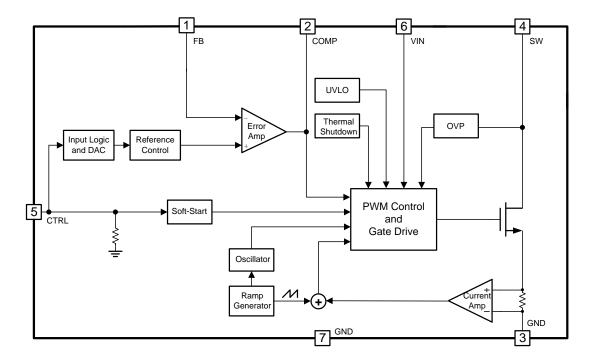

# FUNCTIONAL BLOCK DIAGRAM

Figure 3 FUNCTIONAL BLOCK DIAGRAM

# **TYPICAL APPLICATION CIRCUITS**

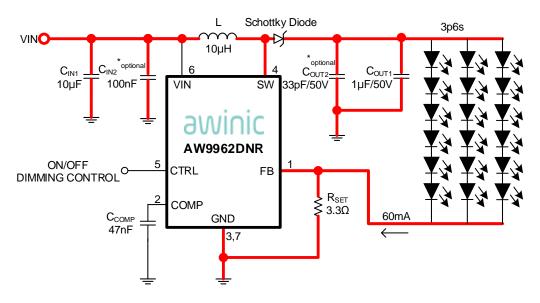

Figure 4 Typical Application of AW9962

Figure 5 Drive 18 White LEDs for Large Screen Display

Notice for Typical Application Circuits:

1: Recommended device for AW9962:

L: LQH3NPN100NM0

C<sub>IN1</sub>: Murata GRM188R61C106MA73

CIN2: Murata GRM155R61C104K

COUT1: Murata GRM21BR71H105KA

COUT2: Murata GRM1555C1H330GA

Schottky Diode: ONsemi MBR0540

2:  $C_{IN2}$  and  $C_{OUT2}$  are recommended to use in parallel with the input capacitor and output capacitor to suppress high frequency noise.

3: Red lines are high current paths, reference to the section APPLICATION INFORMATION.

4: The capacitors (C<sub>IN1</sub>, C<sub>IN2</sub>, C<sub>OUT1</sub>, C<sub>OUT2</sub> and C<sub>COMP</sub>) should be placed as close to the pins of the IC as possible.

5: Minimize trace lengths between the IC and the inductor, the Schottky diode and the output capacitor, keep these traces short, direct, and wide.

6: Minimize the length and area of all traces connected to the SW pin and always use a ground plane under the switching regulator to minimize inter-plane coupling.

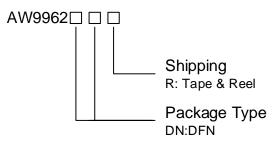

# ORDERING INFORMATION

| Part Number | Temperature | Package    | Marking | Moisture<br>Sensitivity<br>Level | Environmental<br>Information | Delivery<br>Form                |

|-------------|-------------|------------|---------|----------------------------------|------------------------------|---------------------------------|

| AW9962DNR   | -40°C∼85°C  | TDFN2x2-6L | AL62    | MSL1                             | ROHS+HF                      | 3000 units/<br>Tape and<br>Reel |

Figure 6 Package Information

# ABSOLUTE MAXIMUM RATINGS(NOTE1)

| PARAMETERS                                           | RANGE          |  |  |  |  |

|------------------------------------------------------|----------------|--|--|--|--|

| Supply voltage range VIN <sup>(NOTE 2)</sup>         | -0.3V to 6V    |  |  |  |  |

| Voltage on FB,CTRL and COMP <sup>(NOTE 2)</sup>      | -0.3V to 6V    |  |  |  |  |

| Voltage on SW <sup>(NOTE 2)</sup>                    | -0.3V to 40V   |  |  |  |  |

| Junction-to-ambient thermal resistance $\theta_{JA}$ | 120°C /W       |  |  |  |  |

| Operating free-air temperature range                 | -40°C to 85°C  |  |  |  |  |

| Operating Junction temperature TJ                    | 40°C to 150°C  |  |  |  |  |

| Storage temperature T <sub>STG</sub>                 | -65°C to 150°C |  |  |  |  |

| Lead Temperature (Soldering 10 Seconds)              | 260°C          |  |  |  |  |

| ESD <sup>(NOTE 3)</sup>                              |                |  |  |  |  |

| ALL PINS HBM (human body model) (NOTE 4)             | ±6000V         |  |  |  |  |

| ALL PINS CDM (charge device model) (NOTE 5)          | ±2000V         |  |  |  |  |

| ALL PINS MM (machine model) (NOTE 6)                 | ±300V          |  |  |  |  |

| Latch-up <sup>(NOTE 7)</sup>                         |                |  |  |  |  |

| Latab up ourrant maximum rating par JEDEC standard   | +IT: 400mA     |  |  |  |  |

| Latch-up current maximum rating per JEDEC standard   | -IT: -400mA    |  |  |  |  |

NOTE1: Conditions out of those ranges listed in "absolute maximum ratings" may cause permanent damages to the device. In spite of the limits above, functional operation conditions of the device should within the ranges listed in "recommended operating conditions". Exposure to absolute-maximum-rated conditions for prolonged periods may affect device reliability.

NOTE2: All voltage values are with respect to network ground terminal.

NOTE3: This integrated circuit can be damaged by ESD if you don't pay attention to ESD protection. AWINIC recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

NOTE4: The human body model is a 100pF capacitor discharged through a  $1.5k\Omega$  resistor into each pin. Test method: MIL-STD-883H Method 3015.8.

NOTE5: Test Condition: JEDEC EIA/JESD22-C101E.

NOTE6: Test Condition: JEDEC EIA/JESD22-A115.

NOTE7: Test Condition: JEDEC STANDARD NO.78D NOVEMBER 2011.

# **ELECTRICAL CHARACTERISTICS**

| Test Condition: $T_A = 25^{\circ}C$ , VIN = 3.6V | , $V_{CTRL} = VIN$ (Unless otherwise specified). |

|--------------------------------------------------|--------------------------------------------------|

|--------------------------------------------------|--------------------------------------------------|

|                     | PARAMETER                                 | TEST CONDITION                       | MIN | TYP  | MAX  | UNIT |

|---------------------|-------------------------------------------|--------------------------------------|-----|------|------|------|

| SUPPLY              | VOLTAGE AND CURRENT                       |                                      |     |      |      |      |

| VIN                 | Input voltage range                       |                                      | 2.7 |      | 5.5  | V    |

| Vuvlo               | Under-voltage lockout threshold           | VIN falling                          |     | 2.2  | 2.39 | V    |

| V <sub>HYS</sub>    | Under-voltage lockout<br>hysteresis       |                                      |     | 100  |      | mV   |

| Isd                 | Shutdown current                          | V <sub>CTRL</sub> = GND,<br>VIN=4.2V |     | 0.1  | 1    | μA   |

| la                  | Operating quiescent current               | VFB = 1V                             |     | 0.6  | 0.9  | mA   |

| PWM DIM             | MING CONTROL                              |                                      |     |      |      |      |

| fрwм                | Frequency of PWM dimming                  |                                      | 10  |      | 100  | kHz  |

| D <sub>PWM</sub>    | PWM dimming duty cycle                    |                                      | 0.3 |      | 100  | %    |

| t <sub>MIN_ON</sub> | Minimum on pulse width                    |                                      |     | 50   |      | ns   |

| VOLTAGE             | AND CURRENT CONTROL                       |                                      |     |      | ı    |      |

| V <sub>REF</sub>    | Voltage feedback regulation voltage       |                                      | 195 | 200  | 205  | mV   |

|                     | Voltage feedback regulation               | PWM duty cycle = 1%                  | 1.6 | 2    | 2.4  | mV   |

| Vref_pwm            | voltage under brightness<br>control       | PWM duty cycle = 0.3%                | 0.3 | 0.6  | 1.4  | mV   |

| IFB                 | Voltage feedback input bias current       |                                      |     | 0.1  | 1    | μA   |

| BOOST C             | ONVERTER                                  |                                      |     |      |      |      |

|                     | N-channel MOSFET                          | VIN = 3.6V                           |     | 0.36 | 0.65 | Ω    |

| RDS(on)             | on-resistance                             | VIN = 3.0V                           |     |      | 0.7  | Ω    |

| I <sub>L_NFET</sub> | N-channel leakage current                 | Vsw = 35V, T <sub>A</sub> = 25°C     |     |      | 1    | μA   |

| fs                  | Oscillator frequency                      |                                      | 950 | 1100 | 1250 | kHz  |

| D <sub>MAX</sub>    | Maximum duty cycle                        |                                      | 90  | 95   |      | %    |

| OCP AND             | OVP                                       |                                      |     |      | 1    |      |

| ILIM                | N-channel MOSFET current<br>limit         |                                      | 1.5 | 2    | 2.5  | А    |

| Vovp                | Open LED overvoltage protection threshold | Measured on the SW pin               | 36  | 38   | 40   | V    |

| t <sub>REF</sub>    | VREF filter time constant                 |                                      |     | 480  |      | μS   |

| CTRL INT            | ERFACE                                    | 1                                    |     | I    | I    | L    |

| V <sub>CTRL_H</sub> | CTRL logic high voltage                   | VIN = 2.7V to 5.5V                   | 1.4 |      |      | V    |

| V <sub>CTRL_L</sub> | CTRL logic low voltage                    | VIN = 2.7V to 5.5V                   |     |      | 0.4  | V    |

| RCTRL               | CTRL pull down resistor                   |                                      | 300 | 600  | 700  | kΩ   |

www.awinic.com.cn

| Jun | 2018 | V1.3 |

|-----|------|------|

|     |      |      |

| PARAMETER                         |                                       | TEST CONDITION   | MIN | ТҮР | MAX | UNIT |  |

|-----------------------------------|---------------------------------------|------------------|-----|-----|-----|------|--|

| toFF CTRL pulse width to shutdown |                                       | CTRL high to low | 2.5 |     |     | ms   |  |

| THERMAL                           | THERMAL SHUTDOWN                      |                  |     |     |     |      |  |

| Тотр                              | Thermal shutdown threshold            |                  |     | 165 |     | °C   |  |

| T <sub>HYS</sub>                  | Thermal shutdown threshold hysteresis |                  |     | 15  |     | °C   |  |

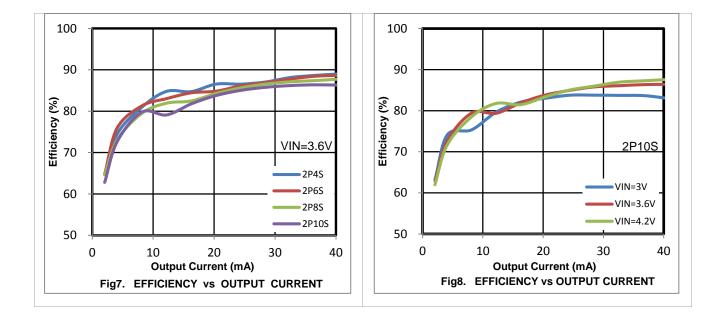

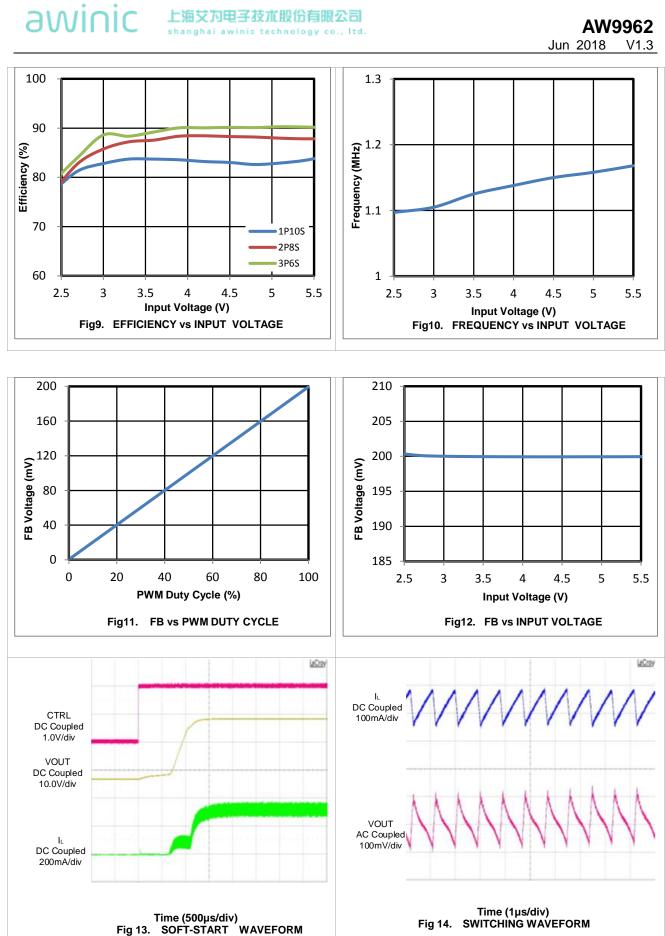

# **TYPICAL CHARACTERISTICS**

#### Table 1 TABLE OF FIGURES

| IND                              | FIGURE No.                                     |           |

|----------------------------------|------------------------------------------------|-----------|

| Efficiency 1                     | VIN=3.6V, 4,6,8,10 LEDs,<br>L=10μH             | FIGURE 7  |

| Efficiency 2                     | VIN=4.2/3.6/3.0V, 10 LEDs,<br>L=10μH           | FIGURE 8  |

| Efficiency 3                     | VIN=2.5~5.5V, 1P10S,<br>2P8S,3P6S LEDs, L=10μH | FIGURE 9  |

| Switching frequency              | VIN=2.5~5.5V, 10 LEDs,<br>L=10μH               | FIGURE 10 |

| PWM dimming linearity            | PWM Freq = 20 kHz                              | FIGURE 11 |

| Feedback voltage line regulation | VIN=2.5~5.5V                                   | FIGURE 12 |

| Soft-start waveform              | VIN=3.6V, 10 LEDs, L=10μΗ                      | FIGURE 13 |

| Switching waveform               | VIN=3.6V, 10 LEDs, L=10μΗ                      | FIGURE 14 |

| Open LED protection              | VIN=3.6V, 10 LEDs, L=10μΗ                      | FIGURE 15 |

# DETAILED FUNCTIONAL DESCRIPTION

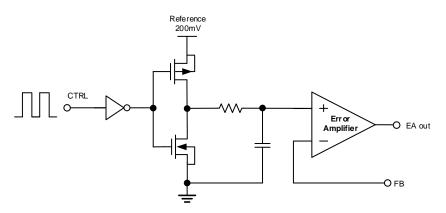

The AW9962 is a high efficiency, high output voltage boost converter in small package size. The device is ideal for driving up to 10 white LED in series. The serial LED connection provides even illumination by sourcing the same output current through all LEDs. The device integrates 40V/2.0A switch FET and operates in pulse width modulation (PWM) with 1.1MHz fixed switching frequency. The duty cycle of the converter is set by the error amplifier output and the current signal applied to the PWM control comparator. The control architecture is based on traditional current-mode control. Therefore, slope compensation is added to the current signal to allow stable operation for duty cycle larger than 50%. The feedback loop regulates the FB pin to a low reference voltage (200mV typical), reducing the power dissipation in the current sense resistor.

#### SOFT START-UP

Soft-start circuitry is integrated into the IC to avoid a high inrush current during start-up. After the device is enabled, the voltage at FB pin ramps up to the reference voltage. This ensures that the output voltage rises slowly to reduce the input current.

#### **OPEN LED OVER-VOLTAGE PROTECTION**

Open LED over-voltage protection circuitry prevents IC damage as the result of white LED disconnection. The AW9962 monitors the voltage at the SW pin during each switching cycle. The circuitry turns off the switch FET as soon as the SW voltage exceeds the V<sub>OVP</sub> threshold for 8 clock cycles.

#### SHUTDOWN

The CTRL input is used to enable or disable the AW9962. Pulling the CTRL pin higher than 1.4V will enable the device. The AW9962 has an internal shutdown delay circuitry, when the CTRL pin is held low for an amount of time longer than 2.5ms, the AW9962 will enter shutdown mode and the input supply current for the device is less than 1µA. Although the internal FET does not switch in shutdown, there is still a DC current path between the input and the LEDs through the inductor and Schottky diode. The minimum forward voltage of the LED array must exceed the maximum input voltage to ensure that the LEDs remain off in shutdown. However, in the typical application with two or more LEDs, the forward voltage is large enough to reverse bias the Schottky and keep leakage current low.

#### UNDER-VOLTAGE LOCKOUT

An under-voltage lockout prevents operation of the device at input voltage below typical 2.2V. When the input voltage is below the under-voltage threshold, the internal switch FET is turned off. If the input voltage rises by under-voltage lockout hysteresis, the IC restarts.

#### CURRENT PROGRAM

The FB voltage is regulated by a low 200mV reference voltage. The LED current is programmed externally using a current sense resistor in series with the LED string. The value of the R<sub>SET</sub> can be calculated by the following equation:

$$I_{LED} = \frac{V_{FB}}{R_{SET}} \qquad (1)$$

Where:

$I_{LED}$  = output current of LEDs

$V_{FB}$  = regulated voltage of FB

R<sub>SET</sub> = current sense resistor

#### **PWM BRIGHTNESS DIMMING**

When the CTRL pin is constantly high, the FB voltage is regulated to 200mV typically. However, the CTRL pin allows a PWM signal to reduce this regulation voltage, it achieves LED brightness dimming. The relationship between the duty cycle and the FB voltage is given by the following equation:

$V_{FB} = Duty \times 200 mV$  (2)

Where:

Duty = duty cycle of the PWM signal

200mV = internal reference voltage

As shown in the <u>FIGURE 16</u>, the IC chops up the internal 200mV reference voltage at the duty cycle of the PWM signal. The pulse signal is then filtered by an internal low pass filter. The output of the filter is connected to the error amplifier as the reference voltage for the FB pin regulation. Therefore, although a PWM signal is used for brightness dimming, only the WLED DC current is modulated, which is often referred as analog dimming. This eliminates the audible noise which often occurs when the LED current is pulsed in replica of the frequency and duty cycle of PWM control. Unlike other scheme which filters the PWM signal for analog dimming, AW9962 regulation voltage is independent of the PWM logic voltage level which often has large variations.

Figure16 Block Diagram of Programmable FB Voltage Using PWM Signal

#### THERMAL SHUTDOWN

An internal thermal shutdown turns off the device when the typical junction temperature of is exceeded 165°C. The device is released from shutdown automatically when the junction temperature decreases by 15°C.

# **APPLICATION INFORMATION**

#### MAXIMUM OUTPUT CURRENT

The over-current limit in a boost converter limits the maximum input current and thus maximum input power for a given input voltage. Maximum output power is less than maximum input power due to power conversion losses. The current limit setting, input voltage, output voltage and efficiency can all change maximum current output. Therefore, the ripple has to be subtracted to derive maximum DC current. The ripple current is a function of switching frequency, inductor value and duty cycle. The following equations take into account of all the above factors for maximum output current calculation.

$$I_{P} = \frac{1}{L \times F_{s} \times (\frac{1}{V_{OUT} + V_{F} - V_{IN}} + \frac{1}{V_{IN}})}$$

(3)

Where:

$I_P$  = inductor peak to peak ripple

L= inductor value

VF = Schottky diode forward voltage

Fs = switching frequency

$V_{\text{OUT}}$  = output voltage of the boost converter. It is equal to the sum of  $V_{\text{FB}}$  and the voltage drop across LEDs.

$$I_{out\_max} = \frac{V_{IN} \times (I_{lim} - I_P / 2) \times \eta}{V_{OUT}}$$

(4)

Where:

Iout\_max = maximum output current of the boost converter

I<sub>lim</sub> = over-current limit, for worst case calculation the minimum value has to be chosen.

$\eta = efficiency$

#### INDUCTOR SELECTION

The selection of the inductor affects steady state operation as well as transient behavior and loop stability. These factors make it the most important component in power regulator design. There are three important inductor specifications, inductor value, DC resistance and saturation current. Considering inductor value alone is not enough.

The inductor value determines the inductor ripple current. Choose an inductor that can handle the necessary peak current without saturating. The inductor DC current is given by:

$$I_{\text{IN}_{\text{DC}}} = \frac{V_{\text{OUT}} \times I_{\text{out}}}{V_{\text{IN}} \times \eta}$$

(5)

Inductor values can have  $\pm 20\%$  tolerance with no current bias. When the inductor current approaches saturation level, its inductance can decrease 20% to 35% from the 0A value depending on how the inductor vendor defines saturation current. Using an inductor with a smaller inductance value forces discontinuous PWM when the inductor current ramps down to zero before the end of each switching cycle. This reduces the boost converter's maximum output current, causes large input voltage ripple and reduces efficiency. Large inductance value provides much more output current and higher conversion efficiency. For these reasons, a 4.7 $\mu$ H to 10 $\mu$ H inductor value range is recommended. A 10 $\mu$ H inductor optimized the efficiency for most

application while maintaining low inductor peak to peak ripple. <u>TABLE 2</u> lists the recommended inductor for the AW9962. When recommending inductor value, the factory has considered –40% and +20% tolerance from its nominal value.

| Part<br>Number | L<br>(µH) | DCR Max<br>(Ω) | Saturation Current<br>(mA) | Size<br>(L x W x H mm) | Vendor    |

|----------------|-----------|----------------|----------------------------|------------------------|-----------|

| LQH3NPN100NM0  | 10        | 0.3            | 750                        | 3 x 3 x 1.5            | Murata    |

| A997AS-220M    | 22        | 0.4            | 510                        | 4 x 4 x 1.8            | ТОКО      |

| CDH3809/SLD    | 10        | 0.3            | 570                        | 4 x 4 x 1.0            | Sumida    |

| LPS4018-472ML  | 4.7       | 0.125          | 1900                       | 4 x 4 x 1.8            | Coilcraft |

Table 2 Recommended Inductors for AW9962

#### SCHOTTKY DIODE SELECTION

The high switching frequency of the AW9962 demands a high-speed rectification for optimum efficiency. Ensure that the diode average and peak current rating exceeds the average output current and peak inductor current. In addition, the diode's reverse breakdown voltage must exceed the open LED over-voltage protection voltage. The ONSemi MBR0540 and the ZETEX ZHCS400 are recommended for AW9962.

### COMPENSATION CAPACITOR SELECTION

The compensation capacitor  $C_{COMP}$  (see the application circuit), connected from COMP pin to GND, is used to stabilize the feedback loop of the AW9962. Use 47nF X5R or X7R ceramic capacitor for  $C_{COMP}$ .

For most applications, ceramic capacitors with X7R or X5R temperature characteristic are preferred for use with the AW9962.

Capacitors with Y5V or Z5U temperature characteristic are generally not recommended for use with the AW9962.

### INPUT AND OUTPUT CAPACITOR SELECTION

The output capacitor is mainly selected to meet the requirements for the output ripple and loop stability. This ripple voltage is related to the capacitor's capacitance and its equivalent series resistance (ESR). Assuming a capacitor with zero ESR, the minimum capacitance needed for a given ripple can be calculated by:

$$C_{OUT} = \frac{(V_{OUT} - V_{IN}) \times I_{out}}{V_{OUT} \times F_{S} \times V_{ripple}}$$

(6)

Where,  $V_{ripple}$  = peak-to-peak output ripple. The additional output ripple component caused by ESR is calculated using:

$$V_{\text{ripple}_{\text{ESR}}} = I_{\text{out}} \times R_{\text{ESR}}$$

(7)

Due to its low ESR, V<sub>ripple\_ESR</sub> can be neglected for ceramic capacitors, but must be considered if tantalum or electrolytic capacitors are used.

Care must be taken when evaluating a ceramic capacitor's derating under dc bias, aging and AC signal. For example, larger form factor capacitors (in 1206 size) have a resonant frequency in the range of the switching frequency. So the effective capacitance is significantly lower. The DC bias can also significantly reduce capacitance. Ceramic capacitors can loss as much as 50% of its capacitance at its rated voltage. Therefore, leave the margin on the voltage rating to ensure adequate capacitance at the required output voltage.

An X5R or X7R capacitor of  $10\mu$ F is recommended for input side. The output requires a X5R or X7R capacitor in the range of  $0.47\mu$ F to  $4.7\mu$ F. A 100nF capacitor and a 33 pF capacitor are recommended to use in parallel with the input capacitor and the output capacitor to suppress high frequency noise.

The output capacitor affects the loop stability of the boost regulator. If the output capacitor is below the range, the boost regulator can potentially become unstable.

Note that capacitor degradation increases the ripple much. Select the capacitor with 50V rated voltage to reduce the degradation at the output voltage. If the output ripple is too large, change a capacitor with less degradation effect or with higher rated voltage could be helpful.

#### POWER DISSIPATION

The maximum IC junction temperature should be restricted to  $125^{\circ}$ C under normal operating conditions. This restriction limits the power dissipation of the AW9962. Calculate the maximum allowable dissipation,  $P_{D(max)}$ , and keep the actual dissipation less than or equal to  $P_{D(max)}$ . The maximum-power-dissipation limit is determined by using the following equation:

$$P_{D(max)} = \frac{T_{Jmax} - T_{A}}{\theta_{ia}}$$

Where,  $T_{Jmax}$  is the Maximum Junction Temperature,  $T_A$  is the maximum ambient temperature for the application.  $\theta_{ja}$  is the thermal resistance junction-to-ambient given in Power Dissipation Table.

The AW9962 comes in a thermally enhanced TDFN package. Compared with the TSOT package, the TDFN package has better heat dissipation. This package includes a thermal pad that improves the thermal capabilities of the package. The  $\theta_{ja}$  of the TDFN package greatly depends on the PCB layout and thermal pad connection. The thermal pad must be soldered directly to the analog ground on the PCB. After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit(IC).

Using thermal vias underneath the thermal pad as illustrated in the layout example.

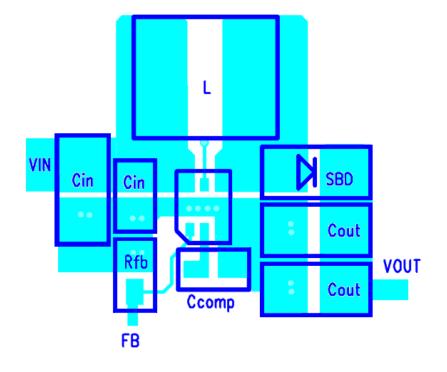

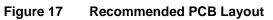

### PCB LAYOUT CONSIDERATION

As for all switching power supplies, especially those high frequency and high current ones, layout is an important design step. If layout is not carefully done, the regulator could suffer from instability as well as noise problems. To reduce switching losses, the SW pin rise and fall times are made as short as possible. To prevent radiation of high frequency resonance problems, proper layout of the high frequency switching path is essential. Minimize the length and area of all traces connected to the SW pin and always use a ground plane under the switching regulator to minimize inter-plane coupling. The loop including the PWM switch, Schottky diode, and output capacitor, contains high current rising and falling in nanosecond and should be kept as short as possible. The input capacitor needs not only to be close to the VIN pin, but also to the GND pin in order to reduce the IC supply ripple.

Connect the exposed paddle to the PCB ground plane using at least two vias. The input and the output bypass capacitors should be placed as close to the IC as possible. Minimize trace lengths between the IC and the inductor, the diode and the output capacitor; keep these traces short, direct, and wide.

A recommended PCB Layout is shown in <u>FIGURE 17</u>. In order to dissipate the package heat, the package thermal pad must be connected to a large copper area on the ground plane underneath using multiple vias.

awinic

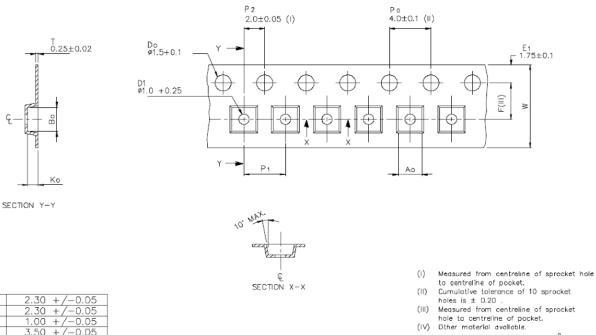

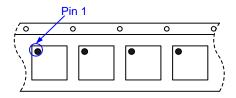

# **TAPE AND REEL INFORMATION**

### **Carrier Tape**

awinic

- - (IV)

- Typical SR of form tape Max 10<sup>9</sup> OHM/SQ (V)

ALL DIMENSIONS IN MILLIMETRES UNLESS OTHERWISE STATED

#### Ao Bo Ko .00 +/-0.05 3.50 +/-0.05 4.00 +/-0.1 8.00 +0.3/-0.1 F P1 W

#### **Pin 1 direction**

User Direction of Feed

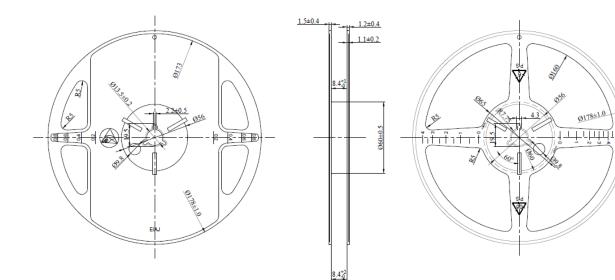

Reel

# **PACKAGE DESCRIPTION**

COMMON DIMENSIIONS (UNITS OF MEASURE=MILLIMETER

| Symbol | Min     | Тур     | Max  |

|--------|---------|---------|------|

| А      | 0.70    | 0.75    | 0.80 |

| A1     | 0.00    | 0.02    | 0.05 |

| A3     | (       | 0.20REF | -    |

| b      | 0.25    | 0.30    | 0.35 |

| D      | 1.90    | 2.00    | 2.10 |

| Е      | 1.90    | 2.00    | 2.10 |

| D2     | 0.90    | 1.00    | 1.10 |

| E2     | 1.50    | 1.60    | 1.70 |

| е      | 0.55    | 0.65    | 0.75 |

| К      | 0.15    | 0.25    | 0.35 |

| L      | 0.20    | 0.25    | 0.30 |

| Н      | 0.20REF |         |      |

NOTES: ALL DIMENSIONS REFER TO JEDEC STANDARD MO-229 DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS.

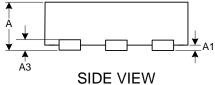

### LAND PATTERN DATA

NOTE A: All linear dimensions are in millimeters.

NOTE B: This drawing is subject to change without notice.

NOTE C: Publication IPC-7351 is recommended for alternate designs.

NOTE D: This land pattern is designed to be soldered to a thermal pad on the board.

NOTE E: Laser cutting aperture with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC-7525 for stencil design considerations.

NOTE F: Customers should contact their board fabrication site for solder mask tolerances.

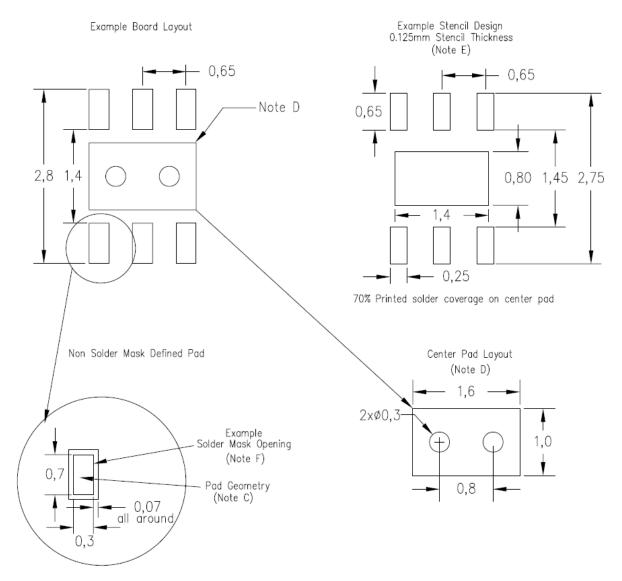

### **REFLOW**

Package Reflow Oven Thermal Profile

| Reflow Note                                | Spec          |

|--------------------------------------------|---------------|

| Average ramp-up rate (217°C to Peak)       | Max. 3°C /sec |

| Time of Preheat temp.(from 150°C to 200°C) | 60-120sec     |

| Time to be maintained above 217°C          | 60-150sec     |

| Peak Temperature                           | >260°C        |

| Time within 5°C of actual peak temp        | 20-40sec.     |

| Ramp-down rate                             | Max. 6°C /sec |

| Time from 25°C to peak temp                | Max. 8min.    |

# **REVISION HISTORY**

| Vision | Date         | Change Record                                                                                                                                                                 |

|--------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V1.0   | June 2017    | Datasheet V1.0 Released                                                                                                                                                       |

| V1.1   | January 2018 | <ol> <li>Delete the Chinese introduction of the first page</li> <li>Added MSL Level</li> <li>Added Environmental Information</li> <li>Added User Direction of Feed</li> </ol> |

| V1.2   | June 2018    | <ol> <li>Added minimum and maxim parameter in electrical characteristic diagram</li> <li>Changed Recommend PCB layout</li> </ol>                                              |

| V1.3   | June 2018    | 7. Changed VOVP max to 40V in electrical characteristic diagram                                                                                                               |

# DISCLAIMER

Information in this document is believed to be accurate and reliable. However, Shanghai AWINIC Technology Co., Ltd (AWINIC Technology) does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.

AWINIC Technology reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. Customers shall obtain the latest relevant information before placing orders and shall verify that such information is current and complete. This document supersedes and replaces all information supplied prior to the publication hereof.

AWINIC Technology products are not designed, authorized or warranted to be suitable for use in medical, military, aircraft, space or life support equipment, nor in applications where failure or malfunction of an AWINIC Technology product can reasonably be expected to result in personal injury, death or severe property or environmental damage. AWINIC Technology accepts no liability for inclusion and/or use of AWINIC Technology products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

Applications that are described herein for any of these products are for illustrative purposes only. AWINIC Technology makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

All products are sold subject to the general terms and conditions of commercial sale supplied at the time of order acknowledgement.

Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

Reproduction of AWINIC information in AWINIC data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. AWINIC is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of AWINIC components or services with statements different from or beyond the parameters stated by AWINIC for that component or service voids all express and any implied warranties for the associated AWINIC component or service and is an unfair and deceptive business practice. AWINIC is not responsible or liable for any such statements.