www DataSheet4U con

**Customer Approval:**

# SPECIFICATION FOR LCM MODULE

MODULE NO.: AX06002

DOC.REVISION:A00

SAMPLE REVISION: A(061109)

|                             | SIGNATURE |

|-----------------------------|-----------|

| PREPARED BY (LCM ENGINEER)  |           |

| CHECKED BY<br>(QA ENGINEER) |           |

| CHECKED BY                  |           |

| VERIFIED BY                 |           |

| APPROVED BY                 |           |

www.DataSheet4U.com

## DOCUMENT REVISION HISTORY

| Version        | DATE        | DESCRIPTION | CHEEKED BY |

|----------------|-------------|-------------|------------|

| Version<br>A00 | Nov-26-2006 | First issue |            |

|                |             |             |            |

|                |             |             |            |

|                |             |             |            |

|                | ,           |             |            |

|                |             |             |            |

|                |             |             |            |

|                |             |             |            |

|                |             |             |            |

|                |             |             |            |

|                |             |             |            |

|                |             |             |            |

|                |             |             |            |

|                |             |             |            |

|                |             |             |            |

|                |             |             |            |

|                |             |             |            |

|                |             |             |            |

|                |             |             |            |

|                |             |             |            |

|                |             |             |            |

|                |             |             |            |

|                |             |             |            |

|                |             |             |            |

|                |             |             |            |

|                |             |             |            |

|                |             |             |            |

|                |             |             |            |

|                |             |             |            |

|                |             |             |            |

|                |             |             |            |

vw.DataSheet4U.com

#### CONTENTS

- 1. Functions & Features

- 2. Mechanical Specifications

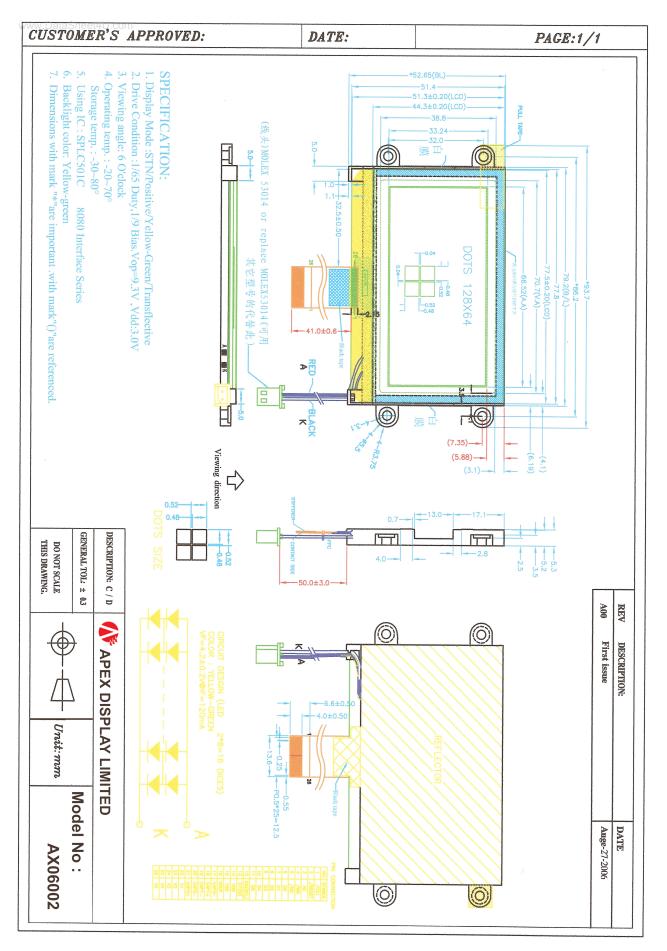

- 3. Dimensional Outline

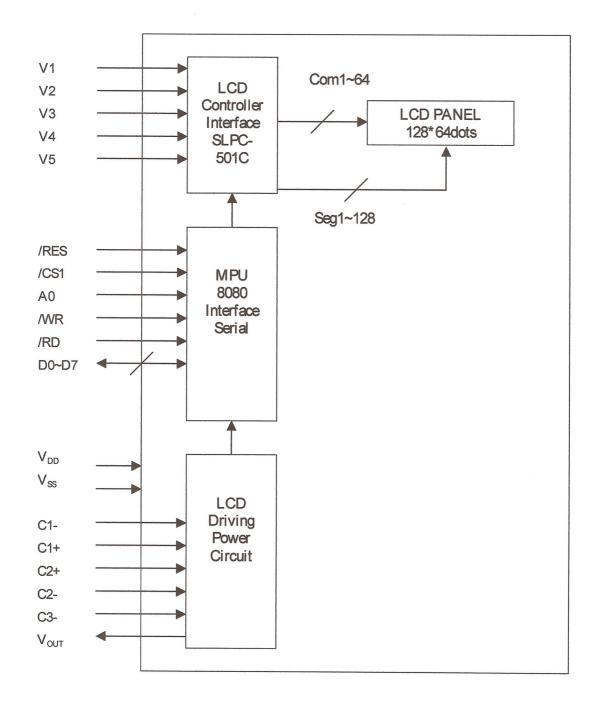

- 4. Block Diagram

- 5. Power Supply

- 6. Pin Description

- 7. Absolute Maximum Ratings

- 8. Electrical Characteristics

- 9. Quality Specifications

2

#### 1. FUNCTIONS & FEATURES

1-1. Format

: 128\*64 dots

1-2. LCD mode

: STN, Yellow-Green, Transflective mode

1-3. Viewing direction

: 6 o'clock

1-4. Driving scheme

1-5. Single Supply Voltage

1-6.8080 Interface Series

: 1/65 Duty cycle, 1/9 Bias, VIcd=9.3V : Power supply voltage range (V<sub>DD</sub>): 3V

## 2. MECHANICAL SPECIFICATIONS

2-1. Module size

: 93.70mm(L)\*52.65mm(W) NO IQF(XGIQJ ) 3&

2-2. Viewing area

: 70.70mm(L)\*38.80mm(W)

2-3. Active area

: 66.52mm(L)\*33.24mm(VV)

2-4. Dot pitch

: 0.52mm(L)\* 0.52mm(VV)

2-5. Dot size

: 0.48mm(L)\* 0.48mm(W)

2-6. Weight

: TBD

www.DataSheet4LL.com

#### 4. BLOCK DIAGRAM

5. POWER SUPPLY

# The power cumply circuits are law now

The power supply circuits are low-power consumption power supply circuits that generate the voltage levels required for the LCD drivers. They are Booster circuits, voltage regulator circuits, and voltage follower circuits. They are only enabled in master operation. The power supply circuits can turn the Booster circuits, the voltage regulator circuits, and the voltage follower circuits ON or OFF independently through the use of the Power Control Set command. Consequently, it is possible to make an external power supply and the internal power supply function somewhat in parallel. The following tables show the Power Control Set Command 3-bit data control function, and reference combinations.

The control details of each bit of the power control set command

| Bit            | Function                                                                                                                           |                | atus<br>"0" |

|----------------|------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------|

| D2<br>D1<br>D0 | Booster circuit control bit Voltage regulator circuit control bit (V/R circuit) Voltage follower circuit control bit (V/F circuit) | ON<br>ON<br>ON | OFF<br>OFF  |

#### Reference combinations

| Use Settings                                                                 | D2 D1 D0 | Voltage<br>booster | Voltage<br>regulator | Voltage<br>follower | External voltage input              | Step-up<br>voltage |

|------------------------------------------------------------------------------|----------|--------------------|----------------------|---------------------|-------------------------------------|--------------------|

| Only the internal power supply is used                                       | 1 1 1    | On                 | On                   | On                  | V <sub>SS2</sub>                    | Used               |

| Only the voltage regulator circuit and the voltage follower circuit are used | 0 1 1    | Off                | On                   | On                  | V <sub>OUT</sub> , V <sub>SS2</sub> | Open               |

| Only the V/F circuit is used                                                 | 0 0 1    | Off                | Off                  | On                  | V5, V <sub>SS2</sub>                | Open               |

| Only the external power supply is used                                       | 0 0 0    | Off                | Off                  | Off                 | V1 to V5                            | Open               |

<sup>\*</sup> The "step-up system terminals" refer CAP1+, CAP1-, CAP2+, CAP2-, and CAP3-.

<sup>\*</sup> While other combinations, not shown above, are also possible, these combinations are not recommended because they have no practical use.

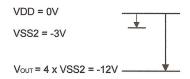

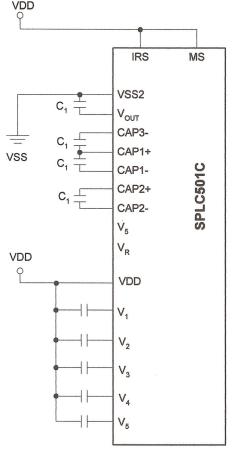

#### 5-1. Voltage Converter Circuits

Using the step-up voltage circuits equipped within the SPLC501C chips it is possible to product a 2X,3X,4X,5X or 6X step-up of the  $V_{DD}-V_{SS2}$  voltage levels.

4 x step-up voltage circuit

4 x step-up voltage relationships

$[C1 = 1.0 \text{ to } 4.7 \,\mu\text{F}, C2 = 0.1 \text{ to } 4.7 \,\mu\text{F}]$

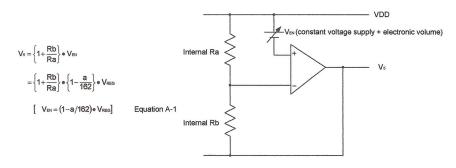

A. When the voltage regulator internal resistor is used. Example where VSS2 = VSS, with 4x step-up

### 5-2. Voltage Regulator Circuits

The step-up voltage generated at  $V_{\text{OUT}}$  outputs the LCD driver voltage V5 through the voltage regulator circuit. Because the SPLC501C chips have an internal high-accuracy fixed voltage power supply with a 64-level electronic volume function and internal resistors for the V5 voltage regulator, systems can be constructed without having to include high-accuracy voltage regulator circuit components. ( $V_{\text{REG}}$  thermal gradients approximate -0.05%/°C)

www.DataSheet4U.com

#### 6. PIN DESCRIPTION

| Pin no.      | Symbol                        | Function                                                                                                                                                                                                                                                                                                                         |

|--------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1            | /CS1                          | This is the chip select signal. When /CS1 = "L" and CS2 = "H", then the chip select becomes active, and data/command I/O is enabled.                                                                                                                                                                                             |

| 2            | /RESET                        | When /RES is set to "L," the settings are initialized. The reset operation is performed by the /RES signal level.                                                                                                                                                                                                                |

| 3            | Α0                            | This is connected to the least significant bit of the normal MPU address bus, and it determines whether the data bits are data or a command.  A0 = "H": Indicates that D0 to D7 are display data.  A0 = "L": Indicates that D0 to D7 are control data.                                                                           |

| 4            | /WR                           | When connected to an 8080 MPU, this s LOW active. This terminal connects to the MPU /WR signal. The signals on the data bus are latched at the rising edge of the /WR signal.  When connected to a 6800 Series MPU, this is the read/write control signal input terminal. When /WR = "H": Read; When /WR = "L": Write.           |

| 5            | /RD                           | When connected to an 8080 MPU, this is active LOW. This pin is connected to the /RD signal of the 8080 MPU, and the SPLC501C data bus is in an output status when this signal is "L". When connected to a 6800 Series MPU, this is active HIGH. This is the 6800 Series MPU enable clock input terminal.                         |

| 6<br>~<br>13 | D5 to D0<br>D6(SCL)<br>D7(SI) | This is an 8-bit bi-directional data bus that connects to an 8-bit or 16-bit standard MPU data bus. When the serial interface is selected (P/S = "L"): D7: serial data input (SI); D6: the serial clock input (SCL). D0 to D5 are set to high impedance. When the chip select is not active, D0 to D7 are set to high impedance. |

| 14           | $V_{DD}$                      | Shared with the MPU power supply terminal V <sub>CC</sub> .                                                                                                                                                                                                                                                                      |

| 15           | V <sub>SS</sub>               | This is a 0V terminal connected to the system GND.                                                                                                                                                                                                                                                                               |

| 16           | $V_{\text{OUT}}$              | DC/DC voltage converter. Connect a capacitor between this terminal and V <sub>ss</sub> .                                                                                                                                                                                                                                         |

| 17           | C3-                           | DC/DC voltage converter.  Connect a capacitor between this terminal and the CAP1+ terminal.                                                                                                                                                                                                                                      |

| 18           | C1+                           | DC/DC voltage converter. Connect a capacitor between this terminal and the CAP1- terminal.                                                                                                                                                                                                                                       |

| 19           | C1-                           | DC/DC voltage converter. Connect a capacitor between this terminal and the CAP1+ terminal.                                                                                                                                                                                                                                       |

| 20           | C2-                           | DC/DC voltage converter. Connect a capacitor between this terminal and the CAP2+ terminal.                                                                                                                                                                                                                                       |

| 21           | C2+                           | DC/DC voltage converter. Connect a capacitor between this terminal and the CAP2- terminal.                                                                                                                                                                                                                                       |

| JULUOTICCLIC |    |

|--------------|----|

| 22           | V1 |

| 23           | V2 |

| 24           | V3 |

| 25           | V4 |

| 26           | V5 |

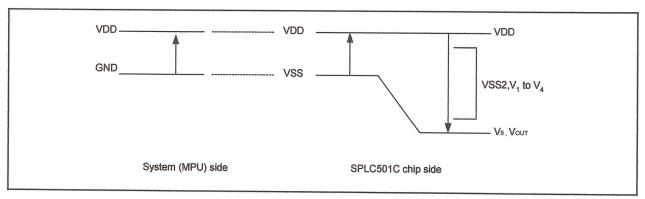

This is a multi-level power supply for the liquid crystal drive. The voltage Supply applied is determined by the liquid crystal cell, and is changed through the use of a resistive voltage divided or through changing the impedance using an op. amp. Voltage levels are determined based on  $V_{DD}$ , and must maintain the relative magnitudes:  $V_{DD}$  (= V0)  $\geq$  V1  $\geq$  V2  $\geq$  V3  $\geq$  V4  $\geq$  V5 When the power supply turns ON, the internal power supply circuits produce the V1 to V4 voltages shown below. The voltage settings are selected using the LCD bias set command.

| r.             | SPLC501C |

|----------------|----------|

| V <sub>1</sub> | 1/9 · V5 |

| V <sub>2</sub> | 2/9 · V5 |

| V <sub>3</sub> | 7/9 · V5 |

| V4             | 8/9 · V5 |

#### 7. ABSOLUTE MAXIMUM RATINGS

#### Unless otherwise noted, $V_{ss} = 0V$

| Paramete                          | a.                                              | Symbol           | Conditions        | Unit |

|-----------------------------------|-------------------------------------------------|------------------|-------------------|------|

| Power Supply \                    | Voltage                                         | $V_{DD}$         | -0.3 ~ +5.0       | V    |

| Power supply voltage              | Power supply voltage (V <sub>DD</sub> standard) |                  | -12.0 ~ +0.3      | V    |

| Power supply voltage (            | Power supply voltage (V DD standard)            |                  | V5~+0.3           | V    |

| Output volt                       | age                                             | Vo               | -0.3to VDD +0.3   | V    |

| Operating temperature             |                                                 | $T_{OPR}$        | <b>−</b> 20 ~ +70 | °C   |

| Storage temperature TCP Bare chip |                                                 | T <sub>STR</sub> | -30 ~ +80         | °C   |

Figure 25

#### Notes and Cautions

- 1. The  $V_{SS2}$ , V1 to V5 and  $V_{OUT}$  are relative to the  $V_{DD}$  = 0V reference.

- 2. Insure that the voltage levels of V1 ~ V4 are always such that  $V_{DD} \geqslant V1 \geqslant V2 \geqslant V3 \geqslant V4 \geqslant V5$ .

- 3. Permanent damage to the LSI may result if the LSI is used outside of the absolute maximum ratings. Moreover, it is recommended that in normal operation the chip be used at the electrical characteristic conditions, and use of the LSI outside of these conditions may not only result in malfunctions of the LSI, but may have a negative impact on the LSI reliability as well.

www.DataSheet4U.com

## 8. ELECTRICAL CHARACTERISTICS

#### 8-1. DC Characteristics

(Unless otherwise specified, VSS = 0V, VDD = 3.0V±10%, T<sub>A</sub> = 25°C)

| _              | 0-1. DO OTTAL ACTO 15t1C5 (Unless otherw |                                 |                                 |                                       | Inless otherwis   | se specified,        | VSS = ( | 0V, VDD = 3          | .0V±10% | $T_A = 25^{\circ}C$                     |

|----------------|------------------------------------------|---------------------------------|---------------------------------|---------------------------------------|-------------------|----------------------|---------|----------------------|---------|-----------------------------------------|

|                |                                          | Item                            | Symbol                          | Conditi                               | Condition         |                      | Rating  |                      | 11-14-  | Applicable                              |

|                |                                          |                                 | Syllibol                        | Condition                             | Condition         |                      | Тур.    | Max.                 | Units   | PIN                                     |

| Ор             | erating                                  | Possible Operating              |                                 |                                       |                   |                      | -       | 3.0                  | V       | VDD*1                                   |

| Vo             | ltage (1)                                | Voltage (1A)                    | VDD                             |                                       |                   |                      |         |                      |         |                                         |

|                |                                          | Possible Operating              | VDD                             |                                       |                   | 3.0                  | -       | 5.5                  | V       | VDD*1                                   |

|                |                                          | Voltage (1B)                    |                                 |                                       |                   |                      |         |                      |         |                                         |

| Ор             | erating                                  | Recommended                     | VSS2                            | (Relative to VDD)                     |                   | -3.3                 | -       | -2.7                 | V       | VSS2                                    |

| Vol            | ltage (2)                                | Voltage                         |                                 |                                       |                   |                      |         |                      |         |                                         |

|                |                                          | Possible Operating              | VSS2                            | (Relative to VDD)                     |                   | -6.0                 | -       | -1.8                 | V       | VSS2                                    |

|                |                                          | Voltage                         |                                 |                                       |                   |                      |         |                      |         |                                         |

| Ор             | erating                                  | Possible Operating              | V <sub>5</sub>                  | (Relative to VDD)                     |                   | -10                  | -       | -4.5                 | V       | V <sub>5</sub> *2                       |

| Vol            | tage (3)                                 | Voltage (3A)                    | -                               |                                       |                   |                      |         |                      |         |                                         |

|                |                                          | Possible Operating              |                                 |                                       |                   | -12                  | -       | -4.5                 | V       | V <sub>5</sub> *2                       |

|                |                                          | Voltage (3B)                    | -                               |                                       |                   |                      |         |                      |         |                                         |

|                |                                          | Possible Operating              | V <sub>1</sub> , V <sub>2</sub> | (Relative to VDD)                     |                   | 0.4 x V <sub>5</sub> | -       | VDD                  | V       | V <sub>1</sub> , V <sub>2</sub>         |

|                |                                          | Voltage                         |                                 |                                       |                   | V <sub>5</sub>       |         |                      |         |                                         |

|                |                                          | Possible Operating              | V <sub>3</sub> , V <sub>4</sub> | (Relative to VDD)                     | (Relative to VDD) |                      | -       | 0.6 x V <sub>5</sub> | V       | V <sub>3</sub> , V <sub>4</sub>         |

|                |                                          | Voltage                         |                                 |                                       |                   |                      |         |                      |         |                                         |

| 1              |                                          | put Voltage                     | V <sub>IHC</sub>                |                                       |                   | 0.8 x VDD            | -       | VDD                  | V       | *3                                      |

|                |                                          | put Voltage                     | V <sub>ILC</sub>                |                                       |                   | VSS                  | -       | 0.2 x VDD            | V       | *3                                      |

|                |                                          | put Voltage                     | V <sub>OHC</sub>                | I <sub>OH</sub> = -0.5mA              |                   | 0.8 x VDD            | -       | VDD                  | V       | *4                                      |

|                |                                          | out Voltage                     | V <sub>OLC</sub>                | I <sub>OL</sub> = 0.5mA               |                   | VSS                  |         | 0.2 x VDD            | V       | *4                                      |

|                | _                                        | e current                       | ILI                             | V <sub>IN</sub> = VDD or VSS          |                   | -1.0                 | -       | 1.0                  | μΑ      | *5                                      |

|                |                                          | ige current                     | Lo                              |                                       |                   | -3.0                 |         | 3.0                  | μΑ      | *6                                      |

|                |                                          | al Driver ON                    | Ron                             | T <sub>A</sub> = 25°C                 | $V_5 = -12V$      | -                    | 2.0     | 3.5                  | ΚΩ      | SEGn                                    |

|                | sistance                                 |                                 |                                 | (Relative To VDD)                     | $V_5 = -8.0V$     | -                    | 3.2     | 5.4                  | ΚΩ      | COMn*7                                  |

|                |                                          | mption Current                  | Issa                            |                                       |                   | -                    | 0.01    | 5.0                  | μА      | VSS, VSS2                               |

|                |                                          | age Current                     | I <sub>5Q</sub>                 | V <sub>5</sub> = -12V (Relative       |                   | -                    | 0.01    | 15                   | μА      | V <sub>5</sub>                          |

|                |                                          | al Capacitance                  | C <sub>IN</sub>                 | T <sub>A</sub> = 25°C f = 1.0MH       | ·lz               | -                    | 5.0     | 8.0                  | pF      | *************************************** |

|                | cillator                                 | Internal Oscillator             | fosc                            | T <sub>A</sub> = 25°C                 |                   | 18                   | 22      | 26                   | KHz     | *8                                      |

| Fre            | quency                                   | External Input                  | f <sub>CL</sub>                 | SPLC501C                              |                   | 18                   | 22      | 26                   | KHz     | CL                                      |

|                | Input Vo                                 | oltage                          | VSS2                            | With Triple (Relative                 |                   | -4.0                 | -       | -2.4                 | V       | VSS2                                    |

| <u>_</u>       | Curant                                   | C-4                             | VSS2                            | With Quad (Relative                   | to VDD)           | -3.0                 | -       | -2.4                 | V       | VSS2                                    |

| Powe           | voltage                                  | Setup-up output<br>Circuit      | V <sub>out</sub>                | (Relative to VDD)                     |                   | -12                  | -       | -                    | V       | V <sub>out</sub>                        |

| Internal Power | _                                        | regulator Circuit<br>ng Voltage | V <sub>OUT</sub>                | (Relative to VDD)                     |                   | -12                  | -       | -6.0                 | v       | V <sub>OUT</sub>                        |

| Ξ              |                                          | Follower Circuit<br>ng Voltage  | V <sub>5</sub>                  | (Relative to VDD)                     |                   | -12                  | -       | -4.5                 | V       | V <sub>5</sub> *9                       |

|                | Base Vo                                  | oltage                          | V <sub>REG0</sub>               | $T_A = 25^{\circ}C$ (Relative to VDD) | -0.05%/℃          | -2.28                | -2.22   | -2.16                | V       | *10                                     |

<sup>\*</sup>Possible operating voltage (1A) is applied for possible operating voltage (3A)

<sup>\*</sup>Possible operating voltage (1B) is applied for possible operating voltage (3B)

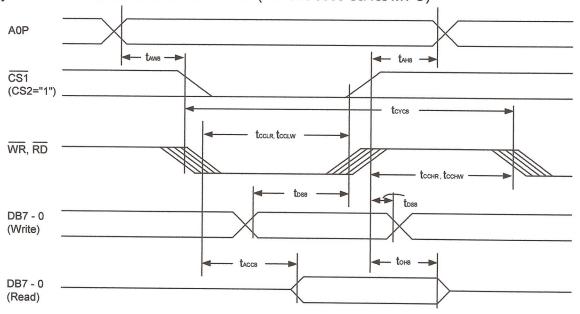

#### 8-2. Timing Characteristics

#### System Bus Read/Write Characteristics (For the 8080 Series MPU)

$(VDD = 2.7V \text{ to } 4.5V, T_A = 25^{\circ}C)$

| (VDD - 2.7 V to 4.3 V, 1 <sub>A</sub> - 25 C) |         |                   |                        |      |      |       |  |

|-----------------------------------------------|---------|-------------------|------------------------|------|------|-------|--|

| Item                                          | Signal  | Symbol            | Condition              | Rat  |      |       |  |

|                                               | Signal  | Cymbol            | Condition              | Min. | Max. | Units |  |

| Address hold time                             | 400     | t <sub>AH8</sub>  |                        | 0    | _    | ns    |  |

| Address setup time                            | A0P     | t <sub>AW8</sub>  |                        | 0    | -    | ns    |  |

| System cycle time                             | A0P     | t <sub>CYC8</sub> |                        | 300  | -    | ns    |  |

| Control L pulse width (WR)                    | WR      | t <sub>cclw</sub> |                        | 60   | -    | ns    |  |

| Control L pulse width (RD)                    | RD      | t <sub>CCLR</sub> | ,                      | 120  | -    | ns    |  |

| Control H pulse width (WR)                    | WR      | t <sub>cchw</sub> |                        | 60   | -    | ns    |  |

| Control H pulse width (RD)                    | RD      | t <sub>cchr</sub> |                        | 60   | -    | ns    |  |

| Data setup time                               |         | t <sub>DS8</sub>  |                        | 40   | -    | ns    |  |

| Address hold time                             |         | t <sub>DH8</sub>  |                        | 15   | _    | ns    |  |

| RD access time                                | DB7 - 0 | t <sub>ACC8</sub> | 0 100 -                | -    | 140  | ns    |  |

| Output disable time                           |         | t <sub>OH8</sub>  | C <sub>L</sub> = 100pF | 10   | 100  | ns    |  |

<sup>\*1</sup> The input signal rise time and fall time (tr, tf) is specified at 15 ns or less. When the system cycle time is extremely fast,  $(tr+tf) \leq (t_{CYC6}-t_{EWLW}-t_{EWHW})$  for  $(tr+tf) \leq (t_{CYC6}-t_{EWLR}-t_{EWHR})$  are specified. \*2 All timing is specified using 20% and 80% of  $V_{DD}$  as the reference.

<sup>\*3</sup>  $t_{\text{EWLW}}$  and  $t_{\text{EWLR}}$  are specified as the overlap between CS1 being "L" (CS2 = "H") and E.

# 8-3. Electro-Optical characteristics

| Item                    |      | Temp | Unit   | Standard value          |                     |      |  |

|-------------------------|------|------|--------|-------------------------|---------------------|------|--|

|                         |      | Тапр | Onit   | Min                     | Тур                 | Max  |  |

| Operating voltage       | Vop  | 25°C | V8     | 9.2                     | 9.3                 | 9.5  |  |

| operating vortage       | V ОР | 0°C  | VO     | 9.3                     | 9.5                 | 9.7  |  |

| Frame frequency         | f    | 25°C | Hz     | 64                      |                     | 200  |  |

| Response time           | Ton  | 25°C | mana   | 150                     |                     | 250  |  |

| response time           | Toff | 25°C | msec   | 150                     |                     | 250  |  |

| Dissipation current     | lop  | 25°C | uA/cm² | Main will have spin com | No. 60 am am        | 3    |  |

| Contrast ratio (θ= 30°) | CR   | 25°C |        | 3                       |                     |      |  |

| Viewing angle (CR>2)    | θ    | 25°C | Deg    | - 45                    | 000 000 000 000 000 | + 45 |  |

| vicwing angle (CR22)    | ф    | 25°C | Deg    | - 45                    |                     | + 45 |  |

#### 9.QUALITY SPECIFICATIONS9

#### 9.1. Standard of the product appearance test

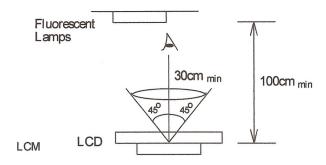

Manner of appearance test: The inspection should be performed in using 20W x 2 fluorescent lamps. Distance between LCM and fluorescent lamps should be 100 cm or more. Distance between LCM and inspector eyes should be 30 cm or more.

Viewing direction for inspection is 45° from vertical against LCM.

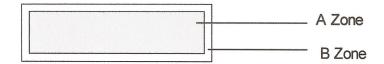

Definition of zone:

A Zone: Active display area (minimum viewing area).

B Zone: Non-active display area (outside viewing area).

# **9.2. Specification of quality assurance** www.DataSheet4U.com

AQL inspection standard

Sampling method: MIL-STD-105E, Level II, single sampling

Defect classification:

| OL :     | 14                           | Nete             | A 01  |

|----------|------------------------------|------------------|-------|

| Classify | Item                         | Note             | AQL   |

| Major    | Short or open circuit        | 1                | 0.65  |

|          | LC leakage                   |                  | (C=0) |

|          | Flickering                   |                  |       |

|          | No display                   |                  |       |

|          | Wrong viewing direction      |                  |       |

|          | Contrast defect (dim, ghost) | 2                |       |

|          | Wrong or missing component   | 10               |       |

| Minor    | Background color deviation   | 2                | 1.0   |

|          | Black spot and dust          | 3                |       |

|          | Line defect, Scratch         | 4                |       |

|          | Rainbow                      | 5                |       |

|          | Chip                         | 6                |       |

|          | Pin hole                     | 7                |       |

|          | Protruded glass              | 8                |       |

|          | Polarizer bubble and foreign | 3                |       |

|          | material                     |                  |       |

|          | FPC Position                 | 9                |       |

|          | Cross talk                   | Refer to limited |       |

|          |                              | sample           |       |

#### Note on defect classification

| M <b>O.</b> Dat | aSheet4U.com <b>I tem</b>         | Criterion                                                |                                             |               |                                 |          |

|-----------------|-----------------------------------|----------------------------------------------------------|---------------------------------------------|---------------|---------------------------------|----------|

| 1               | Short or open circuit             | Not allowed                                              |                                             |               |                                 |          |

|                 | LC leakage                        |                                                          |                                             |               |                                 |          |

|                 | Flickering                        |                                                          |                                             |               |                                 |          |

|                 | No display                        |                                                          |                                             |               |                                 |          |

|                 | Wrong viewing direction           |                                                          |                                             |               |                                 |          |

|                 | Wrong Back-light                  |                                                          |                                             |               |                                 |          |

| 2               | Contrast defect                   | Refer to approval sample                                 |                                             | ple           | Name to combine to combine the  |          |

|                 | Background color deviation        |                                                          |                                             |               |                                 |          |

| 3               | Point defect,<br>Black spot, dust | <u></u>                                                  |                                             | Point<br>Size | Acceptable Qty.                 |          |

|                 | (including Polarizer)             | \ X'                                                     |                                             | φ≤0.10        | Disregard                       |          |

|                 |                                   |                                                          |                                             | 0.10<φ≤0.20   | 2                               |          |

|                 | $\phi = (X+Y)/2$                  |                                                          |                                             | 0.20<φ≤0.25   | 1                               |          |

|                 |                                   |                                                          | L                                           | φ>0.25        | 0                               |          |

|                 |                                   |                                                          |                                             | 1             | Unit: mm                        |          |

| 4               | Line defect,                      |                                                          | patronomonomonomonomonomonomonomonomonomono |               |                                 |          |

|                 | Scratch                           |                                                          |                                             | Line          | Acceptable Qty                  | $\perp$  |

|                 |                                   |                                                          |                                             | W<br>W≤0.015  | Disregard                       | $\dashv$ |

|                 |                                   | _                                                        | L≤3.0                                       |               | Dia cgara                       | $\dashv$ |

|                 |                                   |                                                          | L ≤ 2.0                                     |               | 2                               |          |

|                 |                                   |                                                          | L≤1.0                                       |               | 1                               | $\neg$   |

|                 |                                   |                                                          |                                             | W>0.05        | Applied as poir defect Unit: mm | nt       |

| 5               | Rainbow                           | Not more than two colors change across the viewing area. |                                             |               |                                 |          |

| w <b>No</b> )alaSheet4U.cd <b>Item</b> |                                                      | Criterion                                                                                                                                    |

|----------------------------------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 6                                      | Chip  Remark: X: Length direction Y: Short direction | Acceptable criterion $\begin{array}{c cccc} X & Y & Z \\ \hline & & & & & & & \\ \hline & & & & & & & \\ \hline & & & &$                     |

|                                        | Z: Thickness direction t: Glass thickness            | Acceptable criterion $\begin{array}{c cccc} X & Y & Z \\ \hline X & Y & Z \\ \hline & \leq 2 & 0.5 \text{mm} & \leq t \\ \hline \end{array}$ |

|                                        |                                                      | Acceptable criterion $\begin{array}{c cccc} X & Y & Z \\ \leq 3 & \leq 2 \\ \hline \text{shall not reach to ITO} & \leq t \end{array}$       |

|                                        |                                                      | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                        |

|                                        |                                                      | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                        |

# **APEX DISPLAY LIMITED**

| v <b>No</b> .DataSheet4U.co <b>i[tem</b> |                                     | Criterion                                                                                                                                                                                                           |

|------------------------------------------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7                                        | Dot-matrix pattern $\phi = (X+Y)/2$ | Pin hole                                                                                                                                                                                                            |

|                                          |                                     | Size Acceptable Qty. $\phi < 0.1$ Disregard $\phi > 0.20$ 0  C: Shall not touch other dot(s).                                                                                                                       |

| 8                                        | Protruded W: Terminal width         | W Acceptable criteria: $Y \le 0.4$                                                                                                                                                                                  |

| 9                                        | FPC                                 | Position                                                                                                                                                                                                            |

|                                          |                                     | H H1 FPC ITO $W1 \le 1/3W$ $H1 \le 1/3H$                                                                                                                                                                            |

|                                          |                                     | hı H Acceptable: $ h2 - h1  \le 1/8H$                                                                                                                                                                               |

| 10                                       | Total no. of acceptable Defect      | A. Zone  Maximum 2 minor non-conformities per one unit.  Defect distance: each point to be separated over 10mm  B. Zone  It is acceptable when it is no trouble for quality and assembly in customer's end product. |

# 9.3. Reliability of LCM

www DataSheet4U com

Reliability test condition:

| Item                      | Condition                                              | Time (hrs) | Assessment                                                 |

|---------------------------|--------------------------------------------------------|------------|------------------------------------------------------------|

| High temp. Storage        | 80°C                                                   | 240        |                                                            |

| High temp. Operating      | 70°C                                                   | 240        |                                                            |

| Low temp. Storage         | -30°C                                                  | 240        | No abnormalities                                           |

| Low temp. Operating       | -20°C                                                  | 240        | in functions                                               |

| Humidity                  | 40°C/ 90%RH                                            | 240        | and appearance                                             |

| Temp. Cycle(no operating) | -30°C ← $25$ °C → $+80$ °C<br>(30 min ← 5 min → 30min) | 10cycles   |                                                            |

| ESD test                  | Contact Discharges: ±4KV; Air Discharges: ±8KV         | 2pcs       | When turning on power again, No abnormalities in functions |

#### 9.4. Precaution For Using LCM

LCM is assembled and adjusted with a high degree of precision. Do not attempt to make any alteration or modification. The followings should be noted.

#### **General Precautions:**

- 1. LCD panel is made of glass. Avoid excessive mechanical shock or applying strong pressure onto the surface of display area.

- 2. The polarizer used on the display surface is easily scratched and damaged. Extreme care should be taken when handling. To clean dust or dirt off the display surface, wipe gently with cotton, or other soft material soaked with isopropyl alcohol, ethyl alcohol or trichlorotriflorothane, do not use water, ketone or aromatics and never scrub hard.

- 3. Be careful not to touch or swallow liquid crystal that might leak from a damaged cell. Any liquid crystal adheres to skin or clothes, wash it off immediately with soap and water.

#### **Static Electricity Precautions:**

- 1. CMOS-LSI is used for the module circuit; therefore, operators should be grounded whenever he/she comes into contact with the module.

- 2. Do not touch any of the conductive parts such as the LSI pads; the copper leads on the PCB and the interface terminals with any parts of the human body.

- 3. Do not touch the connection terminals of the display with bare hand; it will cause disconnection or defective insulation of terminals.

- 4. The modules should be kept in anti-static bags or other containers resistant to static for storage.

- 5. Only properly grounded soldering irons should be used.

- 6. If an electric screwdriver is used, it should be grounded and shielded to prevent sparks.

- 7. The normal static prevention measures should be observed for work clothes and working benches.

- 8. Since dry air is inductive to static, a relative humidity of 65±15% is recommended.

#### **Operation Precautions:**

- 1. The viewing angle can be adjusted by varying the LCD driving voltage Vo.

- 2. Since applied DC voltage causes electro-chemical reactions, which deteriorate the display, the applied pulse waveform should be a symmetric waveform such that no DC component remains. Be sure to use the specified operating voltage.

- 3. Driving voltage should be kept within specified range; excess voltage will shorten display life.

- 4. Response time increases with decrease in temperature.

- 5. Display color may be affected at temperatures above its operational range.

- 6. The LCM could only withstand upto 45,000 Lux light intensity. Therefore it advisable to avoid direct sunlight exposure on the LCM. If direct sunlight is unavoidable, proper housing is necessary to protect the LCM.

- 7. Operating humidity should be within 65±15%RH.

#### **Storage Precautions:**

- 1. Keep the temperature within the specified range usage and storage. Excessive temperature and humidity could cause polarization degradation, polarizer peel-off or generate bubbles.

- 2. For long-term storage over 25±3°C is required, the relative humidity should be kept below 65±15%, and avoid direct sunlight.

#### **Limited Warranty**

LCDs and modules are not consumer products, but may be incorporated by WILY's customers into consumer products or components thereof, WILY does not warrant that its LCDs and components are fit for any such particular purpose.

- 1. The liability of WILY is limited to repair or replacement on the terms set forth below. WILY will not be Responsible for any subsequent or consequential events, injury, or damage to any personnel or user including third party personnel and/or user. Unless otherwise agreed in writing between WILY and the customer, WILY will only replace or repair any of its LCD which is found defective electrically or visually when inspected in accordance with WILY GENERAL LCD INSPECTION STANDARD. (Copies available on request)

- 2. No warranty can be granted if any of the precautions state in handling liquid crystal display above has been disregarded. Broken glass, scratches on polarizer mechanical damages as well as defects that are caused accelerated environment tests are excluded from warranty.

- 3. In returning the LCD/LCM, they must be properly packaged; there should be detailed description of the failures or defect.