#### **Features**

Single chip USB 2.0 to Quad Serial Ports and Single Parallel Port controller

#### USB Device Controller

- Integrates on-chip USB 2.0 PHY and controller compliant to USB Spec 2.0 and 1.1

- Supports all USB 2.0 power saving modes (L1, L2)

- Supports USB High/Full Speed modes with Bus-power or Self-power device

- Support USB LPM (Link Power Management)

#### Dual/Quad Serial Port Controller

- Two/Four 16c450/16c550 compatible UARTs

- Supports SIR IrDA mode on any/all ports

- Supports RS-232, RS-485 and RS-422 serial ports

- Supports multi-protocol serial transceivers

- Supports 5, 6, 7, 8 & 9 bit serial data

- Supports automatic data direction control

- Supports multi-drop mode with auto address detection

- Supports hardware and software flow control

- Supports baud rates from 50bps to 6Mbps

- Supports custom baud rates from external clock

- On-Chip 1024-Byte FIFO for upstream and 512-Byte for downstream data transfer for each Serial Port

- I<sup>2</sup>C interface for EEPROM

- Supports read/write EEPROM through USB interface

- On-Chip buffers for serial port signals to operate without external transceivers over short cable

- Pin to Pin compatible with MCS7840

- Driver backward compatible with MCS7840

### **♦** Support Remote Wake Up Function

■ Supports Suspend Mode and Remote Wakeup via RXD, RI, DSR, DCD and CTS pin

Document No: AX78140/V1.10/12/07/17

#### Advanced Power Management Features

- Supports USB LPM (Link Power Management)

- Shut down Transceiver when in Suspend Mode

#### Parallel Port

- AX78140 supports optional 2 Serial Port and 1 Parallel Port configuration

- On-Chip 1024-Byte FIFO for upstream and 512-Byte for downstream data transfer for Parallel Port

#### GPIO

- AX78140 supports 1 GPIO pin and 16 optional software controlled GPIO pins

- Integrates on-chip 1.8V and 3.3V voltage regulator and only requires a single 5V power supply

- Single 12MHz clock input from either crystal or oscillator source

- Integrates on-chip power-on reset circuit

- Small form factor with 64-pin LQFP RoHS compliant package

- Operating over 0°C to 70°C or -40°C to +85°C temperature range

#### Applications

- Serial Attached Devices

- Modems, Generic Serial Devices

- Serial-Port Server

- Data Acquisition System

- POS Terminal & Industrial PC

TEL: 886-3-579-9500 FAX: 886-3-579-9558 http://www.asix.com.tw

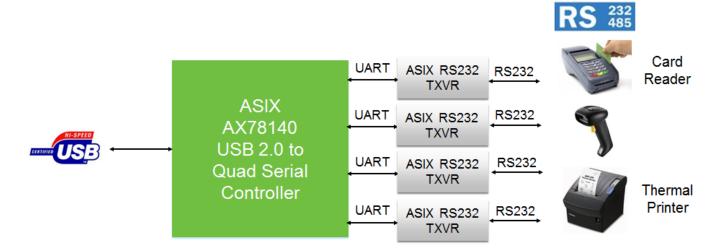

### **Typical System Block Diagrams**

• Hosted by USB to operate with Quad Serial Ports

Figure 1: USB 2.0 to quad serial ports

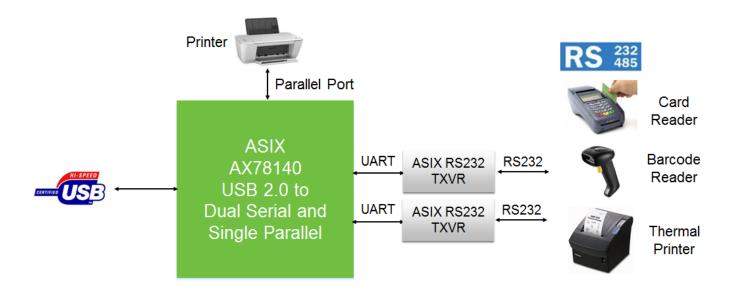

Hosted by USB to operate with Dual Serial Ports and Single Parallel Port

Figure 2: USB 2.0 to dual serial ports and single parallel port

## USB 2.0 to Multi I/O Controller

Copyright © 2016-2017 ASIX Electronics Corporation. All rights reserved.

#### **DISCLAIMER**

No part of this document may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, for any purpose, without the express written permission of ASIX. ASIX may make changes to the product specifications and descriptions in this document at any time, without notice.

ASIX provides this document "as is" without warranty of any kind, either expressed or implied, including without limitation warranties of merchantability, fitness for a particular purpose, and non-infringement.

Designers must not rely on the absence or characteristics of any features or registers marked "reserved", "undefined" or "NC". ASIX reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. Always contact ASIX to get the latest document before starting a design of ASIX products.

#### **TRADEMARKS**

ASIX, the ASIX logo are registered trademarks of ASIX Electronics Corporation. All other trademarks are the property of their respective owners.

## **Table of Contents**

| 1 | INT          | RODUCTION                                                                      |    |

|---|--------------|--------------------------------------------------------------------------------|----|

|   | 1.1          | GENERAL DESCRIPTION                                                            |    |

|   | 1.2          | BLOCK DIAGRAM                                                                  |    |

|   | 1.3          | PINOUT DIAGRAM                                                                 |    |

| 2 |              | NAL DESCRIPTION                                                                |    |

| 4 |              |                                                                                |    |

|   | 2.1          | 64-PIN PINOUT DESCRIPTION                                                      |    |

|   | 2.2          | HARDWARE SETTING FOR OPERATION MODE                                            | 1  |

| 3 | FUN          | NCTION DESCRIPTION                                                             | 12 |

|   | 3.1          | INTERNAL REGULATORS                                                            | 12 |

|   | 3.2          | USB 2.0 PHY                                                                    | 12 |

|   | 3.3          | USB 2.0 Device Controller                                                      | 12 |

|   | 3.4          | BRIDGE                                                                         | 12 |

|   | 3.5          | VENDOR COMMAND PROCESSOR                                                       |    |

|   | 3.6          | SERIAL PORT CONTROLLERS                                                        |    |

|   | 3.7          | PARALLEL PORT CONTROLLER                                                       |    |

|   | 3.8          | WAKE-UP BLOCK                                                                  |    |

|   | 3.9          | I <sup>2</sup> C EEPROM Controller                                             |    |

|   | 3.10         | CLOCK GENERATION AND RESET                                                     |    |

|   | 3.11         | BAUD CLOCK GENERATORS                                                          |    |

|   | 3.12         | GPIO                                                                           | 13 |

| 4 | $I^2C$       | EEPROM MEMORY MAP                                                              | 14 |

|   | 4.1          | DETAILED DESCRIPTION                                                           | 15 |

|   | 4.1.         |                                                                                |    |

|   | 4.1.         |                                                                                |    |

|   | 4.1          | 3 Serial Port 1 – Device Configuration Register 2 (0x0A)                       |    |

|   | 4.1.         | 4 Serial Port (2, 3, & 4) – Device Configuration Register 0 (0x0B, 0x0E, 0x11) | 18 |

|   | 4.1          | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \                                          |    |

|   | 4.1.         | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \                                          |    |

|   | 4.1.         | ( )                                                                            |    |

|   | 4.1.         |                                                                                |    |

|   | 4.1.         | 9 USB Descriptor Registers (0x83~0x87, 0x89~0x8F)                              | 22 |

| 5 | USI          | 3 CONFIGURATION STRUCTURE                                                      | 23 |

|   | 5.1          | USB CONFIGURATION                                                              | 23 |

|   | 5.2          | USB Interface.                                                                 |    |

|   | 5.3          | USB ENDPOINTS                                                                  |    |

| 6 | ELI          | ECTRICAL SPECIFICATIONS                                                        | 24 |

| Ů |              |                                                                                |    |

|   | 6.1          | DC CHARACTERISTICS                                                             |    |

|   | 6.1.<br>6.1. | e e e e e e e e e e e e e e e e e e e                                          |    |

|   | 6.1          | 1 0                                                                            |    |

|   | 6.1.         |                                                                                |    |

|   | 6.1.         | J                                                                              |    |

|   | 6.2          | POWER CONSUMPTION                                                              |    |

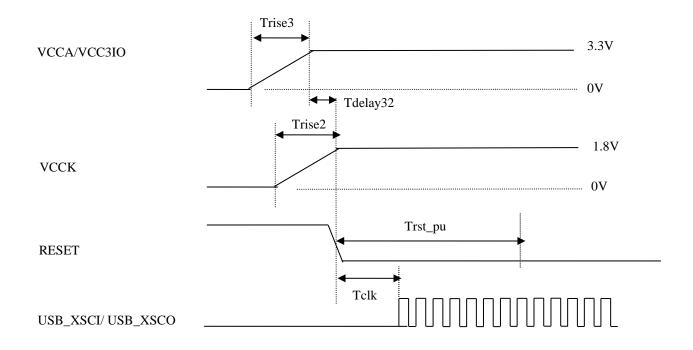

|   | 6.3          | POWER-UP SEQUENCE                                                              |    |

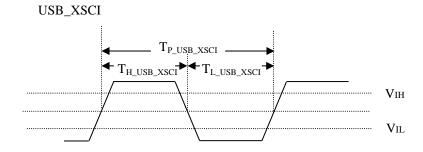

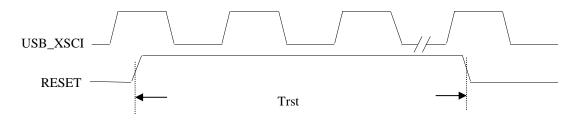

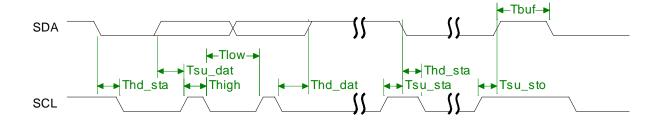

|   | 6.4          | AC TIMING CHARACTERISTICS                                                      |    |

|   | 6.4.         |                                                                                |    |

|   | 6.4.         |                                                                                |    |

|   | 6.4          |                                                                                |    |

| 7 | PAC          | CKAGE INFORMATION                                                              | 3( |

| , | I A          | VALIGE & 1 VIVIIIIVI 1                                                         |    |

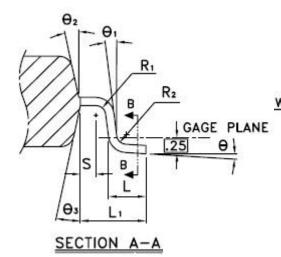

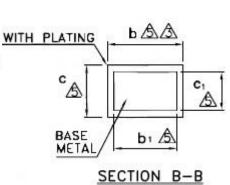

| 7.1    | 64-PIN LQFP 10x10 PACKAGE                                  | 30 |

|--------|------------------------------------------------------------|----|

| 8 O    | PRDERING INFORMATION                                       | 31 |

| 9 R    | EVISION HISTORY                                            | 32 |

|        |                                                            |    |

|        |                                                            |    |

|        |                                                            |    |

|        |                                                            |    |

|        | List of Figures                                            |    |

|        | List of Figures                                            |    |

| FIGURE | E 1: USB 2.0 TO QUAD SERIAL PORTS                          | 1  |

|        | E 2: USB 2.0 TO DUAL SERIAL PORTS AND SINGLE PARALLEL PORT |    |

|        | E 3: BLOCK DIAGRAME 4: PINOUT DIAGRAM                      |    |

|        |                                                            |    |

|        |                                                            |    |

|        |                                                            |    |

|        |                                                            |    |

|        | List of Tables                                             |    |

|        | 1: PINOUT DESCRIPTION                                      |    |

|        | 2: SERIAL EEPROM MEMORY MAP                                |    |

| TABLE  | 6: POWER CONSUMPTION                                       | 26 |

## AASIX

## AX78140 USB 2.0 to Multi I/O Controller

### 1 Introduction

### 1.1 General Description

With the rapid proliferation of USB interface in the embedded world, developers are looking for easiest ways to add USB to microcontroller-based applications in their design. ASIX's new AX78140 features three USB connectivity bridge solutions including USB 2.0 to Quad Serial Ports and USB 2.0 to Dual Serial Ports and Single Parallel Port controllers. For enabling smooth migration from legacy system using ASIX's MCS7840, AX78140 provides pin-to-pin compatible and driver backward compatible with MCS7840.

AX78140 is a USB 2.0 to Quad Serial Ports and Single Parallel Port controller. It has been developed to connect a wide range of standard serial devices to a USB host.

The AX78140 supports the following serial communication programs including: HyperTerminal, PComm, Windows direct connection, Windows dial-up connection through modem, Networking over IrDA and Windows direct connection over IrDA, and Minicom.

The AX78140, in 64-pin LQFP, is available with RoHS compliant package and supports commercial grade operating temperature range from 0 to 70°C and industrial grade from -40 to 85°C.

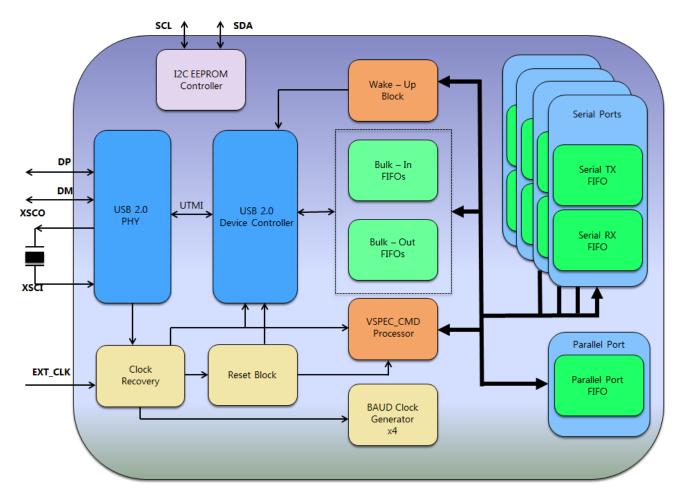

## 1.2 Block Diagram

Figure 3: Block Diagram

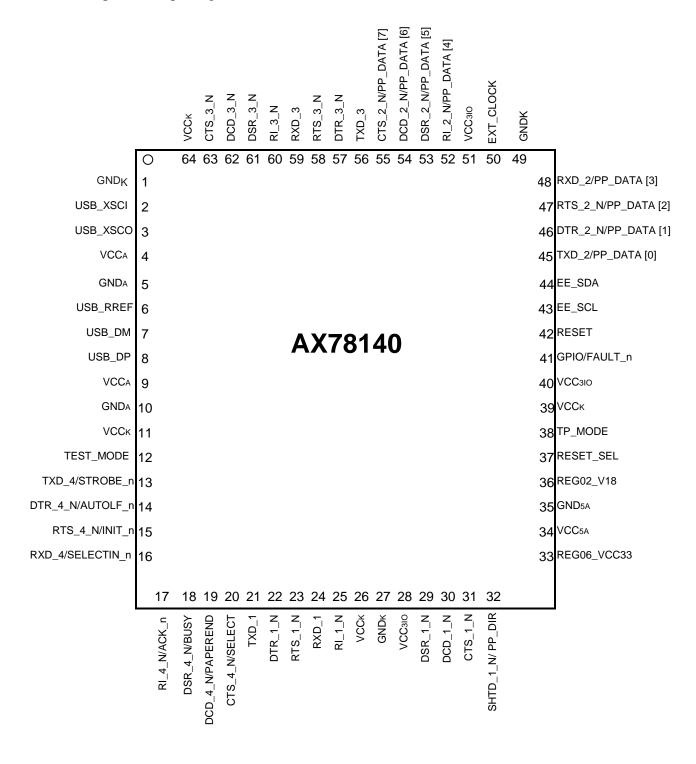

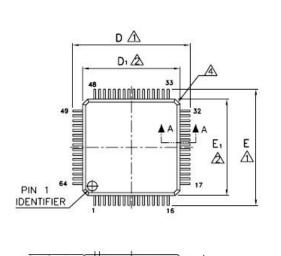

### 1.3 Pinout Diagram

• 64-pin LQFP package

Figure 4: Pinout Diagram

## 2 Signal Description

The following abbreviations apply to the following pin description table.

**I18** Input, 1.8V ΑI **Analog Input I3** Input, 3.3V **Analog Output** AO Analog Bi-directional I/O **I**5 Input, 3.3V with 5V tolerant AB **O5** Output, 3.3V with 5V tolerant  $\mathbf{PU}$ Internal Pull Up (75K ohm) Internal Pull Down (75K ohm) **B5** Bi-directional I/O, 3.3V with 5V tolerant PD **B3** Bi-directional I/O, 3.3V Schmitt Trigger  $\mathbf{S}$ Power/GND T Tri-stateable P

### 2.1 64-pin Pinout Description

| D' . N               | Т            | D' N.         | P's Described as                                                                                                                                                                                   |

|----------------------|--------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name             | Type         | Pin No        | Pin Description                                                                                                                                                                                    |

| HCD DM               | I AD I       | 7             | USB Interface                                                                                                                                                                                      |

| USB_DM               | AB           | <u>7</u><br>8 | USB 2.0 data negative pin.                                                                                                                                                                         |

| USB_DP               | AB           | 8             | USB 2.0 data positive pin.                                                                                                                                                                         |

| Hab Maci             | 12           |               | Clock Pins                                                                                                                                                                                         |

| USB_XSCI             | I3           | 2             | 12Mhz crystal or oscillator clock input.                                                                                                                                                           |

| USB_XSCO             | O3           | 3             | 12Mhz crystal or oscillator clock output.                                                                                                                                                          |

| EE GGI               | D f /DI / E  | 42            | Serial EEPROM Interface                                                                                                                                                                            |

| EE_SCL               | B5/PU/T      | 43            | 2-Wire(I <sup>2</sup> C) EEPROM Clock. Default=High(1)                                                                                                                                             |

| EE_SDA               | B5/PU/T      | 44            | 2-Wire(I <sup>2</sup> C) EEPROM Data in/out. Default=High(1)                                                                                                                                       |

|                      | <del>_</del> |               | Misc. Pins                                                                                                                                                                                         |

| USB_RREF             | I5/PU/S      | 6             | External Reference Resistor (12.1 K $\Omega$ , 1%) Connect resistor to Analog GND.                                                                                                                 |

| TEST_MODE            | I5/PD/S      | 12            | Test Mode Pin, (active high). Default = Low (0) When TEST_MODE = 1, PLL, Core, and SCAN/BIST/ Memory BIST testing can be performed. Set TEST_MODE = 0 for normal operation.                        |

| TXD_4/<br>STROBE_n   | B5/S         | 13            | Serial Port 4 Transmit Data out to transceiver or IrDA data out to IR LED. If AX78140 is configured in 2S1P mode, this pin will operate as STROBE_n.                                               |

| DTR_4_N/<br>AUTOLF_n | B5/S         | 14            | Serial Port 4 Data Terminal Ready (in serial protocol), active low. If AX78140 is configured in 2S1P mode, this pin will operate as AUTOLF n.                                                      |

| RTS_4_N/<br>INIT n   | B5/S         | 15            | Serial Port 4 Request To Send (in serial protocol), active low. If AX78140 is configured in 2S1P mode, this pin will operate as INIT n.                                                            |

| RXD_4/<br>SELECTIN_n | B5/S         | 16            | Serial Port 4 Serial Receive Data in from transceiver or IrDA data in from IrDA detector.  If AX78140 is configured in 2S1P mode, this pin will operate as SELECTIN n.                             |

| RI_4_N/<br>ACK_n     | B5/S         | 17            | Serial Port 4 Ring Indicator, active low.  If AX78140 is configured in 2S1P mode, this pin will operate as ACK_n.  This pin can also perform as a SW controlled GPIO.                              |

| DSR_4_N/<br>BUSY     | B5/S         | 18            | Serial Port 4 Data Set Ready (in serial protocol), active low.  If AX78140 is configured in 2S1P mode, this pin will operate as BUSY.  This pin can also perform as a SW controlled GPIO.          |

| DCD_4_N/<br>PAPEREND | B5/S         | 19            | Serial Port 4 Data Carrier Detect (in serial protocol), active low.  If AX78140 is configured in 2S1P mode, this pin will operate as PAPEREND.  This pin can also perform as a SW controlled GPIO. |

| CTS_4_N/<br>SELECT   | B5/S         | 20            | Serial Port 4 Clear To Send (in serial protocol), active low.  If AX78140 is configured in 2S1P mode, this pin will operate as SELECT.  This pin can also perform as a SW controlled GPIO.         |

| DTR_L N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | TXD_1       | B5/S    | 21         | Serial Port 1 Transmit Data out to transceiver, or IrDA data out to IR LED.  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------|------------|------------------------------------------------------------------------------|

| RTS 1 N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |             |         |            |                                                                              |

| RND_    15/8   24   Serial Port 1 Serial Receive Data in from transceiver, or IrDA data in from from transceiver or IrDA data on to IRLED.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |         |            | • • • • • • • • • • • • • • • • • • • •                                      |

| IrDA detector.   RL_LN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |             |         |            | • • • • • • • • • • • • • • • • • • • •                                      |

| RL   N   B5/S   25   Scrial Port I Ring Indicator, active low. This pin can also perform as a SW controlled GPIO.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 10.12_1     | 10,2    |            |                                                                              |

| This pin can also perform as a SW controlled GPIO.  DSR_1_N  B5/S  29 Serial Port 1 Data Set Ready (in serial protocol), active low.  This pin can also perform as a SW controlled GPIO.  DCD_1_N  B5/S  30 Serial Port 1 Data Carrier Detect (in serial protocol), active low.  This pin can also perform as a SW controlled GPIO.  CTS_1_N  B5/S  31 Serial Port 1 Clear To Send (in serial protocol), active low.  This pin can also perform as a SW controlled GPIO.  CTS_1_N  B5/S  31 Serial Port 1 Clear To Send (in serial protocol), active low.  This pin can also perform as a SW controlled GPIO.  SHTD_1_N/  B5/S  32 Shut Down External Serial Transceiver during normal operation, active low by default, can be configured active high by using DCR setting.  ITAX/18140 is configured in 2S1P mode, this pin will operate as PP_DIATA [6].  B5/S  41 GPIO/USB Max. Power  GPIO_MODE - Bidirectional GPIO bit. The direction (Input or Output) is controlled by the DCR for Serial Port #1.  This pin is also used to indicate the USB Max. Power configuration while reporting USB device configuration descriptor to USB host. (High = S00ma; Low 100mA).  If AX78140 is configured in 2S1P mode, this pin will operate as PAULT_n.  RESET  15/S  42 Reset signal. The polarity is determined by RESET_SEI, pin.  RESET  15/S  43 Serial Port 2 Transmit Data out to transceiver, or IrDA data out to IR LED.  If AX78140 is configured in 2S1P mode, this pin will operate as PP_DATA [0].  B5/S  44 Serial Port 2 Data Terminal Ready (in serial protocol), active low. If AX78140 is configured in 2S1P mode, this pin will operate as PP_DATA [1].  RTS_2_N/  B5/S  45 Serial Port 2 Request To Send (in serial protocol), active low. If AX78140 is configured in 2S1P mode, this pin will operate as PP_DATA [2].  RTS_2_N/  B5/S  46 Serial Port 2 Request To Send (in serial protocol), active low. If AX78140 is configured in 2S1P mode, this pin will operate as PP_DATA [3].  B5/S  47 Serial Port 2 Request To Send (in serial protocol), active low. If AX78140 is configured in 2S1P mode, th | RI 1 N      | B5/S    | 25         |                                                                              |

| DSR_1_N   B5/S   29   Serial Port 1 Data Set Ready (in serial protocol), active low. This pin can also perform as a SW controlled GPIO.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |             |         |            |                                                                              |

| This pin can also perform as a SW controlled GPIO.   DCD_1_N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | DSR 1 N     | B5/S    | 29         |                                                                              |

| DCD_1_N   B5/8   30   Serial Port 1 Data Carrier Detect (in serial protocol), active low. This pin can also perform as a SW controlled GPIO.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | DSIC_I_I    | 3375    |            |                                                                              |

| This pin can also perform as a SW controlled GPIO.  CTS_1_N  B5/S  31 Serial Port 1 Clear To Send (in serial protocol), active low. This pin can also perform as a SW controlled GPIO.  SHTD_1_N/ B5/S  32 Shut Down External Serial Transceiver during normal operation, active low by default, can be configured active high by using DCR setting. If AX78140 is configured in 2S1P mode, this pin will operate as PP_DIR  RESET_SEL  II8/S  37 Select the polarity of RESET signal. Please refer to 2.2 Hardware Setting For Operation Mode.  TP_MODE  IS/PD/S  B5/S  41 GPIO/USB Max. Power  GPIO_MODE - Bidirectional GPIO bit. The direction (Input or Output) is controlled by the DCR for Serial Port #1.  This pin is also used to indicate the USB Max. Power configuration while reporting USB device configuration descriptor to USB host. (High = 500max; Low = 100ma/)  If AX78140 is configured in 2S1P mode, this pin will operate as FAULT_n.  RESET  I5/S  42 Reset signal. The polarity is determined by RESET_SEL pin.  Serial Port 2 Transmit Data out to transceiver, or IrDA data out to IR LED. If AX78140 is configured in 2S1P mode, this pin will operate as PP_DATA [0].  B5/S  45 Serial Port 2 Data Terminal Ready (in serial protocol), active low. If AX78140 is configured in 2S1P mode, this pin will operate as PP_DATA [1].  RTS_2_N/  B5/S  46 Serial Port 2 Data Terminal Ready (in serial protocol), active low. If AX78140 is configured in 2S1P mode, this pin will operate as PP_DATA [1].  RTS_2_N/  B5/S  48 Serial Port 2 Serial Receive Data in from transceiver or IrDA data in from IrDA detector.  If AX78140 is configured in 2S1P mode, this pin will operate as PP_DATA [3].  EXT_CLOCK  I5/S  50 Input Clock from external world. In normal operation mode, clock can be supplied to serial port 2 Ring Indicator, active low. If AX78140 is configured in 2S1P mode, this pin will operate as PP_DATA [4].  This pin can also perform as a SW controlled GPIO.  CTS_2_N/  PP_DATA [6]  Serial Port 2 Data Ser Ready (in serial protocol), active low. If AX78140 is conf | DCD 1 N     | B5/S    | 30         |                                                                              |

| Serial Port 1 Clear To Send (in serial protocol), active low. This pin can also perform as a SW controlled GPIO.    SHITD_1_N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | DOD_1_1(    | 3575    | 50         |                                                                              |

| This pin can also perform as a SW controlled GPIO.   Shut Down External Serial Transceiver during normal operation, active low by default, can be configured active high by using DCR setting. If AX78140 is configured in 2S1P mode, this pin will operate as PP_DRR Select the polarity of RESET signal. Please refer to 2.2 Hardware Setting For Operation Mode.   The Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | CTS 1 N     | B5/S    | 31         |                                                                              |

| SHTD_1N   PP_DIR   B5/S   Start Down External Serial Transceiver during normal operation, active low by default, can be configured active high by using DCR setting. If AX78140 is configured in 2S1P mode, this pin will operate as PP_DIR   Select the polarity of RESET signal. Please refer to 2.2 Hardware Setting For Operation Mode.   For Internal test purpose, so always tie to GND.   GPIO/USB Max. Power   GPIO/MODE - Bidirectional GPIO bit. The direction (Input or Output) is controlled by the DCR for Serial Port #1.   This pin is also used to indicate the USB Max. Power configuration while reporting USB device configuration descriptor to USB host. (High = S00ma; Low = 100mA)   If AX78140 is configured in 2S1P mode, this pin will operate as FAULT_n.   FAVR9140 is configured in 2S1P mode, this pin will operate as FAULT_n.   Serial Port 2 Data Terminal Ready (in serial protocol), active low. If AX78140 is configured in 2S1P mode, this pin will operate as PP_DATA [1]   Serial Port 2 Serial Port 2 Data Terminal Ready (in serial protocol), active low. If AX78140 is configured in 2S1P mode, this pin will operate as PP_DATA [1].   Serial Port 2 Request To Send (in serial protocol), active low. If AX78140 is configured in 2S1P mode, this pin will operate as PP_DATA [1].   Serial Port 2 Request To Send (in serial protocol), active low. If AX78140 is configured in 2S1P mode, this pin will operate as PP_DATA [2].   Serial Port 2 Request To Send (in serial protocol), active low. If AX78140 is configured in 2S1P mode, this pin will operate as PP_DATA [2].   Serial Port 2 Request To Send (in serial protocol), active low. If AX78140 is configured in 2S1P mode, this pin will operate as PP_DATA [3].   Serial Port 2 Request To Send (in serial protocol), active low. If AX78140 is configured in 2S1P mode, this pin will operate as PP_DATA [4].   FAX78140 is configured in 2S1P mode, this pin will operate as PP_DATA [4].   Serial Port 2 Data Cartier Detect (in serial protocol), active low. If AX78140 is configured in 2S1P mode, this p   |             |         |            |                                                                              |

| PP_DIR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SHTD 1 N/   | B5/S    | 32         |                                                                              |

| RESET_SEL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |             | 20,2    | ~ <u>~</u> |                                                                              |

| RESET_SEL   118/S   37   Select the polarity of RESET signal. Please refer to 2.2 Hardware Setting For Operation Mode.   13/PD/S   38   For internal test purpose, so always tie to GND.   GPIO/USB Max. Power GPIO_MODE - Bidirectional GPIO bit. The direction (Input or Output) is controlled by the DCR for Serial Port #1.   This pin is also used to indicate the USB Max. Power configuration while reporting USB device configuration descriptor to USB host. (High = 500mA; Low = 100mA)   If AX78140 is configured in 251P mode, this pin will operate as FAULT in.   RESET   15/S   42   Reset signal. The polarity is determined by RESET_SEL pin.   Serial Port 2 Transmit Data out to transceiver, or IrDA data out to IR LED. If AX78140 is configured in 251P mode, this pin will operate as PP_DATA [0]   Serial Port 2 Data Terminal Ready (in serial protocol), active low. If AX78140 is configured in 251P mode, this pin will operate as PP_DATA [1].   Serial Port 2 Request To Send (in serial protocol), active low. If AX78140 is configured in 251P mode, this pin will operate as PP_DATA [1].   Serial Port 2 Serial Receive Data in from transceiver or IrDA data in from IrDA detector.   If AX78140 is configured in 251P mode, this pin will operate as PP_DATA [2].   RXD_2/   B5/S   48   Serial Port 2 Serial Receive Data in from transceiver or IrDA data in from IrDA detector.   If AX78140 is configured in 251P mode, this pin will operate as PP_DATA [3].   Input Clock from external world. In normal operation mode, clock can be supplied to serial ports and used for custom BAUD Rate of user's choice. In test mode, clock will be the test clock input from external world.   RX78140 is configured in 251P mode, this pin will operate as PP_DATA [4].   This pin can also perform as a SW controlled GPIO.   Serial Port 2 Data Set Ready (in serial protocol), active low. If AX78140 is configured in 251P mode, this pin will operate as PP_DATA [6].   This pin can also perform as a SW controlled GPIO.   Serial Port 2 Data Carrier Detect (in serial protocol),   |             |         |            |                                                                              |

| For Operation Mode.   For internal test purpose, so always tie to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | RESET SEL   | I18/S   | 37         |                                                                              |

| TP_MODE   13/PD/S   38   For internal test purpose, so always tie to GND.   GPIO/   B5/S   41   GPIO/USB Max. Power   GPIO_MODE - Bidirectional GPIO bit. The direction (Input or Output) is controlled by the DCR for Serial Port #1.   This pin is also used to indicate the USB Max. Power configuration while reporting USB device configuration descriptor to USB host. (High = \$50mx; Low = 100mA)   If AX78140 is configured in 2S1P mode, this pin will operate as FAULT_n.   RESET   15/S   42   Reset signal. The polarity is determined by RESET_SEL pin.   TXD_2/   B5/S   45   Serial Port 2 Transmit Data out to transceiver, or IrDA data out to IR LED. If AX78140 is configured in 2S1P mode, this pin will operate as PP_DATA [0].    DTR_2_N/   B5/S   46   Serial Port 2 Data Terminal Ready (in serial protocol), active low. If AX78140 is configured in 2S1P mode, this pin will operate as PP_DATA [1].    RTS_2_N/   B5/S   47   Serial Port 2 Request To Send (in serial protocol), active low. If AX78140 is configured in 2S1P mode, this pin will operate as PP_DATA [2].    RXD_2/   B5/S   48   Serial Port 2 Serial Receive Data in from transceiver or IrDA data in from IrDA detector.   | 12221_222   | 110,5   | 0,         |                                                                              |

| GPIO/WODE - Bidirectional GPIO bit. The direction (Input or Output) is controlled by the DCR for Serial Port #1. This pin is also used to indicate the USB Max. Power configuration while reporting USB device configuration descriptor to USB host. (High = \$500mA; Low = 100mA) If AX78140 is configured in 2S1P mode, this pin will operate as FAULT_n.    RESET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | TP MODE     | I3/PD/S | 38         | 1                                                                            |

| FAULT_n  GPIO_MODE - Bidirectional GPIO bit. The direction (Input or Output) is controlled by the DCR for Serial Port #1.  This pin is also used to indicate the USB Max. Power configuration while reporting USB device configuration descriptor to USB host. (High = 500mA; Low = 100mA)  If AX78140 is configured in 2S1P mode, this pin will operate as FAULT_n.  RESET  I5/S  42  Reset signal. The polarity is determined by RESET_SEL pin.  Serial Port 2 Transmit Data out to transceiver, or IrDA data out to IR LED. If AX78140 is configured in 2S1P mode, this pin will operate as PP_DATA [0].  DTR_2_N/  PP_DATA [0]  B5/S  45  Serial Port 2 Data Terminal Ready (in serial protocol), active low. If AX78140 is configured in 2S1P mode, this pin will operate as PP_DATA [1].  RTS_2_N/  PP_DATA [2]  RSD_2/  PP_DATA [3]  B5/S  48  Serial Port 2 Request To Send (in serial protocol), active low. If AX78140 is configured in 2S1P mode, this pin will operate as PP_DATA [2].  RXD_2/  PP_DATA [3]  EXT_CLOCK  I5/S  50  Input Clock from external world. In normal operation mode, clock can be supplied to serial ports and used for custom BAUD Rate of user's choice. In test mode, clock will be the test clock input from external world.  RL_2_N/  PP_DATA [4]  DSR_2_N/  PP_DATA [5]  Serial Port 2 Data Set Ready (in serial protocol), active low. If AX78140 is configured in 2S1P mode, this pin will operate as PP_DATA [4].  This pin can also perform as a SW controlled GPIO.  DSR_2_N/  PP_DATA [6]  DCD_2_N/  PP_DATA [6]  Serial Port 2 Data Carrier Detect (in serial protocol), active low. If AX78140 is configured in 2S1P mode, this pin will operate as PP_DATA [6].  This pin can also perform as a SW controlled GPIO.  CTS_2_N/  PP_DATA [7]  B5/S  53  Serial Port 2 Data Carrier Detect (in serial protocol), active low. If AX78140 is configured in 2S1P mode, this pin will operate as PP_DATA [6].  This pin can also perform as a SW controlled GPIO.  CTS_2_N/  PP_DATA [7]                                                                                           |             |         |            |                                                                              |

| controlled by the DCR for Serial Port #1.  This pin is also used to indicate the USB Max. Power configuration while reporting USB device configuration descriptor to USB host. (High = 500mA; Low = 100mA)  If AX78140 is configured in 2S1P mode, this pin will operate as FAULT n.  RESET I5/S 42 Reset signal. The polarity is determined by RESET_SEL pin.  TXD_2/ B5/S 45 Serial Port 2 Transmit Data out to transceiver, or IrDA data out to IR LED. If AX78140 is configured in 2S1P mode, this pin will operate as PP_DATA [0].  DTR_2_N/ B5/S 46 Serial Port 2 Data Terminal Ready (in serial protocol), active low. If AX78140 is configured in 2S1P mode, this pin will operate as PP_DATA [1].  RTS_2_N/ B5/S 47 Serial Port 2 Request To Send (in serial protocol), active low. If AX78140 is configured in 2S1P mode, this pin will operate as PP_DATA [2].  RXD_2/ B5/S 48 Serial Port 2 Request To Send (in serial protocol), active low. If AX78140 is configured in 2S1P mode, this pin will operate as PP_DATA [3].  EXT_CLOCK I5/S 50 Input Clock from external world. In normal operation mode, clock can be supplied to serial ports and used for custom BAUD Rate of user's choice. In test mode, clock will be the test clock input from external world.  RI_2_N/ PP_DATA [4] FAX8140 is configured in 2S1P mode, this pin will operate as PP_DATA [4]. This pin can also perform as a SW controlled GPIO.  DSR_2_N/ PD_DATA [4] FAX8140 is configured in 2S1P mode, this pin will operate as PP_DATA [5]. This pin can also perform as a SW controlled GPIO.  DSR_2_N/ B5/S 53 Serial Port 2 Data Set Ready (in serial protocol), active low. If AX78140 is configured in 2S1P mode, this pin will operate as PP_DATA [5]. This pin can also perform as a SW controlled GPIO.  CTS_2_N/ B5/S 54 Serial Port 2 Data Carrier Detect (in serial protocol), active low. If AX78140 is configured in 2S1P mode, this pin will operate as PP_DATA [6].  This pin can also perform as a SW controlled GPIO.  Serial Port 2 Data Carrier Detect (in serial protocol), active low. If AX78140 is configured in |             | 3375    |            |                                                                              |

| This pin is also used to indicate the USB Max. Power configuration while reporting USB device configuration descriptor to USB host. (High = 500mx; Low = 100mA)  If AX78140 is configured in 2S1P mode, this pin will operate as FAULT_n.  RESET 15/S 42 Reset signal. The polarity is determined by RESET_SEL pin.  TXD_2/ B5/S 45 Serial Port 2 Transmit Data out to transceiver, or IrDA data out to IR LED. If AX78140 is configured in 2S1P mode, this pin will operate as PP_DATA [0].  DTR_2_N/ B5/S 46 Serial Port 2 Data Terminal Ready (in serial protocol), active low. If AX78140 is configured in 2S1P mode, this pin will operate as PP_DATA [1]  RTS_2_N/ B5/S 47 Serial Port 2 Request To Send (in serial protocol), active low. If AX78140 is configured in 2S1P mode, this pin will operate as PP_DATA [1].  RTS_2_N/ B5/S 48 Serial Port 2 Request To Send (in serial protocol), active low. If AX78140 is configured in 2S1P mode, this pin will operate as PP_DATA [2].  RXD_2/ B5/S 48 Serial Port 2 Serial Receive Data in from transceiver or IrDA data in from IrDA detector. If AX78140 is configured in 2S1P mode, this pin will operate as PP_DATA [3].  EXT_CLOCK 15/S 50 Input Clock from external world. In normal operation mode, clock can be supplied to serial ports and used for custom BAUD Rate of user's choice. In test mode, clock will be the test clock input from external world. RI_2_N/ B5/S 52 Serial Port 2 Ring Indicator, active low.  If AX78140 is configured in 2S1P mode, this pin will operate as PP_DATA [4]. This pin can also perform as a SW controlled GPIO.  DSR_2_N/ B5/S 53 Serial Port 2 Data Set Ready (in serial protocol), active low. If AX78140 is configured in 2S1P mode, this pin will operate as PP_DATA [5]. This pin can also perform as a SW controlled GPIO.  DCD_2_N/ B5/S 54 Serial Port 2 Data Carrier Detect (in serial protocol), active low. If AX78140 is configured in 2S1P mode, this pin will operate as PP_DATA [6]. This pin can also perform as a SW controlled GPIO.                                                                | 111021_11   |         |            |                                                                              |

| reporting USB device configuration descriptor to USB host. (High = 500mA; Low = 100mA)  If AX78140 is configured in 2S IP mode, this pin will operate as FAULT_n.  RESET 15/S 42 Reset signal. The polarity is determined by RESET_SEL pin.  TXD_2/ PP_DATA [0] Serial Port 2 Transmit Data out to transceiver, or IrDA data out to IR LED. If AX78140 is configured in 2S IP mode, this pin will operate as PP_DATA [1]  DTR_2_N/ B5/S 46 Serial Port 2 Data Terminal Ready (in serial protocol), active low. If AX78140 is configured in 2S IP mode, this pin will operate as PP_DATA [1].  RTS_2_N/ B5/S 47 Serial Port 2 Request To Send (in serial protocol), active low. If AX78140 is configured in 2S IP mode, this pin will operate as PP_DATA [2].  RXD_2/ B5/S 48 Serial Port 2 Serial Receive Data in from transceiver or IrDA data in from IrDA detector.  If AX78140 is configured in 2S IP mode, this pin will operate as PP_DATA [2].  EXT_CLOCK 15/S 50 Input Clock from external world. In normal operation mode, clock can be supplied to serial ports and used for custom BAUD Rate of user's choice. In test mode, clock will be the test clock input from external world.  RI_2_N/ B5/S 52 Serial Port 2 Ring Indicator, active low.  If AX78140 is configured in 2S IP mode, this pin will operate as PP_DATA [4].  This pin can also perform as a SW controlled GPIO.  DSR_2_N/ B5/S 53 Serial Port 2 Data Set Ready (in serial protocol), active low. If AX78140 is configured in 2S IP mode, this pin will operate as PP_DATA [5].  This pin can also perform as a SW controlled GPIO.  DCD_2_N/ B5/S 54 Serial Port 2 Data Carrier Detect (in serial protocol), active low. If AX78140 is configured in 2S IP mode, this pin will operate as PP_DATA [6].  This pin can also perform as a SW controlled GPIO.  CTS_2_N/ B5/S 55 Serial Port 2 Clear To Send (in serial protocol), active low. If AX78140 is configured in 2S IP mode, this pin will operate as PP_DATA [7].                                                                                                                         |             |         |            |                                                                              |

| S00mA; Low = 100mA)   If AX78140 is configured in 2S1P mode, this pin will operate as FAULT_n.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             |         |            |                                                                              |

| If AX78140 is configured in 2S1P mode, this pin will operate as FAULT_n.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |         |            |                                                                              |

| FAULT_n.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |         |            |                                                                              |

| RESET   15/S   42   Reset signal. The polarity is determined by RESET_SEL pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             |         |            | •                                                                            |