# Low-pin-count Non-PCI 8/16-bit 10/100M Fast Ethernet Controller with MII Interface

#### **Features**

- High-performance non-PCI local bus

- Support 8/16-bit local CPU interfaces include MCS-51 series, 80186 series CPU and ISA bus

- SRAM-like host interface (US Patent Approval), easily interfaced to most common embedded MCUs

- Embed 8Kx16 bits SRAM for packet buffers

- Support Slave-DMA to minimize CPU overhead

- Support burst-mode read for highest performance applications

- Interrupt pin with programmable Hold-off timer

- Single-chip Fast Ethernet controller

- Compatible with IEEE802.3, 802.3u standards

- Integrate Fast Ethernet MAC/PHY transceiver in one chip

- Support 10Mbps and 100Mbps data rate

- Support full and half duplex operations

- Support 10/100Mbps N-way Auto-negotiation operation

- Support twisted pair crossover detection and auto-correction (HP Auto-MDIX)

- Support IEEE 802.3x flow control for full-duplex operation

- Support back-pressure flow control for half-duplex operation

- Support VLAN match filter

#### Document No.: AX88196B\_106/01/13/12

- Provide optional MII interface for external 100BASE-FX Ethernet PHY, HomePNA PHY or HomePlug PHY

- Support Wake-on-LAN function by following events to reduce power

- Detection of a change in the network link state

- Receipt of a Magic Packet

- Receipt of a MS wakeup frame

- NE2000 register level compatible instruction

- Detection performance can be enhanced with only a minor host driver modification from original NE2000 driver

- Support EEPROM interface to store MAC address (Optional)

- Support up to 2 (out) /1 (in/out) General Purpose pins

- Support LED pins for various network activity indications

- Integrate voltage regulator and 25MHz crystal oscillator

- 0.18um CMOS process. 3.3V power supply with 5V tolerant I/O pins

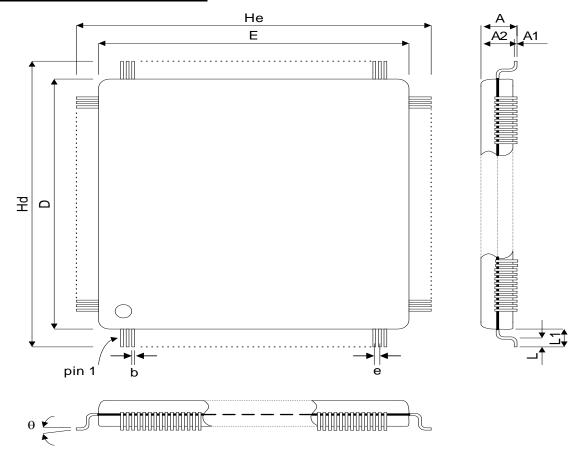

- 100-pin LQFP, RoHS package

- Operate over 0 to +70 °C or -40 to +85 °C temperature range

#### **Product description**

The AX88196B is a non-PCI Ethernet controller with MII for the Embedded Ethernet applications. The AX88196B supports 8/16-bit SRAM-like host interface, providing a glue-less connection to most common embedded MCUs. The AX88196B integrates on-chip Fast Ethernet MAC and PHY, which is IEEE802.3 10Base-T and IEEE802.3u 100Base-TX compatible, and 8Kx16 bits embedded SRAM for packet buffering to accommodate high bandwidth applications. The AX88196B has a wide array of features including support for Twisted Pair Crossover Detection and Auto-Correction, Wake-on-LAN power management, and IEEE 802.3x and back-pressure flow control. The programming of AX88196B is simple and compatible with NE2000, so the users don't need any modification and can easily port the software drivers to many embedded systems very quickly. Combining these features with ASIX's free TCP/IP software stack for 8-bit microcontrollers, AX88196B provides the best Ethernet solution for embedded networking applications.

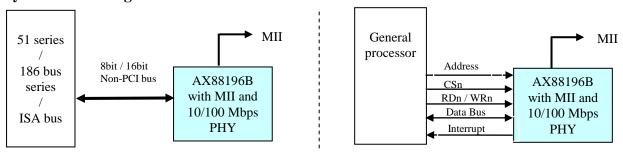

#### **System Block Diagram**

Release Date: 01/13/2012

Copyright © 2006-2012 ASIX Electronics Corporation. All rights reserved.

#### **DISCLAIMER**

No part of this document may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, for any purpose, without the express written permission of ASIX. ASIX may make changes to the product specifications and descriptions in this document at any time, without notice.

ASIX provides this document "as is" without warranty of any kind, either expressed or implied, including without limitation warranties of merchantability, fitness for a particular purpose, and non-infringement.

Designers must not rely on the absence or characteristics of any features or registers marked "reserved", "undefined" or "NC". ASIX reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. Always contact ASIX to get the latest document before starting a design of ASIX products.

#### **TRADEMARKS**

ASIX, the ASIX logo are registered trademarks of ASIX Electronics Corporation. All other trademarks are the property of their respective owners.

## **Table of Contents**

| 1.0 INTRODUCTION                                                                 | 7  |

|----------------------------------------------------------------------------------|----|

| 1.1 GENERAL DESCRIPTION:                                                         | 7  |

| 1.2 AX88196B Block Diagram:                                                      |    |

| 1.3 AX88196B PIN CONNECTION DIAGRAM                                              |    |

| 2.0 SIGNAL DESCRIPTION                                                           | 9  |

|                                                                                  |    |

| 2.1 LOCAL CPU BUS INTERFACE SIGNALS GROUP                                        |    |

| 2.2 10/100MBPS TWISTED-PAIR INTERFACE PINS GROUP                                 |    |

| 2.3 BUILT-IN PHY LED INDICATOR PINS GROUP                                        |    |

| 2.4 EEPROWI SIGNALS GROUP  2.5 MISCELLANEOUS PINS GROUP                          |    |

| 2.6 MII PINS GROUP                                                               |    |

| 3.0 MEMORY AND CSR MAPPING                                                       |    |

|                                                                                  |    |

| 3.1 EEPROM MEMORY MAPPING                                                        |    |

| 3.2 CSR MAPPING                                                                  |    |

| 3.3 Internal SRAM Memory Mapping                                                 |    |

| 4.0 BASIC OPERATION                                                              | 16 |

| 4.1 Receiver Filtering                                                           | 16 |

| 4.1.1 Unicast Address Match Filter                                               | 16 |

| 4.1.2 Multicast Address Match Filter                                             | 16 |

| 4.1.3 Broadcast Address Match Filter                                             |    |

| 4.1.4 VLAN Match Filter                                                          |    |

| 4.1.5 Aggregate Address Filter with Receive Configuration Setup                  |    |

| 4.2 Buffer Management Operation                                                  |    |

| 4.2.1 Packet Reception                                                           |    |

| 4.2.2 Packet Transmission                                                        |    |

| 4.2.3 Filling Packet to Transmit Buffer (Host fill data to memory)               |    |

| 4.2.4 Removing Packets from the Ring (Host read data from memory)                |    |

| 4.2.5 Other Useful Operations                                                    |    |

| 4.3 Wake-up Detection                                                            |    |

| 4.3.1 Wake-up frame                                                              |    |

| 4.3.2 Magic Packet frame                                                         |    |

| 4.4 FLOW CONTROL                                                                 |    |

| 4.4.1 Full-Duplex Flow Control                                                   |    |

| 4.4.2 Half-Duplex Flow Control                                                   |    |

| 4.5 BIG- AND LITTLE-ENDIAN SUPPORT                                               |    |

| 4.7 EEPROM Interface                                                             |    |

| 4.8 POWER MANAGEMENT                                                             |    |

| 4.8.1 Power Management Event Indicators                                          |    |

| 4.9 DEVICE READY OR BUSY                                                         |    |

| 5.0 REGISTERS OPERATION                                                          |    |

|                                                                                  |    |

| 5.1 MAC CONTROL AND STATUS REGISTERS (CSR)                                       |    |

| 5.1.1 Command Register (CR)                                                      |    |

| 5.1.2 Rx Page Start Register (PSTART)                                            |    |

| 5.1.3 Rx Page Stop Register (PSTOP)<br>5.1.4 Boundary Pointer (BNRY)             |    |

| 5.1.4 Boundary Pointer (BNR1)                                                    |    |

| 5.1.5 Transmit Page Start Address (TPSR)<br>5.1.6 Transmit Status Register (TSR) |    |

| 5.1.0 Transmit Status Register (TSR)                                             |    |

| 5.1.8 Number Of Collisions Register (NCR)                                        |    |

| 5.1.9 Transmit Byte Count Register (TBCR1)                                       |    |

| 5.1.10 Current Page Register (CPR)                                               |    |

|                                                                                  |    |

| 5.1.11 Interrupt Status Register (ISR)               | 41 |

|------------------------------------------------------|----|

| 5.1.12 Remote Start Address Register (RSAR0)         | 42 |

| 5.1.13 Remote Start Address Register (RSAR1)         | 42 |

| 5.1.14 Remote Byte Count Register (RBCR0)            |    |

| 5.1.15 Remote Byte Count Register (RBCR1)            |    |

| 5.1.16 Current Remote DMA Address (CRDA0)            |    |

| 5.1.17 Current Remote DMA Address (CRDA1)            |    |

| 5.1.18 Receive Configuration Register (RCR)          |    |

| 5.1.19 Receive Status Register (RSR)                 |    |

| 5.1.20 Transmit Configuration Register (TCR)         | 44 |

| 5.1.21 Frame Alignment Error Tally Register (CNTR0)  | 44 |

| 5.1.22 Data Configuration Register (DCR)             |    |

| 5.1.23 CRC Error Tally Register (CNTR1)              | 11 |

| 5.1.24 Interrupt mask register (IMR)                 | 45 |

| 5.1.25 Frames Lost Tally Register (CNTR2)            | 75 |

| 5.1.26 Physical Address Register 0 (PAR0)            | 45 |

| 5.1.27 Physical Address Register 1 (PAR1)            |    |

| 5.1.28 Physical Address Register 2 (PAR2)            |    |

|                                                      |    |

| 5.1.29 Physical Address Register 3 (PAR3)            | 40 |

| 5.1.30 Physical Address Register 4 (PAR4)            | 40 |

| 5.1.31 Physical Address Register 5 (PAR5)            |    |

| 5.1.32 Current Page Register (CPR)                   |    |

| 5.1.33 Multicast Address Register 0 (MAR0)           |    |

| 5.1.34 Multicast Address Register 1 (MAR1)           |    |

| 5.1.35 Multicast Address Register 2 (MAR2)           | 47 |

| 5.1.36 Multicast Address Register 3 (MAR3)           |    |

| 5.1.37 Multicast Address Register 4 (MAR4)           |    |

| 5.1.38 Multicast Address Register 5 (MAR5)           |    |

| 5.1.39 Multicast Address Register 6 (MAR6)           |    |

| 5.1.40 Multicast Address Register 7 (MAR7)           |    |

| 5.1.41 Total Receive Buffer Free Page Register (TFP) | 48 |

| 5.1.42 Receive Configuration Register (RCR)          |    |

| 5.1.43 Transmit Configuration Register (TCR)         |    |

| 5.1.44 Data Configuration Register (DCR)             | 48 |

| 5.1.45 Interrupt Mask Register (IMR)                 | 48 |

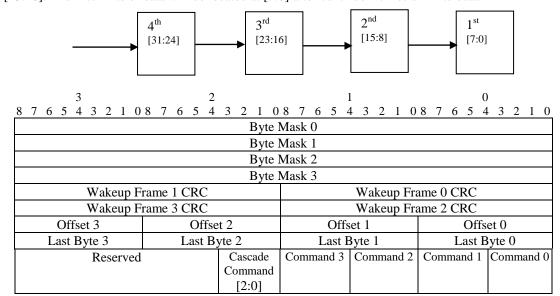

| 5.1.46 Wakeup Frame Byte Mask (WFBM0)                |    |

| 5.1.47 Wakeup Frame Byte Mask (WFBM1)                | 49 |

| 5.1.48 Wakeup Frame Byte Mask (WFBM2)                |    |

| 5.1.49 Wakeup Frame Byte Mask (WFBM3)                |    |

| 5.1.50 Wakeup Frame 1,0 CRC (WF10CRC)                |    |

| 5.1.51 Wakeup Frame 3,2 CRC (WF32CRC)                |    |

| 5.1.52 Wakeup Frame Offset (WFOFST)                  |    |

| 5.1.53 Wakeup Frame Last Byte (WFLB)                 |    |

| 5.1.54 Wakeup Frame Command (WFCMD)                  |    |

| 5.1.55 Wakeup Control and Status Register (WUCSR)    |    |

| 5.1.56 Power Management Register (PMR)               |    |

| 5.1.57 Reload EEPROM Register (REER)                 |    |

| 5.1.58 Misc. Control Register (MISC)                 |    |

| 5.1.59 General Purpose Timer0 Register (GPT0)        |    |

| 5.1.60 General Purpose Timero Register (GPT1)        |    |

| 5.1.61 Data Port (DP)                                |    |

| 5.1.62 Inter-frame gap Segment 1(IFGS1)              |    |

|                                                      |    |

| 5.1.63 Inter-frame gap Segment 2(IFGS2)              |    |

| 5.1.64 MII/EEPROM Management Register (MEMR)         |    |

| 5.1.65 I/O Buffer Type Configure Register (BTCR)     |    |

| 5.1.66 Inter-frame gap (IFG)                         |    |

| 5.1.67 Back-pressure Jam Limit Count (BJLC)          |    |

| 5.1.68 Device Status Register (DSR)                  |    |

| 5.1.69 MAX Frame Size Register (MFSR0)               |    |

| 5.1.70 MAX Frame Size Register (MFSR1)               | 55 |

## **AX88196BLF**

| 5.1.71 Flow Control Register (FCR)                                                                                          |    |

|-----------------------------------------------------------------------------------------------------------------------------|----|

| 5.1.72 MAC Configure Register (MCR)                                                                                         |    |

| 5.1.73 VLAN ID 0 Register (VIDR0)                                                                                           |    |

| 5.1.74 Current TX End Page Register (CTEPR)                                                                                 |    |

| 5.1.75 VLAN ID 1 Register (VIDR1)                                                                                           |    |

| 5.1.76 Big-Endian Register (BER)                                                                                            |    |

| 5.1.77 Host Wake Up Register (HWUR)                                                                                         |    |

| 5.1.78 Software Reset                                                                                                       |    |

| 5.2 THE EMBEDDED PHY REGISTERS                                                                                              |    |

| 5.2.1 MRO Control Register Bit Descriptions                                                                                 |    |

| 5.2.2 MR1 Status Register Bit Descriptions                                                                                  |    |

| 5.2.3 MR2 Identification 1 Registers                                                                                        |    |

| 5.2.3 MR3 – Identification 2 Registers                                                                                      |    |

| 5.2.4 MR4 – Autonegotiation Advertisement Register<br>5.2.5 MR5 – Autonegotiation Link Partner Ability (Base Page) Register |    |

| 5.2.5 MR5 – Autonegotiation Link Further Ability (Base Fage) Register                                                       |    |

| • •                                                                                                                         |    |

| 6.0 CPU READ AND WRITE FUNCTIONS                                                                                            |    |

| 6.1 ISA BUS TYPE ACCESS FUNCTIONS.                                                                                          |    |

| 6.2 80186 CPU BUS TYPE ACCESS FUNCTIONS.                                                                                    |    |

| 6.3 MCS-51 CPU BUS TYPE ACCESS FUNCTIONS.                                                                                   |    |

| 6.5 CPU ACCESS MII SERIAL MANAGEMENT INTERFACE                                                                              | 66 |

| 7.0 ELECTRICAL SPECIFICATION AND TIMINGS                                                                                    | 67 |

| 7.1 Absolute Maximum Ratings                                                                                                | 67 |

| 7.2 GENERAL OPERATION CONDITIONS                                                                                            |    |

| 7.3 DC CHARACTERISTICS                                                                                                      |    |

| 7.3.1 DC Characteristics of 3.3V with 5V Tolerance                                                                          | 67 |

| 7.3.2 Power Consumption                                                                                                     |    |

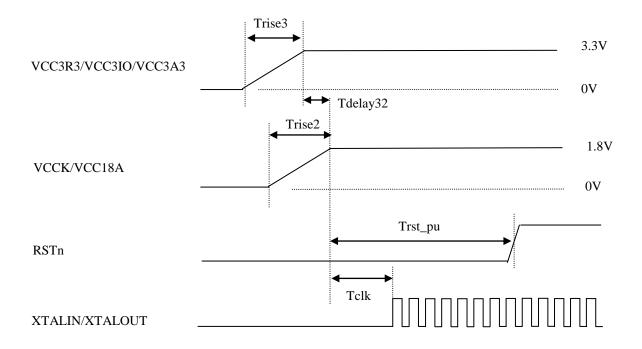

| 7.3.3 Power-up Sequence                                                                                                     |    |

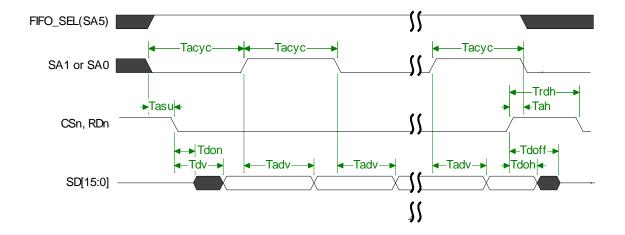

| 7.4 AC TIMING CHARACTERISTICS                                                                                               | 71 |

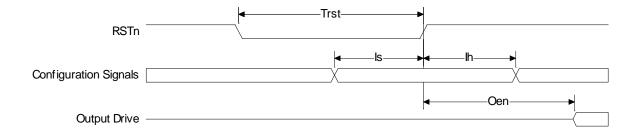

| 7.4.1 Reset Timing                                                                                                          | 71 |

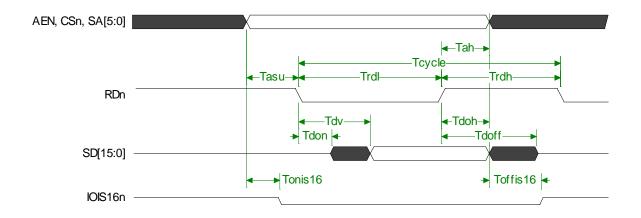

| 7.4.2 ISA Bus Access Timing                                                                                                 | 72 |

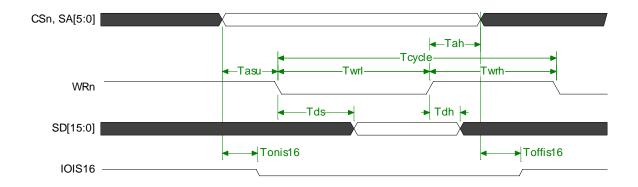

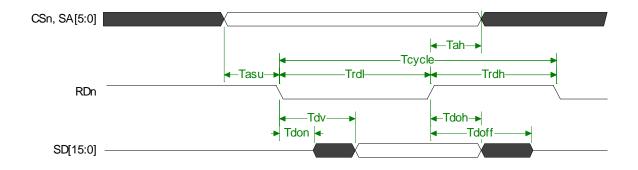

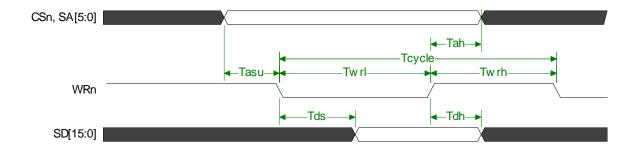

| 7.4.3 80186 Type I/O Access Timing                                                                                          | 74 |

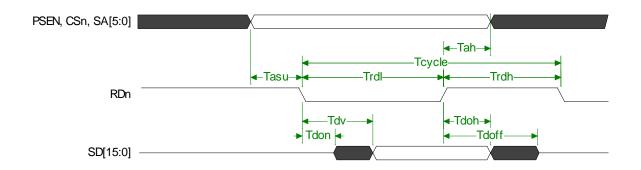

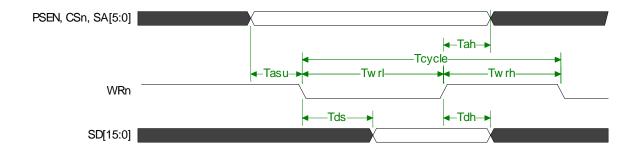

| 7.4.4 8051 Bus Access Timing                                                                                                |    |

| 7.4.5 Burst Reads Access Timing                                                                                             |    |

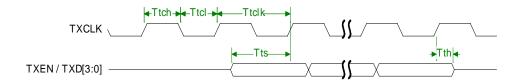

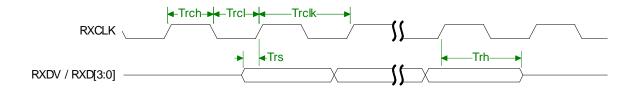

| 7.4.6 MII Timing                                                                                                            | 79 |

| 8.0 PACKAGE INFORMATION                                                                                                     | 80 |

| 9.0 ORDERING INFORMATION                                                                                                    | 81 |

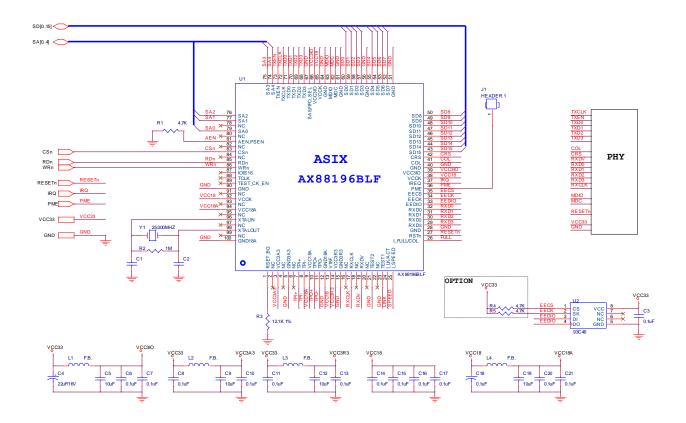

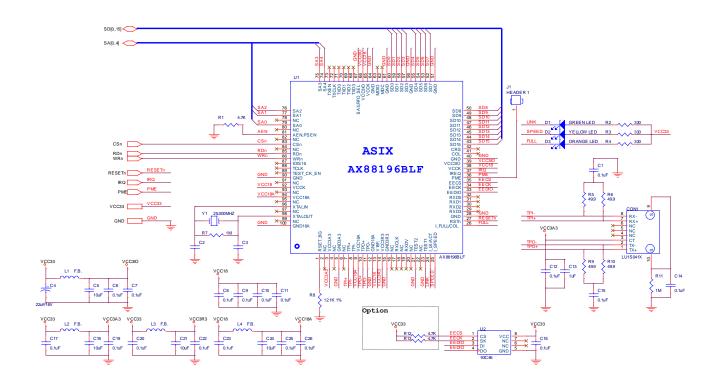

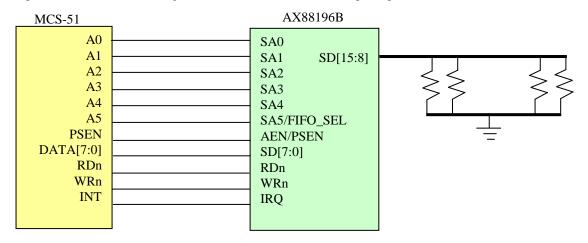

| APPENDIX A1: MCS51-LIKE (8-BIT)                                                                                             | 82 |

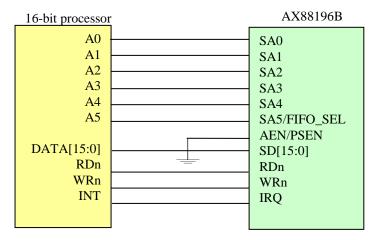

| APPENDIX A2: ISA-LIKE (8/16-BIT)                                                                                            | 83 |

| APPENDIX A3: 186-LIKE (16-BIT)                                                                                              | 94 |

|                                                                                                                             |    |

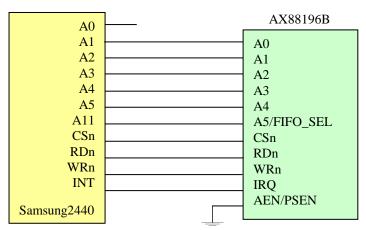

| APPENDIX A4: CO-WORK WITH 32-BIT PROCESSOR                                                                                  |    |

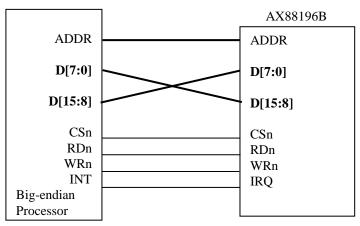

| APPENDIX A5: BIG-ENDIAN PROCESSOR OF DATA BYTE LANDS                                                                        | 87 |

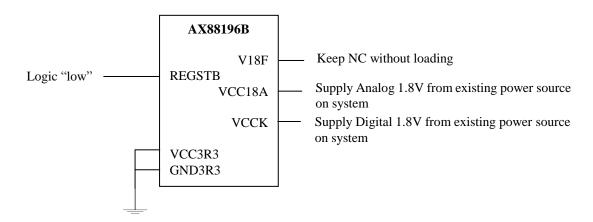

| APPENDIX B: DISABLE AX88196B VOLTAGE REGULATOR                                                                              | 88 |

| REVERSION HISTORY                                                                                                           | 89 |

## **List of Figures**

| FIG - 1 AX88196B BLOCK DIAGRAM                        | 7  |

|-------------------------------------------------------|----|

| FIG - 2 AX88196B PIN OUT DIAGRAM                      |    |

| FIG - 3 INTERNAL SRAM MAP                             | 15 |

| Fig - 4 Receive Buffer Ring.                          | 19 |

| Fig - 5 Receive Buffer Ring At Initialization         | 20 |

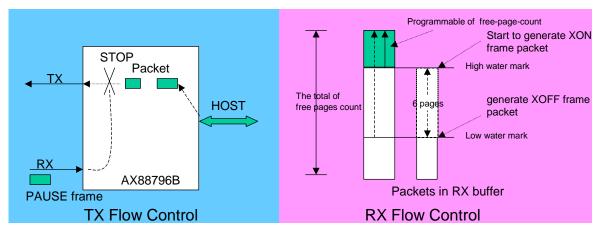

| FIG - 6 TX / RX FLOW CONTROL                          | 30 |

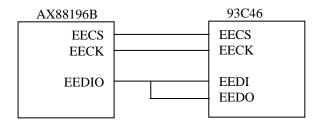

| Fig - 7 EEPROM CONNECTIONS                            | 32 |

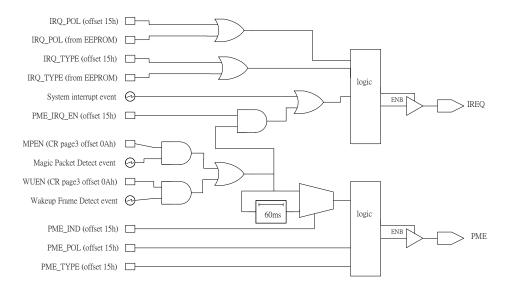

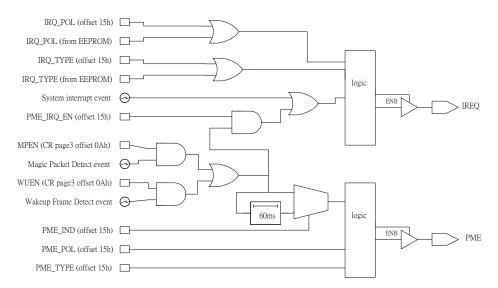

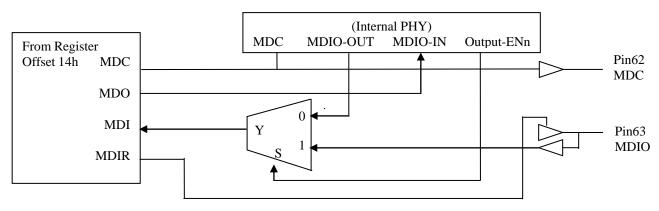

| FIG - 8 PME AND IRQ SIGNAL GENERATION                 | 33 |

| Fig - 9 SMI connections                               |    |

|                                                       |    |

| List of Tables                                        |    |

| TAB - 1 LOCAL CPU BUS INTERFACE SIGNALS GROUP         |    |

| Tab - 2 10/100Mbps Twisted-Pair Interfaces pins group |    |

| TAB - 3 BUILT-IN PHY LED INDICATOR PINS GROUP         | 10 |

| TAB - 4 EEPROM BUS INTERFACE SIGNALS GROUP            |    |

| TAB - 5 MISCELLANEOUS PINS GROUP                      |    |

| TAB - 6 MII PINS GROUP                                |    |

| Tab - 7 EEPROM data format example                    |    |

| TAB - 8 CSR Address Mapping                           |    |

| TAB - 9 LOCAL MEMORY MAPPING                          |    |

| Tab - 10 Internal SRAM Map 00H ~ 1FH                  |    |

| Tab - 11 Internal SRAM Map 0400H ~ 040FH              |    |

| TAB - 12 BYTE LANE MAPPING                            |    |

| TAB - 13 POWER MANAGEMENT STATUSES                    |    |

| TAB - 14 PAGE 0 OF MAC CORE REGISTERS MAPPING         | 35 |

| TAB - 15 PAGE 1 OF MAC CORE REGISTERS MAPPING         |    |

| TAB - 16 PAGE 2 OF MAC CORE REGISTERS MAPPING         |    |

| TAB - 17 PAGE 3 OF MAC CORE REGISTERS MAPPING         | 38 |

| Tab - 18 The Embedded PHY Registers                   | 58 |

| TAB - 19 SMI MANAGEMENT FRAME FORMAT                  | 66 |

### 1.0 Introduction

## 1.1 General Description:

The AX88196B provides industrial standard NE2000 registers level compatible instruction set. Various drivers are easily acquired, maintained and no much additional effort is required. Software is easily port to various embedded systems with no pain and tears. AX88196B also provides transmit queuing function to enhance standard NE2000 of transmitting performance. Please contact ASIX Sales (Sales@asix.com.tw) to get the AX88x96B Software Programming Guide for more details of AX88196B driver implementation.

The AX88196B Fast Ethernet Controller is a high performance and highly integrated local CPU bus Ethernet Controller with embedded 10/100Mbps PHY/Transceiver and 8K\*16 bit SRAM. The AX88196B supports both 8/16-bit local CPU interfaces including MCS-51 series, 80186 series, ISA bus and high-performance SRAM-like interface. The simple host interface provides a glue-less connection to most common microprocessors and microcontrollers. The AX88196B implements both 10Mbps and 100Mbps Ethernet function based on IEEE802.3 / IEEE802.3u LAN standard. The AX88196B provides optional MII interface for external 100BASE-FX Ethernet PHY, HomePNA PHY or HomePlug PHY

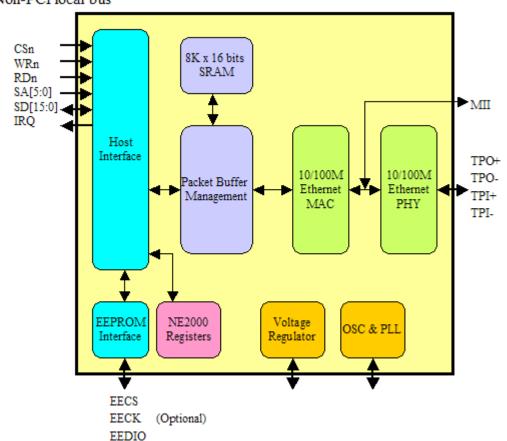

## 1.2 AX88196B Block Diagram:

8/16-bit SRAM-like Non-PCI local bus

Fig - 1 AX88196B Block Diagram

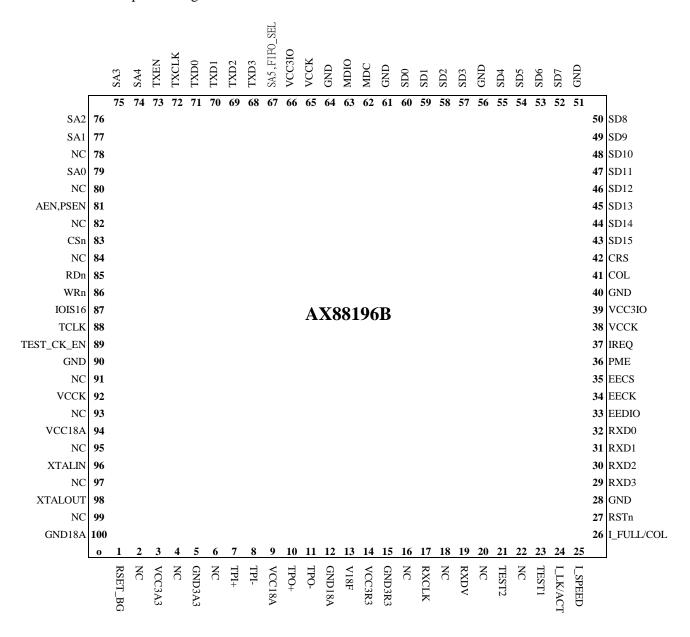

## 1.3 AX88196B Pin Connection Diagram

The AX88196B is housed in the 100-pin LQFP package. 錯誤! 找不到參照來源。 shows the AX88196B pinout diagram.

Fig - 2 AX88196B Pin Out Diagram

## 2.0 Signal Description

The following abbreviations are used in AX88196B pinout tables: All pin names with the "n" suffix are low-active signals.

Input 1.8V Ι 8mA driving strength  $\mathbf{o}$ Output 1.8V S Schmitt trigger  $\mathbf{PU}$ **I5 Input 3.3V with 5V tolerant** Internal Pull Up 75Kohm Output 3.3V with 5V tolerant Internal Pull Down 75kohm **O5** PD **T5**

T5 Tri-state with 5V tolerant P Power Pin

B5 Bi-directional I/O, 3.3V with 5V tolerant A Analog

4m 4mA driving strength

## 2.1 Local CPU Bus Interface Signals Group

| Signal      | Type     | Pin No.                 | Description                                                          |

|-------------|----------|-------------------------|----------------------------------------------------------------------|

| SA[4:0]     | I5       | 74, 75, 76, 77, 79      | System Address: Signals SA[4:0] are address bus input lines.         |

|             |          |                         | Used to select internal CSR's.                                       |

| SA[5] or    | I5/PD    | 67                      | System Address or FIFO Select: When driven high, all accesses to     |

| FIFO_SEL    |          |                         | the AX88196B are to the RX or TX data buffer FIFO (DP).              |

|             |          |                         | AX88196B supports two kinds of Data Port for                         |

|             |          |                         | receiving/transmitting packets from/to AX88196B. One is the          |

|             |          |                         | PIO Data Port (offset 10h); the other one is the SRAM-like Data      |

|             |          |                         | Port (e.g. offset 800h ~ FFFh for Samsung2440 processor as           |

|             |          |                         | described in Appendix A4 of AX88196B datasheet). The                 |

|             |          |                         | SRAM-like Data Port address range depends on which address           |

|             |          |                         | line of host processor is being connected to the address line        |

|             |          |                         | SA5/FIFO_SEL of AX88196B.                                            |

|             |          |                         | Software on host CPU can issue Single Data Read/Write                |

|             |          |                         | command to both PIO Data Port and SRAM-like Data Port.               |

|             |          |                         | However, to use Burst Data Read/Write commands, one has to use       |

|             |          |                         | SRAM-like Data Port, which requires SA5/FIFO_SEL (pin 45) of         |

|             |          |                         | AX88196B connecting to an upper address line of host CPU. Our        |

|             |          |                         | reference schematic has SA5/FIFO_SEL pin connected to upper          |

|             |          |                         | address line for supporting Burst Data Read/Write commands.          |

| SD[15:0]    | B5/8m    |                         | System Data Bus: Signals SD[15:0] constitute the bi-directional      |

|             |          | 49, 50, 52, 53, 54, 55, | data bus.                                                            |

|             |          | 57, 58, 59, 60          |                                                                      |

| IRQ         | O5/T5/8m | 37                      | Programmable Interrupt request. Programmable polarity, source        |

|             |          |                         | and buffer types.                                                    |

|             |          |                         | Can be configure by EEPROM auto-loader or BTCR (offset 15h)          |

| CSn         | I5       | 83                      | Chip Select: Active low.                                             |

| RDn         | I5       | 85                      | Read: Active low strobe to indicate a read cycle.                    |

| WRn         | I5       | 86                      | Write: Active low strobe to indicate a write cycle. This signal also |

|             |          |                         | used to wakeup the AX88196B when it is in reduced power state.       |

| IOIS16n     | T5/8m    | 87                      | 16 Bit Port: For ISA bus used. The IOIS16n is asserted when the      |

|             |          |                         | address at the range corresponds to an I/O address to which the      |

|             |          |                         | chip responds, and the I/O port addressed is capable of 16-bit       |

|             | _        | _                       | access.                                                              |

| AEN or PSEN | I5       | 81                      | Address Enable: When 186, ISA mode, this signal is active low to     |

|             |          |                         | access AX88196B.                                                     |

|             |          |                         | PSEN: When 51 modes, this signal is active high to access            |

|             |          |                         | AX88196B.                                                            |

| PME | O5/T5/8m | 36 | Wakeup Indicator: When programmed to do so, is asserted when        |

|-----|----------|----|---------------------------------------------------------------------|

|     |          |    | the AX88196B detects a wake event and is requesting the system      |

|     |          |    | to wake up from the D1 sleep state. The polarity and buffer type of |

|     |          |    | this signal is programmable by BTCR (offset 15h)                    |

Tab - 1 Local CPU bus interface signals group

## 2.2 10/100Mbps Twisted-Pair Interface pins group

| Signal  | Type | Pin No.                                | Pin No. Description                                            |  |

|---------|------|----------------------------------------|----------------------------------------------------------------|--|

| TPI+    | AB   | 7 Twisted Pair Receive Input, Positive |                                                                |  |

| TPI-    | AB   | 8                                      | Twisted Pair Receive Input, Negative                           |  |

| TPO+    | AB   | 10                                     | Twisted Pair Transmit Output, Positive                         |  |

| TPO-    | AB   | 11                                     | Twisted Pair Transmit Output, Negative                         |  |

| RSET_BG | AO   | 1                                      | Off-chip resister. Must be connected 12.1K ohm ± 1% to ground. |  |

Tab - 2 10/100Mbps Twisted-Pair Interfaces pins group

## 2.3 Built-in PHY LED indicator pins group

| Signal     | Type  | Pin No. | Description                                                                   |

|------------|-------|---------|-------------------------------------------------------------------------------|

| I_FULL/COL | O5/8m | 26      | Full-Duplex/Collision Status. If this signal is low, it indicates             |

|            |       |         | full-duplex link established, and if it is high, then the link is in          |

|            |       |         | half-duplex mode. When in half-duplex and collision occurrence, the           |

|            |       |         | output will be driven low for 80ms and driven high at minimum 80ms.           |

| I_SPEED    | O5/8m | 25      | Speed Status: If this signal is low, it indicates 100Mbps, and if it is high, |

|            |       |         | then the speed is 10Mbps.                                                     |

| I_LK/ACT   | O5/8m | 24      | Link Status/Active: If this signal is low, it indicates link, and if it is    |

|            |       |         | high, then the link is fail. When in link status and line activity            |

|            |       |         | occurrence, this signal is pulsed high (LED off) for 80ms whenever            |

|            |       |         | transmit or receive activity is detected. This signal is then driven low      |

|            |       |         | again for a minimum of 80ms, after which time it will repeat the process      |

|            |       |         | if TX or RX activity is detected.                                             |

Tab - 3 Built-in PHY LED indicator pins group

## 2.4 EEPROM Signals Group

| Signal | Type     | Pin No. | Description                                                   |                                                     |                                                 |  |

|--------|----------|---------|---------------------------------------------------------------|-----------------------------------------------------|-------------------------------------------------|--|

| EECS   | B5/4m/PD | 35      | EEPROM                                                        | EEPROM Chip Select: EEPROM chip select signal.      |                                                 |  |

| EECK   | B5/4m/PD | 34      | EEPROM                                                        | EEPROM Clock: Signal connected to EEPROM clock pin. |                                                 |  |

|        |          |         | EECS, EI                                                      | ECK can load                                        | d BUS type setting during power on reset cycle. |  |

|        |          |         |                                                               |                                                     |                                                 |  |

|        |          |         | EECS                                                          | EECK                                                | BUS TYPE                                        |  |

|        |          |         | 0                                                             | 0                                                   | ISA BUS / SRAM-Like                             |  |

|        |          |         | 0                                                             | 1                                                   | 80186                                           |  |

|        |          |         | 1                                                             | 0                                                   | Reserved                                        |  |

|        |          |         | 1                                                             | 1                                                   | MCS-51 (805X)                                   |  |

| EEDIO  | B5/4m/PU | 33      | EEPROM Data In/Out: Signal connected to EEPROM data input and |                                                     |                                                 |  |

|        |          |         | data outp                                                     | ut pin.                                             | -                                               |  |

Tab - 4 EEPROM bus interface signals group

## 2.5 Miscellaneous pins group

| Signal     | Type         | Pin No.          | Description                                                                    |  |

|------------|--------------|------------------|--------------------------------------------------------------------------------|--|

| XTALIN     | I            | 96               | CMOS Local Clock: A 25Mhz clock, +/-50 PPM, 40%-60% duty                       |  |

|            |              |                  | cycle. Note that the pin does not support 3.3V or 5V voltage supply.           |  |

|            |              |                  | Crystal Oscillator Input: A 25Mhz crystal, +/-50 PPM can be                    |  |

|            |              |                  | connected across XTALIN and XTALOUT.                                           |  |

| XTALOUT    | O            | 98               | Crystal Oscillator Output: A 25Mhz crystal, +/-50 PPM can be                   |  |

|            |              |                  | connected across XTALIN and XTALOUT. If a single-ended external                |  |

|            |              |                  | clock (LCLK) is connected to XTALIN, the crystal output pin should             |  |

|            | <del> </del> |                  | be left floating.                                                              |  |

| RSTn       | I5/S         | 27               | Reset:                                                                         |  |

|            |              |                  | Reset is active low then place AX88196B into reset mode. During the            |  |

|            |              |                  | rising edge the AX88196B loads the power on setting data.                      |  |

| TCLK       | I5/PD        | 88               | Test Clock Pins: As a clock input for ASIC testing only                        |  |

|            | <del></del>  |                  | No connection when normal operation                                            |  |

| TEST_CK_EN | I5/PD/S      | 89               | Enable TCLK in to ASIC as a main clock for test only.                          |  |

|            |              |                  | No connection when normal operation                                            |  |

| TEST2      | I5/S         | 21               | TEST mode select                                                               |  |

|            |              |                  | Connect to ground when normal operation                                        |  |

| TEST1      | I5/S         | 23               | TEST mode select                                                               |  |

| TYCCO A O  |              | 2                | Connect to ground when normal operation                                        |  |

| VCC3A3     | P            | 3                | Power Supply for Analog Circuit: +3.3V DC.                                     |  |

| GND3A3     | P            | 5                | Power Supply for Analog Circuit: +0V DC or Ground Power.                       |  |

| VCC18A     | P            | 9, 94            | Analog power for oscillator, PLL, and Ethernet PHY differential I/O pins, 1.8V |  |

| GND18A     | P            | 12, 100          | Analog ground for oscillator, PLL, and Ethernet PHY differential I/O           |  |

|            | <u> </u>     |                  | pins.                                                                          |  |

| V18F       | P            | 13               | On-chip 3.3V to 1.8V Regulator output +1.8V DC.                                |  |

| VCC3R3     | P            | 14               | On-chip 3.3V to 1.8V Regulator power supply: +3.3V DC.                         |  |

| GND3R3     | P            | 15               | On-chip 3.3V to 1.8V Regulator ground.                                         |  |

| GND        | P            | 28, 40, 51, 56,  | Ground.                                                                        |  |

|            | <u> </u>     | 61, 64, 90       |                                                                                |  |

| VCC3IO     | P            | 39, 66           | Power Supply for IO: +3.3V DC.                                                 |  |

| VCCK       | P            |                  | Power Supply for core logic: +1.8V DC.                                         |  |

| NC         |              | 2, 4, 6, 16, 18, | No connection                                                                  |  |

|            |              | 20, 22, 78, 80,  |                                                                                |  |

|            |              | 82, 84, 91, 93,  |                                                                                |  |

|            |              | 95, 97, 99       |                                                                                |  |

Tab - 5 miscellaneous pins group

## 2.6 MII pins group

| Signal   | Type  | Pin No.        | Description                                                            |  |

|----------|-------|----------------|------------------------------------------------------------------------|--|

| TXCLK    | I/PD  | 72             | Transmit Clock: TXCLK is a continuous clock from PHY. It provides      |  |

|          |       |                | the timing reference for the transfer of the TXEN and TXD[3:0] signals |  |

|          |       |                | from the MII port to the PHY.                                          |  |

| TXEN     | O5/8m | 73             | Transmit Enable: TXEN is transition synchronously with respect to the  |  |

|          |       |                | rising edge of TXCLK. TXEN indicates that the port is presenting       |  |

|          |       |                | nibbles on TXD [3:0] for transmission.                                 |  |

| TXD[3:0] | O5/8m | 68, 69, 70, 71 | Transmit Data: TXD[3:0] is transition synchronously with respect to    |  |

|          |       |                | the rising edge of TXCLK. For each TXCLK period in which TXEN is       |  |

|          |       |                | asserted, TXD[3:0] are accepted for transmission by the PHY.           |  |

| COL      | I/PD  | 41             | Collision: this signal is driven by PHY when collision is detected.    |  |

| CRS      | I/PD  | 42             | Carrier Sense: Asynchronous signal CRS is asserted by the PHY when     |  |

|          |       |                | either transmit or receive medium is non-idle.                         |  |

| RXCLK    | I/PD  | 17             | Receive Clock: RXCLK is a continuous clock that provides the timing    |  |

|          |       |                | reference for the transfer of the RXDV and RXD[3:0] signals from the   |  |

|          |       |                | PHY to the MII port.                                                   |  |

| RXDV     | I/PD  | 19             | Receive Data Valid: RXDV is driven by the PHY synchronously with       |  |

|          |       |                | respect to RXCLK. Asserted high when valid data is present on RXD      |  |

|          |       |                | [3:0].                                                                 |  |

| RXD[3:0] | I/PD  | 29, 30, 31, 32 | Receive Data: RXD[3:0] is driven by the PHY synchronously with         |  |

|          |       |                | respect to RXCLK.                                                      |  |

| MDC      | O5/8m | 62             | Station Management Data Clock: The timing reference for MDIO. All      |  |

|          |       |                | data transfers on MDIO are synchronized to the rising edge of this     |  |

|          |       |                | clock.                                                                 |  |

| MDIO     | B5/PU | 63             | Station Management Data Input/Output: Serial data input/output         |  |

|          |       |                | transfers from/to the PHYs.                                            |  |

Tab - 6 MII pins group

## 3.0 Memory and CSR Mapping

- 1. EEPROM Memory Mapping

- 2. CSR Mapping

- 3. Local Memory Mapping

## 3.1 EEPROM Memory Mapping

EEPROM interface can access via CSR offset 14h SMI/EEPROM registers when auto load operation completed. The content of EEPROM data will be auto-loaded to internal memory from 0000h to 001Fh and from 0400h to 040Fh automatically when hardware reset. It is similar to NE2000 PROM store Ethernet address. The real MAC address must configured by PAR0  $\sim$  PAR5 (CR page1 offset1  $\sim$  offset6). The auto-loader only write to internal SRAM not write to PAR0  $\sim$  PAR5. An example as below, if the desired Ethernet physical address is 10-32-54-76-98-BA It is a programmed EEPROM if auto-load value is 5AA5h from EEPROM address 0h. After hardware reset the EEPROM loader will read first word and check pattern 5AA5h. If the first word value not equal to 5AA5h then the EEPROM loader proclaimed that no external EEPROM or external EEPROM is a non-programmed EEPROM.

| Addr | Bits    | D[15:8]    | D[7:0]       | Description                                                                                                                                                                                                                                              |                                                                                    |  |

|------|---------|------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|--|

| 5h   | [15:0]  | BAh        | 98h          | MAC address 6 <sup>th</sup> , 5 <sup>th</sup>                                                                                                                                                                                                            |                                                                                    |  |

| 4h   | [15:0]  | 76h        | 54h          | MAC address 4 <sup>th</sup> , 3 <sup>rd</sup>                                                                                                                                                                                                            |                                                                                    |  |

| 3h   | [15:0]  | 32h        | 10h          | MAC addr                                                                                                                                                                                                                                                 | ress 2 <sup>nd</sup> , 1 <sup>st</sup> (multicast bit is 1 <sup>st</sup> of bit_0) |  |

| 2h   | [15:11] | No define  |              | Always zer                                                                                                                                                                                                                                               |                                                                                    |  |

|      | [10:8]  | PHY_CONFIG |              | Configure internal PHY in different ways, such as 10BASE_half-duplex mode. If EEPROM auto loader not found 5AA51 pattern in first word then internal PHY will be not been manu configuration. (Default is Auto-negotiation enable with all capabilities) |                                                                                    |  |

|      |         |            |              | [10:8]                                                                                                                                                                                                                                                   | Function                                                                           |  |

|      |         |            |              |                                                                                                                                                                                                                                                          | Auto-negotiation enable with all capabilities                                      |  |

|      |         |            |              |                                                                                                                                                                                                                                                          | Auto-negotiation with 100BASE-TX FDX / HDX ability                                 |  |

|      |         |            |              |                                                                                                                                                                                                                                                          | Auto-negotiation with 10BASE-T FDX / HDX ability                                   |  |

|      |         |            |              |                                                                                                                                                                                                                                                          | Reserved                                                                           |  |

|      |         |            |              | 100                                                                                                                                                                                                                                                      | Manual selection of 100BASE-TX FDX                                                 |  |

|      |         |            |              | 101                                                                                                                                                                                                                                                      | Manual selection of 100BASE-TX HDX                                                 |  |

|      |         |            |              | 110                                                                                                                                                                                                                                                      | Manual selection of 10BASE-T FDX                                                   |  |

|      |         |            |              | 111                                                                                                                                                                                                                                                      | Manual selection of 10BASE-T HDX                                                   |  |

|      | [7:6]   |            | No define    | Always zero                                                                                                                                                                                                                                              |                                                                                    |  |

|      | [5]     |            | IRQ_TYPE_EEP | This bit will logic OR with BTCR (15h) bit-5 and will bee clear when host write BTCR. (Offset 15h)                                                                                                                                                       |                                                                                    |  |

|      | [4]     |            | IRQ_POL_EEP  | This bit wi                                                                                                                                                                                                                                              | ill logic OR with BTCR (15h) bit-4 and will been                                   |  |

|      | [2]     |            | No define    | Always zei                                                                                                                                                                                                                                               | host write BTCR. (Offset 15h)                                                      |  |

|      | [3]     |            |              |                                                                                                                                                                                                                                                          |                                                                                    |  |

|      | [2]     |            | NE2000_PROM  |                                                                                                                                                                                                                                                          | AX88196B internal memory map of 1Ch ~ 1Fh will                                     |  |

|      |         |            |              |                                                                                                                                                                                                                                                          | red to 57h. An ASCII code "W". Otherwise I to 42h. An ASCII code "B".              |  |

|      | [1:0]   |            | No define    | Always zei                                                                                                                                                                                                                                               |                                                                                    |  |

| 1h   | [15:0]  | 00h        | 06h          |                                                                                                                                                                                                                                                          | he total of word counts for auto loading                                           |  |

| Oh   | [15:0]  | 5Ah        | A5h          | Programmed pattern                                                                                                                                                                                                                                       |                                                                                    |  |

| 011  | [13.0]  | J1 111     | 71511        | 1 Togrammi                                                                                                                                                                                                                                               | ou pattorn                                                                         |  |

Tab - 7 EEPROM data format example

## 3.2 CSR Mapping

| System I/O Offset | Function                         |

|-------------------|----------------------------------|

| 0000H ~ 001FH     | AX88196B Command Status Register |

Tab - 8 CSR Address Mapping

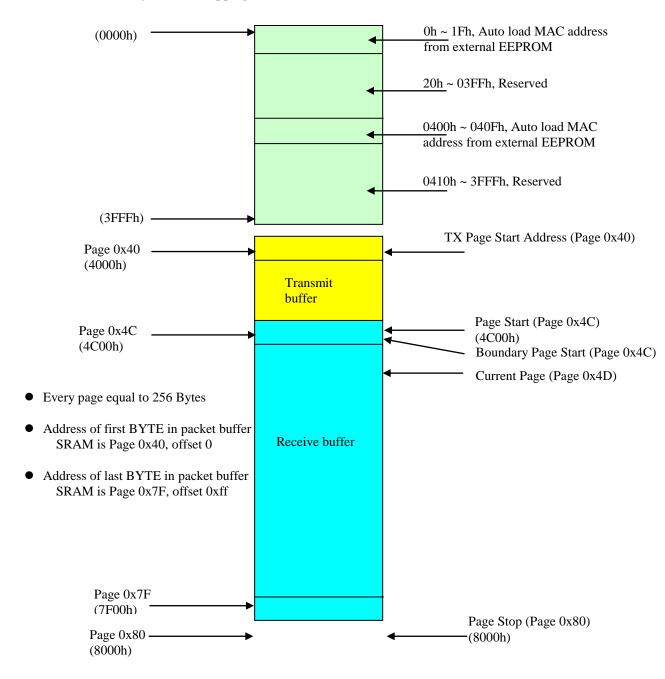

## 3.3 Internal SRAM Memory Mapping

| Offset        | Function               |

|---------------|------------------------|

| 0000H ~ 001FH | Load from EEPROM       |

| 0020H ~ 03FFH | Reserved               |

| 0400H ~ 040FH | Load from EEPROM       |

| 0410H ~ 3FFFH | Reserved               |

| 4000H ~ 7FFFH | NE2000 compatible mode |

|               | 8K x 16 SRAM Buffer    |

| 8000H ~ FFFFH | Reserved               |

Tab - 9 Local Memory Mapping

| SRAM Address | D[15:8]   | D[7:0]                |

|--------------|-----------|-----------------------|

| 1EH          | 57H / 42H | 57H / 42H             |

| 1CH          | 57H / 42H | 57H / 42H             |

| 1AH ~ 10H    | 00H       | 00Н                   |

| 0AH          | BAH       | BAH (E'NET ADDRESS 5) |

| 08H          | 98H       | 98H (E'NET ADDRESS 4) |

| 06H          | 76H       | 76H (E'NET ADDRESS 3) |

| 04H          | 54H       | 54H (E'NET ADDRESS 2) |

| 02H          | 32H       | 32H (E'NET ADDRESS 1) |

| 00H          | 10H       | 10H (E'NET ADDRESS 0) |

Tab - 10 Internal SRAM Map 00H ~ 1FH

| SRAM Address  | D[15:8]               | D[7:0]                |

|---------------|-----------------------|-----------------------|

| 40EH          | 57H                   | 57H                   |

| 0406H ~ 040DH | 00H                   | 00Н                   |

| 0404H         | BAH (E'NET ADDRESS 5) | 98H (E'NET ADDRESS 4) |

| 0402H         | 76H (E'NET ADDRESS 3) | 54H (E'NET ADDRESS 2) |

| 0400H         | 32H (E'NET ADDRESS 1) | 10H (E'NET ADDRESS 0) |

Tab - 11 Internal SRAM Map 0400H ~ 040FH

#### AX88196B internal memory address mapping

Fig - 3 Internal SRAM map

## 4.0 Basic Operation

## 4.1 Receiver Filtering

The address filtering logic compares the Destination Address Field (first 6 bytes of the received packet) to the Physical address registers stored in the Address Register Array. If any one of the six bytes does not match the pre-programmed physical address, the Protocol Control Logic rejects the packet. This is for unicast address filtering. All multicast destination addresses are filtered using a hashing algorithm. (See following description.) If the multicast address indexes a bit that has been set in the filter bit array of the Multicast Address Register Array the packet is accepted, otherwise the Protocol Control Logic rejects it. Each destination address is also checked for all 1's, which is the reserved broadcast address.

#### 4.1.1 Unicast Address Match Filter

The physical address registers are used to compare the destination address of incoming packets for rejecting or accepting packets. Comparisons are performed on a byte wide basis. The bit assignment shown below relates the sequence in PAR0-PAR5 to the bit sequence of the received packet.

|      | D7   | D6   | D5   | D4   | D3   | D2   | D1   | D0   |

|------|------|------|------|------|------|------|------|------|

| PAR0 | DA7  | DA6  | DA5  | DA4  | DA3  | DA2  | DA1  | DA0  |

| PAR1 | DA15 | DA14 | DA13 | DA12 | DA11 | DA10 | DA9  | DA8  |

| PAR2 | DA23 | DA22 | DA21 | DA20 | DA19 | DA18 | DA17 | DA16 |

| PAR3 | DA31 | DA30 | DA29 | DA28 | DA27 | DA26 | DA25 | DA24 |

| PAR4 | DA39 | DA38 | DA37 | DA36 | DA35 | DA34 | DA33 | DA32 |

| PAR5 | DA47 | DA46 | DA45 | DA44 | DA43 | DA42 | DA41 | DA40 |

Note: The bit sequence of the received packet is DA0, DA1, ... DA7, DA8 ....

#### 4.1.2 Multicast Address Match Filter

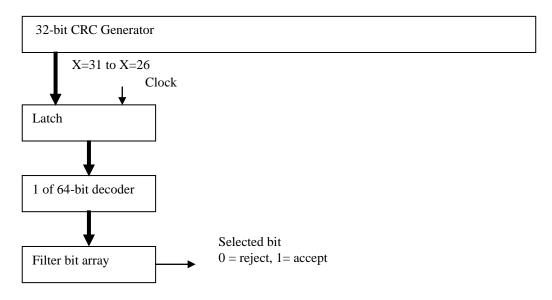

The Multicast Address Registers provide filtering of multicast addresses hashed by the CRC logic. All destination addresses are fed through the 32 bits CRC generation logic and as the last bit of the destination address enters the CRC, the 6 most significant bits of the CRC generator are latched. These 6 bits are then decoded by a 1 of 64 decode to index a unique filter bit (FB0-63) in the Multicast Address Registers. If the filter bit selected is set, the multicast packet is accepted. The system designer would use a program to determine which filter bits to set in the multicast registers. All multicast filter bits that correspond to Multicast Address Registers accepted by the node are then set to one. To accept all multicast packets all of the registers are set to all ones.

| _    | D7   | D6   | D5   | D4   | D3   | D2   | D1   | D0   |

|------|------|------|------|------|------|------|------|------|

| MAR0 | FB7  | FB6  | FB5  | FB4  | FB3  | FB2  | FB1  | FB0  |

| MAR1 | FB15 | FB14 | FB13 | FB12 | FB11 | FB10 | FB9  | FB8  |

| MAR2 | FB23 | FB22 | FB21 | FB20 | FB19 | FB18 | FB17 | FB16 |

| MAR3 | FB31 | FB30 | FB29 | FB28 | FB27 | FB26 | FB25 | FB24 |

| MAR4 | FB39 | FB38 | FB37 | FB36 | FB35 | FB34 | FB33 | FB32 |

| MAR5 | FB47 | FB46 | FB45 | FB44 | FB43 | FB42 | FB41 | FB40 |

| MAR6 | FB55 | FB54 | FB53 | FB52 | FB51 | FB50 | FB49 | FB48 |

| MAR7 | FB63 | FB62 | FB61 | FB60 | FB59 | FB58 | FB57 | FB56 |

If address Y is found to hash to the value 32 (20H), then FB32 (ref. 4.1.2) in MAR4 should be initialized to 1". This will cause the AX88196B to accept any multicast packet with the address Y.

Although the hashing algorithm does not guarantee perfect filtering of multicast address, it will perfectly filter up to 64 logical address filters if these addresses are chosen to map into unique locations in the multicast filter.

Note: The first bit of received packet sequence is 1's stands by Multicast Address.

#### 4.1.3 Broadcast Address Match Filter

The Broadcast check logic compares the Destination Address Field (first 6 bytes of the received packet) to all 1's, which is the values are "FF FF FF FF FF FF FF FF" in Hex format. If any bit of the six bytes does not equal to 1's, the Protocol Control Logic rejects the packet.

#### 4.1.4 VLAN Match Filter

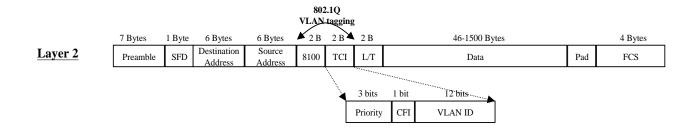

AX88196B compares the thirteenth and fourteenth bytes of receive frames. If not match with VLAN\_ID1, VLAN\_ID\_0 (offset 1dh, 1ch) then reject current frame. The VLAN filter will always accept VLAN\_ID is zero of receive frames due to it is 802.1q (for priority purpose) frames. The maximum length of the good packet is thus change from 1518 bytes to 1522 bytes.

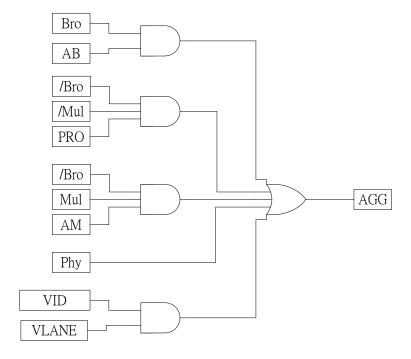

## 4.1.5 Aggregate Address Filter with Receive Configuration Setup

The final address filter decision depends on the destination address types, identified by the above 4 address match filters, and the setup of parameters of Receive Configuration Register.

Definitions of address match filter result are as following:

| Signal | Value | Description                 |  |

|--------|-------|-----------------------------|--|

| Phy    | =1    | Unicast Address Match       |  |

|        | =0    | Unicast Address not Match   |  |

| Mul    | =1    | Multicast Address Match     |  |

|        | =0    | Multicast Address not Match |  |

| Bro    | =1    | Broadcast Address Match     |  |

|        | =0    | Broadcast Address not Match |  |

| VID    | =1    | VLAN ID Match               |  |

|        | =0    | VLAN ID not Match           |  |

| AGG    | =1    | Aggregate Address Match     |  |

|        | =0    | Aggregate Address not Match |  |

The meaning of AB, AM and PRO signals, please refer to "Receive Configuration Register" RCR (offset 0Ch) The meaning of VLANE signal, Please refer to "MAC Configure Register" MCR (offset 1Bh)

Aggregate Address Filter function will be:

### 4.2 Buffer Management Operation

There are four buffer memory access types used in AX88196B.

- 1. Packet Reception (Write data to memory from MAC)

- 2. Packet Transmission (Read data from memory to MAC)

- 3. Filling Packets to Transmit Buffer (Host fill data to memory)

- 4. Removing Packets from the Receive Buffer Ring (Host read data from memory)

The type 1 and 2 operations act as Local DMA. Type 1 does Local DMA write operation and type 2 does Local DMA read operation. The type 3 and 4 operations act as Remote DMA. Type 3 does Remote DMA write operation and type 4 does Remote DMA read operation.

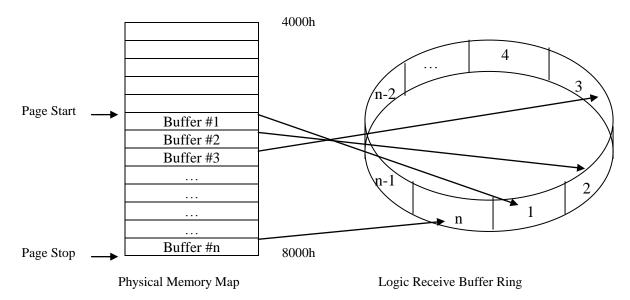

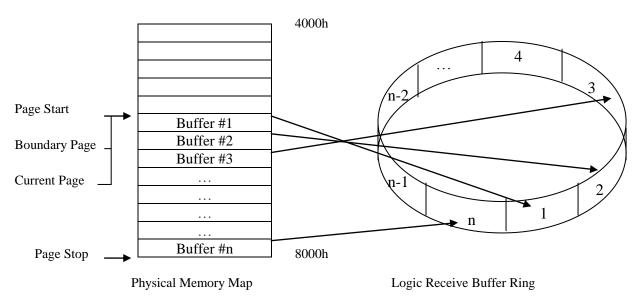

### 4.2.1 Packet Reception

The Local DMA receives channel uses a Buffer Ring Structure comprised of a series of contiguous fixed length 256 byte (128 word) buffers for storage of received packets. The location of the Receive Buffer Ring is programmed in two registers, a Page Start and a Page Stop Register. Ethernet packets consist of minimum packet size (64 bytes) to maximum packet size (1522 bytes), the 256 byte buffer length provides a good compromise between short packets and longer packets to most efficiently use memory. In addition these buffers provide memory resources for storage of back-to-back packets in loaded networks. Buffer Management Logic in the AX88196B controls the assignment of buffers for storing packets. The Buffer Management Logic provides three basic functions: linking receive buffers for long packets, recovery of buffers when a packet is rejected, and recalculation of buffer pages that have been read by the host.

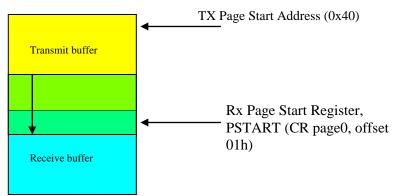

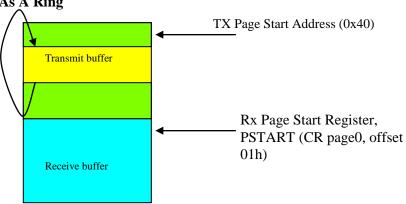

At initialization, a portion of the 16k byte (or 8k word) address space is reserved for the receiver buffer ring. Two eight bit registers, the Page Start Address Register (PSTART) and the Page Stop Address Register (PSTOP) define the physical boundaries of where the buffers reside. The AX88196B treats the list of buffers as a logical ring; whenever the DMA address reaches the Page Stop Address, the DMA is reset to the Page Start Address.

Fig - 4 Receive Buffer Ring

#### **Initialization Of The Buffer Ring**

Two static registers and two working registers control the operation of the Buffer Ring. These are the Page Start Register, Page Stop Register (both described previously), the Current Page Register and the Boundary Pointer Register. The Current Page Register points to the first buffer used to store a packet and is used to restore the DMA for writing status to the Buffer Ring or for restoring the DMA address in the event of a Runt packet, a CRC, or Frame Alignment error. The Boundary Register points to the first packet in the Ring not yet read by the host. If the local DMA address ever reaches the Boundary, reception is aborted. The Boundary Pointer is also used to initialize the Remote DMA for removing a packet and is advanced when a packet is removed. A simple analogy to remember the function of these registers is that the Current Page Register acts as a Write Pointer and the Boundary Pointer acts as a Read Pointer.

Fig - 5 Receive Buffer Ring At Initialization

#### **Beginning Of Reception**

When the first packet begins arriving the AX88196B and begins storing the packet at the location pointed to by the Current Page Register. An offset of 4 bytes is reserved in this first buffer to allow room for storing receives status corresponding to this packet.

#### **Linking Receive Buffer Pages**

If the length of the packet exhausts the first 256 bytes buffer, the DMA performs a forward link to the next buffer to store the remainder of the packet. For a maximal length packet the buffer logic will link six buffers to store the entire packet. Buffers cannot be skipped when linking; a packet will always be stored in contiguous buffers. Before the next buffer can be linked, the Buffer Management Logic performs two comparisons. The first comparison tests for equality between the DMA address of the next buffer and the contents of the Page Stop Register. If the buffer address equals the Page Stop Register, the buffer management logic will restore the DMA to the first buffer in the Receive Buffer Ring value programmed in the Page Start Address Register. The second of comparison test between the DMA address of the next buffer address and the contents of the Boundary Pointer Register. If the two values are equal the reception is aborted. The Boundary Pointer Register can be used to protect against overwriting any area in the receive buffer that has not yet been read. When linking buffers, buffer management will never cross this pointer, effectively avoiding any overwrites. If the buffer address does not match either the Boundary Pointer or Page Stop Address, the link to the next buffer is performed.

#### **Linking Buffers**

Before the DMA can enter the next contiguous 256 bytes buffer, the address is checked for equality to PSTOP and to the Boundary Pointer. If neither is reached, the DMA is allowed to use the next buffer.

#### **Buffer Ring Overflow**

If the Buffer Ring has been filled and the DMA reaches the Boundary Pointer Address, reception of the current incoming packet will be discard by the AX88196B. Thus, the packets previously received and still contained in the Ring will not be destroyed.

#### **End Of Packet Operations**

At the end of the packet the AX88196B determines whether the received packet is to be accepted or rejected. It either branch to a routine to store the or to another routine that recovers the buffers used to store the packet. If current of packet is accepted then AX88196B write two words of buffer header on receive buffer.

| Buffer Header | Description                  |

|---------------|------------------------------|

| NPR, Status   | D[15:8]: Next Page Pointer   |

|               | D[7:6]: always zero          |

|               | D[5]: multicast or broadcast |

|               | D[4]: runt packet            |

|               | D[3]: MII error              |

|               | D[2]: alignment error        |

|               | D[1]: CRC error              |

|               | D[0]: good packet            |

| Length        | D[15:11]: always zero        |

|               | D[10:0]: packet length       |

#### **Successful Reception**

If the packet is successfully received as shown, the DMA is restored to the first buffer used to store the packet (pointed to by the Current Page Register). The DMA then stores the Receive Status, a Pointer to where the next packet will be stored and the number of received bytes. Note that the remaining bytes in the last buffer are discarded and reception of the next packet begins on the next empty 256 byte buffer boundary. The Current Page Register is then initialized to the next available buffer in the Buffer Ring. (The location of the next buffer had been previously calculated and temporarily stored in an internal scratchpad register.)

#### **Buffer Recovery For Rejected Packets**

If the packet is a runt packet or contains CRC or Frame Alignment errors, it is rejected. The buffer management logic resets the DMA back to the first buffer page used to store the packet (pointed to by CPR), recovering all buffers that had been used to store the rejected packet. This operation will not be performed if the AX88196B is programmed to accept either runt packets or packets with CRC or Frame Alignment errors. The received CRC is always stored in buffer memory after the last byte of received data for the packet.

#### 4.2.2 Packet Transmission

The Local DMA Read is also used during transmission of a packet. Three registers control the DMA transfer during transmission, a Transmit Page Start Address Register (TPSR) and the Transmit Byte Count Registers (TBCR0, 1). When the AX88196B receives a command to transmit the packet pointed to by these registers, buffer memory data will be moved into the FIFO as required during transmission. The AX88196B Controller will generate and append the preamble, synch and CRC fields. AX88196B supports options of transmit queue function to enhance transmit performance.

#### Original NE2000 Of Transmit Buffer

AX88196B remote DMA write default operation is continue to write next address even over transmit buffer area. Host can do whole memory read / write testing. And host must handle the transmit data do not overwrite receive buffer area when performing fill transmit data to transmit buffer.

#### **Options Of Transmit Buffer As A Ring**

When active Transmit Buffer Ring Enable (CR page3 of offset 0Dh). AX88196B remote DMA write operation will role over from last transmit page to first transmit page. Host no need reassign RSAR0, RSAR1 again to fill transmit data for first page.

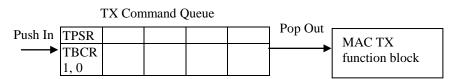

#### Options Back-To-Back Transmission (TX Command Queue)

When active TX Queue Enable (offset 1Bh), Host can continue Writing TXP (bit 2 of CR register) to push TPSR and TBCR1, 0 into AX88196B TX command queue as long as Transmit buffer has enough vacancy and CTEPR (offset 1Ch) bit7 is '0' (Not full). After current packet transmitted completely, MAC TX will pop out next TPSR and TBCR1, 0 from TX Command Queue then transmit this packet following CSMA/CD protocol.

It is recommended to enable this function to enhance TX performance.

AX88196B will report Current of Transmit End Page CTEPR (offset 1Ch) when every packet transmits completed.

Host can understand AX88196B current of transmitting buffer point by reading CTEPR.

#### **Transmit Packet Assembly**

The AX88196B requires a contiguous assembled packet with the format shown below. The transmit byte count includes the Destination Address, Source Address, Length Field and Data. It does not include preamble and CRC. When transmitting data smaller than 64 bytes, AX88196B can auto padding to a minimum length of 64 bytes Ethernet frame. The packets are placed in the buffer RAM by the system. System programs the AX88196B Core's Remote DMA to move the data from the system buffer RAM to internal transmit buffer RAM.

The data transfer must be 16-bits (1 word) when in 16-bit mode, and 8-bits when the AX88196B Controller is set in 8-bit mode. The data width is selected by setting the WTS bit in the Data Configuration Register.

| Destination Address | 6 Bytes  |

|---------------------|----------|

| Source Address      | 6 Bytes  |

| Length / Type       | 2 Bytes  |

| Data                | 46 Bytes |

| (Pad if < 46 Bytes) | Min.     |

General Transmit Packet Format

#### **Transmission**

Prior to transmission, the TPSR (Transmit Page Start Register) and TBCR0, TBCR1 (Transmit Byte Count Registers) must be initialized. To initiate transmission of the packet the TXP bit in the Command Register is set. The Transmit Status Register (TSR) is cleared and the AX88196B begins to pre-fetch transmit data from memory. If the Inter-packet Gap (IPG) has timed out the AX88196B will begin transmission.

#### **Conditions Required To Begin Transmission**

In order to transmit a packet, the following three conditions must be met:

- 1. The Inter-packet Gap Timer has timed out

- 2. At least one byte has entered the FIFO.

- 3. If a collision had been detected then before transmission the packet back-off time must have timed out.

#### **Collision Recovery**

During transmission, the Buffer Management logic monitors the transmit circuitry to determine if a collision has occurred. If a collision is detected, the Buffer Management logic will reset the FIFO and restore the Transmit DMA pointers for retransmission of the packet. The COL bit will be set in the TSR and the NCR (Number of Collisions Register) will be incremented. If 15 retransmissions each result in a collision the transmission will be aborted and the ABT bit in the TSR will be set.

#### **Transmit Packet Assembly Format**

The following diagrams describe the format for how packets must be assembled prior to transmission for different byte ordering schemes. The various formats are selected in the Data Configuration Register.

| D15 D8                | D7 D0                 |

|-----------------------|-----------------------|

| D[15:8]               | D[7:0]                |

| Destination Address 1 | Destination Address 0 |

| Destination Address 3 | Destination Address 2 |

| Destination Address 5 | Destination Address 4 |

| Source Address 1      | Source Address 0      |

| Source Address 3      | Source Address 2      |

| Source Address 5      | Source Address 4      |

| Type / Length 1       | Type / Length 0       |

| Data 1                | Data 0                |

|                       |                       |

WTS = 1 in Data Configuration Register. This format is used with ISA or 80186 Mode.

| D7 |                             | D0 |

|----|-----------------------------|----|

|    | Destination Address 0 (DA0) |    |

|    | Destination Address 1 (DA1) |    |

|    | Destination Address 2 (DA2) |    |

|    | Destination Address 3 (DA3) |    |

|    | Destination Address 4 (DA4) |    |

|    | Destination Address 5 (DA5) |    |

|    | Source Address 0 (SA0)      |    |

|    | Source Address 1 (SA1)      |    |

|    | Source Address 2 (SA2)      |    |

|    | Source Address 3 (SA3)      |    |

|    | Source Address 4 (SA4)      |    |

|    | Source Address 5 (SA5)      |    |

|    | Type / Length 0             |    |

|    | Type / Length 1             |    |

|    | Data 0                      |    |

|    | Data 1                      |    |

|    | ••••                        |    |

WTS = 0 in Data Configuration Register.

This format is used with ISA or MCS-51 Mode.

Note: All examples above will result in a transmission of a packet in order of DA0 (Destination Address 0), DA1, DA2, DA3 and so on in byte. Bits within each byte will be transmitted least significant bit first.

### 4.2.3 Filling Packet to Transmit Buffer (Host fill data to memory)

The Remote DMA channel is used to both assembles packets for transmission, and to remove received packets from the Receive Buffer Ring. It may also be used as a general-purpose slave DMA channel for moving blocks of data or commands between host memory and local buffer memory. There are two modes of operation, Remote Write and Remote Read Packet.

Two register pairs are used to control the Remote DMA, a Remote Start Address (RSAR0, RSAR1) and a Remote Byte Count (RBCR0, RBCR1) register pair. The Start Address Register pair points to the beginning of the block to be moved while the Byte Count Register pair is used to indicate the number of bytes to be transferred. Full handshake logic is provided to move data between local buffer memory (Embedded Memory) and a bi-directional data port.

#### **Remote Write**

A Remote Write transfer is used to move a block of data from the host into local buffer memory. The Remote DMA will read data from the I/O port and sequentially write it to local buffer memory beginning at the Remote Start Address. The DMA Address will be incremented and the Byte Counter will be decremented after each transfer. The DMA is terminated when the Remote Byte Count Register reaches a count of zero.

### 4.2.4 Removing Packets from the Ring (Host read data from memory)

#### **Remote Read**