# 5-Port Gigabit Ethernet Switch with Embedded Memory

#### Features

- 5-port Gigabit Ethernet switch integrating MACs, packet buffer memory and switching engine with RGMII/GMII/MII interface

- RGMII support REV 1.3 with 3.3V IO

- Full Duplex 1000 Mbit/s.

- Full and Half Duplex 10/100 Mbit/s

- Supports auto-sensing or manual selection for speed and duplex capability with an embedded MPU

- Store-and-forward operation support

- Performs full wire-speed switching with Head of Line (HOL) blocking prevention

- Supports up to 8 Port-based VLAN Groups

- Supports broadcast storm filtering.

- Quality-of-Service provisioning on 802.1P tag and port-pairs with two priority queues

- By-port Egress/Ingress bandwidth (rate) control

- Embedded 128K Byte SRAM for packet buffer

- Supports packet length up to 1522 bytes

- Supports 9K/12K byte JUBMO packet

- Integrated two-way Address-Lookup engine and table for 4K MAC addresses

Document No.: AX88655AB / V0.8 / June 11, 2003

- Programmable aging mechanism for the two-way 4K MAC addresses table

- Two hashing schemes: direct and XOR mode.

- Support ingress port security mode, incoming packets with unknown source MAC address could be dropped

- Egress/Ingress Port Mirroring for Sniffer function.

- Flow control

- Full-duplex IEEE 802.3x flow control

- Half-duplex back pressure flow control

- Optional smart flow control for mix-speed connection

- Supports port-based trunking for high-bandwidth links

- Provides 5 GPIO ports

- Provides EEPROM interface for auto-configuration

System clock input is one 25MHz Crystal and one

- 125MHz from PHY GCLK output

- 1.8 and 3.3V operations

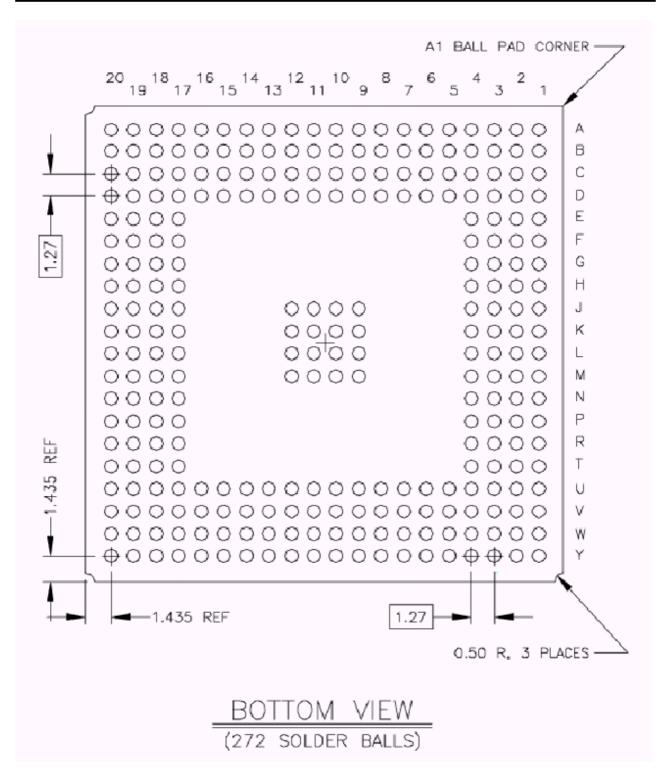

- 3.3 I/Os and packaged in 272-pin BGA

#### **Product Description**

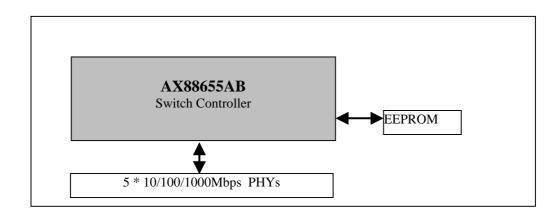

The AX88655AB is an 5-port 10/100/1000 Mbps Ethernet switch with, GMII/RGMII or MII Interface. The switch controller provides network system manufacturers the ideal platform for building smart and cost-effective backbone switches for small to medium sized businesses.

The AX88655AB 5-port 10/100/100 BASE-T single chip switch controllers combine the benefits of network simplicity, flexibility and high integration. Its highly integrated feature set enables network system manufacturers to build smart switches for the fast-growing small to medium business market segment.

Benefits of AX88655AB Switches are below.

Simplicity

Provides a smart, simple and low maintenance plug-and-play network interconnect system for small to medium size businesses

Flexibility

Highly scalable configuration allows system manufacturers to enable or disable a range of features to best meet their target price point.

Integration Highly integrated design drives down overall switch manufacturing costs.

#### **Target Applications**

- ✓ 5-port Gigabit Layer 2 Switches for workgroup

- ✓ High-port count Layer 2 switches with trunking

- ✓ High performance solution of Ethernet backbone

#### ASIX ELECTRONICS CORPORATION

4F, NO.8, Hsin Ann Rd., Science-based Industrial Park, Hsin-Chu City, Taiwan, R.O.C. TEL: 886-3-579-9500 FAX: 886-3-563-9799 First Released Date: 11/07/2002

http://www.casix.com.twheet4U.com

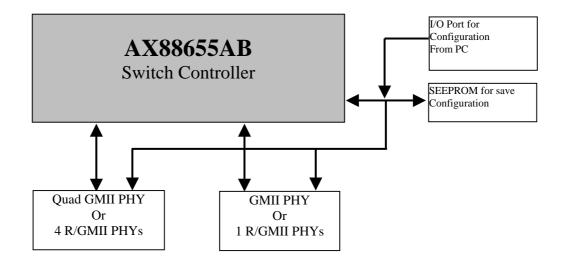

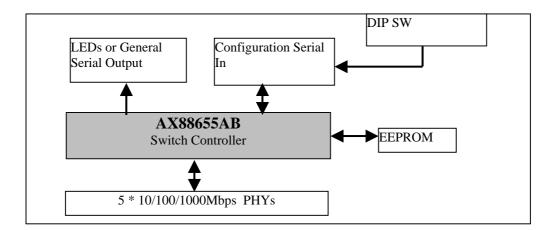

#### System Block Diagram

#### Always contact ASIX for possible updates before starting a design.

This data sheet contains new products information. ASIX ELECTRONICS reserves the rights to modify the product specification without notice. No liability is assumed as a result of the use of this product. No rights under any patent accompany the sale of the product.

# CONTENTS

| 1.0 AX88655AB OVERVIEW                                      | 5  |

|-------------------------------------------------------------|----|

| 1.1 GENERAL DESCRIPTION                                     | 5  |

| 1.2 AX88655AB BLOCK DIAGRAM                                 | 5  |

| 1.3 PIN CONNECTION DIAGRAM                                  | 6  |

| 2.0 I/O DEFINITION                                          | 7  |

| 2.1 RGMII/GMII/MII INTERFACE                                | 7  |

| 2.2 Miscellaneous                                           |    |

| 3.0 FUNCTIONAL DESCRIPTION                                  |    |

| 3.1 Introduction                                            | 11 |

| 3.2 PACKET FILTERING AND FORWARDING PROCESS                 |    |

| 3.3 MAC ADDRESS ROUTING, LEARNING AND AGING PROCESS         |    |

| 3.4 FULL DUPLEX 802.3x FLOW CONTROL                         | 11 |

| 3.5 HALF DUPLEX BACK PRESSURE CONTROL                       | 11 |

| 3.6 MII POLLING                                             |    |

| 3.7 Port-Based QoS: Port-Pair                               |    |

| 3.8 VLAN AND BROADCAST STORMING PREVENTION                  |    |

| 3.9 SECURITY OPERATION - PORT SA RESTRICTION                |    |

| 3.10 INGRESS/EGRESS BANDWIDTH CONTROL SCHEME                |    |

| 3.11 Port Mirroring                                         |    |

| 4.0 REGISTER DESCRIPTIONS                                   |    |

| 5.0 ELECTRICAL SPECIFICATION AND TIMING                     | 21 |

| 5.1 Absolute Maximum Ratings                                | 21 |

| 5.2 GENERAL OPERATION CONDITIONS                            | 21 |

| 5.3 DC CHARACTERISTICS                                      |    |

| 5.4 AC SPECIFICATIONS                                       |    |

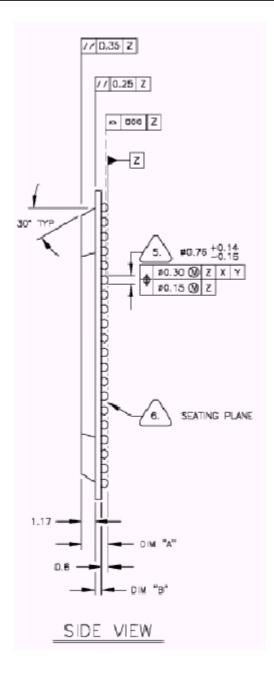

| 6.0 PACKAGE INFORMATION                                     | 27 |

| APPENDIX A: SYSTEM APPLICATIONS                             |    |

| APPENDIX B: DESIGN NOTE                                     |    |

| APPENDIX C: WEIGHT SETTING FOR QOS                          |    |

| APPENDIX D: RESOLUTION INGRESS/EGRESS FOR BANDWIDTH CONTROL |    |

# FIGURES

| FIG-1 AX88655AB BLOCK DIAGRAM              | 5 |

|--------------------------------------------|---|

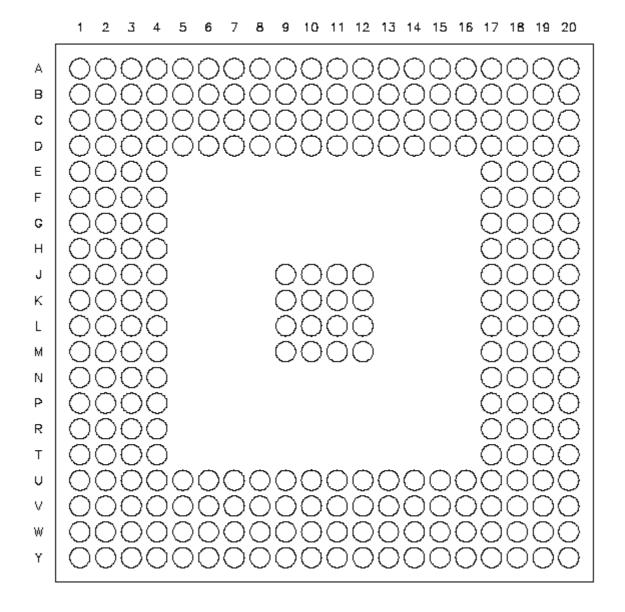

| FIG-2 TOP VIEW OF AX88655AB AB PIN DIAGRAM | 6 |

# 1.0 AX88655AB Overview

## **1.1 General Description**

The AX88655AB Gigabit switch controller supports eight 10/100/1000 Mbps ports in wire-speed operation. The AX88655AB Gigabit switch controller provides eight 10/100/1000 Ethernet ports with RGMII/GMII/MII interface. For each ports, the AX88655AB supports GMII/RGMII (802.3ab, 1000BASE-T) interface with full-duplex operation at Gigabit speed, full- or half-duplex operation at 10/100 Mbps speed (using 802.3/u, 10/100BASE-T) and polls the status of PHYs with an embedded MPU.

The device supports 4K internal MAC addresses which are shared by all ports with an embedded SRAM. The learning/routing engine is implemented with a two-way hash/linear algorithm to reduce possibility of routing collision.

Basically the AX88655AB supports non-blocking wire speed forwarding rate and no Head-of-Line (HOL) blocking issue. The AX88655AB provides two flow-control mechanisms to avoid loss of data: an optional jamming based backpressure flow control in the half-duplex operation and IEEE 802.3x in the full-duplex mode.

To support Quality of Service (QoS), each output port has two priority queues and their assignment can be based on the 802.1p priority field or Port-Pair setting. Each output port retrieves the frames from the shared buffer based on queuing and sends them to the transmitting (Tx) FIFO.

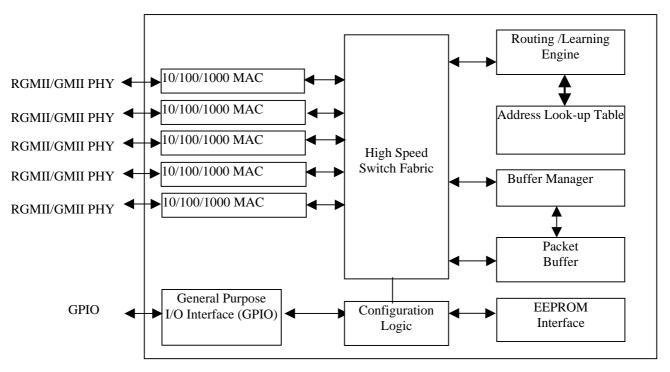

# 1.2 AX88655AB Block Diagram

Fig-1 AX88655AB Block Diagram

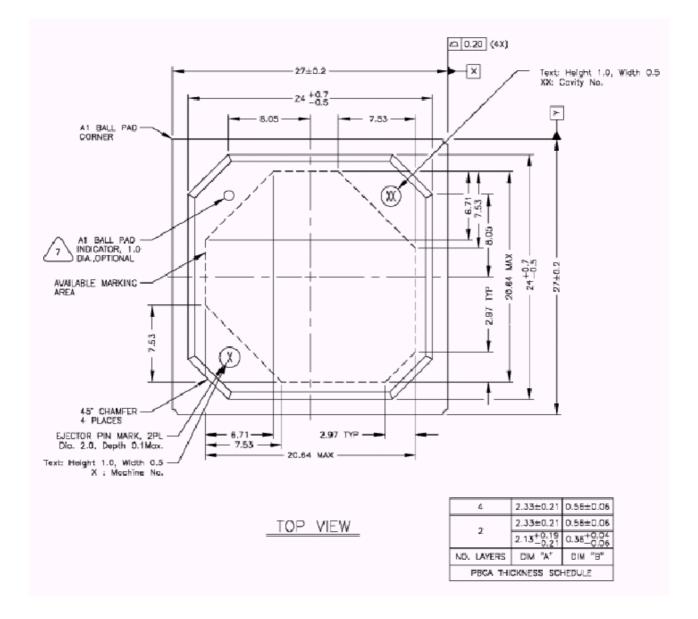

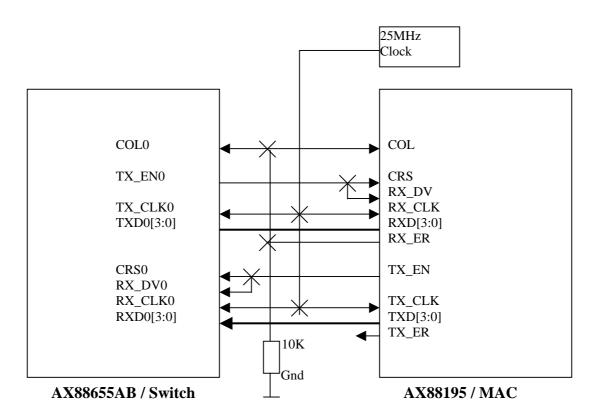

# **1.3 Pin Connection Diagram**

Fig-2 Top View of AX88655ABB Pin Diagram

# 2.0 I/O Definition

The following terms describe the AX88655AB pin-out: All pin names with the "/" suffix are asserted low. The following abbreviations are used in following Tables.

| Ι   | Input        | PU | Pull Up          |

|-----|--------------|----|------------------|

| 0   | Output       | PD | Pull Down        |

| I/O | Input/Output | Р  | <b>Power Pin</b> |

| OD  | Open Drain   |    |                  |

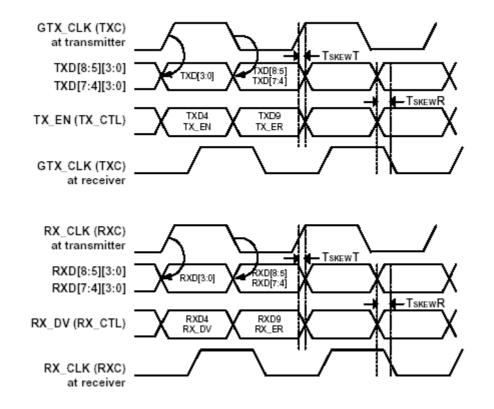

### 2.1 RGMII/GMII/MII Interface

| Signal Name | I/O  | Pin No.     | Description                                                                |

|-------------|------|-------------|----------------------------------------------------------------------------|

| GTX_CLK0    | 0    | Y2          | <b>125MHz Clock Output:</b> it is a continuous 125 MHz clock output to     |

|             |      |             | giga-PHY operating at 1000BASE-T. That is, it is a timing reference for    |

|             |      |             | TX_EN0 and TXD0[7:0]                                                       |

| TX_EN0      | 0    | Y1          | Transmit Enable: When TX_EN0 is asserted, data on TXD0[7:0] are            |

|             |      |             | transmitted onto PHY. TX_EN0 is synchronous to GTX_CLK0 in                 |

|             |      |             | 1000BASE-T mode and synchronous to TX_CLK0 in 10/100BASE-T                 |

|             |      |             | mode.                                                                      |

| TXD0[7:0]   | 0    | W1, V2, V1, | Transmit Data: Synchronous to the rising of GTX_CLK0 in                    |

|             |      | U3, U2,U1 , | 1000BASE-T mode. And synchronous to rising edge of TX_CLK0 in              |

|             |      | T2, T1      | 10/100BASE-T mode., For RGMII, only TXD0[3:0]                              |

| TX_CLK0     | I/PD | W5          | MII Transmit Clock Input: TX_EN0 and TXD0[3:0] are                         |

|             |      |             | synchronous to the rising edge of this clock in 10/100BASE-T mode.         |

| COL0        | I/PD | Y5          | Collision Detect: Active high to indicate that there is collision occurred |

|             |      |             | in half duplex mode. In full duplex mode COL0 is always low.               |

| CRS0        | I/PD | U6          | Carrier Sense: Active high if there is carrier on medium. In half duplex   |

|             |      |             | mode CRS0 is also asserted during transmission and asynchronous to         |

|             |      |             | any clock.                                                                 |

| RX_DV0      | Ι    | U5          | Receive Data Valid: Active high to indicate that data presented on         |

|             |      |             | RXD0[7:0] is valid and synchronous to RX_CLK0.                             |

| RX_CLK0     | Ι    | V5          | Receive Clock Input: 125, 25 and 2.5 MHz is running at 1000/100/10         |

|             |      |             | BASE-T mode respectively. RX_DV0 and RXD0[7:0] are                         |

|             |      |             | synchronous to rising edge of this clock.                                  |

| RXD0[7:0]   | I/PD | U4, V4, W4, | Receive Data: Data received by the PHY are presented on RXD0 and           |

|             |      | Y4, V3, W3, | synchronous to RX_CLK0. RXD0[3:0] is valid in                              |

|             |      | Y3, W2      | 10/100/1000BASE-T and RXD[7:4] is valid only in 1000BASE-T                 |

|             |      |             | modes. For RGMII, only RXD0[3:0]                                           |

#### 2.1.1 RGMII/GMII/MII Interface Port 0

#### 2.1.5 RGMII/GMII/MII Interface Port 1

| Signal Name | I/O  | Pin No.                                      | Description                                                  |

|-------------|------|----------------------------------------------|--------------------------------------------------------------|

| GTX_CLK1    | 0    | G20                                          | <b>125MHz Clock Output:</b> Please references section 2.1.1. |

| TX_EN1      | 0    | H17                                          | Transmit Enable: Please references section 2.1.1.            |

| TXD1[7:0]   | 0    | H18, H19,<br>H20, J18, J19,<br>J20, K19, K20 |                                                              |

| TX_CLK1     | I/PD | E17                                          | MII Transmit Clock Input: Please references section 2.1.1.   |

7

ASIX ELECTRONICS CORPORATION

AX88655AB 5-Port 10/100/1000BASE-T Ethernet Switch CONFIDENTIAL

| COL1      | I/PD | D18            | Collision Detect: Please references section 2.1.1.    |

|-----------|------|----------------|-------------------------------------------------------|

| CRS1      | I/PD | D19            | Carrier Sense: Please references section 2.1.1.       |

| RX_DV1    | Ι    | E19            | Receive Data Valid: Please references section 2.1.1.  |

| RX_CLK1   | Ι    | E18            | Receive Clock Input: Please references section 2.1.1. |

| RXD1[7:0] | I/PD | E20, F17, F18, | Receive Data: Please references section 2.1.1.        |

|           |      | F19, F20, G17, |                                                       |

|           |      | G18, G19       |                                                       |

#### 2.1.6 RGMII/GMII/MII Interface Port 2

| Signal Name | I/O  | Pin No.                                      | Description                                                  |

|-------------|------|----------------------------------------------|--------------------------------------------------------------|

| GTX_CLK2    | 0    | A18                                          | <b>125MHz Clock Output:</b> Please references section 2.1.1. |

| TX_EN2      | 0    | B18                                          | Transmit Enable: Please references section 2.1.1.            |

| TXD2[7:0]   | 0    | C18, B19, A19,<br>A20, B20, C19,<br>C20, D20 | Transmit Data: Please references section 2.1.1.              |

| TX_CLK2     | I/PD | C15                                          | MII Transmit Clock Input: Please references section 2.1.1.   |

| COL2        | I/PD | D15                                          | Collision Detect: Please references section 2.1.1.           |

| CRS2        | I/PD | D14                                          | Carrier Sense: Please references section 2.1.1.              |

| RX_DV2      | Ι    | A15                                          | Receive Data Valid: Please references section 2.1.1.         |

| RX_CLK2     | Ι    | B15                                          | Receive Clock Input: Please references section 2.1.1.        |

| RXD2[7:0]   | I/PD | D16, C16, B16,                               | Receive Data: Please references section 2.1.1.               |

|             |      | A16, D17,                                    |                                                              |

|             |      | C17, B17, A17                                |                                                              |

#### 2.1.7 RGMII/GMII/MII Interface Port 3

| Signal Name | I/O  | Pin No.                                      | Description                                                  |

|-------------|------|----------------------------------------------|--------------------------------------------------------------|

| GTX_CLK3    | 0    | A11                                          | <b>125MHz Clock Output:</b> Please references section 2.1.1. |

| TX_EN3      | 0    | C12                                          | Transmit Enable: Please references section 2.1.1.            |

| TXD3[7:0]   | 0    | B12, A12, C13,<br>B13, A13, C14,<br>B14, A14 | Transmit Data: Please references section 2.1.1.              |

| TX_CLK3     | I/PD | D9                                           | MII Transmit Clock Input: Please references section 2.1.1.   |

| COL3        | I/PD | C8                                           | Collision Detect: Please references section 2.1.1.           |

| CRS3        | I/PD | D8                                           | Carrier Sense: Please references section 2.1.1.              |

| RX_DV3      | Ι    | B9                                           | Receive Data Valid: Please references section 2.1.1.         |

| RX_CLK3     | Ι    | C9                                           | Receive Clock Input: Please references section 2.1.1.        |

| RXD3[7:0]   | I/PD | A9, D10, C10,                                | Receive Data: Please references section 2.1.1.               |

|             |      | B10, A10,<br>D11, C11, B11                   |                                                              |

#### 2.1.8 RGMII/GMII/MII Interface Port 4

| Signal Name | I/O | Pin No. | Description                                                  |          |

|-------------|-----|---------|--------------------------------------------------------------|----------|

| GTX_CLK4    | 0   | A5      | <b>125MHz Clock Output:</b> Please references section 2.1.1. |          |

| TX_EN4      | 0   | B5      | Transmit Enable: Please references section 2.1.1.            | www.Data |

| TXD4[7:0] | 0    | C6, B6, A6, | Transmit Data: Please references section 2.1.1.              |

|-----------|------|-------------|--------------------------------------------------------------|

|           |      | C7, B7, A7, |                                                              |

|           |      | B8, A8      |                                                              |

| TX_CLK4   | I/PD | B1          | MII Transmit Clock Input: Please references section 2.1.1.   |

| COL4      | I/PD | C1          | Collision Detect: Please references section 2.1.1.           |

| CRS4      | I/PD | C2          | Carrier Sense: Please references section 2.1.1.              |

| RX_DV4    | Ι    | B2          | Receive Data Valid: Please references section 2.1.1.         |

| RX_CLK4   | Ι    | A1          | <b>Receive Clock Input:</b> Please references section 2.1.1. |

| RXD4[7:0] | I/PD | A2, B3, A3, | Receive Data: Please references section 2.1.1.               |

|           |      | C4, B4, A4, |                                                              |

|           |      | D5, C5      |                                                              |

## **2.2 Miscellaneous**

| NC                   | ļ |                 |                                                                                                                                                 |

|----------------------|---|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

|                      | 1 | L1, L2, L3,     | NC                                                                                                                                              |

|                      | 1 | M2, M3, M4,     |                                                                                                                                                 |

|                      | 1 | N1, N2, N3,     |                                                                                                                                                 |

|                      | 1 | P1, P2, P3,     |                                                                                                                                                 |

|                      | 1 | R1,R2, R3,      |                                                                                                                                                 |

|                      | 1 | R4 ,T3, T4, F4, | ,                                                                                                                                               |

|                      | 1 | F3, G2, E1,     |                                                                                                                                                 |

|                      | 1 | H3,G3, C3,      |                                                                                                                                                 |

|                      | 1 | G1,Y9,V8,       |                                                                                                                                                 |

|                      | 1 | W8, Y8,         |                                                                                                                                                 |

|                      | 1 | V7, W7, Y7,     |                                                                                                                                                 |

|                      | 1 | V6, W6,         |                                                                                                                                                 |

|                      | 1 | Y6,U11,V12,U    |                                                                                                                                                 |

|                      | 1 | 12,W11,V11,     |                                                                                                                                                 |

|                      | 1 | Y11, U10, V10   |                                                                                                                                                 |

|                      | 1 | W10, Y10        |                                                                                                                                                 |

|                      | 1 | U9, V9,         |                                                                                                                                                 |

|                      | 1 | W9,Y15,U14,     |                                                                                                                                                 |

|                      | 1 | V14, W14,       |                                                                                                                                                 |

|                      | 1 | Y14, V13,       |                                                                                                                                                 |

|                      | 1 | W13,Y13,        |                                                                                                                                                 |

|                      | 1 | W12,            |                                                                                                                                                 |

|                      | 1 | Y12,W18,Y19,    |                                                                                                                                                 |

|                      | 1 | W19,V17,Y18,    |                                                                                                                                                 |

|                      | 1 | W17, Y17,       |                                                                                                                                                 |

|                      | 1 | U16, V16,       |                                                                                                                                                 |

|                      | 1 | W16, Y16,       |                                                                                                                                                 |

|                      | 1 | V15,            |                                                                                                                                                 |

|                      | 1 | W15,T20,U17,    |                                                                                                                                                 |

|                      | 1 | U18, U19,       |                                                                                                                                                 |

|                      | 1 | U20, V18,       |                                                                                                                                                 |

|                      | 1 | V19, V20,       |                                                                                                                                                 |

|                      | 1 | W20,            |                                                                                                                                                 |

|                      | 1 | Y20,P17,N20,    |                                                                                                                                                 |

|                      | 1 | N19,P19,P18,    |                                                                                                                                                 |

|                      | 1 | P20, R17, R18,  |                                                                                                                                                 |

|                      | 1 | R19, R20, T17,  |                                                                                                                                                 |

| E 9061 EN            |   | T18, T19        | D 111                                                                                                                                           |

| E_8051_EN<br>USE_83M | I | D4<br>D3        | Pull low, using external 8051, NC or Pull hi, using internal 8051<br>System clock enable,0:use SYSCLK, 1:90M generate by PLL with Date Sheet4U. |

| USE_03IVI            | 1 | J               | 9 ASIX ELECTRONICS CORPORATION                                                                                                                  |

| OL IZ OCENI |        | T 10          |                                                                           |

|-------------|--------|---------------|---------------------------------------------------------------------------|

| CLK_80IN    | I      | L19           | System clock input :85~90M                                                |

| F1          | Ι      | M1            | Frequency 1 input, must pull high with 4.7K ohm resistor                  |

| F2          | Ι      | M19           | Frequency 2 input from PHY 125M clock source.                             |

| F2_CTL      | Ι      | D2            | Frequency 2 input enable, must pull low with 4.7K ohm resistor            |

| X_IN        | Ι      | M20           | Crystal or OSC 25MHz Input: This is a clock source of internal PLL.       |

| X_OUT       | 0      | L20           | Crystal 25MHz Output: This pin should be floating with single-ended       |

|             |        |               | external clock.                                                           |

| /RST        | Ι      | D1            | Reset: Active Low                                                         |

| MDIO        | I/O/PU | H2            | Station Management Data In/Out: PHY Management Data Input and             |

|             |        |               | Output.                                                                   |

| MDC         | 0      | H1            | Station Management Data Clock Out: PHY Management Clock.                  |

| SDIO        | I/O/PU | J2            | EEPROM Data In/Out: EEPROM Serial Data Input and Output.                  |

| SDC         | I/O/PU | J1            | <b>EEPROM Data Clock In/Out:</b> EEPROM Serial Clock. (Note: It is        |

|             |        |               | output pin if the embedded MPU is active; otherwise as input pin)         |

| SID[4:0]    | I/PD   | F2, F1,       | Switch ID: MPU can identify the switch and PHYs with this ID.             |

|             | I/PD   | E4, E3, E2    | Default is "00011b".                                                      |

|             | I/PD   |               |                                                                           |

|             | I/UP   |               |                                                                           |

|             | I/UP   |               |                                                                           |

| GPIO[4:0]   | I/O/PU | K3, K2,       | General Purpose I/O: The 5 GPIOs can be programmed for special            |

|             |        | K1, J4, J3    | application. (Note: The function is not released to user normally. Please |

|             |        |               | contact with ASIX directly if any requirement)                            |

| VDD33       | Р      |               | 3.3V +/-5% Supply Voltage.                                                |

|             |        | J17, P4, U7   |                                                                           |

| VDD18       | Р      | D7, H4, N4,   | 1.8V +/-5% Supply Voltage.                                                |

|             |        | N17, U8, U13  |                                                                           |

| AVDD18      | Р      |               | 1.8V +/-5% Supply Voltage for PLL.                                        |

| VSS         | Р      | D12, J9, J10, | Ground                                                                    |

|             |        | J11, J12, K4, |                                                                           |

|             |        | K9, K10, K11, |                                                                           |

|             |        | K12, L4, L9,  |                                                                           |

|             |        | L10, L11,     |                                                                           |

|             |        | L12,, M9,     |                                                                           |

|             |        | M10, M11,     |                                                                           |

|             |        | M12, N18,     |                                                                           |

|             |        | U15, M18,     |                                                                           |

|             |        | L18, K18      |                                                                           |

# **3.0 Functional Description**

## **3.1 Introduction**

In general, the AX88655AB device is a highly integrated Layer 2 switch. It supports eight 10/100/1000 ports with on-chip MACs. It also supports integrated switching logic, packet queuing memory and packet storage memory. The AX88655AB is capable of routing-and-forwarding packets at wire speed on all ports regardless of packet size. It is a low cost solution for eight ports Gigabit Ethernet backbone switch design. No CPU interface is required; After

It is a low cost solution for eight ports Gigabit Ethernet backbone switch design. No CPU interface is required; After power on reset, AX88655AB provide an auto load configuration setting function through a 2 wire serial EEPROM interface to access external EEPROM device, and AX88655AB can easily be configured to support trunking, QoS, IEEE 802.3x flow control threshold setting, broadcast storm control ...etc functions. An overview of AX88655AB's major functional blocks is shown in Fig-1.

## **3.2 Packet Filtering and Forwarding Process**

The switch use simple store-and-forward algorithm as packet switching method. After receives incoming packets, the packets will be stored to the embedded memory first. The AX88655AB searches in the Address-Lookup Table with DA of the packet. The packet will be forward to its destination port, if this packet's DA hits; otherwise this packet will be broadcasted. Of course, only good packets will be forward.

## 3.3 MAC Address Routing, Learning and Aging Process

The switch supports 4K MAC entries for switching. Two-way dynamic address learning is performed by each good unicast packet is completely received. And linear/XOR hash algorithm of the static address learning is achieved by EEPROM configuration. On the other hand, the routing process is performed whenever the packet's DA is captured. If the DA can not get a hit result, the packet is going to broadcast.

Only the learned address entries are scheduled in the aging machine. If one station does not transmit any packet for a period of time, the belonging MAC address will be kicked out from the address table. The aging out time can be program automatically through the EEPROM configuration. (Default value is 300 seconds)

## 3.4 Full Duplex 802.3x Flow Control

In full duplex mode, AX88655AB supports the standard flow control mechanism defined in IEEE 802.3x standard. It enables the stopping of remote node transmissions via a PAUSE frame information interaction. When space of the packet buffer is less than the initialization setting threshold value, AX88655AB will send out a PAUSE-ON packet with pause time equal to "xFFF" to stop the remote node transmission. And then AX88655AB will send out a PAUSE-OFF packet with pause time equal to zero to inform the remote node to retransmit packet if has enough space to receive packets.

## 3.5 Half Duplex Back Pressure Control

In half duplex mode, AX88655AB provide a backpressure control mechanism to avoid dropping packets during network conjection situation. When space of the packet buffer is less than the initialization setting threshold value, AX88655AB will send a JAM pattern in the input port when it senses an incoming packet, thus force a collision to make the remote node transmission back off and will effectively avoid dropping packets. And then AX88655AB will not send out a JAM packet any more if has enough space to receive one packet.

## **3.6 MII Polling**

The AX88655AB supports PHY management through the serial MDIO/MDC interface. That is, the AX88655AB access related register of PHYs via MDIO/MDC interface after power on reset. The AX88655AB will periodically and continuously poll and update the link status and link partner's ability which include speed, duplex mode, and 802.3x flow control capable status of the connected PHY devices through MDIO/MDC serial interface.

# 3.7 Port-Based QoS: Port-Pair

AX88655AB provides 4 Port-Pairs for bandwidth management. Users can assign any two ports as one Port-Pair with internal registers basically. Any packets will put the high priority queue of the Port-Pair when send the packets each other. That is, two ports of each Port-Pair will obtain more bandwidth than other ports when congestion.

In addition, one port can be as the highest priority port if one All\_Bit of a Port-Pair is active. That is, user can assign format of the Port-Pair as OnePort-to-All and every packets of the OnePort will put in the high priority transmit queue of other ports.

## 3.8 VLAN and Broadcast Storming Prevention

AX88655AB supports 8 port-based VLAN groups to ease the administration of logical groups of stations that can communicate as if they were on the same LAN, and move, add or change numbers of these groups. The scheme can prevent effectively the broadcast storming from interfering with the whole transmission performance between ports. During this time, the ports belonging to different groups are independent. Only the destination port of broadcast packets in the same group will be allowed. Furthermore, the scheme of the VLAN group dividing is very flexible. The overlapped port-groups are allowed during some operations, for example, one port can be shared by two groups, and all the other operations between these two groups remain independent except for the overlapped port. Only the overlapped port could use the same destination MAC address for two different VLAN port-groups.

The AX88655AB can enable broadcast storm filtering control by MaxStorm[1:0]. This allows limitation of the number of broadcast packets into the switch, and can be implemented on a per port basis. The threshold of number of broadcast packets is set to 64/32/16. When enabled (i.e., MaxStorm[1:0] is not 2'b00), each port will drop broadcast packets (Destination MAC ID is ff after receiving 64 continuous broadcast packets. The counter will be reset to 0 every 1 second or when receiving any non-broadcast packets (Destination MAC ID is not ff ff ff ff ff ff).

When disabled (i.e., MaxStorm[1:0] is 2'b00), or the number of non-unicast packets received at the port is not over the programmed threshold, the switch will forward the packet to all the ports (except the receiving port) within the VLANs specified at the receiving port.

If Broadcast-Storm-drop is enabled, the AX88655ABB will only drop broadcast packets but not the multicast packets.

## 3.9 Security Operation - Port SA restriction

AX88655AB provides source MAC address security support. When OneSaSecurityMode is turned on, then the port(s) will be fixed in the secured SA and stop learning. The port(s) will forward packets with the matched SA. If any other ports receive the packet with this secures SA, this packet will be discarded. Learns a source MAC address again if UpdateSaForSecurity is turned on.

## 3.10 Ingress/Egress Bandwidth Control Scheme

The bandwidth control will set the maximum bandwidth that each port can support. Basically AX88655AB provides 256 bandwidth classes of 1000 Mbps with thresholds (ResolutionIngress and ResolutionEngress). In half-duplex mode, the receiving side (ingress) will drop packets or send JAM with IgressMode if it is over the bandwidth threshold. On the transmitting side (egress), if it goes over the threshold, it will stop transmitting until time is up, then transmit data again. Under full-duplex mode, if the transmitting data meet the bandwidth threshold, the bandwidth control scheme will send the drop packets or 802.3x PAUSE frame. When it expires, it will send the release packet. For the receiving side without flow control (802.3x), it will drop the packet if it goes over the threshold.

## 3.11 Port Mirroring

Port mirroring is a function that mirrors or duplicates traffic from one "target port" to a "mirror port". The mirror or target port mirroring can be set up for each port individually to mirror either incoming packets or outgoing packets. Incoming and outgoing traffic need not be mirrored to the same port. Unidirectional traffic on a port can only be mirrored to one mirror port. Only correct packets that would normally be handled by the AX88655AB will be mirrored. Packets with CRC errors and collision fragments etc are **not** mirrored.

- Input mirroring: Traffic received on a port will be sent to the mirror port as well as to any other addressed port.

- **Output mirroring:** Traffic sent out on a port will also be sent to the mirror port.

# **4.0 Register Descriptions**

Register Tables Summary:

| Address | 15                            | 14              | 13      | 12        | 2                             | 11                            | 10                            | 9      | 8                                                       | 7                                 | 6       | 5      | 4      | 3       | 2       | 1      | 0 | Default |

|---------|-------------------------------|-----------------|---------|-----------|-------------------------------|-------------------------------|-------------------------------|--------|---------------------------------------------------------|-----------------------------------|---------|--------|--------|---------|---------|--------|---|---------|

| 00 H    | -                             |                 | -       |           |                               | VEI                           | -                             | -      | -                                                       |                                   |         | -      |        | RVEL    |         |        |   | 0000 H  |

| 01 H    |                               |                 |         | RES       | ER                            | VEI                           | )                             |        |                                                         | RESERVED                          |         |        | FFFF H |         |         |        |   |         |

| 02 H    |                               | RES             | ERV     | <b>ED</b> | + R                           | xFlo                          | wCtrl                         | [4:0]  |                                                         | <b>RESERVED</b> + TxFlowCtrl[4:0] |         |        | 0000 H |         |         |        |   |         |

| 03 H    | I RESERVED                    |                 |         |           |                               |                               |                               |        |                                                         | F                                 | RESE    | RVEL   | )      |         |         | 00FF H |   |         |

| 04 H    | I RESERVED                    |                 |         |           |                               |                               | RESERVED                      |        |                                                         |                                   | 00FF H  |        |        |         |         |        |   |         |

| 05 H    |                               |                 |         |           |                               |                               |                               | ]      | RESE                                                    | ESERVED                           |         |        |        | 0000 H  |         |        |   |         |

| 06 H    |                               |                 |         | RES       | ER                            | VEI                           | )                             |        |                                                         |                                   |         | F      | RESE   | RVEL    | )       |        |   | 00FF H  |

| 07 H    |                               |                 |         | R         | ES                            | ERV                           | ED                            |        |                                                         |                                   |         |        | RE     | SERV    | ED      |        |   | 1215 H  |

| 08 H    | I                             | RESE            | RVE     | D         |                               | F                             | RESE                          | RVE    | D                                                       | ŀ                                 | RESER   | VEI    | )      | F       | RESE    | RVED   | ) | 7777 H  |

| 09 H    | I                             | RESE            | RVE     | D         |                               | F                             | RESE                          | RVE    | D                                                       | ŀ                                 | RESER   | VEI    | )      | F       | RESE    | RVED   | ) | 7777 H  |

| 0A H    |                               |                 |         |           |                               | 1[4:0                         |                               |        |                                                         |                                   |         |        |        | ir0[4:0 | -       |        |   | 0000 H  |

| 0B H    |                               |                 |         |           |                               | 3[4:0                         |                               |        |                                                         |                                   |         |        |        | ir2[4:0 | ]       |        |   | 0000 H  |

| 0C H    | LowQ                          | ueueV           | Veigh   | t[3:0]    | R                             |                               |                               | lw_I   | LowQ                                                    | leueD                             | iscardL | imit   | [9:0]  |         |         |        |   | 1060 H  |

|         |                               |                 |         |           |                               | D                             |                               |        |                                                         |                                   |         |        |        |         |         |        |   |         |

|         |                               |                 |         |           |                               |                               |                               |        | hQueueDiscardLimit [9:0]                                |                                   |         |        | 1060 H |         |         |        |   |         |

|         |                               |                 |         |           | SP                            |                               |                               |        |                                                         | 8880 H                            |         |        |        |         |         |        |   |         |

| 0F H    |                               |                 |         | ESEI      |                               |                               |                               | 1      |                                                         | MaxAge[8:0]                       |         |        |        | 1865 H  |         |        |   |         |

| 10 H    |                               | nk47[           | 2:0]    |           |                               | k30[                          |                               |        | RESERVED                                                |                                   |         |        | 00C0 H |         |         |        |   |         |

| 11 H    | RES                           |                 |         |           |                               | RVEI                          | )                             |        | LowQueueFlowCtrlMark[9:0]<br>HighQueueFlowCtrlMark[9:0] |                                   |         |        | 0010 H |         |         |        |   |         |

| 12 H    |                               |                 | MaxJ    |           |                               |                               |                               |        |                                                         |                                   |         |        |        |         |         |        |   | 2810 H  |

| 13 H    |                               |                 | RES     |           |                               |                               |                               |        |                                                         |                                   | _LowQu  |        |        | -       |         |        |   | 0070 H  |

| 14 H    | RES                           | Smart<br>[1:0   |         | RES       |                               | RES<br>E                      | ERV<br>D                      |        | hw_HighQueueDiscardLimit[9:0]                           |                                   |         |        |        | 0070 H  |         |        |   |         |

| 15 H    |                               | Po              | ort-ba  | sed '     | VLA                           | AN G                          | roup                          | #1     |                                                         |                                   | Port    | t-bas  | ed VL  | LAN G   | roup    | #0     |   | 0000 H  |

| 16 H    |                               | Po              | ort-ba  | sed '     | VLA                           | AN G                          | roup                          | #3     |                                                         | Port-based VLAN Group #2          |         |        |        | 0000 H  |         |        |   |         |

| 17 H    |                               |                 |         | RES       | ER                            | VEI                           | )                             |        |                                                         | Port-based VLAN Group #4          |         |        |        | 0000 H  |         |        |   |         |

| 18 H    |                               |                 |         | RES       | ER                            | VEI                           | )                             |        |                                                         | RESERVED                          |         |        |        | 0000 H  |         |        |   |         |

| 19 H    | ResolutionIngress Port 1[7:0] |                 |         |           |                               |                               | ResolutionIngress Port 0[7:0] |        |                                                         |                                   | FFFF H  |        |        |         |         |        |   |         |

| 1A H    | ResolutionIngress Port 3[7:0] |                 |         |           | ResolutionIngress Port 2[7:0] |                               |                               | FFFF H |                                                         |                                   |         |        |        |         |         |        |   |         |

| 1B H    |                               |                 |         |           |                               | ResolutionIngress Port 4[7:0] |                               |        | FFFF H                                                  |                                   |         |        |        |         |         |        |   |         |

| 1C H    |                               |                 |         |           |                               | RESERVED                      |                               |        |                                                         | FFFF H                            |         |        |        |         |         |        |   |         |

| 1D H    | iso                           | rm <sup>M</sup> | lirrorP | ort[2:    | 0] P                          | ortMi<br>1:                   |                               | Ingre  | ssMode                                                  |                                   | Reso    | lutio  | nEng   | ress Po | ort 7[7 | 7:0]   |   | 00FF H  |

| 1E H    | RE                            | SERV            |         |           |                               |                               |                               |        | 4:0]                                                    |                                   | SERV    |        |        |         |         |        |   | 0000 H  |

| 1F H    | I GCLK125MHz_Dly1ns_n[7:0]    |                 |         |           |                               | Targe                         | tPort[2:0]                    | ] Ju   | mboLe                                                   | ng13_10                           | )[3:0]  | JumboE | Inable | 0000 H  |         |        |   |         |

Note:

- 1. The word "Reserved" = "Res." on the above table.

- 2. Care must be taken that the "Reserved" registers should keep the default value always. Change of any reserved value may be resulting in unpredictable conditions.

- 3. The registers can be accessed by internal MPU only. The MPU will read in configuration table, located on EEPROM at somewhere address, and programs the above registers when every time power on or after system reset.

- 4. Basically, the registers can be accessed with the same data format as station management (similar to MDC and MDIO) via ADC and ADIO pins.

#### 4.1 Register 00

| BIT  | R/W | DESCRIPTION |

|------|-----|-------------|

| 15:8 | R/W | RESERVED    |

| 7:0  | R/W | RESERVED    |

## 4.2 Register 01

| BIT  | R/W | DESCRIPTION |

|------|-----|-------------|

| 15:8 | R/W | RESERVED    |

| 7:0  | R/W | RESERVED    |

#### 4.3 Register 02

| BIT     | R/W | DESCRIPTION                                                                             |

|---------|-----|-----------------------------------------------------------------------------------------|

| 15:12,8 | R/W | FlowCtrlEnable for MAC's receive part of Port[4:0] are configured by int. or ext. 8051  |

|         |     | 0: not identify PAUSE frames by receive part of MAC                                     |

|         |     | 1: can identify PAUSE frames. That is, PauseTimer of MAC will be active.                |

| 7:4,0   | R/W | FlowCtrlEnable for MAC's transmit part of Port[4:0] are configured by int. or ext. 8051 |

|         |     | 0: not send PAUSE frames                                                                |

|         |     | 1: send PAUSE frames when the packet buffer run out.                                    |

#### 4.4 Register 03

| BIT  | R/W | DESCRIPTION |

|------|-----|-------------|

| 15:8 | R/W | RESERVED    |

| 7:0  | R/W | RESERVED    |

#### 4.5 Register 04

| BIT  | R/W | DESCRIPTION |

|------|-----|-------------|

| 15:8 | R/W | RESERVED    |

| 7:0  | R/W | RESERVED    |

#### 4.6 Register 05

| BIT  | R/W | DESCRIPTION |

|------|-----|-------------|

| 15:0 | R   | RESERVED    |

#### 4.7 Register 06

| BIT   | R/W | DESCRIPTION |

|-------|-----|-------------|

| 15:10 | R/W | RESERVED    |

| 9:0   | R/W | RESERVED    |

### 4.8 Register 07

| BIT  | R/W | DESCRIPTION |

|------|-----|-------------|

| 15   | R/W | RESERVED    |

| 14:8 | R/W | RESERVED    |

| 7    | R/W | RESERVED    |

| 6:0  | R/W | RESERVED    |

WWW DataSheet4U.com ASIX ELECTRONICS CORPORATION

#### 4.9 Register 08

| BIT   | R/W | DESCRIPTION |

|-------|-----|-------------|

| 15:12 | R/W | RESERVED    |

| 11:9  | R/W | RESERVED    |

| 8:4   | R/W | RESERVED    |

| 3:0   | R/W | RESERVED    |

### 4.10 Register 09

| BIT   | R/W | DESCRIPTION |

|-------|-----|-------------|

| 15:12 | R/W | RESERVED    |

| 11:9  | R/W | RESERVED    |

| 8:4   | R/W | RESERVED    |

| 3:0   | R/W | RESERVED    |

### 4.11 Register 0A

| BIT   | R/W | DESCRIPTION                                |

|-------|-----|--------------------------------------------|

| 15    | R/W | All_Bit of PortPair #1 when QoS[0] is high |

| 14:12 | R/W | Port_ID of PortPair #1 when QoS[0] is high |

| 11    | R/W | All_Bit of PortPair #1 when QoS[0] is high |

| 10:8  | R/W | Port_ID of PortPair #1 when QoS[0] is high |

| 7     | R/W | All_Bit of PortPair #0 when QoS[0] is high |

| 6:4   | R/W | Port_ID of PortPair #0 when QoS[0] is high |

| 3     | R/W | All_Bit of PortPair #0 when QoS[0] is high |

| 2:0   | R/W | Port_ID of PortPair #0 when QoS[0] is high |

#### 4.12 Register 0B

| BIT   | R/W | DESCRIPTION                                |

|-------|-----|--------------------------------------------|

| 15    | R/W | All_Bit of PortPair #3 when QoS[0] is high |

| 14:12 | R/W | Port_ID of PortPair #3 when QoS[0] is high |

| 11    | R/W | All_Bit of PortPair #3 when QoS[0] is high |

| 10:8  | R/W | Port_ID of PortPair #3 when QoS[0] is high |

| 7     | R/W | All_Bit of PortPair #2 when QoS[0] is high |

| 6:4   | R/W | Port_ID of PortPair #2 when QoS[0] is high |

| 3     | R/W | All_Bit of PortPair #2 when QoS[0] is high |

| 2:0   | R/W | Port_ID of PortPair #2 when QoS[0] is high |

#### 4.13 Register 0C

| BIT   | R/W | DESCRIPTION                                                                         |

|-------|-----|-------------------------------------------------------------------------------------|

| 15:12 | R/W | WeightForLowQue: Weight for low priority queues when QoS is active (see Appendix C) |

| 11:10 | R/W | Reserved                                                                            |

| 9:0   | R/W | LowWaterMark of low priority queues when drop packets                               |

#### 4.14 Register 0D

| BIT   | R/W | DESCRIPTION                                                                            |

|-------|-----|----------------------------------------------------------------------------------------|

| 15:12 | R/W | WeightForHighQue: Weight for high priority queues when QoS is active (see Appendix C)  |

| 11:10 | R/W | Maximum number of broadcast frames that can be accumulated in each input frame buffer. |

|       |     | 00: disable broadcast storm control                                                    |

|       |     | 01: 31 frames                                                                          |

|       |     | 10: 47 frames                                                                          |

|       |     | 11: 63 frames                                                                          |

| 9:0   | R/W | LowWaterMark of high priority queues when drop packets                                 |

## 4.15 Register 0E

| BIT   | R/W | DESCRIPTION                                                                             |

|-------|-----|-----------------------------------------------------------------------------------------|

| 15    | RO  | RESERVED                                                                                |

| 14    | R/W | 802.3x Flow control frame recognition control                                           |

|       |     | 0: check for MAC control frame DA MAC address in addition to the MAC control type field |

|       |     | 1: check only the MAC control type field                                                |

| 13    | R/W | Setting for maximum length of packet that received                                      |

|       |     | 0: 1518 byte                                                                            |

|       |     | 1: 1522 byte                                                                            |

| 12:11 | R/W | RESERVED                                                                                |

| 10    | R/W | Software Reset (Only reset the switch kernel)                                           |

|       |     | 0: active                                                                               |

|       |     | 1: disable                                                                              |

| 9     | R/W | Back-off algorithm selection                                                            |

|       |     | 0: disable. Device will perform the IEEE standard exponential back off algorithm when a |

|       |     | collision occurs.                                                                       |

|       |     | 1: enable. When collisions occur, the MACs will back off up to 7 slots.                 |

|       |     | Note :: SuperMac v.s. FlowCtrl                                                          |

| 8     | R/W | 0: stop generate JAM patterns after some collision that is defined by MaxJam[5:0]       |

|       |     | 1: Never stop back-pressure (Note: Only available for EthernetNot FastEternet)          |

| 7     | R/W | RESERVED                                                                                |

| 6     | R/W | RESERVED                                                                                |

| 5   | R/W | RESERVED                                                                                      |

|-----|-----|-----------------------------------------------------------------------------------------------|

| 4:3 | R/W | QoS selection                                                                                 |

|     |     | 00: disable QoS function                                                                      |

|     |     | 01: Port-Pair Priority algorithm                                                              |

|     |     | 10: 802.1p                                                                                    |

| 2   | R/W | AgingEnable Switch Table Entry Aging Control. Only the dynamically learned addresses          |

|     |     | will be aged. All explicit entries will not age. The aging time is programmed in register 0F. |

|     |     | 0: disable. The table aging process is disabled.                                              |

|     |     | 1: enable. The table aging process is enabled and a hardware process ages every               |

|     |     | dynamically learned table entry.                                                              |

| 1   | R/W | Hash algorithm selection                                                                      |

|     |     | 0: XOR mapping                                                                                |

|     |     | 1: Linear mapping                                                                             |

| 0   | R/W | RESERVED                                                                                      |

### 4.16 Register 0F

| BIT  | R/W | DESCRIPTION                                                                                               |

|------|-----|-----------------------------------------------------------------------------------------------------------|

| 15:9 | R/W | IPG1 for transmit part of all MII MACs                                                                    |

| 8:0  |     | MaxAge. This is a seven-bit register containing unsigned integer for determining the address-aging timer. |

### 4.17 Register 10

| BIT   | R/W | DESCRIPTION                                           |

|-------|-----|-------------------------------------------------------|

| 15:13 | R/W | Trunking selection for Port[7:4]                      |

|       |     | 000: disable trunking                                 |

|       |     | 001: disable trunking                                 |

|       |     | 010: one 2-Port Trunking for Port[5:4]                |

|       |     | 011: one 2-Port Trunking for Port[5:4]                |

|       |     | 100: one 2-Port Trunking for Port[7:6]                |

|       |     | 101: one 4-Port Trunking                              |

|       |     | 110: two 2-Port Trunkings for Port[7:6] and Port[5:4] |

|       |     | 111: one 4-Port Trunking                              |

| 12:10 | R/W | Trunking selection for Port[3:0]                      |

|       |     | 000: disable trunking                                 |

|       |     | 001: disable trunking                                 |

|       |     | 010: one 2-Port Trunking for Port[1:0]                |

|       |     | 011: one 2-Port Trunking for Port[1:0]                |

|       |     | 100: one 2-Port Trunking for Port[3:2]                |

|       |     | 101: one 4-Port Trunking                              |

|       |     | 110: two 2-Port Trunkings for Port[3:2] and Port[1:0] |

|       |     | 111: one 4-Port Trunking                              |

| 9:0   | R/W | Reserved                                              |

### 4.18 Register 11

| BIT   | R/W | DESCRIPTION                                                                                                                               |

|-------|-----|-------------------------------------------------------------------------------------------------------------------------------------------|

| 15:10 | R/W | Reserved                                                                                                                                  |

| 9:0   |     | LowWaterMarkForFlowCtrl. This is a ten-bit register containing unsigned integer for low priority queues whether generate PAUSE-ON or not. |

#### 4.19 Register 12

| BIT   | R/W | DESCRIPTION                                                                               |

|-------|-----|-------------------------------------------------------------------------------------------|

| 15:10 | R/W | MaxJam. This is a six-bit register containing unsigned integer for determining the JAM    |

|       |     | counter whether generate JAM or not.                                                      |

| 9:0   | R/W | HighWaterMarkForFlowCtrl. This is a ten-bit register containing unsigned integer for high |

|       |     | priority queues whether generate PAUSE-OFF or not.                                        |

#### 4.20 Register 13

| BIT   | R/W | DESCRIPTION                                            |

|-------|-----|--------------------------------------------------------|

| 15:10 | R/W | Reserved                                               |

| 9:0   | R/W | HighWaterMark of low priority queues when drop packets |

#### 4.21 Register 14

| BIT   | R/W | DESCRIPTION                                             |

|-------|-----|---------------------------------------------------------|

| 15    | R/W | RESERVED                                                |

| 14:13 | R/W | SmartFlowCtrl for mix-speed connection                  |

|       |     | 0: disable                                              |

|       |     | 1: disable flow ctrl for all 10 Mbps port               |

|       |     | 2: disable flow ctrl for all 100 Mbps port              |

|       |     | 3: reserved                                             |

| 12    | R/W | RESERVED                                                |

| 11:10 | R/W | Reserved                                                |

| 9:0   | R/W | HighWaterMark of high priority queues when drop packets |

#### 4.22 Register 15

| BIT  | R/W | DESCRIPTION |

|------|-----|-------------|

| 15:8 | R/W | VLAN #1     |

| 7:0  | R/W | VLAN #0     |

### 4.23 Register 16

| BIT  | R/W | DESCRIPTION |  |  |  |  |

|------|-----|-------------|--|--|--|--|

| 15:8 | R/W | VLAN #3     |  |  |  |  |

| 7:0  | R/W | VLAN #2     |  |  |  |  |

#### 4.24 Register 17

| BIT  | R/W | DESCRIPTION |  |  |  |  |

|------|-----|-------------|--|--|--|--|

| 15:8 | R/W | RESERVED    |  |  |  |  |

| 7:0  | R/W | VLAN #4     |  |  |  |  |

#### 4.25 Register 18

| BIT  | R/W | DESCRIPTION |  |  |  |  |

|------|-----|-------------|--|--|--|--|

| 15:8 | R/W | RESERVED    |  |  |  |  |

| 7:0  | R/W | RESERVED    |  |  |  |  |

#### 4.26 Register 19

| BIT  | R/W | DESCRIPTION                                         |  |  |  |

|------|-----|-----------------------------------------------------|--|--|--|

| 15:8 | R/W | Resolution of port #1 for ingress bandwidth control |  |  |  |

| 7:0  | R/W | Resolution of port #0 for ingress bandwidth control |  |  |  |

#### 4.27 Register 1A

| BIT  | R/W | DESCRIPTION                                         |  |  |  |

|------|-----|-----------------------------------------------------|--|--|--|

| 15:8 | R/W | Resolution of port #3 for ingress bandwidth control |  |  |  |

| 7:0  | R/W | Resolution of port #2 for ingress bandwidth control |  |  |  |

#### 4.28 Register 1B

| BIT  | R/W | DESCRIPTION                                         |  |  |  |

|------|-----|-----------------------------------------------------|--|--|--|

| 15:8 | R/W | RESERVED                                            |  |  |  |

| 7:0  | R/W | Resolution of port #4 for ingress bandwidth control |  |  |  |

#### 4.28 Register 1C

| BIT  | R/W | DESCRIPTION |  |  |  |  |  |

|------|-----|-------------|--|--|--|--|--|

| 15:8 | R/W | RESERVED    |  |  |  |  |  |

| 7:0  | R/W | RESERVED    |  |  |  |  |  |

#### 4.28 Register 1D

| BIT   | R/W | DESCRIPTION                                        |

|-------|-----|----------------------------------------------------|

| 15    | R/W | Isolation Enable for Port-based Mirror             |

|       |     | 0: disable                                         |

|       |     | 1: active                                          |

| 14    | R/W | ResolutionMode                                     |

|       |     | 0: Byte mode                                       |

|       |     | 1: Word mode                                       |

| 13:11 | R/W | Mirror Port for Port-based Mirror                  |

| 10:9  | R/W | Port-based Mirror Mode                             |

|       |     | 0: disable Port-based Mirror                       |

|       |     | 1: Imgress                                         |

|       |     | 2: Egress                                          |

|       |     | 3: Reserved                                        |

| 8     | R/W | Igress Mode                                        |

|       |     | 0: drop pkts by ARL                                |

|       |     | 1: send Pause for GmacTx                           |

| 7:0   | R/W | Resolution of port #7 for egress bandwidth control |

#### 4.28 Register 1E

| BIT     | R/W | DESCRIPTION                                      |  |  |  |  |  |

|---------|-----|--------------------------------------------------|--|--|--|--|--|

| 15:12,8 | R/W | Jpdate Source MAC For Security Mode of each Port |  |  |  |  |  |

|         |     | keep one Source MAC                              |  |  |  |  |  |

|         |     | update the Source MAC                            |  |  |  |  |  |

| 7:4,0   | R/W | OneSaSecurityMode[4:0]                           |  |  |  |  |  |

|         |     | 0: disable                                       |  |  |  |  |  |

|         |     | 1: active                                        |  |  |  |  |  |

### 4.28 Register 1F

| BIT     | R/W | DESCRIPTION                                     |  |  |  |  |  |

|---------|-----|-------------------------------------------------|--|--|--|--|--|

| 15:12,8 | R/W | GCLK125MHz_Dly_1ns_n[4:0]                       |  |  |  |  |  |

|         |     | ): Delay 1ns                                    |  |  |  |  |  |

|         |     | no delay                                        |  |  |  |  |  |

| 7:5     | R/W | rget Port for Port-based Mirror                 |  |  |  |  |  |

| 4:1     | R/W | Max Length of Jumbo Packet: from 1K to 15K Byte |  |  |  |  |  |

| 0       | R/W | Accept Jumbo Enable                             |  |  |  |  |  |

|         |     | ): drop jumbo packets                           |  |  |  |  |  |

|         |     | 1: accept jumbo packets                         |  |  |  |  |  |

# 5.0 ELECTRICAL SPECIFICATION AND TIMING

## **5.1 Absolute Maximum Ratings**

| Description                                     | SYM  | Min  | Max     | Units |

|-------------------------------------------------|------|------|---------|-------|

| Operating Temperature                           | Та   | 0    | +70     | °C    |

| Storage Temperature                             | Ts   | -55  | +150    | °C    |

| Supply Voltage                                  | Vcc  | -0.3 | +4.0    | V     |

| Input Voltage                                   | Vin  | -0.3 | Vdd+0.5 | V     |

| Output Voltage                                  | Vout | -0.3 | Vdd+0.5 | V     |

| Lead Temperature (soldering 10 seconds maximum) | Tl   | -55  | +220    | °C    |

Note: Stress above those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to Absolute Maximum Ratings conditions for extended period, adversely affect device life and reliability

## **5.2 General Operation Conditions**

| Description           | SYM | Min  | Max  | Units |

|-----------------------|-----|------|------|-------|

| Operating Temperature | Та  | 0    | +70  | °C    |

| Supply Voltage        | Vdd | +3.0 | +3.6 | V     |

## **5.3 DC Characteristics**

(Vdd=3.0V to 3.6V, Vss=0V, Ta=0°C to 70°C)

| Description                      | SYM  | Min     | Max     | Units |

|----------------------------------|------|---------|---------|-------|

| Low Input Voltage                | Vil  | Vss-0.3 | 0.8     | V     |

| High Input Voltage               | Vih  | 2       | Vdd+0.5 | V     |

| Low Output Voltage               | Vol  |         | 0.4     | V     |

| High Output Voltage              | Voh  | 2.4     |         | V     |

| Input Leakage Current 1 (Note 1) | Iil1 |         | 10      | uA    |

| Input Leakage Current 2 (Note 2) | Iil1 |         | 500     | uA    |

| Output Leakage Current           | Iol  |         | 10      | uA    |

| Description       | SYM | Min | Тру | Max | Units |

|-------------------|-----|-----|-----|-----|-------|

| Power Consumption | Pc  |     | TBD |     | mA    |

Note:

- 1. All the input pins without pull low or pull high.

- 2. Those pins had been pull low or pull high.

## **5.4 AC specifications**

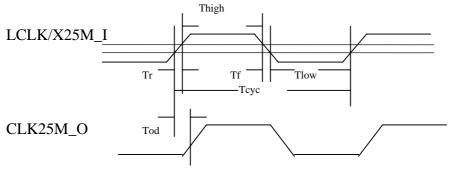

## 5.4.1 LCLK

| Symbol | Description             | Min | Тур. | Max | Units |

|--------|-------------------------|-----|------|-----|-------|

| Тсус   | CYCLE TIME              |     | 20   |     | ns    |

| Thigh  | CLK HIGH TIME           | 8   | 10   | 12  | ns    |

| Tlow   | CLK LOW TIME            | 8   | 10   | 12  | ns    |

| Tr/Tf  | CLK SLEW RATE           | 1   | -    | 4   | ns    |

| Tod    | LCLK TO BMCLK OUT DELAY |     | 2    |     | ns    |

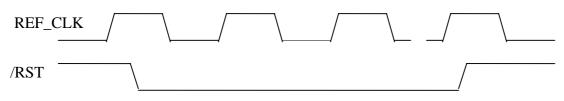

### 5.4.2 Reset Timing

| Symbol | Description       | Min | Тур. | Max | Units   |

|--------|-------------------|-----|------|-----|---------|

| Trst   | Reset pulse width | 10  | -    | -   | REF_Clk |

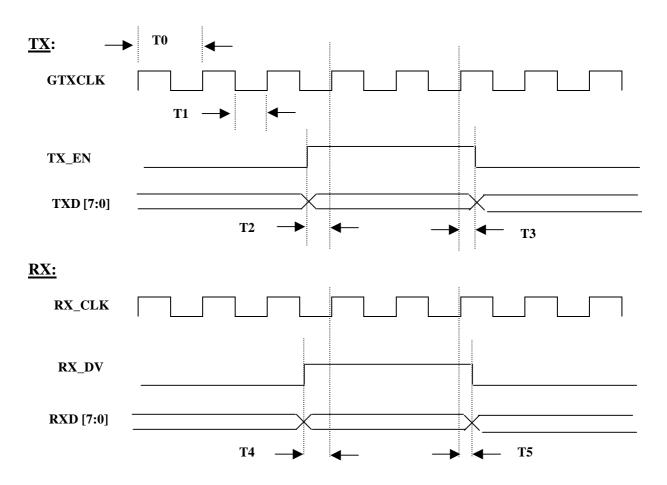

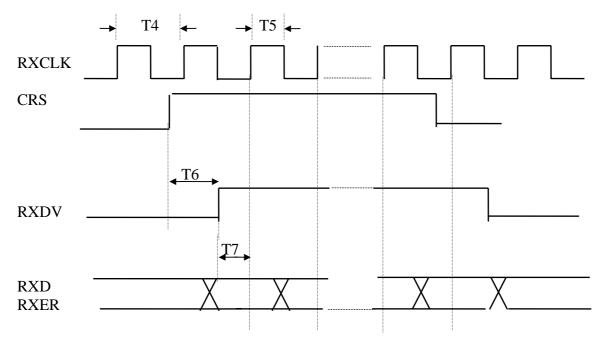

### 5.4.3 GMII Interface Timing TX & RX

| Symbol | Description                                    | Min   | Тур. | Max   | Units |

|--------|------------------------------------------------|-------|------|-------|-------|

| T0     | REF_CLK Clock Cycle Time                       | 7.998 | 8    | 8.002 | ns    |

| T1     | REF_CLK Clock High Time                        |       | 4    |       | ns    |

| T2     | TX_EN and TXD data setup to REF_CLK rising     | 2.5   |      |       | ns    |

|        | edge                                           |       |      |       |       |

| T3     | TX_EN and TXD data hold from REF_CLK rising    | 0.5   |      |       | ns    |

|        | edge                                           |       |      |       |       |

| T4     | RX_DV and RXD data setup to RX_CLK rising edge | 2.0   |      |       | ns    |

|        | (RCVR)                                         |       |      |       |       |

| T5     | RX_DV and RXD data hold from RX_CLK rising     | 0     |      |       | ns    |

|        | edge(RCVR)                                     |       |      |       |       |

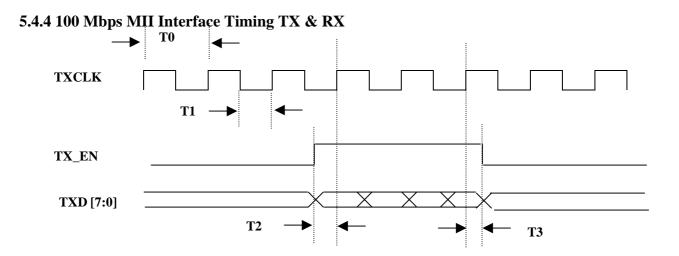

| Symbol | Description                 | Min    | Тур. | Max    | Units |

|--------|-----------------------------|--------|------|--------|-------|

| T0     | TX_CLK Cycle Time           | 39.996 | 40   | 40.004 | ns    |

| T1     | TX_CLK High Time            | 14     | 20   | 26     | ns    |

| T2     | TX_EN Delay from TXCLK High | 7.440  |      | 21.760 | ns    |

| T3     | TXD Delay from TX_CLK High  | 3.410  |      | 13.320 | ns    |

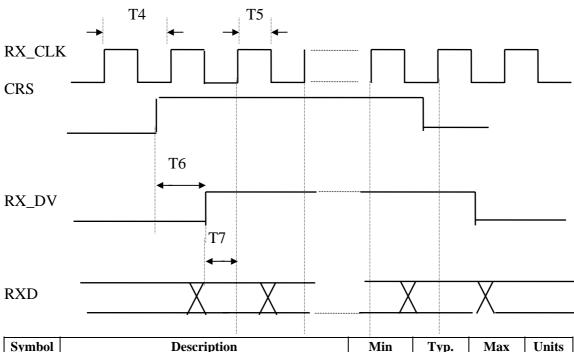

| Symbol | Description                            | Min    | Тур. | Max    | Units |

|--------|----------------------------------------|--------|------|--------|-------|

| T4     | RX_CLK Clock Cycle Time                | 39.996 | 40   | 40.004 | ns    |

| T5     | RX_CLK Clock High Time                 | 14     | 20   | 26     | ns    |

| T6     | CRS to RX_DV Delay Requirement         | 40     |      | 160    | ns    |

| T7     | RXD or RX_DV setup to RX_CLK rise time | 10     |      |        | ns    |

www.DataSheet4U.com ASIX ELECTRONICS CORPORATION

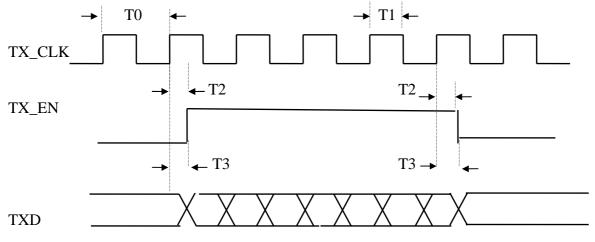

## 5.4.5 10 Mbps MII Interface Timing Tx & Rx

| Symbol | Description                  | Min    | Тур. | Max    | Units |

|--------|------------------------------|--------|------|--------|-------|

| T0     | TX_CLK Cycle Time            | 399.96 | 400  | 400.04 | ns    |

| T1     | TX_CLK High Time             | 14     | 20   | 26     | ns    |

| T2     | TX_EN Delay from TX_CLK High | 7.440  |      | 21.760 | ns    |

| T3     | TXD Delay from TX_CLK High   | 3.410  |      | 13.320 | ns    |

| Symbol | Description                            | Min    | Тур. | Max    | Units |

|--------|----------------------------------------|--------|------|--------|-------|