Document No: AX88782\_783/V1.05/04/27/12

### Features

### High Performance Non-PCI Interface

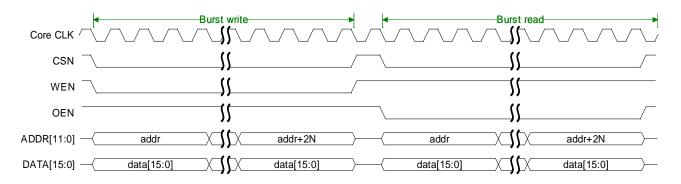

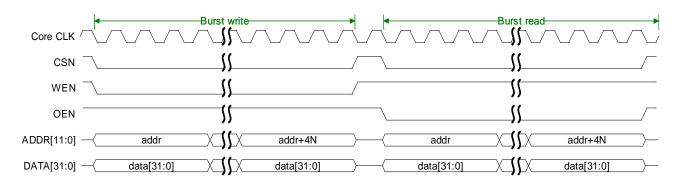

- Configurable 8/16/32-bit SRAM-like host interface, easily interfaces with most common embedded MCUs (AX88782: 8/16-bit, AX88783: 8/16/32-bit)

- Supports PPPoE/IPv4 IP/TCP/UDP/ICMP/ IGMP checksum offload to relieve CPU loading

- Supports burst-mode access, minimizing CPU overhead

### Fast Ethernet MAC + PHY

- IEEE 802.3 10Base-T/100Base-TX compatible

- Supports Full Duplex operation with IEEE 802.3x flow control and Half Duplex with backpressure

- 10/100M PHY supports twisted pair crossover detection and auto-correction (HP Auto-MDIX)

- Supports Wake-on-LAN by Microsoft Wakeup Frame, Magic Packet and link status change detection

### Switching Fabric

- Performs non-blocking wire-speed forwarding and filtering

- Embeds 32KB SRAM for packet buffering

- Supports broadcast storm filtering

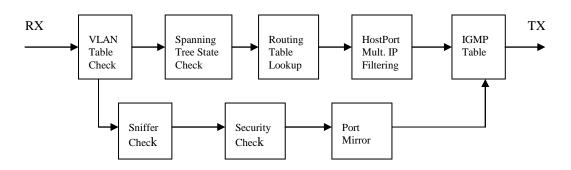

- Supports per queue and per port ingress and egress programmable rate limit control

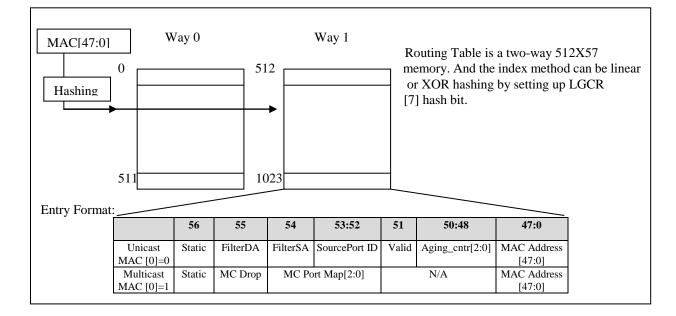

- Integrates two-way Address-Lookup engine and table for 1K MAC addresses

- Supports Routing Table/IGMP/VLAN Table access through CPU read/write operation

- Supports 802.1D Spanning Tree Protocol and 802.1w Rapid Spanning Tree Protocol

### QoS

- Supports Quality-of-Service for Port-Based, 802.1p VLAN and IPv4 TOS/IPv6 COS packets with four priority queues

- Supports RFC2475 DiffServ-based

- VLAN

- Supports up to 3 VLAN groups for port-based VLAN and 16 VLAN entries for 802.1Q tag-based VLAN functions

- Supports the Double tagging 802.1Q-in-802.1Q Function for WAN access

#### Security

- Supports ingress port security mode, incoming packets with unknown source MAC address could be dropped

- Supports eight Security MAC Registrations

- Supports 802.1X port-based Authorization

#### Multicast

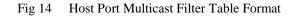

- Supports GMRP/GVRP/GARP packet snooping

- Support IPv4 IGMP and IPv6 ICMP/MLD (Multicast Listener Discovery) Snooping

- Supports up to 1K Multicast Group (shared with L2 MAC table)

- Supports eight IGMP Multicast IP address snooping

#### Monitoring

- Supports RMON group 1, 2, 3 and 9 counter (RFC1213)

- Supports Ethernet-like MIB counter (RFC 1643)

- Supports Bridge MIB counter (RFC 1493)

- Egress/Ingress Port Mirroring

- Sniffer functions:

- Source/Destination Port

- DA/SA

- 🔷 VLAN ID

- Ethernet Packet Type

- IPv4/IPv6 Protocol

- IPv4/IPv6 TCP/UDP Port Number

### Optional Interfaces Supported:

- Optional serial EEPROM

- MII or Reverse-MII (AX88783 only)

- RMII or Reverse-RMII (AX88783 only)

- Optional GPIO/GPI/GPO (AX88783 only)

- Single 3.3V power supply with options for 1.8V, 2.5V and 3.3V I/O voltage support

- Integrated an on-chip voltage regulator requiring only a single power supply of 3.3V

- Integrates an on-chip oscillator and PLL requiring only a 25MHz crystal to operate

- Integrates on-chip power-on reset circuit

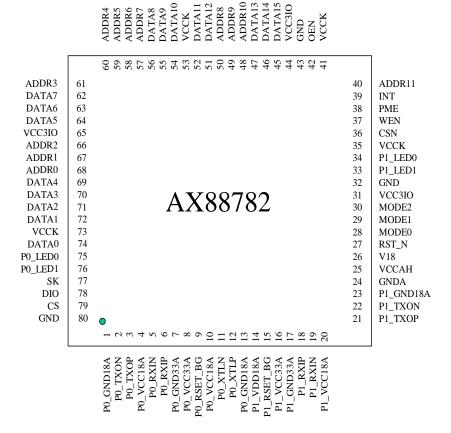

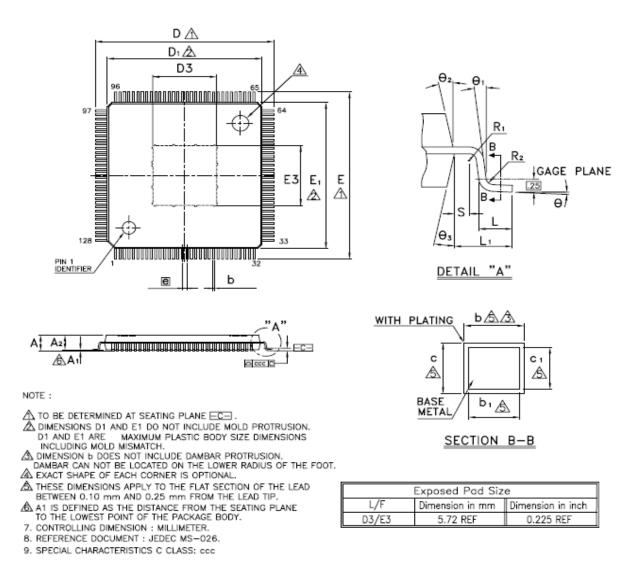

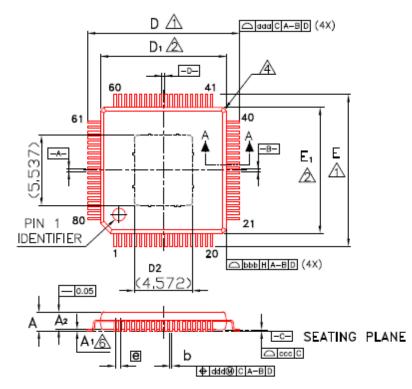

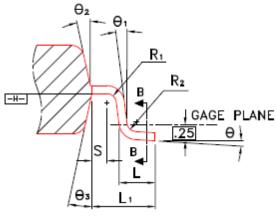

- Small form factor: 80-pin E-PAD LQFP (AX88782) or 128-pin E-PAD LQFP (AX88783) RoHS compliant package

- Operating temperature range: 0°C to 70°C

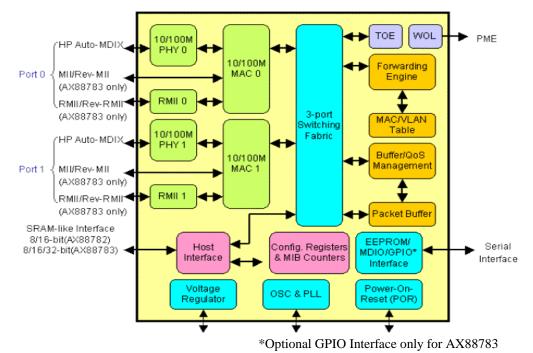

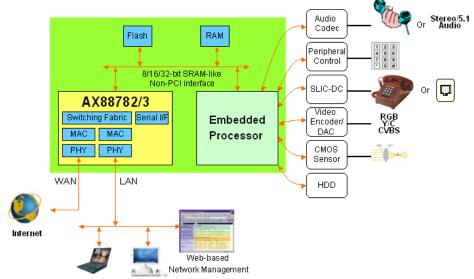

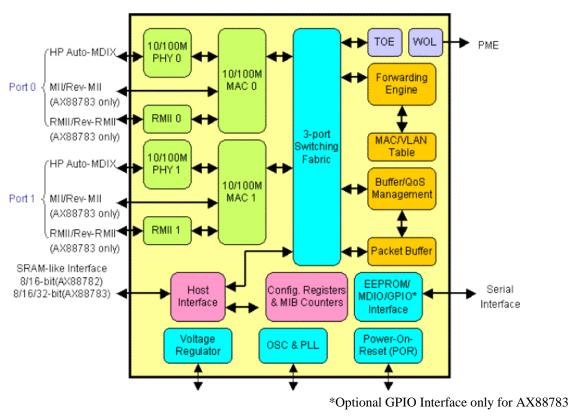

### **Product Description**

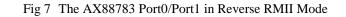

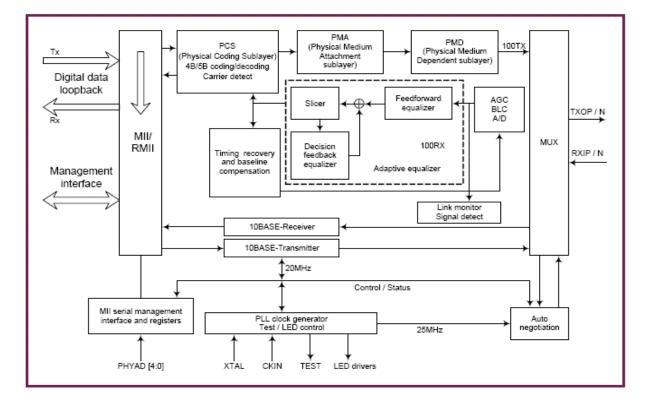

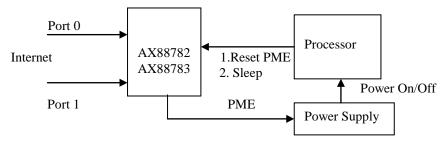

The AX88782/AX88783 is a non-PCI 2-port 10/100M Ethernet controller with an integrated 3-port switching fabric, three 10/100M MACs, two 10/100M PHYs, and an 8/16/32-bit SRAM-like host interface. This controller is targeted at embedded system applications that need to support two Ethernet ports, typically one for a LAN port and one for a WAN port. The AX88782/AX88783 supports simple a SRAM-like host interface, routine packet checksum calculation, and burst-mode access which make it easy to provide high performance 2-port Ethernet connectivity solutions for any embedded MCU. The built-in switching fabric supports non-blocking wire-speed forwarding and provides four priority

queues for advanced QoS functions including Port-Based, 802.1p VLAN, IPv4 TOS/IPv6 COS for voice, video, audio and data traffic classification. The AX88782/AX88783 combines the benefits of high integration and flexibility which makes it an ideal single-chip solution for designing high performance, QoS-aware, cost effective and small form factor 2-port Ethernet function for any embedded system application.

### **Block Diagram**

### **Target Applications**

- VoIP Phone, VoIP ATA Adapter

- IP Camera for Remote Surveillance

- Next Generation IP-STB and IPTV

- Industrial Controller and Networked Sensor

- Port Redundancy and Port Monitoring

- Single Board Computers (SBC)

Copyright © 2008-2012 ASIX Electronics Corporation. All rights reserved.

### DISCLAIMER

No part of this document may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, for any purpose, without the express written permission of ASIX. ASIX may make changes to the product specifications and descriptions in this document at any time, without notice.

ASIX provides this document "as is" without warranty of any kind, either expressed or implied, including without limitation warranties of merchantability, fitness for a particular purpose, and non-infringement.

Designers must not rely on the absence or characteristics of any features or registers marked "reserved", "undefined" or "NC". ASIX reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. Always contact ASIX to get the latest document before starting a design of ASIX products.

### TRADEMARKS

ASIX, the ASIX logo are registered trademarks of ASIX Electronics Corporation. All other trademarks are the property of their respective owners.

# **Table of Contents**

| 1.0        | OVERVIEW                                                              |    |

|------------|-----------------------------------------------------------------------|----|

| 1.1        | General Description                                                   |    |

| 1.2        | BLOCK DIAGRAM                                                         | 10 |

| 1.3        |                                                                       |    |

| 1          | 1.3.1 AX88782: Port 0/Port 1 PHY Mode                                 |    |

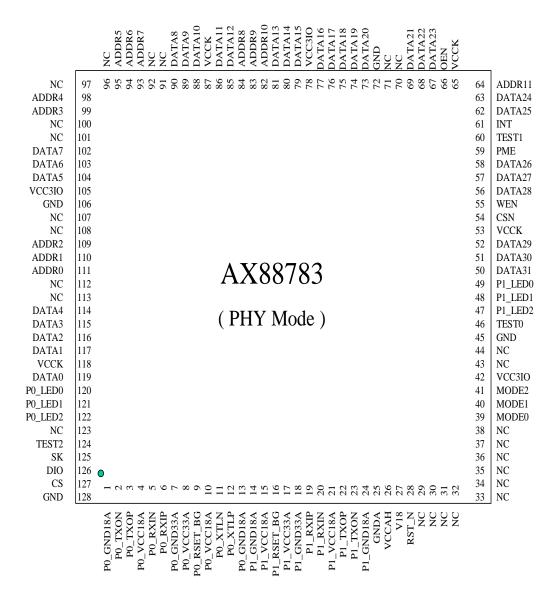

| 1          | 1.3.2 AX88783 : Port 0/Port 1 PHY Mode                                | 12 |

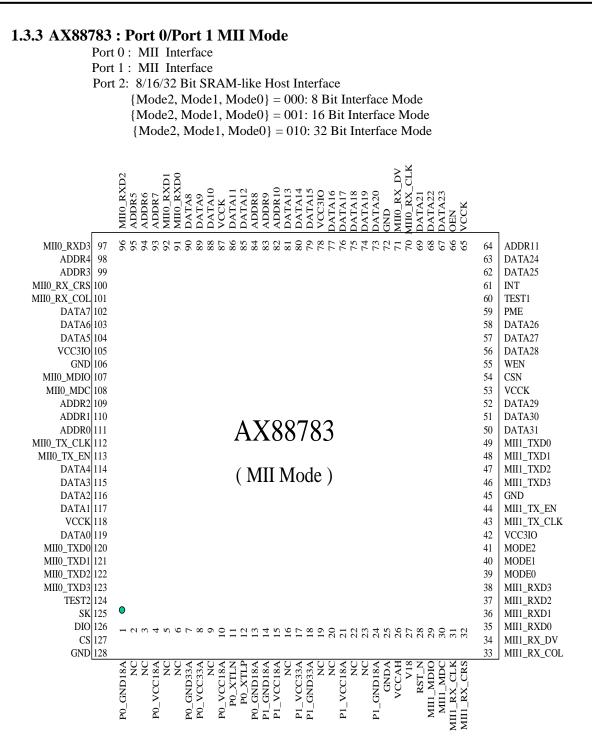

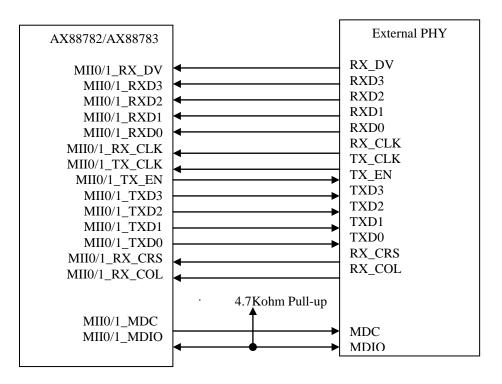

| 1          | 1.3.3 AX88783 : Port 0/Port 1 MII Mode                                |    |

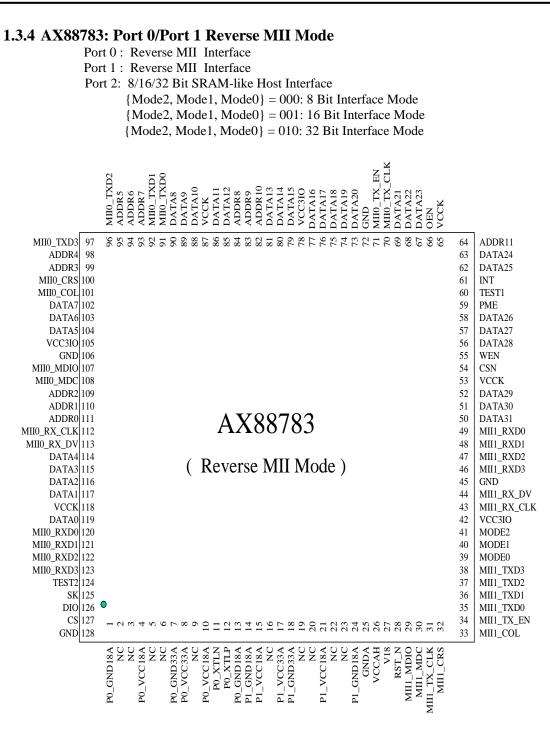

| 1          | 1.3.4   AX88783: Port 0/Port 1 Reverse MII Mode                       |    |

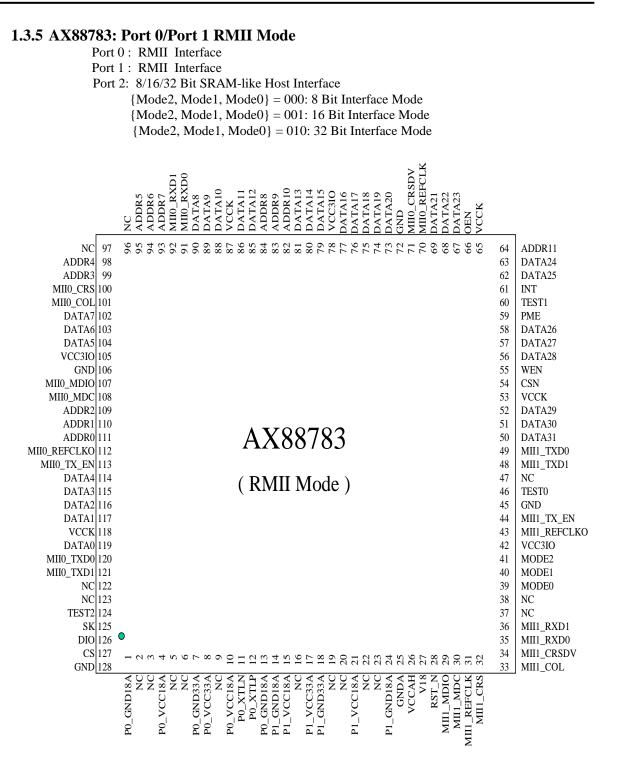

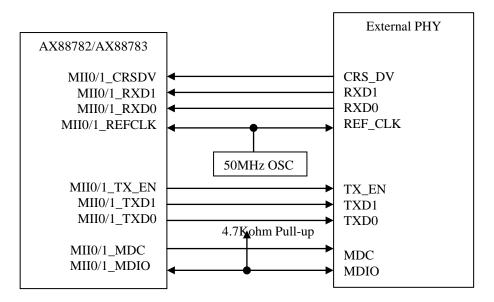

| 1          | 1.3.5AX88783: Port 0/Port 1 RMII Mode                                 |    |

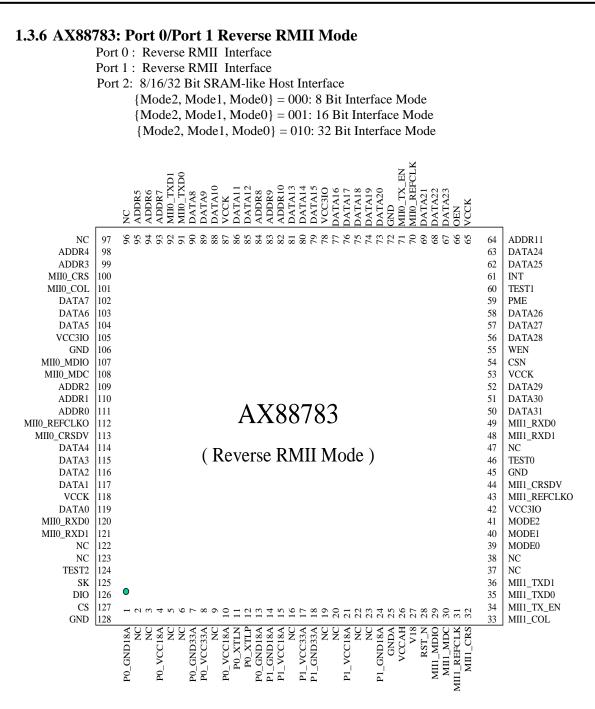

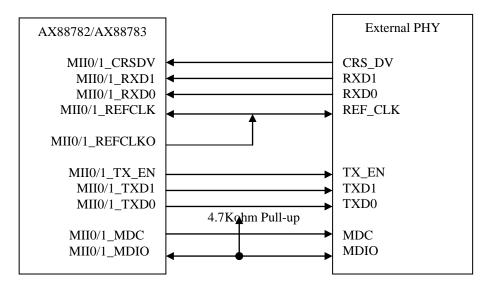

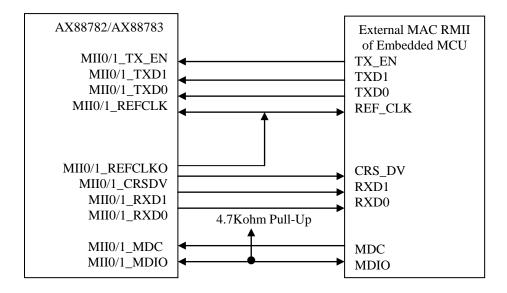

| 1          | 1.3.6   AX88783: Port 0/Port 1 Reverse RMII Mode                      | 16 |

| 2.0        | PIN DESCRIPTIONS                                                      | 17 |

| 2.1        | Port 0 Interface                                                      |    |

| 2          | 2.1.1 PHY Mode                                                        | 17 |

| 2          | 2.1.2 MII Mode                                                        |    |

| 2          | 2.1.3 Reverse MII Mode                                                | 19 |

| 2          | 2.1.4 RMII Mode                                                       | 20 |

| 2          | 2.1.5 Reverse RMII Mode                                               |    |

| 2          | 2.1.6 GPIO Mode (AX88783)                                             |    |

|            | 2.1.7 Port 0 Multi-Function Pin Summary                               |    |

| 2.2        |                                                                       |    |

|            | 2.2.1 PHY Mode                                                        |    |

| _          | 2.2.2 MII Mode                                                        |    |

|            | 2.2.3 Reverse MII Mode                                                |    |

|            | 2.2.4 RMII Mode                                                       |    |

| _          | 2.2.5 Reverse RMII Mode                                               |    |

| 2.3        | 2.2.6 Port 1 Multi-Function Pin Summary<br>PORT 2 SRAM-LIKE INTERFACE |    |

|            | 2.3.1 8/16 Bit CPU Interface for the AX88782                          |    |

|            | 2.3.2 8/16/32 Bit CPU Interface for the AX88783                       |    |

| 2.4        |                                                                       |    |

| 2.4        |                                                                       |    |

|            |                                                                       |    |

| 3.0        | FUNCTIONAL DESCRIPTION                                                |    |

| 3.1        | OVERVIEW                                                              |    |

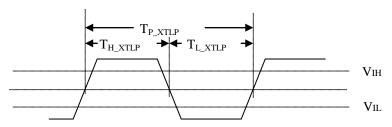

| 3.2        | Clock                                                                 |    |

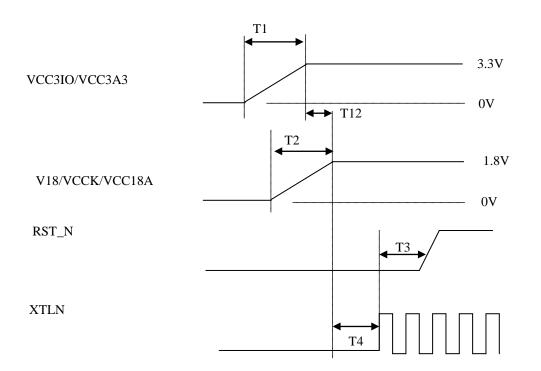

| 3.3        | BUILT-IN POWER-ON-RESET                                               |    |

| 3.4        |                                                                       |    |

| 3.5        |                                                                       |    |

| 3.6        |                                                                       |    |

| 3.7        |                                                                       |    |

| 3.8        |                                                                       |    |

| 3.9        |                                                                       |    |

| 3.1        |                                                                       |    |

| 3.1        |                                                                       |    |

| 3.1        |                                                                       |    |

| 3.1<br>3.1 |                                                                       |    |

| 3.1        |                                                                       |    |

| 3.1        |                                                                       |    |

| 3.1        |                                                                       |    |

| 3.1        |                                                                       |    |

| 3.1        |                                                                       |    |

| 3.2        |                                                                       |    |

|            |                                                                       |    |

| 8.21 GPI | O INTERFACE SUPPORT (ONLY FOR AX88783)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.21.1   | GPIO Interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3.21.2   | GPO Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3.21.3   | GPI Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

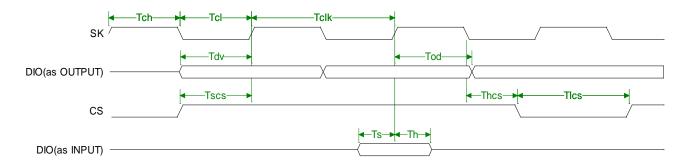

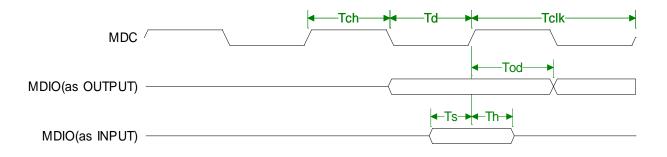

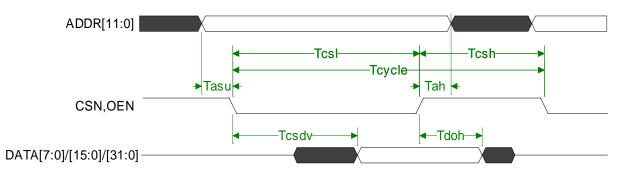

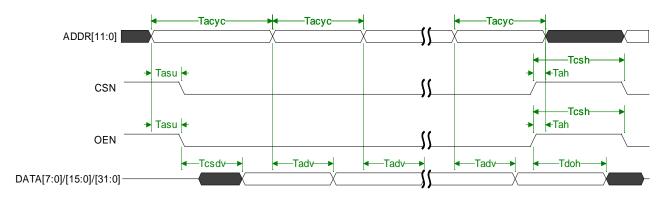

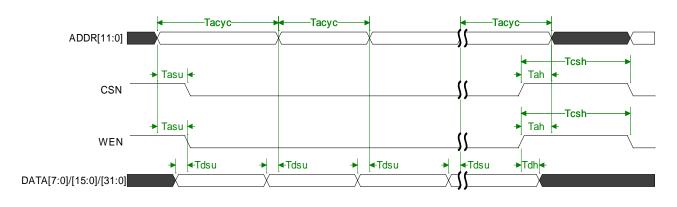

| 8.22 CPU | INTERFACE PROTOCOL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| INTE     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4.2.1    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

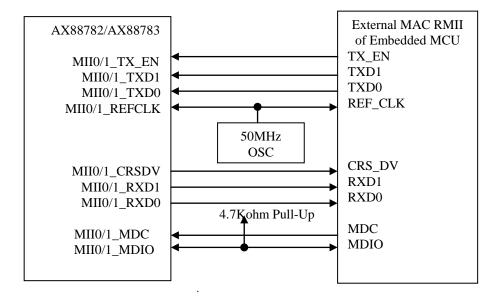

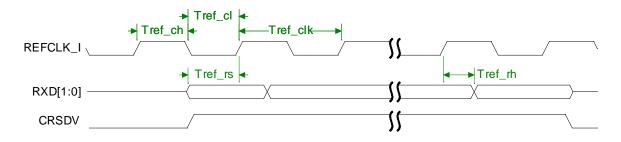

| .3 RM    | II AND REVERSE RMII INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4.3.1    | RMII Mode Reference connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4.3.2    | RMII Interface Set-Up Procedure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4.3.3    | Reverse RMII Mode Reference connection: (Only support 100 Full Duplex mode)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4.3.4    | Reverse RMII Interface Set-Up Procedure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

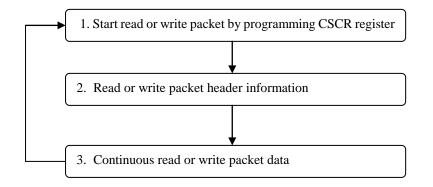

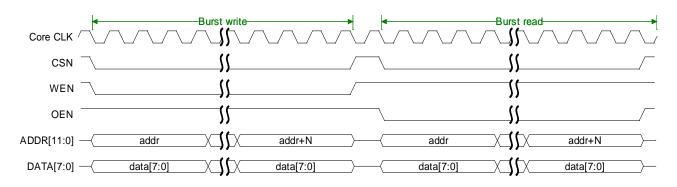

| .4 CPU   | READ/WRITE OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4.4.1    | 8-Bit CPU Burst Read/Write Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |