# Multiply by 16, 32 Phase-Locked Loop Clock Generator

## **FEATURES**

- Differential Inputs/Outputs for External Voltage Controlled SAW Oscillator

- Optional Internal Crystal Oscillator Driver

- Internal Edge-Matching Phase/Frequency Detector

- Internal Charge-Pump/Integrator Amplifier

- RF Bipolar Design for Low Phase Noise

- Available in a 3x3 mm MLP Package

#### PACKAGE AVAILABILITY

| PACKAGE                                            | PART NO.   | MARKING                            | NOTES |

|----------------------------------------------------|------------|------------------------------------|-------|

| MLP 16 (3x3)                                       | AZ12010AL  | AZ12010A<br><date code=""></date>  | 1,2   |

| MLP 16 (3x3)<br>RoHS Compliant /<br>Lead (Pb) Free | AZ12010AL+ | AZ12010A+<br><date code=""></date> | 1,2   |

| MLP 16 (3x3)                                       | AZ12010BL  | AZ12010B<br><date code=""></date>  | 1,2   |

| MLP 16 (3x3)<br>RoHS Compliant /<br>Lead (Pb) Free | AZ12010BL+ | AZ12010B+<br><date code=""></date> | 1,2   |

| DIE                                                | AZ12010XP  | N/A                                | 3     |

- 1 Add R1 at end of part number for 7 inch (1K parts), R2 for 13 inch (2.5K parts) Tape & Reel.

- 2 Date code format: "YY" for year followed by "WW" for week.

- 3 Waffle Pack

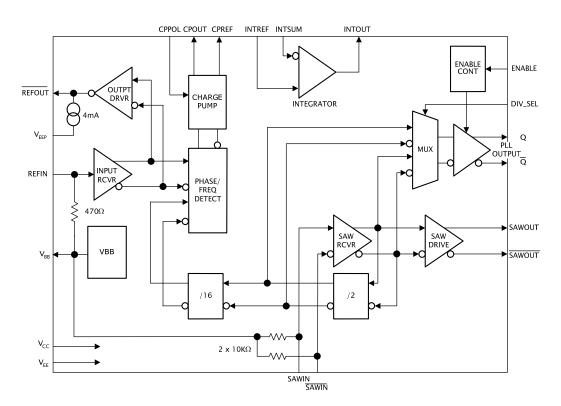

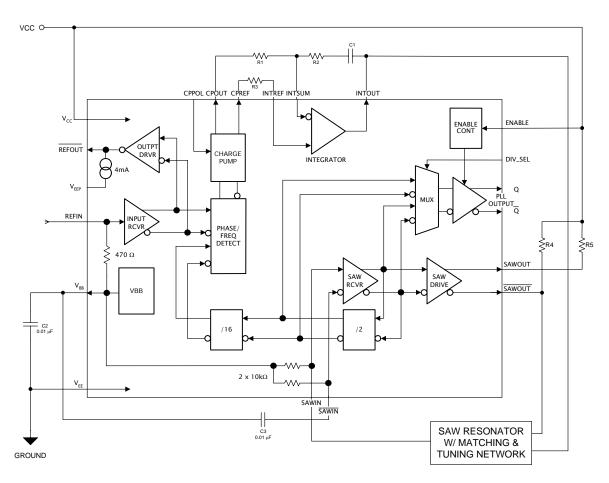

## **DESCRIPTION**

The AZ12010 contains all of the functional elements necessary to implement a Phase-Locked Loop for clock multiplication at frequencies up to 800 MHz. A fixed 32 times multiplication allows the use of low cost crystals or a low frequency reference signal. The output can be divided by two for 16 times net multiplication. The VCSO is differentially or single-ended driven using the chip CML SAW outputs. The dynamic properties of the PLL are under the control of the user through selection of the desired external components.

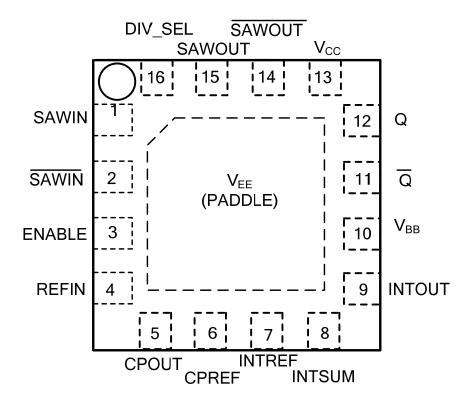

3X3 MLP 16 PACKAGE

AZM12010A: CPPOL pulled High AZM12010B: CPPOL pulled Low

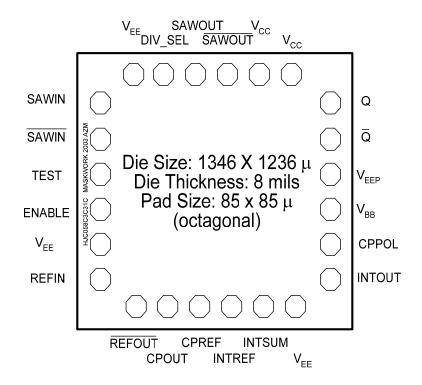

DIE MAP

Pad Center Locations

| Signal Name  | X coordinate (μ) | Y coordinate (μ) |

|--------------|------------------|------------------|

| SAWIN        | -522.0           | 372.3            |

| SAWIN        | -522.0           | 220.3            |

| TEST         | -522.0           | 68.3             |

| ENABLE       | -522.0           | -83.7            |

| $ m V_{EE}$  | -522.0           | -235.7           |

| REFIN        | -522.0           | -387.7           |

| REFOUT       | -365.0           | -515.8           |

| CPOUT        | -213.0           | -515.8           |

| CPREF        | -61.0            | -515.8           |

| INTREF       | 91.0             | -515.8           |

| INTSUM       | 243.0            | -515.8           |

| $ m V_{EE}$  | 395.0            | -515.8           |

| INTOUT       | 552.0            | -387.7           |

| CPPOL        | 552.0            | -235.7           |

| $ m V_{BB}$  | 552.0            | -83.7            |

| $ m V_{EEP}$ | 552.0            | 68.3             |

| Q            | 552.0            | 220.3            |

| Q            | 552.0            | 372.3            |

| $V_{\rm CC}$ | 395.0            | 509.9            |

| $V_{CC}$     | 243.0            | 509.9            |

| SAWOUT       | 91.0             | 509.9            |

| SAWOUT       | -61.0            | 509.9            |

| DIV SEL      | -219.0           | 509.9            |

| $ m V_{EE}$  | -377.0           | 509.9            |

## AZ12010 FUNCTIONAL PIN/PAD DESCRIPTIONS

| Name              | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Logic Level     |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| REFIN             | Reference Frequency Input This pin/pad includes an on-chip 470 $\Omega$ pull down resistor to $V_{BB}$ . The input from the reference circuit should be AC                                                                                                                                                                                                                                                                                                                                | Ü               |

| REFOUT            | coupled.  Reference Frequency Output This pin is an inverted and amplified version of the signal on the REFIN pin. The gain from REFIN to $\overline{\text{REFOUT}}$ is approximately 20. If $V_{\text{EEP}}$ is connected to $V_{\text{EE}}$ , a 4 ma on-chip current source is provided for the output. $\overline{\text{REFOUT}}$ is not available on the packaged versions (AZ12010A, AZ12010B).                                                                                      | PECL            |

| CPREF             | <b>Charge Pump Reference Output</b> The pin/pad voltage is nominally 1.2 volts below V <sub>CC</sub> .                                                                                                                                                                                                                                                                                                                                                                                    |                 |

| CPOUT             | <b>Charge Pump Output</b> The charge pump output voltage is $V_{CPREF} \pm 0.3V$ during a phase correction pulse. When there is no correction pulse the output goes high impedance.                                                                                                                                                                                                                                                                                                       |                 |

| CPPOL             | Charge Pump Polarity When this pin/pad is pulled high the PLL operates with a VCSO circuit exhibiting negative pulling slope (the VCSO frequency goes down when the control voltage goes up). When this pin/pad is pulled low (AZM12010B) the PLL operates with a VCSO circuit exhibiting positive pulling slope (the VCSO frequency goes up when the control voltage goes up). If the pin/pad is left open (AZM12010A), an internal pullup resistor selects negative pulling slope mode. | LVCMOS<br>LVTTL |

| INTREF            | <b>Integrator Reference Input</b> This pin/pad should be connected to CPREF through a bias current cancellation network                                                                                                                                                                                                                                                                                                                                                                   |                 |

| INTSUM            | <b>Integrator Summing Junction</b> This pin/pad is the summing junction for the integrator amplifier                                                                                                                                                                                                                                                                                                                                                                                      |                 |

| INTOUT            | Integrator Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                 |

| SAWIN<br>SAWIN    | <b>SAW Amplifier Inputs</b> If only one input is used (Single-ended VCSO), the unused input should be bypassed with a capacitor to $V_{BB}$ .                                                                                                                                                                                                                                                                                                                                             |                 |

| SAWOUT<br>SAWOUT  | <b>SAW Amplifier Outputs</b> These are open collector outputs for driving the VCSO device. Operating at nominally 9 ma, external pullup resistors must be connected between these pins/pads and $V_{CC}$ . If only one output is used, the other output should be connected to $V_{CC}$ through a 50 $\Omega$ resistor.                                                                                                                                                                   | CML (Analog)    |

| ENABLE            | <b>PLL Output Enable</b> The Q and $\overline{Q}$ outputs are enabled when this pin/pad is pulled high. When this pin/pad is low, the Q output is high, and the $\overline{Q}$ output is low. If the pin/pad is left open, an internal pullup resistor enables the outputs.                                                                                                                                                                                                               | LVCMOS<br>LVTTL |

| DIV_SEL           | <b>Divide Select</b> When this pin/pad is high, the Q and $\overline{Q}$ outputs are divided by one from the SAW device. When it is low, the Q and $\overline{Q}$ outputs are divided by two from the SAW device. If the pin/pad is left open, an internal pullup resistor selects the divide by one mode.                                                                                                                                                                                | LVCMOS<br>LVTTL |

| Q<br>Q            | <b>Clock Output</b> These pin/pads are the main clock output. When ENABLE is low, the outputs are disabled with Q high and $\overline{Q}$ low.                                                                                                                                                                                                                                                                                                                                            | PECL            |

| $V_{\mathrm{BB}}$ | <b>Reference Voltage Output</b> This pin/pad is used to bias the REFIN signal. It must be bypassed externally to the $V_{EE}$ pins/pads with a 0.01 $\mu$ F capacitor.                                                                                                                                                                                                                                                                                                                    |                 |

| V <sub>EEP</sub>  | <b>REFOUT Current Source</b> If $V_{EEP}$ is connected to $V_{EE}$ , a 4 ma on-chip current source is provided for the $\overline{REFOUT}$ output. $V_{EEP}$ is not available on the packaged versions (AZ12010A, AZ12010B).                                                                                                                                                                                                                                                              |                 |

| $V_{CC}$          | <b>Positive Supply</b> +3.0 to +3.6 V                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                 |

| $ m V_{EE}$       | Negative Supply Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                 |

Absolute Maximum Ratings are those values beyond which device life may be impaired.

| Symbol      | Characteristic                           | Rating      | Unit |

|-------------|------------------------------------------|-------------|------|

| $V_{CC}$    | Power Supply $(V_{EE} = GND)$            | 0 to +6.0   | Vdc  |

| $V_{\rm I}$ | Input Voltage $(V_{EE} = GND)$           | 0 to +6.0   | Vdc  |

| $I_{OUT}$   | PECL Output Current — Continuous — Surge | 50<br>100   | mA   |

| $T_{A}$     | Operating Temperature Range              | -40 to +85  | °C   |

| $T_{STG}$   | Storage Temperature Range                | -65 to +150 | °C   |

## **AZ12010 DC CHARACTERISTICS** ( $V_{CC} = +3.0 \text{ to } +3.6 \text{ V}, V_{EE} = GND$ )

| Symbol            | Characteristic                                         | -40°C                 |                         | 0°C                   |                       | 25°C                  |                         | 85°C                  |                          | Unit                     |     |

|-------------------|--------------------------------------------------------|-----------------------|-------------------------|-----------------------|-----------------------|-----------------------|-------------------------|-----------------------|--------------------------|--------------------------|-----|

| Symbol            | Character istic                                        | Min                   | Max                     | Min                   | Max                   | Min                   | Тур                     | Max                   | Min                      | Max                      | Omt |

| $V_{BB}$          | Reference Voltage                                      | V <sub>CC</sub> -1.38 | V <sub>CC</sub> -1.26   | V <sub>CC</sub> -1.38 | V <sub>CC</sub> -1.26 | V <sub>CC</sub> -1.38 | V <sub>CC</sub> -1.31   | V <sub>CC</sub> -1.26 | V <sub>CC</sub><br>-1.38 | V <sub>CC</sub><br>-1.26 | V   |

| R <sub>REF</sub>  | REFIN Pull-Down resistor to $V_{BB}$                   |                       |                         |                       |                       |                       | 470                     |                       |                          |                          | Ω   |

| $R_{SAW}$         | SAWIN, SAWIN Pull-<br>Down resistor to V <sub>BB</sub> |                       |                         |                       |                       |                       | 10K                     |                       |                          |                          | Ω   |

| $V_{HCTL}$        | High level integrator output                           | V <sub>CC</sub> -1.0  |                         | V <sub>CC</sub> -1.0  |                       | V <sub>CC</sub> -1.0  |                         |                       | V <sub>CC</sub><br>-1.0  |                          | V   |

| $V_{LCTL}$        | Low level integrator output                            |                       | 0.5                     |                       | 0.5                   |                       |                         | 0.5                   |                          | 0.5                      | V   |

| V <sub>OH</sub>   | Output HIGH Voltage <sup>1</sup><br>Q, \( \bar{Q} \)   | V <sub>CC</sub> -1085 | V <sub>CC</sub><br>-880 | V <sub>CC</sub> -1025 | V <sub>CC</sub> -880  | V <sub>CC</sub> -1025 | V <sub>CC</sub><br>-955 | V <sub>CC</sub> -880  | V <sub>CC</sub><br>-1025 | V <sub>CC</sub><br>-880  | mV  |

| $V_{\mathrm{OH}}$ | Output HIGH Voltage <sup>2</sup><br>SAWOUT, SAWOUT     | V <sub>CC</sub> -10   | V <sub>CC</sub>         | V <sub>CC</sub> -10   | V <sub>CC</sub>       | V <sub>CC</sub> -10   |                         | V <sub>CC</sub>       | V <sub>CC</sub> -10      | V <sub>CC</sub>          | mV  |

| V <sub>OL</sub>   | Output LOW Voltage <sup>1</sup><br>Q, \( \bar{Q} \)    | V <sub>CC</sub> -1830 | V <sub>CC</sub> -1555   | V <sub>CC</sub> -1810 | V <sub>CC</sub> -1620 | V <sub>CC</sub> -1810 | V <sub>CC</sub> -1705   | V <sub>CC</sub> -1620 | V <sub>CC</sub> -1810    | V <sub>CC</sub> -1620    | mV  |

| $V_{OL}$          | Output LOW Voltage <sup>2</sup> SAWOUT, SAWOUT         | V <sub>CC</sub> -349  | V <sub>CC</sub><br>-481 | V <sub>CC</sub> -365  | V <sub>CC</sub> -516  | V <sub>CC</sub> -392  | V <sub>CC</sub><br>-449 | V <sub>CC</sub> -557  | V <sub>CC</sub><br>-465  | V <sub>CC</sub><br>-661  | mV  |

| $V_{IH}$          | Input HIGH Voltage,<br>LVCMOS/LVTTL<br>EN, DIV SEL     | 2.2                   | V <sub>CC</sub>         | 2.2                   | V <sub>CC</sub>       | 2.2                   |                         | V <sub>CC</sub>       | 2.2                      | V <sub>CC</sub>          | V   |

| V <sub>IL</sub>   | Input LOW Voltage,<br>LVCMOS/LVTTL<br>EN, DIV_SEL      | 0.0                   | 0.8                     | 0.0                   | 0.8                   | 0.0                   |                         | 0.8                   | 0.0                      | 0.8                      | V   |

| $I_{CC}(I_{EE})$  | Power Supply Current                                   |                       | 65                      |                       | 65                    | 45                    | 54                      | 65                    |                          | 65                       | mA  |

- 1. Load is  $50\Omega$  to  $V_{CC}$ -2V

- 2. Load is  $50\Omega$  to  $V_{CC}$

### AZ 12010 AC CHARACTERISTICS ( $V_{CC} = +3.0 \text{ to } +3.6 \text{ V}, V_{EE} = \text{GND}$ )

| Symbol      | Characteristic                                                 | -40°C |      |     | 25°C |      |      | 85°C |     |      | Unit      |

|-------------|----------------------------------------------------------------|-------|------|-----|------|------|------|------|-----|------|-----------|

| Symbol      | Characteristic                                                 | Min   | Тур  | Max | Min  | Тур  | Max  | Min  | Тур | Max  | Cint      |

| $A_{PD}$    | Phase Detector Gain                                            |       |      |     |      | 20.3 |      |      |     |      | radians/V |

| $f_{VCO}$   | External VSCO frequency                                        |       |      | 800 |      |      | 800  |      |     | 800  | MHz       |

| $t_r / t_f$ | Output Rise & Fall Times $(20\% - 80\%)$ Q, $\overline{Q}$     |       |      |     |      | 120  |      |      |     |      | ps        |

| $a_{ m V}$  | SAW Amplifier and<br>Driver Gain at 622.08<br>MHz <sup>1</sup> | 18    | 24.5 | 28  | 15.5 | 21   | 24.5 | 13.5 | 19  | 22.5 | dB        |

1. Single Ended Input and Output, Driven from  $50\Omega$  backmatched source, Load  $50\Omega$  to  $V_{CC}$ .

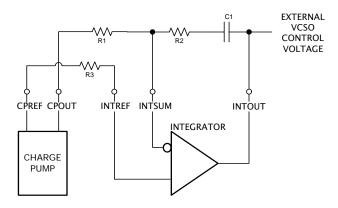

#### **Loop Filter Design**

The combination of the phase detector, amplifier, VCO and divider form a second-order phase-locked loop. Proper selection of the loop components is important to obtain stable, low jitter operation.

The loop bandwidth (or natural frequency,  $\omega_n$ ) and damping factor ( $\zeta$ ) are the two major driving forces that define the loop's response to a disturbance. The value of  $\zeta$  is typically 0.7 to ensure the fastest step response consistent with no ringing. However in many oscillator application  $\zeta$  may be 3 or higher to provide further phase noise reduction.  $\omega_n$  is chosen as a compromise between settling time, VCO jitter and reference feedthrough. These values can be computed by the following equations:

$$\omega_n = \frac{1}{N} \sqrt{\frac{K_{\phi} K_{VCO}}{\tau_1}}$$

$$\zeta = \frac{\tau_2 \omega_n}{2}$$

$$\tau_1 = R_1 C_1$$

$$\tau_2 = R_2 C_1$$

$K_{\phi}$  = Phase Detector Gain (20.3 radians/V)

$K_{VCO} = VCO Gain (radians/sec/volt)$

N = Frequency Divisor value (32)

The component definitions are shown in the figure below. R3 should be equal to R1 to minimize integrator offsets.

Figure 1 Charge Pump and Integrator

# **Application Circuit**

A typical application circuit is shown in Figure 2.

Figure 2. Typical Application, Always Enabled and Divide by One for Output

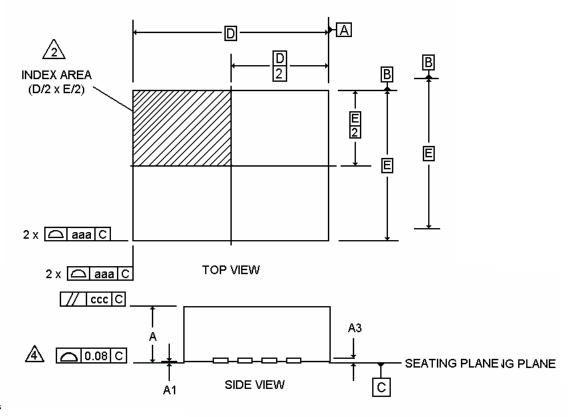

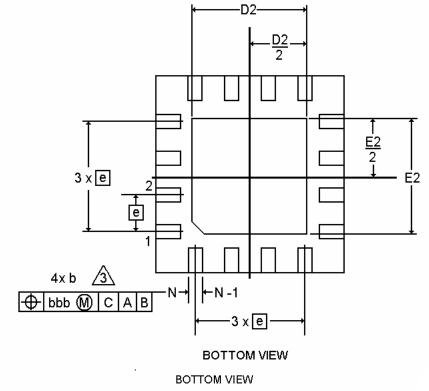

# PACKAGE DIAGRAM MLP 16

## NOTE

## NOTES

1. DIMENSIONING AND TOLERANCING CONFORM TO ASME T14-1994.

THE TERMINAL #1 AND PAD

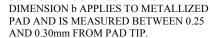

NUMBERING CONVENTION SHALL CONFORM TO JESD 95-1 SPP-012. DIMENSION b APPLIES TO METALLIZE

COPLANARITY APPLIES TO THE EXPOSED PAD AS WELL AS THE TERMINALS.

|           | MILLIMETERS |       |  |  |  |  |  |

|-----------|-------------|-------|--|--|--|--|--|

| DIM       | MIN         | MAX   |  |  |  |  |  |

| A         | 0.80        | 1.10  |  |  |  |  |  |

| <b>A1</b> | 0.00        | 0.05  |  |  |  |  |  |

| <b>A3</b> | 0.25        | REF   |  |  |  |  |  |

| b         | 0.225       | 0.275 |  |  |  |  |  |

| D         | 2.90        | 3.10  |  |  |  |  |  |

| <b>D2</b> | 1.65        | 1.95  |  |  |  |  |  |

| E         | 2.90        | 3.10  |  |  |  |  |  |

| <b>E2</b> | 1.65        | 1.95  |  |  |  |  |  |

| e         | 0.50        | BSC   |  |  |  |  |  |

| L         | 0.35        | 0.45  |  |  |  |  |  |

| aaa       | 0.25        |       |  |  |  |  |  |

| bbb       | 0.10        |       |  |  |  |  |  |

| ccc       | 0.10        |       |  |  |  |  |  |

Arizona Microtek, Inc. reserves the right to change circuitry and specifications at any time without prior notice. Arizona Microtek, Inc. makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Arizona Microtek, Inc. assume any liability arising out of the application or use of any product or circuit and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Arizona Microtek, Inc. does not convey any license rights nor the rights of others. Arizona Microtek, Inc. products are not designed, intended or authorized for use as components in systems intended to support or sustain life, or for any other application in which the failure of the Arizona Microtek, Inc. product could create a situation where personal injury or death may occur. Should Buyer purchase or use Arizona Microtek, Inc. products for any such unintended or unauthorized application, Buyer shall indemnify and hold Arizona Microtek, Inc. and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Arizona Microtek, Inc. was negligent regarding the design or manufacture of the part.