## AiP16C23

# Ram Mapping 56 SEG/4 COM or 52 SEG/8 COM LCD Controllers with 2-line Serial Interface

Product

# Specification

**Specification Revision History:**

| Version    | Date    | Description |

|------------|---------|-------------|

| 2021-04-A1 | 2021-04 | New         |

|            |         |             |

|            |         |             |

|            |         |             |

Address:Building B4,NO.777,Jianzhu Road,Binhu District,Wuxi City,Jiangsu Province http://www.i-core. cn P.C.: 214072

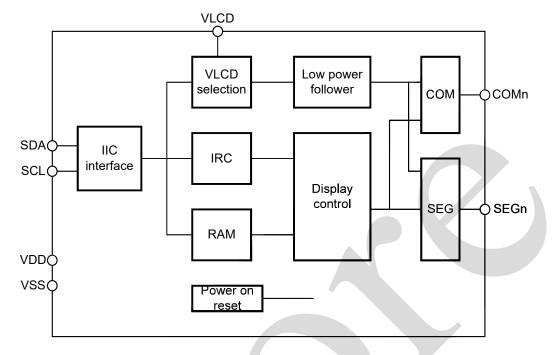

#### 1、 General Description

AiP16C23 is a standard I<sup>2</sup>C interface communication LCD controller/driver. The device provides two display modes: 1/4 duty and 1/8 duty display modes. The display segments of the device are 224 patterns  $(56\times4)$  or 416 patterns  $(52\times8)$ .

AiP16C23 has a built-in clock generator, LCD bias voltage generation module, LCD drive voltage follower and standard I<sup>2</sup>C interface.

#### Features:

- Operating voltage: 2.4 to 5.5V •

- I<sup>2</sup>C interface

- Low power consumption

- Versatile blinking modes

- Read/Write address auto increment

- Internal 32kHz RC oscillator

- 16-step V<sub>LCD</sub> voltage adjustable

- Display patterns: 56×4 patterns: 56 SEGs and 4 COMs 52×8 patterns: 52 SEGs and 8 COMs

- Bias: 1/3 or 1/4; duty: 1/4 or 1/8

- 52×8 bit display data register

- Internal LCD bias generator with voltage follower

- Two selectable LCD frame frequencies: 80Hz or 160Hz

- LCD drive voltage can be adjusted by external resistor

- Packaging information: LQFP48/LQFP64

## **Ordering Information:**

| ' | Tube | packing | specifications: |  |

|---|------|---------|-----------------|--|

|   |      |         |                 |  |

| Type number   | Packaging<br>form | Marking<br>code | Tube<br>quantity | Boxed<br>tube<br>quantity | Boxed<br>quantity | Packing<br>box<br>number | Packing<br>quantity | Notes                                                                       |

|---------------|-------------------|-----------------|------------------|---------------------------|-------------------|--------------------------|---------------------|-----------------------------------------------------------------------------|

| AiP16C23LA.TB | LQFP48            | AiP16C23        | 250<br>PCS/plate | 10<br>plate/box           | 2500<br>PCS/box   | 6<br>box/pack            | 15000<br>PCS/pack   | Dimensions of<br>plastic enclosure:<br>7.0mm×7.0mm<br>Pin spacing:<br>0.5mm |

| AiP16C23LB.TB | LQFP64            | AiP16C23        | 250<br>PCS/plate | 10<br>plate/box           | 2500<br>PCS/box   | 6<br>box/pack            | 15000<br>PCS/pack   | Dimensions of<br>plastic enclosure:<br>7mm×7mm<br>Pin spacing:<br>0.4mm     |

Note: If the physical information is inconsistent with the ordering information, please refer to the actual product.

Number: AiP16C23-AX-XS-A067EN

#### 2、 Block Diagram And Pin Description

#### 2.1、Block Diagram

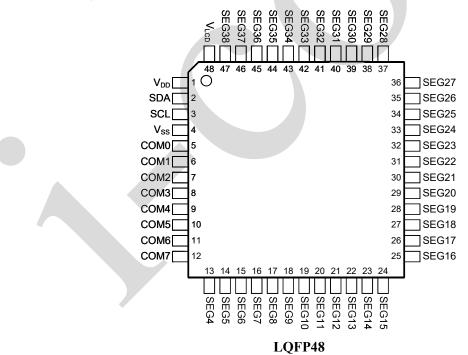

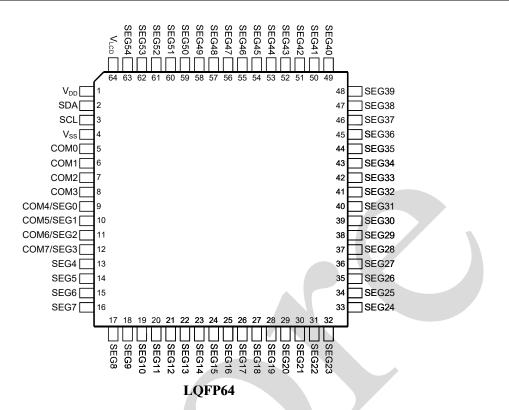

#### 2.2、 Pin Configurations

Wuxi I-CORE Electronics Co., Ltd. Tab: 835-12 rev:B3 Number: AiP16C23-AX-XS-A067EN

Note:

- 1. Application at  $V_{DD} \leq V_{LCD}$  or  $V_{LCD} \leq V_{DD}$ .

- 2. When the LQFP48 package is selected, this device does not support LCD 1/4 duty.

| 2.35 T III DUS | ription |                     |      |                                                         |

|----------------|---------|---------------------|------|---------------------------------------------------------|

| Pin            | No.     | Pin Name            | Туре | Description                                             |

| LQFP48         | LQFP64  |                     | Type | Description                                             |

| 2              | 2       | SDA                 | I/O  | Serial data input/output for I <sup>2</sup> C interface |

| 3              | 3       | SCL                 | Ι    | Serial clock input for I <sup>2</sup> C interface       |

| 1              | 1       | $V_{DD}$            | -    | Positive power supply                                   |

| 4              | 4       | V <sub>SS</sub>     | -    | Negative power supply, ground                           |

| 48             | 64      | $V_{LCD}$           | -    | LCD drive power                                         |

| 5~8            | 5~8     | COM0~COM3           | 0    | LCD COM outputs                                         |

| 9~12           | -       | COM4~COM7           | 0    | LCD COM outputs                                         |

| -              | 9~12    | COM4/SEG0~COM7/SEG3 | О    | LCD COM/SEG multiplexed<br>driver outputs               |

| 13~47          | 13~47   | SEG4~SEG38          | 0    | LCD SEG outputs                                         |

| -              | 48~63   | SEG39~SEG54         | 0    | LCD SEG outputs                                         |

| 2.3 | Pin I | Description |

|-----|-------|-------------|

|-----|-------|-------------|

rev:B3

#### 3、 Electrical Parameter

#### 3.1、 Absolute Maximum Ratings

$(T_{amb}=25^{\circ}C, All \text{ voltage referenced to Vss, unless otherwise specified})$

| Characteristic        | Symbol           | Conditions | Value                          | Unit |

|-----------------------|------------------|------------|--------------------------------|------|

| supply voltage        | -                | -          | $V_{SS}$ -0.3 to $V_{SS}$ +6.5 | V    |

| input voltage         | V <sub>IN</sub>  | -          | $V_{SS}$ -0.3 to $V_{DD}$ +0.3 | V    |

| operating temperature | T <sub>amb</sub> | -          | -40 to +85                     | °C   |

| storage temperature   | T <sub>stg</sub> | -          | -55 to +150                    | °C   |

#### 3.2 Electrical Characteristics

#### 3.2.1, DC Characteristics 1

| Demonster                 | G1 1             |                 | Conditions                                                              | M            | T    | м               | TT . • 4 |

|---------------------------|------------------|-----------------|-------------------------------------------------------------------------|--------------|------|-----------------|----------|

| Parameter                 | Symbol           | V <sub>DD</sub> | Conditions                                                              | Min.         | Тур. | Max.            | Unit     |

| operating<br>voltage      | V <sub>DD</sub>  | -               | -                                                                       | 2.4          | -    | 5.5             | V        |

| operating<br>voltage      | V <sub>LCD</sub> | -               | -                                                                       | 2.4          | -    | 5.5             | V        |

| operating                 | T                | 3V              | no load, $V_{LCD}=V_{DD}$ , 1/3 bias, $f_{LCD}=80$ Hz, LCD display on,  | -            | 25   | 40              | uA       |

| current                   | I <sub>DD</sub>  | 5V              | internal system oscillator on,<br>DA0~DA3 are set to "0000"             | -            | 35   | 50              | uA       |

| operating                 | I <sub>DD1</sub> | 3V              | no load, $V_{LCD}=V_{DD}$ , 1/3 bias, $f_{LCD}=80$ Hz, LCD display off, | -            | 2    | 5               | uA       |

| current                   | וממי             | 5V              | internal system oscillator on,<br>DA0~DA3 are set to "0000"             | -            | 4    | 10              | uA       |

| standby                   | т                | 3V              | o load, V <sub>LCD</sub> =V <sub>DD</sub> , LCD                         | -            | -    | 1               | uA       |

| curent                    | I <sub>STB</sub> | 5V              | display off, internal system<br>oscillator off                          | -            | -    | 2               | uA       |

| HIGH level intput current | V <sub>IH</sub>  | -               | SDA, SCL                                                                | $0.7 V_{DD}$ | -    | V <sub>DD</sub> | V        |

| LOW level intput current  | V <sub>IL</sub>  | -               | SDA, SCL                                                                | 0            | -    | $0.3 V_{DD}$    | V        |

| input leakage<br>curent   | I <sub>IL</sub>  | -               | $V_{IN}\!\!=\!\!V_{SS}$ or $V_{DD}$                                     | -1           | -    | 1               | uA       |

| LOW level<br>output       | I <sub>OL</sub>  | 3V              | $V_{OI}=0.4V, SDA$                                                      | 3            | -    | -               | mA       |

| current                   | IOL              | 5V              | V <sub>0L</sub> =0.4V, SDA                                              | 6            | -    | -               | mA       |

| LCD COM                   | I <sub>OL1</sub> | 3V              | $V_{LCD}=3V, V_{OL}=0.3V$                                               | 250          | 400  | -               | uA       |

| sink current              | TOLI             | 5V              | $V_{LCD}$ =5V, $V_{OL}$ =0.5V                                           | 500          | 800  | -               | uA       |

| LCD COM source            | I <sub>OH1</sub> | 3V              | $V_{LCD}=3V, V_{OH}=2.7V$                                               | -140         | -230 | -               | uA       |

| current                   | TOHJ             | 5V              | $V_{LCD}$ =5V, $V_{OH}$ =4.5V                                           | -300         | -500 | -               | uA       |

| LCD SEG                   | I <sub>OL2</sub> | 3V              | $V_{LCD}=3V, V_{OL}=0.3V$                                               | 250          | 400  | -               | uA       |

| sink current              | TOL2             | 5V              | $V_{LCD}=5V, V_{OL}=0.5V$                                               | 500          | 800  | -               | uA       |

Address:Building B4,NO.777,Jianzhu Road,Binhu District,Wuxi City,Jiangsu Province http://www.i-core. cn P.C.: 214072

-Tab: 835-12

Wuxi I-CORE Electronics Co., Ltd. <sup>12</sup> rev:B3 Number: AiP160

Number: AiP16C23-AX-XS-A067EN

| LCD SEG | Т                | 3V | $V_{LCD}\!\!=\!\!3V, V_{OH}\!\!=\!\!2.7V$ | -140 | -230 | - | uA |

|---------|------------------|----|-------------------------------------------|------|------|---|----|

| current | I <sub>OH2</sub> | 5V | $V_{LCD}$ =5V, $V_{OH}$ =4.5V             | -300 | -500 | - | uA |

#### 3.2.2 AC Characteristics 1

(T<sub>amb</sub>=-40 to +85 °C, V<sub>DD</sub>=2.4 to 5.5V, V<sub>SS</sub>=0V, unless otherwise specified)

| Parameter                 | Sumbol            | Symbol Conditions |                                      | Min. | Tum  | Max.   | Unit |

|---------------------------|-------------------|-------------------|--------------------------------------|------|------|--------|------|

| rarameter                 | Symbol            | V <sub>DD</sub>   | Conditions                           |      | Тур. | Iviax. | Unit |

| LCD frame<br>frequency    | f <sub>LCD1</sub> | 4V                | $1/4$ duty, $T_{amb}$ =+25 °C        | 72   | 80   | 88     | Hz   |

| LCD frame<br>frequency    | f <sub>LCD2</sub> | 4V                | $1/4$ duty, $T_{amb}$ =+25 °C        | 144  | 160  | 176    | Hz   |

| LCD frame<br>frequency    | f <sub>LCD3</sub> | 4V                | $1/4$ duty, $T_{amb}$ =-40 to +85 °C | 52   | 80   | 124    | Hz   |

| LCD frame<br>frequency    | f <sub>LCD4</sub> | 4V                | $1/4$ duty, $T_{amb}$ =-40 to +85 °C | 104  | 160  | 248    | Hz   |

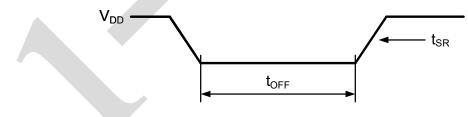

| V <sub>DD</sub> off time  | t <sub>OFF</sub>  | -                 | V <sub>DD</sub> drop down to 0V      | 20   | -    | -      | ms   |

| V <sub>DD</sub> slew rate | t <sub>SR</sub>   | -                 | -                                    | 0.05 | -    | -      | V/ms |

Note:

1. During the power on/off period, if the conditions of the power-on reset sequence are not met, the internal power-on reset (POR) circuit cannot work normally.

2. During operating, if the  $V_{DD}$  voltage drops below the specified minimum operating voltage, the power-on reset sequence conditions must be satisfied. In other words, the  $V_{DD}$  voltage must drop to 0V and must maintain a 0V voltage of at least 20ms before rising to the normal operating voltage.

| Parameter                    | Symphol                     | Conditions                                                                       | V <sub>DD</sub> =2.4 | V to 5.5V | V <sub>DD</sub> =3.0 | V to 5.5V | Unit |

|------------------------------|-----------------------------|----------------------------------------------------------------------------------|----------------------|-----------|----------------------|-----------|------|

| Parameter                    | Symbol                      | Conditions                                                                       | Min.                 | Max.      | Min.                 | Max.      | Unit |

| clock<br>frequency           | $\mathbf{f}_{\mathrm{SCL}}$ |                                                                                  | -                    | 100       | -                    | 400       | kHz  |

| bus free time                | t <sub>BUF</sub>            | during this period the<br>bus must be free until<br>a new transmission<br>starts | 4.7                  | -         | 1.3                  | -         | us   |

| Start condition<br>hold time | t <sub>hd: sta</sub>        | after this period, the<br>first clock pulse is<br>generated                      | 4                    | -         | 0.6                  | -         | us   |

| SCL LOW<br>time              | t <sub>LOW</sub>            | -                                                                                | 4.7                  | -         | 1.3                  | -         | us   |

| SCL HIGH<br>time             | t <sub>HIGH</sub>           | -                                                                                | 4                    | -         | 0.6                  | -         | us   |

| Start condition setup time   | t <sub>su: sta</sub>        | only relevant for<br>repeated START<br>condition                                 | 4.7                  | -         | 0.6                  | -         | us   |

| data hold time               | t <sub>HD: DAT</sub>        | -                                                                                | 0                    | -         | 0                    | -         | ns   |

| data setup time              | t <sub>SU: DAT</sub>        | -                                                                                | 250                  | -         | 100                  | -         | ns   |

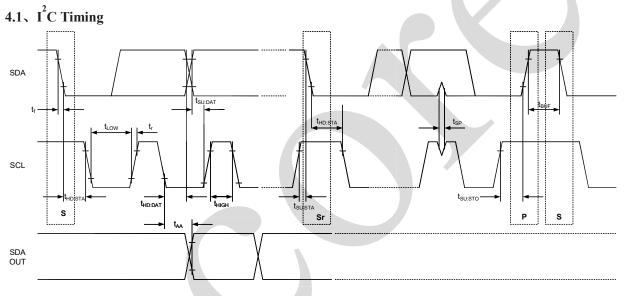

3.2.3 AC Characteristics 2 (I<sup>2</sup>C Interface)

Address:Building B4,NO.777,Jianzhu Road,Binhu District,Wuxi City,Jiangsu Province http://www.i-core. cn P.C.: 214072

# Wuxi I-CORE Electronics Co., Ltd.<br/>rev:B3Tab: 835-12rev:B3Number: AiP16C23-AX-XS-A067EN

| SDA and SCL rise time                       | t <sub>R</sub>       | -                         | - | 1   | -   | 0.3 | us |

|---------------------------------------------|----------------------|---------------------------|---|-----|-----|-----|----|

| SDA and SCL fall time                       | t <sub>F</sub>       | -                         | - | 0.3 | -   | 0.3 | us |

| Stop condition<br>setup time                | t <sub>SU: STO</sub> | -                         | 4 | -   | 0.6 | -   | us |

| effective clock<br>output time              | t <sub>AA</sub>      | -                         | - | 3.5 | -   | 0.9 | us |

| input filter<br>time constant<br>(SDA, SCL) | t <sub>SP</sub>      | noise suppression<br>time | - | 100 | -   | 50  | ns |

## 4、 Timing Diagrams

```

4.2, Power-on Reset Timing

```

Tab: 835-12

rev:B3

#### **5**、**Function Description**

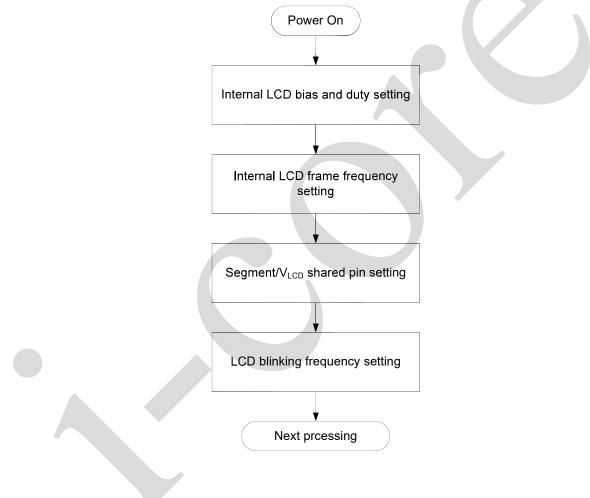

#### 5.1 Power-on Reset

After power-on, the device is initialized by the internal power-on reset circuit. The state of the internal circuit after initialization is as follows:

- The drive mode 1/4 duty output and 1/3 bias is selected for LQFP64 package.

- The drive mode 1/4 duty output and 1/3 bias is selected for LQFP48 package.

- Both the system oscillator and LCD bias generator are off state.

- The LCD display is off sate.

- The internal voltage adjustment function is enabled.

- The SEG/ $V_{LCD}$  shared pin is set to SEG pin.

- The detection switch function of the V<sub>LCD</sub> pin is disabled.

- The frame frequency is set to 80Hz.

- The blinking function is switched off.

After power-on, Data transfers on the  $I^2C$  bus within 1ms should be avoided to complete the reset action.

#### 5.2 Display Memory—RAM Structure

AiP16C23 has a 52×8-bit static RAM for storing LCD display data. Write "1" to it to turn on the corresponding LCD, and write "0" to turn off the corresponding LCD.

The contents of the RAM data are directly mapped to the LCD. The SEGs in the first column of RAM operate together with their corresponding COM0. In multiplexed LCD applications, SEGs in columns 2, 3, and 4 are time-multiplexed with their corresponding COM1, COM2, and COM3, respectively. The mapping relationship between RAM data and LCD pattern is as follows:

| Output | COM3 | COM2 | COM1 | COM0 | Output | COM3 | COM2 | COM1 | COM0 | Address |

|--------|------|------|------|------|--------|------|------|------|------|---------|

| SEG1   |      |      |      |      | SEG0   |      |      |      |      | 00H     |

| SEG3   |      |      |      |      | SEG2   |      |      |      |      | 01H     |

| SEG5   |      |      |      |      | SEG4   |      |      |      |      | 02H     |

| SEG7   |      |      |      |      | SEG6   |      |      |      |      | 03H     |

| SEG9   |      |      |      |      | SEG8   |      |      |      |      | 04H     |

| SEG11  |      |      |      |      | SEG10  |      |      |      |      | 05H     |

|        |      |      |      |      |        |      |      |      |      |         |

| SEG55  |      |      |      |      | SEG54  |      |      |      |      | 1BH     |

|        | D7   | D6   | D5   | D4   | 656.4  | D3   | D2   | D1   | D0   | Data    |

RAM mapping of 56×4 display mode

**Tab:** 835-12

Wuxi I-CORE Electronics Co., Ltd. <sup>12</sup> rev:B3 Number: AiP160

| Output | COM7/<br>SEG3 | COM6/<br>SEG2 | COM5/<br>SEG1 | COM4/<br>SEG0 | COM3 | COM2 | COM1 | COM0 | Address |

|--------|---------------|---------------|---------------|---------------|------|------|------|------|---------|

| SEG4   |               |               |               |               |      |      |      |      | 00H     |

| SEG5   |               |               |               |               |      |      |      |      | 01H     |

| SEG6   |               |               |               |               |      |      |      |      | 02H     |

| SEG7   |               |               |               |               |      |      |      |      | 03H     |

| SEG8   |               |               |               |               |      |      |      |      | 04H     |

| SEG9   |               |               |               |               |      |      |      |      | 05H     |

|        |               |               |               |               |      |      |      |      |         |

| SEG55  |               |               |               |               |      |      |      |      | 33H     |

|        | D7            | D6            | D5            | D4            | D3   | D2   | D1   | D0   | Data    |

RAM mapping of 52×8 display mode

| MSB |    |            |                 |                            |           |    | LSB |

|-----|----|------------|-----------------|----------------------------|-----------|----|-----|

| D7  | D6 | D5         | D4              | D3                         | D2        | D1 | D0  |

|     |    | Display of | lata transfer f | ormat for I <sup>2</sup> C | interface |    |     |

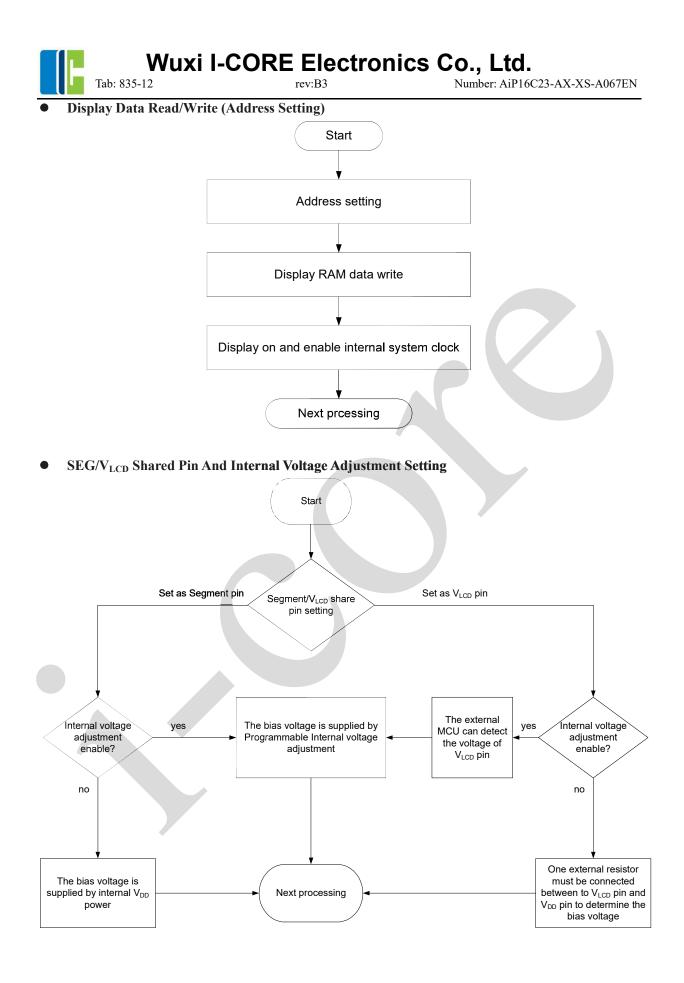

#### 5.3、 Address Pointer

Display RAM addressing technology is realized by address pointer. This mechanism allows single or multiple display data bytes to be loaded at any location in the display RAM. The address pointer sequence is initialized by the address pointer command.

#### 5.4 System Oscillator

The internal oscillator provides timing for the internal logic and LCD drive signals. The system clock frequency ( $f_{SYS}$ ) determines LCD frame frequency. During the system power-on initialization, the system oscillator will be in the stop state.

#### 5.5, Frame Frequency

The AiP16C21 provides two frame frequencies, which can be selected by the mode setting command to be 80Hz or 160Hz.

#### 5.6 Blinker Function

The device contains versatile blinking modes. The whole display can be blinked at frequencies selected by blink command. The ratio between the system frequency and the blinking frequency depends on the blinking mode, as shown in the following table:

| Blinking Mode | <b>Operating Mode Ratio</b>     | Blinking Frequency (Hz) |

|---------------|---------------------------------|-------------------------|

| 0             | 0                               | 闪烁关闭                    |

| 1             | $f_{SYS}/16384Hz$               | 2                       |

| 2             | $f_{\text{sys}}/32768\text{Hz}$ | 1                       |

| 3             | $f_{sys}/65536Hz$               | 0.5                     |

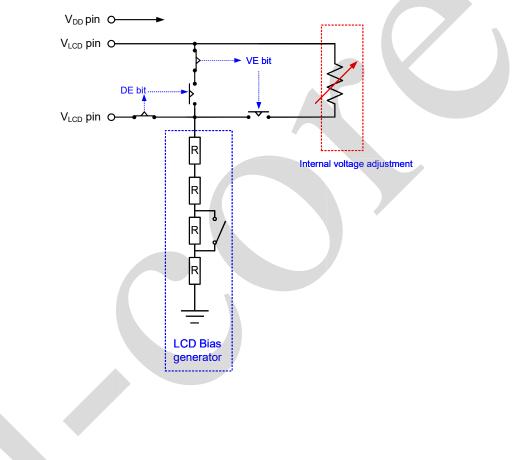

#### 5.7、 LCD Bias Generator

LCD full voltage ( $V_{OP}$ ) comes from ( $V_{LCD}$ - $V_{SS}$ ). The LCD voltage can be externally compensated for temperature through the voltage provided by the  $V_{LCD}$  pin.

1/3 or 1/4 bias voltage can be obtained from an internal voltage divider of four series resistors connected between V<sub>sc</sub> and V<sub>s</sub>. The centre resistor can be switched out of circuits to provide a 1/3 bias voltage.

#### 5.8、Internal V<sub>LCD</sub> Voltage Adjustment

- The internal V<sub>LCD</sub> adjustment contains four series resistors and a 4-bit programmable analog switch which can provide 16-level voltage adjustment options using the V<sub>LCD</sub> voltage adjustment command.

- The internal V<sub>LCD</sub> adjustment as shown below:

Number: AiP16C23-AX-XS-A067EN

When DE=1, VE=1:

| Bias    |                        |                        |               |

|---------|------------------------|------------------------|---------------|

| DA3~DA0 | 1/3                    | 1/4                    | Note          |

| 00H     | $1.000 \times V_{LCD}$ | $1.000 \times V_{LCD}$ | default value |

| 01H     | $0.944 \times V_{LCD}$ | $0.957 \times V_{LCD}$ |               |

| 02H     | $0.894 \times V_{LCD}$ | $0.918 \times V_{LCD}$ |               |

| 03H     | $0.849 \times V_{LCD}$ | $0.882 \times V_{LCD}$ |               |

| 04H     | $0.808 \times V_{LCD}$ | $0.849 \times V_{LCD}$ |               |

| 05H     | $0.771 \times V_{LCD}$ | $0.818 \times V_{LCD}$ |               |

| 06H     | $0.738 \times V_{LCD}$ | $0.789 \times V_{LCD}$ |               |

| 07H     | $0.707 \times V_{LCD}$ | $0.763 \times V_{LCD}$ |               |

| 08H     | $0.678 \times V_{LCD}$ | $0.738 \times V_{LCD}$ |               |

| 09H     | $0.652 \times V_{LCD}$ | $0.714 \times V_{LCD}$ |               |

| 0AH     | $0.628 \times V_{LCD}$ | $0.692 \times V_{LCD}$ |               |

| 0BH     | $0.605 \times V_{LCD}$ | $0.672 \times V_{LCD}$ |               |

| 0CH     | $0.584 \times V_{LCD}$ | $0.652 \times V_{LCD}$ |               |

| 0DH     | $0.565 \times V_{LCD}$ | $0.634 \times V_{LCD}$ |               |

| 0EH     | 0.547×V <sub>DD</sub>  | $0.616 \times V_{DD}$  |               |

| 0FH     | 0.529×V <sub>DD</sub>  | 0.600×V <sub>DD</sub>  |               |

#### 5.9、 SEG Drive Output

The LCD drive module contains 56 SEG outputs SEG0~SEG55 or 52 SEG outputs SEG4~SEG55, these SEGs should be directly connected to the LCD panel. The SEG output signals are generated according to the multiplexed COM signals and the data in the display latch. If the number of SEG used is less than 56 or 52, the unused SEG outputs should be left open-circuit.

#### 5.10、 COM Drive Output

The LCD drive section contains 4 COM outputs (COM0~COM3) or 8 COM outputs (COM0~COM7). These COMs should be directly connected to the LCD panel. The COM output signals are generated according to the selected LCD drive mode. If the number of COMs used is less than 4 or 8, the unused COM output should be left open-circuit.

Tab: 835-12

Wuxi I-CORE Electronics Co., Ltd. 12 rev:B3 Number: AiP160

Number: AiP16C23-AX-XS-A067EN

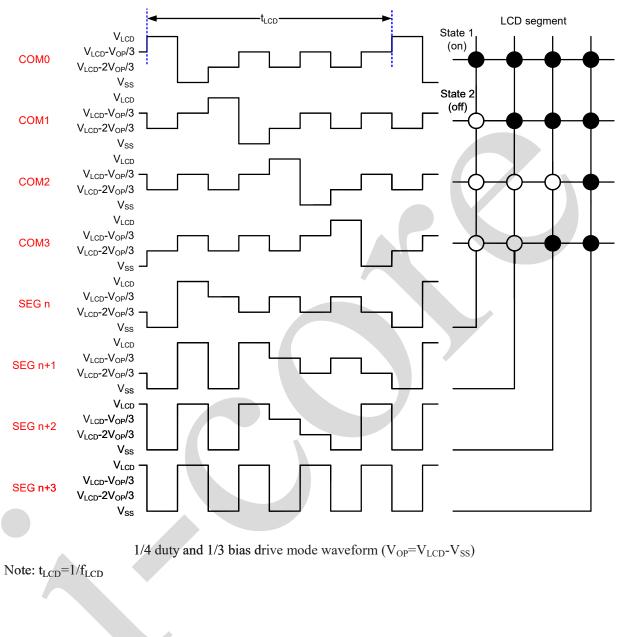

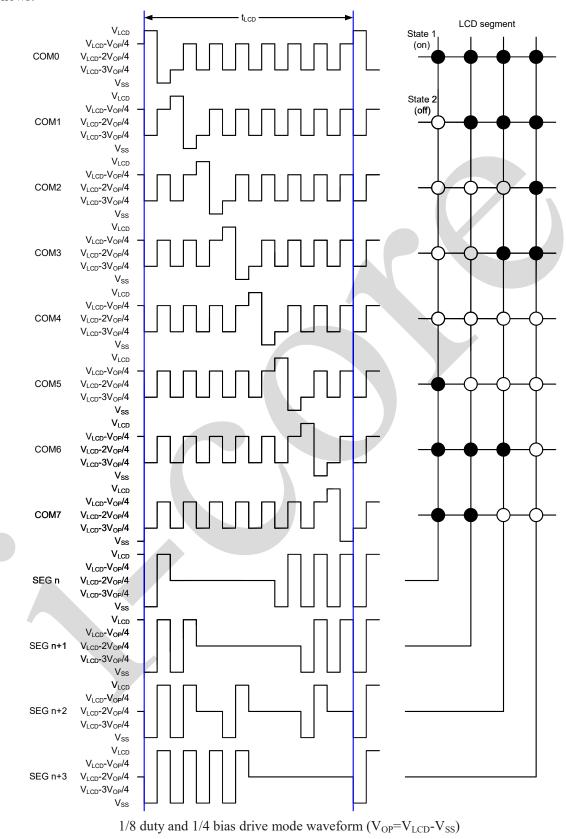

#### 5.11、 LCD Drive Mode Waveforms

• When the LCD drive mode selects 1/4 duty and 1/3 bias, the waveform and LCD display is shown as follows:

Tab: 835-12

Number: AiP16C23-AX-XS-A067EN

• When the LCD drive mode selects 1/8 duty and 1/4 bias, the waveform and LCD display is shown as follows:

Note:  $t_{LCD} = 1/f_{LCD}$

Address:Building B4,NO.777,Jianzhu Road,Binhu District,Wuxi City,Jiangsu Province http://www.i-core. cn P.C.: 214072

Wuxi I-CORE Electronics Co., Ltd.

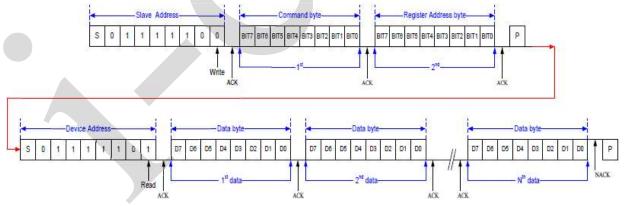

#### 5.12, I<sup>2</sup>C Serial Interface

The device provides  $I^2C$  serial interface, and the device is only used as a slave for  $I^2C$  communication. The  $I^2C$  interface is for bidirectional, two-line communication between different ICs or modules, that is, a serial data line SDA and a serial clock line SCL. These two lines are respectively connected to the positive power supply through a pull-up resistor with a typical value of  $4.7K\Omega$ . When the  $I^2C$  bus is free, both lines are HIGH. The microcontroller connected to the  $I^2C$  interface must have an open-drain or open-collector output to realize the wired-or function. Data transmission starts only when the  $I^2C$  interface is not busy.

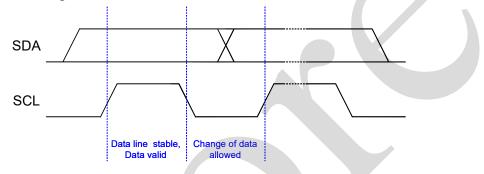

#### 5.13, Data Validity

When SCL=1, the data on the SDA pin must be stable. Only when SCL=0, the level of the SDA pin will change, as shown in the diagram below:

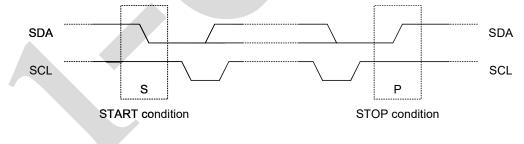

#### 5.14 START And STOP Conditions

- When SCL=1, a high to low transition on the SDA line defines a START condition.

- When SCL=1, a low to high transition on the SDA line defines a STOP condition.

- START and STOP conditions are always generated by the master. The I<sup>2</sup>C interface is considered to be busy after the START condition. The I<sup>2</sup>C interface is considered to be free again a certain time after the STOP condition.

- The I<sup>2</sup>C interface stays busy if a repeated START (Sr) is generated instead of a STOP condition. In some respects, the START and repeated START (Sr) conditions are functionally identical.

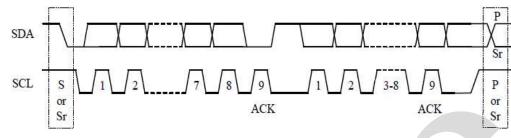

#### 5.15, Byte Format

Every byte on the SDA line must be 8-bit long. The number of bytes that can be transmitted at a time is unlimited. Each byte has to be followed by an acknowledge bit. Data transmission starts from the highest bit.

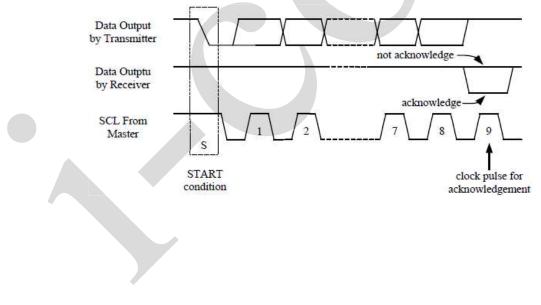

#### 5.16、Acknowledge (ACK)

- Each bytes of eight bits is followed by one acknowledge bit. This acknowledge bit is a LOW level placed on the I<sup>2</sup>C interface by the receiver. The master generates an extra acknowledge related clock pulse.

- A slave receiver which is addressed must generate an acknowledge, ACK, after the receiving each byte.

- The device that acknowledges must pull down the SDA line during the acknowledge clock pulse so that it remains stable LOW during the HIGH period of this clock pulse.

- A master receiver generates a not-acknowledge (NACK) when the slave sends the last byte and has told the slave to end data transmission. In this case, the master receiver must leave the data line HIGH during the 9th pulse to not acknowledge. The master will generate a STOP or repeated START condition.

#### 5.17、Slave Addressing

Tab: 835-12

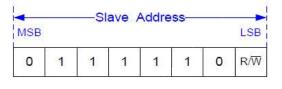

- The slave address byte is the first byte received following the START condition form the master device. The first seven bits of the first byte make up the slave address. The eighth bit defines a read or write operation to be performed. When the R/W bit is "1", then a read operation is selected. When the  $R/\overline{W}$  bit is "0", then a write operation is selected.

- AiP16C23 address bit is "0111110". When an address byte is sent, the device compares with its internal address. If they match, the device outputs an acknowledge on the SDA line.

#### 5.18, Write Operation

#### 5.18.1、 Byte Writes Operation

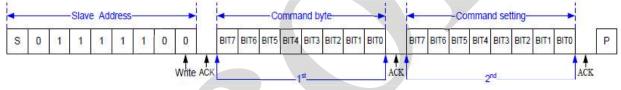

#### **Command Byte**

A Command Byte write operation consists of a START condition, a slave address with an R/W bit, a command byte, a command setting byte and a STOP condition.

Command Byte Write Operation

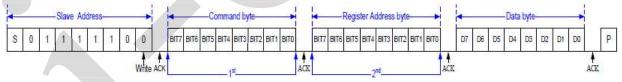

#### **Display RAM Single Data Byte**

A display RAM data byte write operation consists of a START condition, a slave address with an  $R/\overline{W}$  bit, a command byte, a valid Register Address byte, a Data byte and a STOP condition.

Display RAM Single Data Byte Write Operation

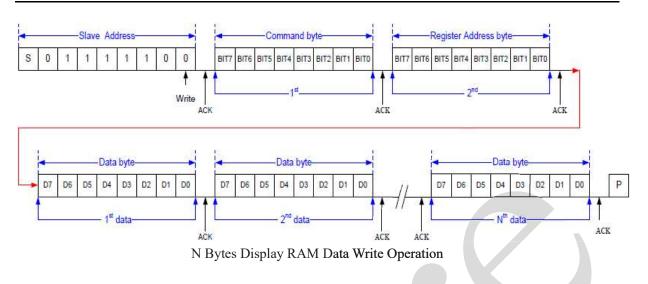

#### 5.18.2 Display RAM Page Write Operation

After a START condition the slave address with the  $R/\overline{W}$  bit is sent to the I<sup>2</sup>C interface followed with a command byte and the specified display RAM Register Address of which the contents are written to the internal address pointer. The data to be written to the memory will be transmitted next and then the address pointer will be automatically incremented by 1, so it can write to the next address after receiving an acknowledge. After the internal address pointer reaches the maximum address, which is 1BH for 1/4 duty drive mode or 33H for 1/8 duty drive mode, the address pointer will be reset to 00H.

Number: AiP16C23-AX-XS-A067EN

#### 5.19、 Display RAM Read Operation

Tab: 835-12

- In this mode, the master reads the AiP16C23 data after setting the slave address. Following the  $R/\overline{W}$  bit (="0") is an acknowledge bit, a command byte and the register address byte which is written to the internal address pointer. After configuring the start address of the Read Operation, another START condition and the slave address are transferred on the I<sup>2</sup>C interface followed by the  $R/\overline{W}$  bit (="1"). Then the MSB of the data which was addressed is transmitted first on the I<sup>2</sup>C interface. The address pointer is incremented by 1 after the receiving an acknowledge. That means that if the device sends the data at the address of  $A_{N+1}$ , the master will read and acknowledge the transferred new data byte and the address pointer is incremented to  $A_{N+2}$ . After the internal address pointer reaches the maximum address, which is 1BH for 1/4 duty drive mode or 33H for 1/8 duty drive mode, the address pointer will be reset to 00H.

- The cycle of reading consecutive addresses will continue until the master sends a STOP condition.

#### 5.20, Command Summary

#### • Display Data Input Command

This command is used to send data from MCU to memory map of the AiP16C23.

| Function                                 | Byte            | (MSB)<br>Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | (LSB)<br>Bit 0 | Note                                              | R/W | Def |

|------------------------------------------|-----------------|----------------|-------|-------|-------|-------|-------|-------|----------------|---------------------------------------------------|-----|-----|

| display data<br>input/ output<br>command | 1 <sup>st</sup> | 1              | 0     | 0     | 0     | 0     | 0     | 0     | 0              | -                                                 | W   | -   |

| address pointer                          | 2 <sup>nd</sup> | Х              | X     | A5    | A4    | A3    | A2    | A1    | A0             | Display data<br>start address<br>of memory<br>map | W   | 00H |

Note:

• Power on status: The address is set to 00H.

• If the command is not defined, the function will not be affected.

• For 1/4 duty drive mode, if the address pointer reaches 1BH, the pointer will reset to 00H.

• For 1/8 duty drive mode, if the address pointer reaches 33H, the pointer will reset to 00H.

| Function                            | Byte            | (MSB)<br>Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | (LSB)<br>Bit 0 | Note                                                                                               | R/W | Def |

|-------------------------------------|-----------------|----------------|-------|-------|-------|-------|-------|-------|----------------|----------------------------------------------------------------------------------------------------|-----|-----|

| Drive<br>mode<br>setting<br>command | 1 <sup>st</sup> | 1              | 0     | 0     | 0     | 0     | 0     | 1     | 0              | -                                                                                                  | W   | -   |

| Duty and bias setting               | 2 <sup>nd</sup> | Х              | х     | x     | X     | x     | X     | Duty  | Bias           | No matter what<br>"Duty" bit is set,<br>1/8 duty drive<br>mode is only<br>available for<br>LQFP48. | W   | 00H |

Drive Mode Command

Note:

| Bit 1 | Bit 0 | Duta     | Dist     |

|-------|-------|----------|----------|

| Duty  | Bias  | Duty     | Bias     |

| 0     | 0     | 1/4 duty | 1/3 bias |

| 0     | 1     | 1/4 duty | 1/4 bias |

| 1     | 0     | 1/8 duty | 1/3 bias |

| 1     | 1     | 1/8 duty | 1/4 bias |

• Power on status: The drive mode 1/4 duty output and 1/3 bias is selected.

• If the command is not defined, the function will not be affected.

#### • System Mode Command

This command controls the internal system oscillator on/off and display on/off.

| - st            |                           |                                                                                             | Bit 5                                | Bit 4                                                                                          | Bit 3                                                                                        | Bit 2                                                                       | Bit 1                                                                           | (LSB)<br>Bit 0                                                     | Note                                                               | R/W                                                                                                                          | Def                                                                                                                          |

|-----------------|---------------------------|---------------------------------------------------------------------------------------------|--------------------------------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| 1 <sup>st</sup> | 1                         | 0                                                                                           | 0                                    | 0                                                                                              | 0                                                                                            | 1                                                                           | 0                                                                               | 0                                                                  | -                                                                  | W                                                                                                                            | -                                                                                                                            |

| 2 <sup>nd</sup> | Х                         | X                                                                                           | Х                                    | Х                                                                                              | Х                                                                                            | Х                                                                           | S                                                                               | E                                                                  | -                                                                  | W                                                                                                                            | 00H                                                                                                                          |

|                 |                           |                                                                                             |                                      |                                                                                                |                                                                                              |                                                                             |                                                                                 |                                                                    |                                                                    |                                                                                                                              |                                                                                                                              |

| Bit 0           | Inte                      | ernal Sy                                                                                    | stem                                 | IC                                                                                             |                                                                                              | <b>a</b> 11                                                                 |                                                                                 |                                                                    |                                                                    |                                                                                                                              |                                                                                                                              |

| Е               |                           | Oscillat                                                                                    | or                                   | LU                                                                                             | D Dispi                                                                                      | ау                                                                          |                                                                                 |                                                                    |                                                                    |                                                                                                                              |                                                                                                                              |

| Х               |                           | off                                                                                         |                                      |                                                                                                | off                                                                                          |                                                                             |                                                                                 |                                                                    |                                                                    |                                                                                                                              |                                                                                                                              |

| 0               |                           | on                                                                                          |                                      |                                                                                                | off                                                                                          |                                                                             |                                                                                 |                                                                    |                                                                    |                                                                                                                              |                                                                                                                              |

| 1               |                           | on                                                                                          |                                      |                                                                                                | on                                                                                           |                                                                             |                                                                                 |                                                                    |                                                                    |                                                                                                                              |                                                                                                                              |

|                 | Bit 0<br>E<br>X<br>0<br>1 | Bit 0         Integration           E         0           X         0           1         1 | Bit 0Internal SyEOscillateXoff0on1on | Bit 0     Internal System       E     Oscillator       X     off       0     on       1     on | Bit 0     Internal System<br>Oscillator     LC       X     off       0     on       1     on | Bit 0Internal System<br>OscillatorLCD DisplEOscillatorOffXOffOff0OnOff1OnOn | Bit 0     Internal System       E     Oscillator       X     off       0     on | Bit 0Internal System<br>OscillatorLCD DisplayEOscillatorXoff0on1on | Bit 0Internal System<br>OscillatorLCD DisplayEOscillatorXoff0on1on | Bit 0     Internal System<br>Oscillator     LCD Display       X     off     off       0     on     off       1     on     on | Bit 0     Internal System<br>Oscillator     LCD Display       X     off     off       0     on     off       1     on     on |

• If the command is not defined, the function will not be affected.

#### • Frame Frequency Command

This command selects the frame frequency.

|                            |                 |                |       |       |       | r     |       |       |                |      |     |     |

|----------------------------|-----------------|----------------|-------|-------|-------|-------|-------|-------|----------------|------|-----|-----|

| Function                   | Byte            | (MSB)<br>Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | (LSB)<br>Bit 0 | Note | R/W | Def |

| frame frequency<br>command | 1 <sup>st</sup> | 1              | 0     | 0     | 0     | 0     | 1     | 1     | 0              | -    | W   | -   |

| frame frequency<br>setting | 2 <sup>nd</sup> | Х              | X     | X     | X     | X     | X     | X     | F              | -    | W   | 00H |

| Note:                      |                 |                |       |       |       |       |       |       |                |      |     |     |

| Bit 0                      | Fra             | ame            |       |       |       |       |       |       |                |      |     |     |

| F                          | Freq            | uency          |       |       |       |       |       |       |                |      |     |     |

| 0                          | 80              | Hz             |       |       |       |       |       |       |                |      |     |     |

| 1                          | 16              | 0Hz            |       |       |       |       |       |       |                |      |     |     |

• Power on status: Frame frequency is 80Hz.

• If the command is not defined, the function will not be affected.

Number: AiP16C23-AX-XS-A067EN

#### Blinking Frequency Command

This command defines the blinking frequency of the display modes.

| Function                         | Byte            | (MSI<br>Bit 7 | 2 I BILP       | Bit 5  | Bit 4     | Bit 3 | Bit 2 | Bit 1 | (LSB)<br>Bit 0 | Note | R/W | Def |

|----------------------------------|-----------------|---------------|----------------|--------|-----------|-------|-------|-------|----------------|------|-----|-----|

| blinking<br>frequency<br>command | 1 <sup>st</sup> | 1             | 0              | 0      | 0         | 1     | 0     | 0     | 0              | -    | w   | -   |

| blinking<br>frequency<br>setting | 2 <sup>nd</sup> | X             | X              | Х      | X         | X     | X     | BK1   | BK0            | -    | W   | 00H |

| ote:                             |                 |               |                |        | •         |       | •     | •     |                |      | •   |     |

| Bit 1                            | Bit (           | )             | Blinking       |        |           |       |       |       |                |      |     |     |

| BK1                              | BKO             | )             | Frequency      |        |           |       |       |       |                |      |     |     |

| 0                                | 0               |               | Blinking off   |        |           |       |       |       |                |      |     |     |

| 0                                | 1               |               | 2Hz            |        |           |       |       |       |                |      |     |     |

| 1                                | 0               |               | 1Hz            |        |           |       |       |       |                |      |     |     |

| 1                                | 1               |               | 0.5Hz          |        |           |       |       |       |                |      |     |     |

| Power on statu                   | s: Blinking     | g functio     | on is switched | l off. |           |       |       |       |                |      |     |     |

| If the comman                    |                 |               |                |        | e affecte | d.    |       |       |                |      |     |     |

#### • Internal Voltage Adjustment (IVA) Setting Command

The internal voltage ( $V_{LCD}$ ) can provide sixteen kinds of regulator voltage adjustment options by setting the LCD operating voltage adjustment command.

| Function       | Byte            | (MSB)<br>Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | (LSB)<br>Bit 0 | Note                                                                                                                                                                                                                                                    | R/W | Def |

|----------------|-----------------|----------------|-------|-------|-------|-------|-------|-------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|

| IVA<br>setting | $1^{st}$        | 1              | 0     | 0     | 0     | 1     | 0     | 1     | 0              | -                                                                                                                                                                                                                                                       | W   | -   |

| IVA<br>control | 2 <sup>nd</sup> | X              | x     | DE    | VE    | DA3   | DA2   | DA1   | DA0            | <ul> <li>SEG/V<sub>LCD</sub> shared pin can be set via the "DE" bit.</li> <li>The "VE" bit is used to enable or disable the internal voltage adjustment.</li> <li>The DA3~DA0 bits can be used to adjust the V<sub>LCD</sub> output voltage.</li> </ul> | W   | 30H |

| Bit 5 | Bit 4 | SEG/V <sub>LCD</sub>                     | Internal              |                                                                                                                                                                                                                                                |

|-------|-------|------------------------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DE    | VE    | Shared Pin<br>Select                     | Voltage<br>Adjustment | Note                                                                                                                                                                                                                                           |

| 0     | 0     | Analog power<br>supply LCD<br>drive bias | off                   | <ul> <li>The LCD drive voltage is input from the external to the V<sub>LCD</sub> pin.</li> <li>Disable the internal voltage adjustment function</li> <li>DA3~DA0 bit must be set as "0000".</li> </ul>                                         |

| 0     | 1     | Analog power<br>supply LCD<br>drive bias | on                    | <ul> <li>The V<sub>LCD</sub> pin and the V<sub>DD</sub> pin connect to use.</li> <li>It can be use, but it is not recommended to use the scheme of connectin a resistor between the V<sub>LCD</sub> pin and the V<sub>DD</sub> pin.</li> </ul> |

| 1     | 0     | Analog power<br>supply LCD               | off                   | <ul> <li>The LCD drive voltage is input from the external to the V<sub>LCD</sub> pin.</li> <li>Disable the internal voltage adjustment function.</li> </ul>                                                                                    |

Address:Building B4,NO.777,Jianzhu Road,Binhu District,Wuxi City,Jiangsu Province http://www.i-core. cn P.C.: 214072

| I |         |                                                                                                         | drive bias                 |    | • DA3~DA0 can be any value.                                                                                                                                |  |

|---|---------|---------------------------------------------------------------------------------------------------------|----------------------------|----|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|   | 1       | 1                                                                                                       | Analog power<br>supply LCD | on | <ul> <li>The LCD drive voltage is input from the external to the V<sub>LCD</sub> pin.</li> <li>Enable the internal voltage adjustment function.</li> </ul> |  |

|   |         |                                                                                                         | drive bias                 |    | • DA3~DA0 can be any value.                                                                                                                                |  |

|   | • Power | er on status: Disable the internal voltage adjustment and the SEG/ $V_{LCD}$ pin is set as the SEG pin. |                            |    |                                                                                                                                                            |  |

- Power on status: Disable the internal voltage adjustment and the SEG/V<sub>LCD</sub> pin is set as the SEG pin.

When the DA0~DA3 bits are set to "0000", the internal voltage-follower (OP4) is disabled. When the DA0~DA3 bits are set to other values except "0000", the internal voltage follower (OP4) is enabled.

- If the command is not defined, the function will not be affected.

#### 5.21 Operation Flow Chart

The flow charts of the access procedures are shown below.

Initialization

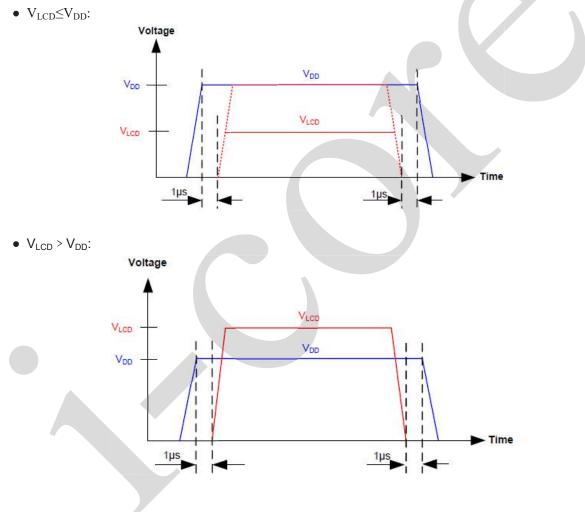

#### 5.21, Power Supply Sequence

• If the LCD and  $V_{DD}$  pin are powered separately, it is strongly recommended to follow the power supply sequence requirements.

- Failure to follow the requirements of the power supply sequence may cause malfunctions.

- Power supply sequence requirements:

1. Power-on sequence: First turn on the logic power supply voltage  $V_{DD}$ , then turn on the LCD drive voltage  $V_{LCD}$ .

2. Power-off sequence: First turn off the LCD drive voltage  $V_{LCD}$ , then turn off the logic power supply voltage  $V_{DD}$ .

3. Regardless of whether the  $V_{LCD}$  voltage is higher than the  $V_{DD}$  voltage, the power supply sequence must be followed.

Number: AiP16C23-AX-XS-A067EN

## 6, Typical Application Circuit And Application Note

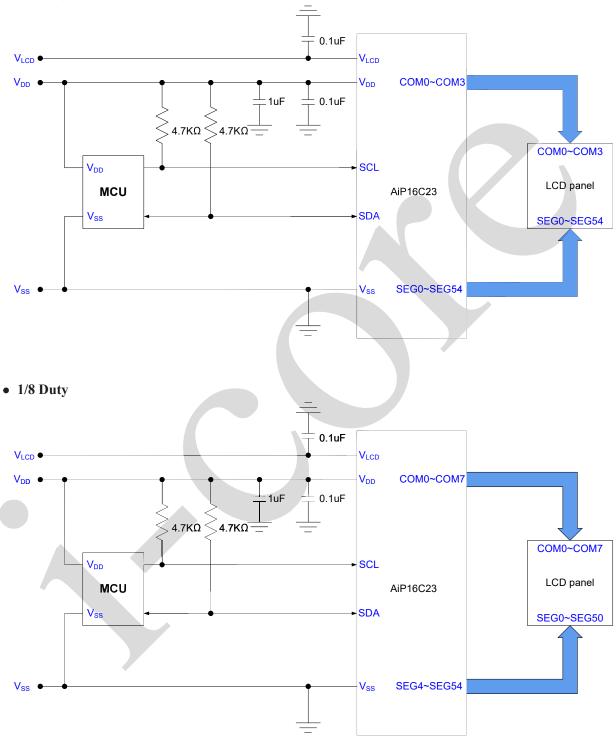

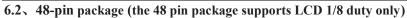

- 6.1、64-pin package

- 1/4 Duty

Wuxi I-CORE Electronics Co., Ltd. 12 rev:B3 Number: AiP16C23-AX-XS-A067EN

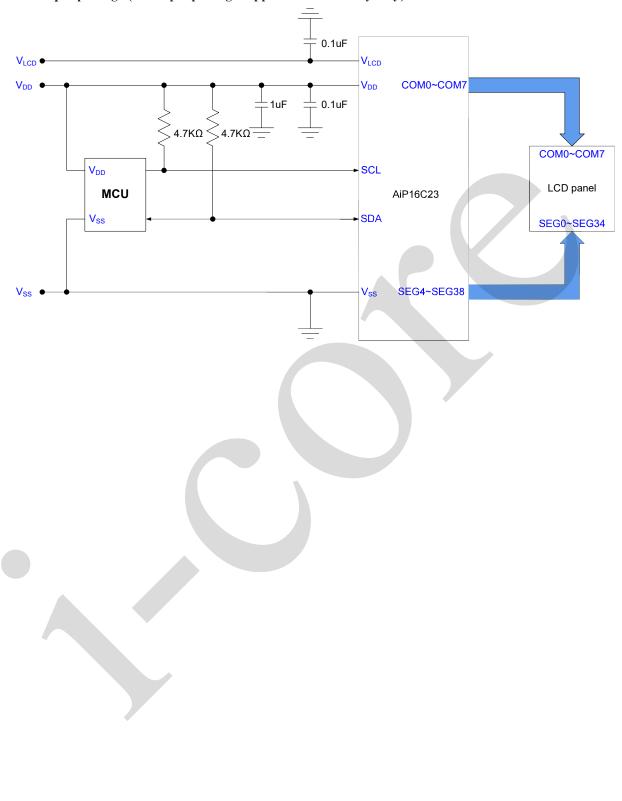

#### 7、Package Information

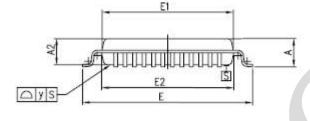

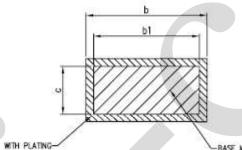

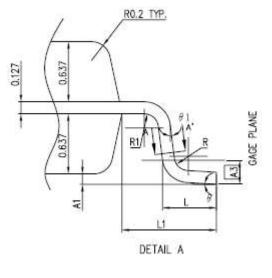

7.1、LQFP48

8

| Symbol | Min  | Nom   | Max  |  |  |

|--------|------|-------|------|--|--|

| А      |      |       | 1.63 |  |  |

| A1     | 0.01 |       | 0.21 |  |  |

| A2     | 1.30 | 1.40  | 1.50 |  |  |

| A3     |      | 0.254 |      |  |  |

| b      | 0.18 | 0.23  | 0.28 |  |  |

| b1     | 0.15 | 0.20  | 0.25 |  |  |

| с      |      | 0.127 |      |  |  |

| D1     | 6.85 | 6.95  | 7.05 |  |  |

| D2     | 6.90 | 7.00  | 7.10 |  |  |

| E      | 8.80 | 9.00  | 9.20 |  |  |

| E1     | 6.85 | 6.95  | 7.05 |  |  |

| E2     | 6.90 | 7.00  | 7.10 |  |  |

| e      |      | 0.50  |      |  |  |

| L      | 0.43 |       | 0.71 |  |  |

| L1     | 0.90 | 1.00  | 1.10 |  |  |

| R      | 0.1  |       | 0.25 |  |  |

| R1     | 0.1  |       |      |  |  |

| θ      | 0    |       | 10*  |  |  |

| 01     | 0    |       |      |  |  |

| у      |      |       | 0.1  |  |  |

| Z      |      | 0.75  |      |  |  |

20

ħ

BASE METAL SECTION A-A'

Tab: 835-12

Wuxi I-CORE Electronics Co., Ltd. <sup>12</sup> rev:B3 Number: AiP160

Number: AiP16C23-AX-XS-A067EN

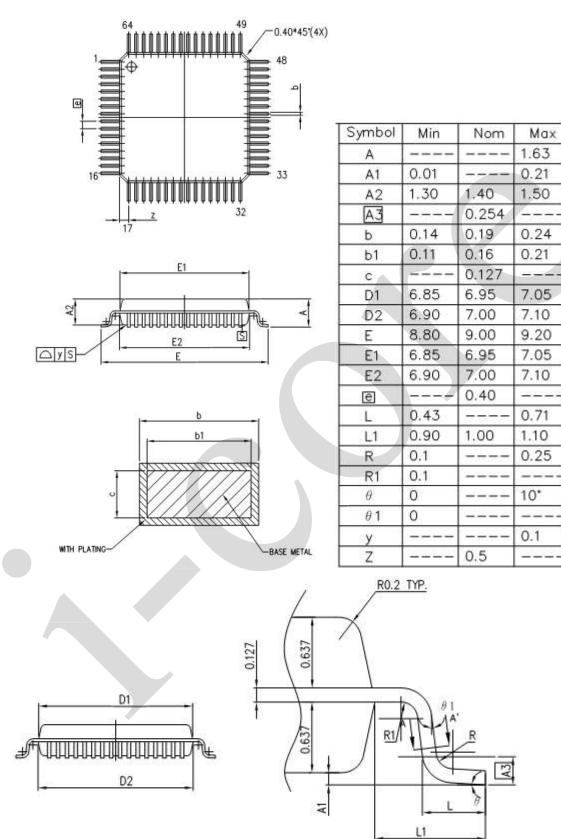

7.2、LQFP64

#### 8. Statements And Notes

#### 8.1. The name and content of Hazardous substances or Elements in the product

|                               | Hazardous substances or Elements                                                                                            |                                                 |                                                    |                                                 |                                     |                                                  |                          |                                  |                                          |                                 |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|----------------------------------------------------|-------------------------------------------------|-------------------------------------|--------------------------------------------------|--------------------------|----------------------------------|------------------------------------------|---------------------------------|

| Part name                     | Lead<br>and<br>lead<br>compou<br>nds                                                                                        | Mercur<br>y and<br>mercur<br>y<br>compo<br>unds | Cadm<br>ium<br>and<br>cadmi<br>um<br>comp<br>ounds | Hexaval<br>ent<br>chromiu<br>m<br>compoun<br>ds | Polybro<br>minated<br>biphenyl<br>s | Polybro<br>minate<br>d<br>biphen<br>yl<br>ethers | Dibutyl<br>phthala<br>te | Butylbe<br>nzyl<br>phthala<br>te | Di-2-et<br>hylhex<br>yl<br>phthala<br>te | Diisobu<br>tyl<br>phthala<br>te |

| Lead<br>frame                 | 0                                                                                                                           | 0                                               | 0                                                  | 0                                               | 0                                   | 0                                                | 0                        | 0                                | 0                                        | 0                               |

| Plastic<br>resin              | 0                                                                                                                           | 0                                               | 0                                                  | 0                                               | 0                                   | 0                                                | 0                        | 0                                | 0                                        | 0                               |

| Chip                          | 0                                                                                                                           | 0                                               | 0                                                  | 0                                               | 0                                   | 0                                                | 0                        | 0                                | 0                                        | 0                               |

| The lead                      | 0                                                                                                                           | 0                                               | 0                                                  | 0                                               | 0                                   | 0                                                | 0                        | 0                                | 0                                        | 0                               |

| Plastic<br>sheet<br>installed | 0                                                                                                                           | 0                                               | 0                                                  | 0                                               | 0                                   | 0                                                | 0                        | 0                                | 0                                        | 0                               |

|                               | •: Indicates that the content of hazardous substances or elements in the detection limit                                    |                                                 |                                                    |                                                 |                                     |                                                  |                          |                                  |                                          |                                 |

| explanatio                    | of the following the SJ/T11363-2006 standard.                                                                               |                                                 |                                                    |                                                 |                                     |                                                  |                          |                                  |                                          |                                 |

| n                             | ×: Indicates that the content of hazardous substances or elements exceeding the SJ/T11363-2006 Standard limit requirements. |                                                 |                                                    |                                                 |                                     |                                                  |                          |                                  |                                          |                                 |

#### 8.2、Notion

Recommended carefully reading this information before the use of this product;

The information in this document are subject to change without notice;

This information is using to the reference only, the company is not responsible for any loss;

The company is not responsible for the any infringement of the third party patents or other rights of the responsibility.