# Am2833/2533

1024-Bit Static Shift Registers

## **Distinctive Characteristics**

- Second source to Signetics 2533

- All inputs are low-level DTL/TTL compatible

- Static operation with single clock input.

#### FUNCTIONAL DESCRIPTION

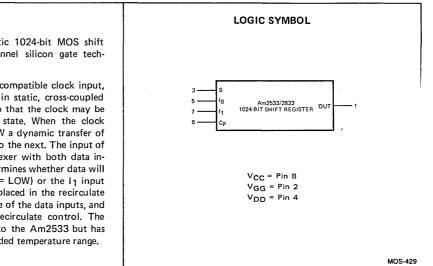

The Am2533/2833 is a quasi-static 1024-bit MOS shift register using low-threshold P-channel silicon gate technology.

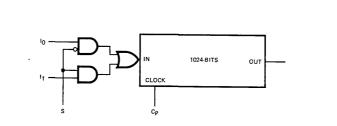

The device has a single TTL/DTL compatible clock input, Cp. Data in the register is stored in static, cross-coupled latches while the clock is LOW, so that the clock may be stopped indefinitely in the LOW state. When the clock shifts from LOW to HIGH to LOW a dynamic transfer of data occurs from one static latch to the next. The input of the register is a two-input multiplexer with both data inputs available. A select line, S, determines whether data will be accepted from the I<sub>0</sub> input (S = LOW) or the I<sub>1</sub> input (S = HIGH). The register can be placed in the recirculate mode by tying the output, O, to one of the data inputs, and using the select line as a write/recirculate control. The Am2833 is functionally identical to the Am2533 but has superior performance over an extended temperature range.

DC to 2.0MHz operation with Am2833

LOGIC DIAGRAM

MOS-43

ORDERING INFORMATION

| Package<br>Type | Temperature<br>Range | Am2533<br>Order<br>Number | Am2833<br>Order<br>Number |

|-----------------|----------------------|---------------------------|---------------------------|

| Molded DIP      | 0°C to +70°C         | AM2533V                   | AM2833PC                  |

| Hermetic DIP    | 0°C to +70°C         | AM2533DC                  | AM2833DC                  |

| Hermetic DIP    | –55°C to +125°C      |                           | AM2833DM                  |

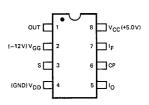

CONNECTION DIAGRAM Top View

Note: Pin 1 marked for orientation

## Am2833/2533

#### MAXIMUM RATING (Above which the useful life may be impaired)

| Storage Temperature              | -65°C to +150°C                               |

|----------------------------------|-----------------------------------------------|

| Temperature (Ambient) Under Bias | –55°C to +125°C                               |

| V <sub>DD</sub> Supply Voltage   | V <sub>CC</sub> -20V to V <sub>CC</sub> +0.3V |

| V <sub>GG</sub> Supply Voltage   | V <sub>CC</sub> –20V to V <sub>CC</sub> +0.3V |

| DC Input Voltage                 | V <sub>CC</sub> –20V to V <sub>CC</sub> +0.3V |

#### **OPERATING RANGE**

| Part No.                               | Temperature    | Vcc      | V <sub>GG</sub> | VDD |  |

|----------------------------------------|----------------|----------|-----------------|-----|--|

| Am2833PC/Am2533PC<br>Am2833DC/Am2533DC | 0°C to +70°C   | 5.0V ±5% | -12V ±5%        | 0V  |  |

| Am2833DM                               | 55°C to +125°C | 5.0V ±5% | -12V ±5%        | ٥v  |  |

## ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE (Unless Otherwise Noted)

| Parameters            | Description                               | Test                                                                   | Conditions                  | Min.                          | Typ.<br>(Note 1)     | Max.                 | Units |    |

|-----------------------|-------------------------------------------|------------------------------------------------------------------------|-----------------------------|-------------------------------|----------------------|----------------------|-------|----|

| VOH                   | Output HIGH Voltage                       | V <sub>CC</sub> = MIN., I <sub>OH</sub> =                              | —100μA                      | 2.4                           | 3.5                  |                      | Volts |    |

| <b>v<sub>ol</sub></b> | Output LOW Voltage                        | V <sub>CC</sub> = MIN., I <sub>OL</sub> =                              | 1.6mA                       |                               | 0.2                  | 0.4                  | Volts |    |

| v <sub>IH</sub>       | Input HIGH Level                          | Guaranteed input logical<br>HIGH voltage for all inputs                |                             | V <sub>CC</sub> 1<br>(Note 3) |                      | V <sub>CC</sub> +0.3 | Volts |    |

| VIL                   | Input LOW Level                           | Guaranteed input logical LOW<br>voltage for all inputs                 |                             | V <sub>GG</sub>               |                      | 0.8                  | Volts |    |

| ήL                    | Input LOW Current                         | V <sub>CC</sub> = MAX., V <sub>IN</sub> =                              | = 0V, T <sub>A</sub> = 25°C |                               | 10                   | 500                  | nA    |    |

| Чн                    | Input HIGH Current                        | T <sub>A</sub> = 25°C, V <sub>IN</sub> = V <sub>CC</sub> -1.0 (Note 3) |                             | -150                          | -300                 |                      | μA    |    |

| Чт                    | Peak input transition<br>current (Note 3) | $1.5 \le V_{SS} - V_{IN} \le 4.0, T_A = 25^{\circ}C$                   |                             |                               |                      | -1.6                 | mA    |    |

| V <sub>Imax</sub>     | Voltage at maximum<br>input current       | T <sub>A</sub> = 25°C                                                  |                             | ∨ <sub>SS</sub> –4.0          | V <sub>SS</sub> -3.0 | V <sub>SS</sub> -1.5 | v     |    |

|                       | Mars Davian Cumplu                        | f = 1.5MHz                                                             | Am2533                      |                               | 16                   | 30                   |       |    |

| Icc                   | V <sub>CC</sub> Power Supply<br>Current   |                                                                        | 6 - 0 0000-                 | Am2833PC, DC                  |                      | 16                   | 54    | mA |

|                       |                                           | f = 2.0MHz                                                             | Am2833DM                    |                               | 20                   | 70                   |       |    |

|                       | V <sub>GG</sub> Power Supply              | f = 1.5MHz                                                             | Am2533                      |                               | 5.0                  | -7.5                 |       |    |

| IGG                   |                                           |                                                                        | f = 2.0MHz                  | Am2833PC, DC                  |                      | 5.0                  | -14   | mA |

|                       | Current                                   |                                                                        | Am2833DM                    |                               | -7.0                 | -18                  |       |    |

ctes: 1. Typical limits are at  $V_{CC}$  = 5.0V,  $V_{GG}$  = -12V, 25°C ambient. 2. Power supply currents are with inputs and outputs open.

A special input pull-up circuit becomes active at V<sub>IN</sub> = V<sub>SS</sub> -3.5V to pull the internal input node up to the MOS threshold. To return the internal node to the LOW state, current must be drawn from the MOS input. This current is maximum at approximately 2.0V.

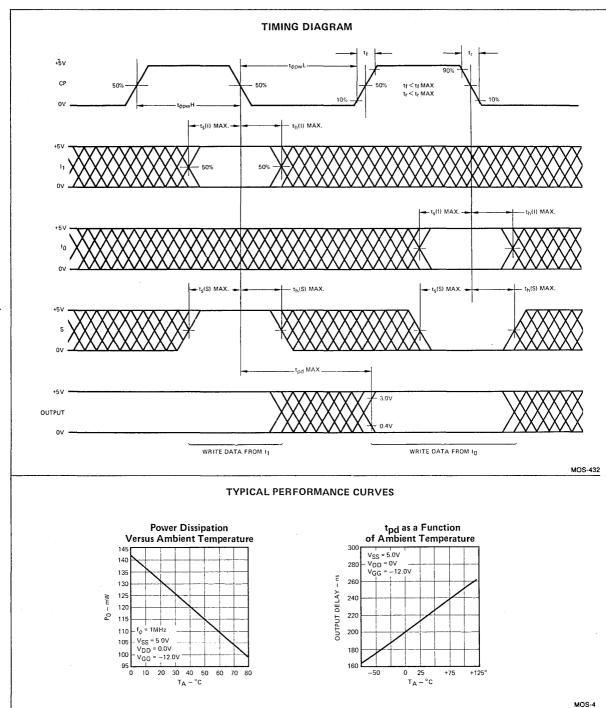

## NITCHING CHARACTERISTICS OVER OPERATING RANGE (Unless Otherwise Noted)

| rameters                        | Description                                                            | Test Conditions                       | Min.  | Am2533<br>Typ.<br>(Note 1) | Max. | Min.  | Am2833<br>Typ. | Max. | Units |

|---------------------------------|------------------------------------------------------------------------|---------------------------------------|-------|----------------------------|------|-------|----------------|------|-------|

| f <sub>max</sub>                | Maximum Clock Frequency                                                |                                       | 1.5   | 2.0                        |      | 2.0   | 3.0            |      | MHz   |

| t <sub>øpw</sub> L              | Clock LOW Time                                                         |                                       | 0.250 |                            | ~~   | 0.200 |                | ~~~  | μs    |

| t <sub>opw</sub> H              | Clock HIGH Time                                                        |                                       | 0.350 |                            | 100  | 0.250 |                | 100  | μs    |

| t <sub>r</sub> , t <sub>f</sub> | Clock Rise and Fall Times                                              | · · · · · · · · · · · · · · · · · · · |       |                            | 1    |       |                | 1    | μs    |

| t <sub>s</sub> (i)              | Set-up Time, IO or I1 Input<br>(see definitions)                       |                                       | 50    |                            |      | 50    |                |      | ns    |

| t <sub>h</sub> (I)              | Hold Time, I <sub>0</sub> or I <sub>1</sub> Input<br>(see definitions) |                                       | 50    |                            |      | 50    |                |      | ns    |

| t <sub>S</sub> (S)              | Set-up Time, S Input<br>(see definitions)                              | $t_r = t_f \le 25 ns$                 | 80    |                            |      | 80    |                |      | ns    |

| t <sub>h</sub> (S)              | Hold Time, S Input<br>(see definitions)                                |                                       | 50    |                            |      | 50    |                |      | ns    |

| t <sub>pd</sub>                 | Delay, Clock to Output<br>LOW or HIGH                                  | RL = 2.9k, CL = 20pF                  |       |                            | 300  |       |                | 300  | ns    |

| pr, tpf                         | Output Rise and Fall Times                                             | 10% to 90%                            |       |                            | 150  |       |                | 150  | ns    |

| Din                             | Capacitance, Any Input (Note 2)                                        | f = 1 MHz, VIN = VCC                  |       | 3                          | 5    |       | 3              | 5    | pF    |

es:

1. Typical limits are at V<sub>CC</sub> = 5.0V, V<sub>GG</sub> = -12.0V and T<sub>A</sub> = 25°C 2. This parameter is periodically sampled but not 100% tested. It is guaranteed by design.

### **DEFINITION OF TERMS**

STATIC SHIFT REGISTER A shift register that is capable of maintaining stored data without being continuously clocked. Most static shift registers are constructed with dynamic master and static slave flip-flops. The data is stored dynamically while the clock is HIGH and is transferred to the static slaves while the clock is LOW. The clock may be stopped indefinitely in the LOW state, but there are limitations on the time it may reside in the HIGH state.

SET-UP and HOLD TIMES The shift register will accept the c that is present on its input around the time the clock goes fr HIGH-to-LOW. Because of variations in individual devices, th is some uncertainty as to exactly when, relative to this cl transition, the data will be stored. The set-up and hold ti define the limits on this uncertainty. To guarantee storing correct data, the data inputs should not be changed betw the maximum set-up time before the clock transition and maximum hold time after the clock transition. Data chai within this interval may or may not be detected.

MOS-434

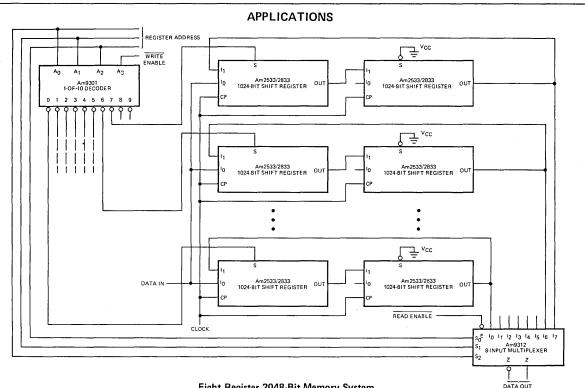

#### Eight Register 2048-Bit Memory System

Data enters one of the eight 2048-bit registers when the write enable input to the decoder is LOW. The addressed register will accept the data on the data input; the other seven registers will recirculate their data. Outputs are driven directly into an Am9312 8-input multiplexer. Obviously, the read and write registers need not be the same.

## TRUTH TABLE

| s | I <sub>0</sub> | I <sub>1</sub> | Data Entered |

|---|----------------|----------------|--------------|

| L | L              | x              | L            |

| L | н              | х              | Н            |

| н | х              | L              | L            |

| н | х              | н              | н            |

| 1 |                |                |              |

H = HIGH Voltage level L = LOW Voltage Level

X = Don't Care

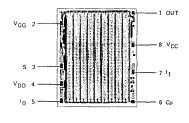

DIE SIZE: 0.133" X 0.163"