# Am95C60 Quad Pixel Dataflow Manager

Advanced Micro Devices

Applications Handbook

# **Advanced Micro Devices**

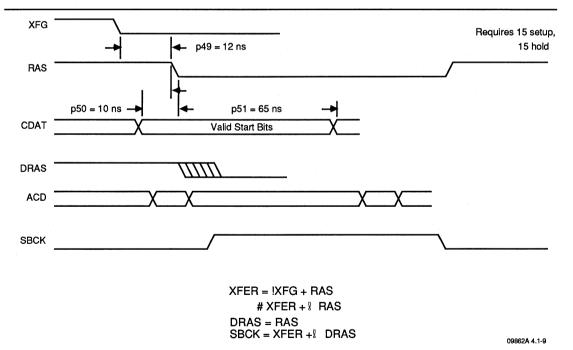

# Am95C60 QPDM Quad Pixel Dataflow Manager

# Applications Handbook

# © 1988 Advanced Micro Devices

Advanced Micro Devices reserves the right to make changes in its products without notice in order to improve design or performance characteristics.

This handbook neither states nor implies any warranty of any kind, including but not limited to implied warranties of merchantability or fitness for a particular application. AMD assumes no responsibility for the use of any circuitry other than the circuitry embodied in an AMD product.

The information in this publication is believed to be accurate in all respects at the time of publication, but is subject to change without notice. AMD assumes no responsibility for any errors or omissions, and disclaims responsibility for any consequences resulting from the use of the information included herein. Additionally, AMD assumes no responsibility for the functioning of undescribed features or parameters.

901 Thompson Place, P.O. Box 3453, Sunnyvale, California 94088-3000 (408)732-2400 TWX: 910-339-9280 TELEX: 34-6306

Authors:

Tom Crawford Stuart Tindall Ed Dupuis Wolfgang Reis Achim Strupat Chapters 3.0, 3.2, 3.3, 4, 5, and 6. Chapters 1 and 3.1. Chapter 2.1. Chapter 2.2. Chapter 2.3.

1

# Introduction

This QPDM Applications Handbook is the third in a series of documents describing the Am95C60 Quad Pixel Data Manager (QPDM) device and its use in graphics systems.

The first, most basic document is the QPDM data sheet (Order Number 07013B) which gives a terse functional description plus a very detailed listing of the electrical and timing parameters, as well as package, pin-out, and ordering information. This data sheet will be updated for any parametric changes, e.g. speed enhancements, made as the device matures.

The second document is the QPDM Technical Manual (Order Number 07785B). It provides a more complete functional description and explains each of the 61 instructions in detail.

The third document, this QPDM Applications Handbook, describes a wide variety of interfaces to the QPDM. The System Bus is covered in Chapters 2 and 5, the Display Memory Bus is covered in Chapters 3 and 5, the Memory Bus in Chapters 4 and 5.

Chapter 6 contains some programming hints and a complete initialization program.

# **Table of Contents**

| CHAPTER 1                    | 1 Overview                     |                                        |      |

|------------------------------|--------------------------------|----------------------------------------|------|

|                              | DESIC                          | 1-1                                    |      |

| CHAPTER 2                    | CHAPTER 2 System Bus Interface |                                        |      |

|                              | 2.1                            | Am9560 - 80186 INTERFACE DESIGN        | 2-1  |

|                              | 2.2                            | VME BUS                                | 2-28 |

|                              | 2.3                            | 68020 BUS                              | 2-34 |

| CHAPTER 3 Display Memory Bus |                                |                                        | 3-1  |

|                              | 3.1                            | DISPLAY MEMORY CONNECTIONS OF THE QPDM | 3-1  |

|                              | 3.2                            | DISPLAY MEMORY PROGRAM                 | 3-16 |

|                              | 3.3                            | FONT STORAGE IN KANJI ROMS             | 3-41 |

| CHAPTER 4                    | Video                          | Bus                                    | 4-1  |

|                              | 4.1                            | VIDEO BUS                              | 4-1  |

|                              | 4.2                            | SERIALIZERS IN GENERAL                 | 4-1  |

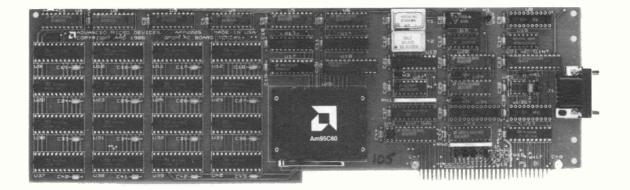

| CHAPTER 5                    | Evalu                          | ation and Demonstration Board          | 5-1  |

|                              | 5.1                            | PC INTERFACE                           | 5-1  |

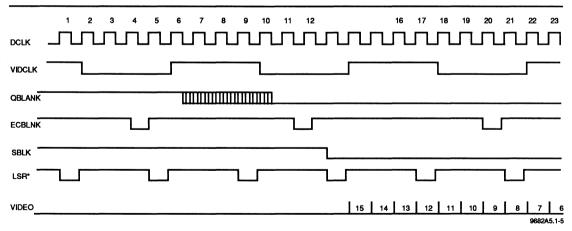

|                              | 5.2                            | DISPLAY MEMORY INTERFACE               | 5-3  |

|                              | 5.3                            | TIMING GENERATOR                       | 5-4  |

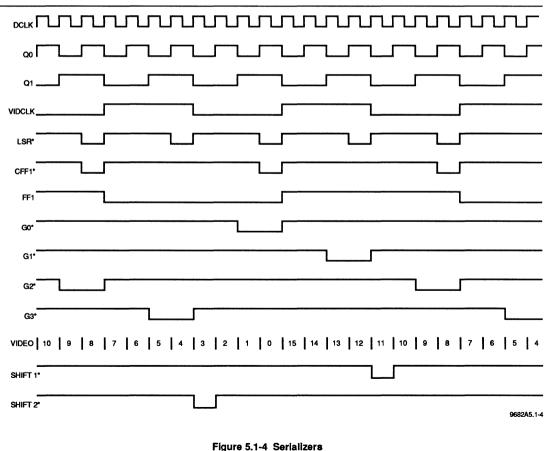

|                              | 5.4                            | SERIALIZERS                            | 5-5  |

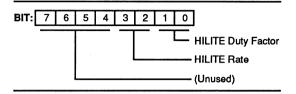

|                              | 5.5                            | COLOR LOOKUP TABLE AND DACS            | 5-7  |

|                              | 5.6                            | EPROMS                                 | 5-8  |

|                              | 5.7                            | MEMORY BUS TIMING ANALYSIS             | 5-8  |

|                              | 5.8                            | SOFTWARE                               | 5-15 |

|                              | 5.9                            | PAL DEVICE EQUATIONS                   | 5-16 |

|                              | 5.10                           | USERS GUIDE                            | 5-23 |

|                              |                                | DIAGRAMS                               | 5-24 |

| CHAPTER 6                    | Softw                          | are                                    | 6-1  |

|                              | 6.1                            | INITIALIZATION                         | 6-1  |

|                              | 6.2                            | COPY BLOCK OPERATORS IN THE QPDM       | 6-6  |

# **CHAPTER 1**

٠

Overview DESIGN APPLICATIONS

1-1

# CHAPTER 1 Overview

# Interface helps controller boost graphics performance

Stuart Tindall and Achim Strupat

Advanced Micro Devices Inc., 901 Thompson Pl., P.O. Box 3453, Sunnyvale, CA 94088; (408) 732-2400.

A new generation of graphics processors is hiking the performance of graphic systems by more than an order of magnitude. These devices work their wonders by taking over tasks formerly performed by the system's CPU: frame updating, video refreshing, and memory refreshing. The dedicated processors offload the system CPU of unnecessary tasks while they manipulate image data faster than the original controllers ever could.

The price to pay for the extra speed and the easier

A dedicated graphics processor speeds image handling while making the CPU's job easier. Moreover, its bus interface is a snap to implement. overall system design is the added complexity of connecting one or more graphics processors to the system bus. The task need not be daunting, however. In fact, with the Am95C60 Quad Pixel Dataflow Manager, the connection to the system bus is very straightforward.

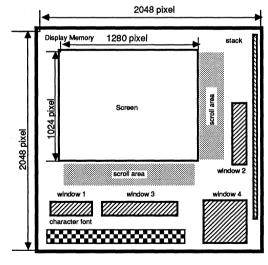

The Am95C60 CMOS device is aimed at minicomputers and workstations built around the 68020 microprocessor. The device manages bit maps of up to 4096 by 4096 pixels and pixel rates of up to 400 MHz, which translates into screen sizes of up to 2000 by 2000 pixels. For reference purposes, today's high-resolution CAD and desktop publishing workstations have 1280-by-1024-pixel displays.

The graphics processor can draw up to 110,000 lines, averaging 10 pixels long, per second; place text at 50,000 characters per second; fill polygons at 20 ns per pixel; and perform bit-block transfers at 60 ns per pixel. One device manages and drives up to four bit-mapped memory planes, and designers can cascade up to 64 devices without slowing performance. As a result, a system based on the Am95C60 processor can support 256 display memory planes.

Moreover, the graphics processor connects directly to video dynamic RAMs and supplies all the signals to drive them. Video dynamic RAMs are dual-port memories that make possible simultaneous display refresh from a serial port and display update through a random-access port. In a highresolution system with video dynamic RAMs, the update bandwidth exceeds 90%, almost triple that with conventional dynamic RAMs.

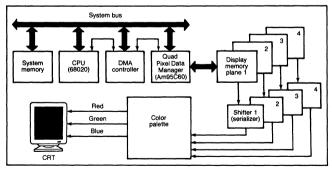

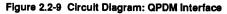

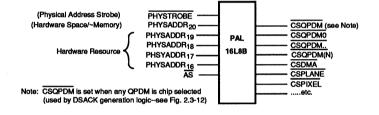

In a typical graphics subsystem, one or more graphics processors connect to the system bus. Other major components include video dynamic RAMs, one serializer per memory plane, a highfrequency dot clock generator, and a color palette (Fig. 1).

Note that the 68020 is a bus master, and the Am95C60 is addressed as a bus slave. If the system did not have a DMA controller, the CPU would be the only bus master, and it would never have to perform bus-arbitration cycles or give away the system bus. The optional DMA controller helps the CPU load instructions into or exchange data with the graphics processor, but the controller must request the bus and use the standard bus-arbitration handshake.

Because the graphics processor is always a system bus slave, the transactions on its interface do not have to be synchronized to a clock. As a result, bus-interface connections are relatively simple, and the graphics processor needs only a small amount of additional logic to work with all common 8-, 16-, or 32-bit microprocessors.

#### 8- OR 16-BIT MODES POSSIBLE

After a reset, the designer can configure the data bus to work in an 8-bit mode with programmable byte order or in a 16-bit mode. In a 68020 system, the 16-bit mode offers the highest throughput. In this case, the device's 16 data lines connect to bits 16 through 31 of the processor's 32-bit data bus.

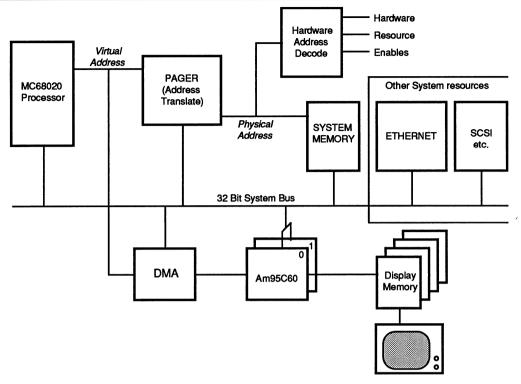

The 68020 accommodates both virtual and direct addressing. Because the processor does not distinguish between memory and I/O addresses, peripherals are memory mapped. Virtual memory management is better when the 68020 is the kernel CPU running a high-level operating system. Then

### CHAPTER 1 Overview

any execution process can access the CPU's total address space—4 Gbytes for the 68020.

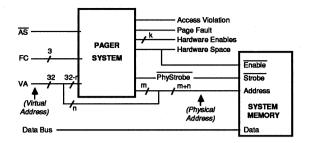

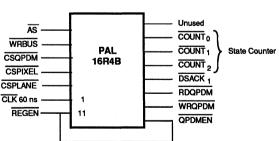

Direct addressing is preferred when the 68020 controls peripheral devices or when the peripherals have unique addresses because only one user can access the quad pixel data-flow manager in an interactive graphics system. Even if this user displays results from a multitasking process, the I/O accesses run sequentially through an operating system driver. Ideally, a PAL device contains the address decoding logic needed to generate the relevant Chip Enable signals to the graphics processor. As a result, the following discussion assumes a direct-addressing scheme.

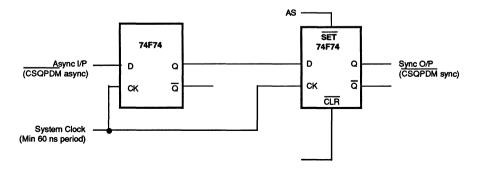

To interface a processor to a peripheral with an independent system bus cycle, as the graphics processor has, several control and response signals must be translated. Also, each device must operate at its own highest clock rate, and therefore, asynchronously.

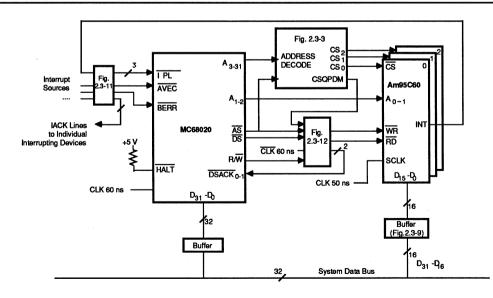

The interface to the Am95C60 includes a 16-bit bidirectional, three-state data bus (lines  $D_0$  to  $D_{15}$ ), Read and Write strobe inputs (RD and WR), a Chip Select input (CS), two address line inputs ( $A_0$  and  $A_1$ ), an interrupt output, three DMA handshake signals, an output that enables an external driver, a reset, and a system clock input. The system clock, which runs at up to 20 MHz, times the internal microengine and controls the display-memory timing, but not the system-bus and video timing. The two address lines connect to four ports within the device.

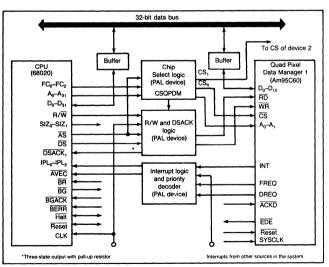

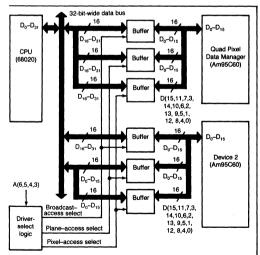

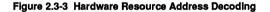

A typical application has a 68020 connected to two Am95C60s that form an eight-plane system (Fig. 2). A PAL device decodes the 68020 address and outputs two Chip Select ( $CS_0$  and  $CS_1$ ) signals to the graphics processors. A third signal, CSQPDM, which shows an access to either graphics processor, combines with the 68020's Read/Write signal to form the read and write inputs for the Am95C60. The timing of the Chip Select signal and the read and write inputs follows the timing of the 68020's Address Strobe, with the addition of the decode logic's propagation delay.

Because all resources within the graphics processor are 16 bits wide, any write cycle to the device results in the 16bit quantity on the bus being loaded into the appropriate register. But the data word must be aligned, because the least significant address line is not used in addressing the resources within the device. Connecting the 68020's address lines,  $A_1$  and  $A_2$ , to the graphics processor's address pins,  $A_0$  and  $A_1$ , allows data to be transferred one word at a time. Consequently, the quad pixel data-flow manager does not need any transfer-size information; the requested 16 bits are always fulfilled. The 68020's address bits  $A_1$ and  $A_2$  connect to the graphics processor's two address inputs,  $A_0$  and  $A_1$ , to select the internal resource for a bus access.

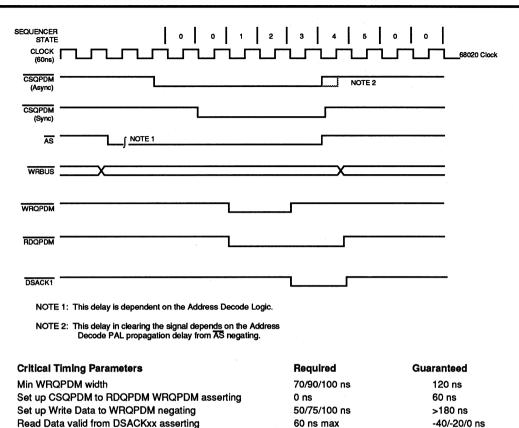

Depending on the speed difference between the two processors, none, one, or more wait states extend the processor's bus cycle. Two lines—Data Transfer and Size Acknowledge (DSACK)—cause wait states in the bus cycle if they are not asserted. To avoid this, the designer can generate DSACK responses that are synchronous to the 68020 clock by using a fixed-delay logic sequence that defines the length of any access to the graphics processor after Address Strobe is asserted.

This delay can be modulated by a registered PAL device, timed by the processor's clock. The PAL device's DSACK outputs are put in a three-state mode because a multiperipheral system may have several sources of DSACK signals. A pull-up resistor on the three-stated outputs defines the logical state when the PAL device is not driving the lines.

The 68020 communicates with the graphics processor over two types of bus cycles: word read and word write. At the beginning of a system bus cycle, the 68020 as the bus master asserts the R/W signal to indicate the direction of data flow. A word read cycle moves data from the

> graphics processor to the CPU, then presents the address and function code to distinguish between user and supervisory address space.

To transfer 16 bits with a word-transfer instruction, the CPU's transfer size outputs, SIZ<sub>1</sub> and SIZ<sub>0</sub>, are set to two bytes (that is, 10H). As noted, however, the Am95C60 does not need this information, if the CPU's address lines and the graphics processor's address pins are properly connected.

Because all transactions are word aligned and word wide, address bit  $A_0$  is always low,

The AM95C60 Quad Pixel Dataflow Manager can accommodate four bitmapped memory planes. A graphics subsystem can include up to 64 devices, for 256 memory planes.

and the information is read in on the data-bus lines  $D_{16}$  through  $D_{31}$ . The 68020 then asserts Address Strobe to show that the address is valid, and activates Data Strobe to indicate that the graphics processor should drive the data bus.

After the CPU produces Chip Select and asserts the read input, the graphics processor needs a specified minimum time to complete the word read bus cycle, depending on the device's speed version. For a 20-MHz device, for instance, the read data on the system bus is valid after a maximum of 110 ns.

Depending on the 68020's clock speed, this time may or may not be fast enough to ensure access without a wait state. To cover the general case, the example assumes that after a certain delay, the graphics processor creates a wait state by asserting the DSACK lines to the CPU. The delay, produced by external logic, is a multiple of the 68020's clock cycle.

Once valid data is on the data bus and the DSACK signals are asserted, the CPU latches the data and terminates the bus cycle by deasserting Data Strobe and Address Strobe. This negates the graphics processor's Read Strobe and lets the device enter the three-state mode on its data bus. To conclude the bus cycle, the PAL device that generates the DSACK signals goes into a three-state mode also.

The pull-up resistor brings the outputs to an inactive state. As soon as the CPU receives the deasserted

DSACK signals, it knows the word read cycle is complete and starts another cycle.

The transactions are similar for a write cycle, except that the R/W signal shows a transfer from the CPU to the graphics processor. In this case the CPU places valid data on the system bus before activating the Data Strobe. Because the Write Strobe to the graphics processor may be as short as 70 ns, fewer wait states are needed than in a Word Read cycle. If any are inserted, the PAL device's DSACK signals again handle them.

Assertion of the two DSACK lines tells the CPU that the graphics processor is ready to latch the data. The 68020 then negates its Address and Data strobes and removes the data from the bus. The graphics processor latches the data with the rising edge of its Write pulse, which is formed from the 68020's Data Strobe pulse. Negation of the DSACK signals by the PAL device after the rising edge of Address Strobe concludes the bus cycle.

#### ADDRESS LINES CONTROL I/O PORTS

The Am95C60 has four I/O ports addressed by lines  $A_0$  and  $A_1$ . Through these ports, the CPU, using its own  $A_1$  and  $A_2$  lines, directly addresses the instruction FIFO buffer and status register, the block I/O FIFO buffer, the I/O-pointer register, and the data registers indicated by that register (see the table, p. 100).

Access to the other registers within the device employs a two-tier process. The operator first loads the address of the desired resource into the I/O-pointer register, through which the resource can be accessed. Then, any subsequent access to the I/O-data register transfers data between the bus master and the register.

In a multiple data-manager system, the processors can be addressed either individually or as a single peripheral. The broadcast mode, in which the CPU transmits data to all quad pixel data managers simultaneously, offers the fastest overall system speed.

In broadcast mode, a global address enables all Chip Select lines. The CPU sends most of the register data during the initialization phase and all but one drawing instruction to the quad pixel data managers. All the graphics processors then execute the same instruction

In the straightforward system bus connection between the Am95C60 graphics processor and the 68020 microprocessor, three PAL devices create the logic needed for the connection. The CPU's clock and the graphics controller's clock are asynchronous, easing the interface.

simultaneously. The 68020's address bits  $A_3$  and  $A_4$  create the required Chip Select signals in a two-data-manager system (see the table again).

The one instruction executed can affect different display memory planes differently, depending on what data is in the display memory and on certain parameters in the quad pixel data manager. Those parameters include activity bits, which define the active planes; color bits, which pick the color the graphics processor draws with; and search bits and listen bits, which show what color is needed in certain planes for fill area instructions.

The instructions that set these parameters include a field denoting which quad pixel data manager is being addressed. Each device compares its plane position with this field to determine whether the device is a target. Thus instructions that change only one quad pixel data manager within an array can be broadcast to all devices.

Initialization of individual Am95C60s is important because the multiple graphics processors in a system may be initialized differently. One graphics processor may be the video master, while the others are video slaves. Each device's position in an array is determined by the Set QPDM Position instruction, which must be sent to each chip individually.

A user activates the Am95C60 graphics engine by initializing several registers that define its environment. For instance, these registers specify the type and size of the connected display memory, the video timing, the dynam-

Adding driver select logic and extra buffers lets the operator of this two-controller system choose a data-transfer scheme from among a 16-bit broadcast technique, a 32-bit by-plane transfer, and a 32bit by-pixel transfer. ic memory refresh frequency, and the screen and window size and position within the display memory.

After initialization, the CPU transmits drawing instructions to the graphics processor. The 60 instructions in the set include drawing lines, moving rectangular blocks, filling triangles, and writing character strings. The selection allows users to create many different types of drawings and to mix graphics and text efficiently.

The graphics processor accepts instructions in three ways: programmed I/O loading, fast loading with an external DMA controller, and program mode. Programmed I/O is the most straightforward method. The host processor directly addresses the instruction FIFO buffer, supplying instructions as long as the buffer has space.

The CPU checks whether the buffer needs service by polling the internal status register or the open-drain FIFO Request (FREQ) output pins, because the FREQ signal is asserted whenever the buffer has room for at least one instruction word.

In a system with multiple graphics processors, all the FREQ pins are tied together and their open-drain structure is connected to an external pull-up resistor that performs a logical AND function. Therefore, only when every device has room in its instruction FIFO buffer will the FREQ node be asserted. The FREQ signal can also be tied into the interrupt structure to request immediate service from the CPU.

Or a DMA channel can load the instruction FIFO buffer directly from system memory. This method also employs the FREQ signal for handshaking with the DMA controller. In effect, the graphics processor requests additional instructions under control of the previously initialized DMA channel.

Finally, the program mode uses the Call instruction to cause the graphics processor to read instructions from the nonvisible part of the display memory, instead of accessing the instruction FIFO buffer. Basically, the program mode switches the device from a Harvard to a von Neumann architecture because the display memory bus both delivers instructions and transports manipulated data.

Essentially, the CPU writes a group of instructions into the display memory. Then a Call instruction is executed, meaning that subsequent instructions are fetched from the display memory. Embedded Calls allow nesting of subroutines within the display memory. A Return instruction restores control to the instruction FIFO buffer.

Users employ Block input and Output instructions to transfer data between the display and system memories. These commands move image, or font, and control data over the Data Input and Output FIFO buffer. Several access methods exist.

Programmed I/O loading is the simplest technique. The data request, DREQ, bit in the status register or the DREQ pin signals when the BLOCK FIFO buffer needs service. As with the FREQ bit, this condition can be tested by polling, by letting it generate an interrupt, or by the AND structure of the open-drain DREQ node.

In addition, a dedicated DMA channel can service the Block FIFO buffer. The Acknowledge Data, ACKD, line allows the DMA channel to accommodate a two-bus-cycle DMA transfer (Flow-Thru Mode) or a single-bus-cycle transfer (Fly-By Mode).

When transferring data between system bus and display memory, the user can access the data by plane or pixel. A by-plane access transfers 16 bits from one plane. On the other hand, a by-pixel access transfers a complete pixel, meaning one-bit from each plane.

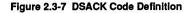

For best efficiency, a designer should choose a transfer scheme that fills the 68020's 32-bit-wide data word. For example, in a two-graphics processor system, a by-plane access transfers 16 bits from each of two planes to the 32bit bus. Or a by-pixel access allows four 8-bit deep pixels to be transferred to the CPU's bus.

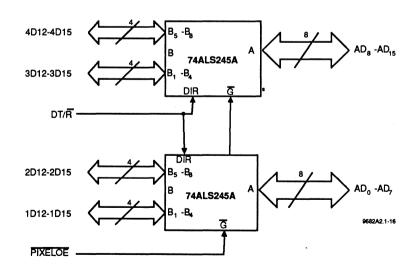

The example application of a two-graphics processor system needs additional data buffers between the system bus and the graphic processors' data lines. These buffers multiplex the relevant data lines to the correct data bits on the bus (Fig. 3).

The 68020 uses the Chip Select lines to enable the buffers and chooses between the additional or the standard access buffers. The choice is implemented by the CPU's address bits  $A_5$  and  $A_6$ , which enable the relevant data bus driver. They select either a 16-bit-wide broadcast access using bits 16 through 31, a 32-bit by-plane access of two planes, or a 32-bit by-pixel access of four 8-bit pixels.

# Addressing the Am95C60's internal resources

|                                                                        | 68020 address lines |    |    |    |    |    |

|------------------------------------------------------------------------|---------------------|----|----|----|----|----|

| Function desired                                                       | A,                  | A, | A, | Α, | A2 | Α, |

| Access instruction FIFO register for<br>write access and access status |                     |    |    |    |    |    |

| register for read access                                               | Х                   | х  | х  | х  | 0  | 0  |

| Access block in/out FIFO register                                      | Х                   | Х  | х  | х  | 0  | 1  |

| Access I/O pointer                                                     | Х                   | х  | х  | х  | 1  | 0  |

| Access register pointed to by<br>I/O pointer                           | х                   | x  | x  | x  | 1  | 1  |

| Both Quad Pixel Data Managers                                          |                     |    |    |    |    |    |

| are accessed (broadcast)                                               | х                   | Х  | 0  | 0  | X  | X  |

| Device 1 is accessed                                                   | х                   | х  | 0  | 1  | х  | х  |

| Device 2 is accessed                                                   | х                   | Х  | 1  | 0  | х  | х  |

| Reserved                                                               | х                   | х  | 1  | 1  | х  | х  |

| 16-bit wide broadcast                                                  | 0                   | 0  | Х  | х  | Х  | Х  |

| Double 16-bit data transfer                                            | 0                   | 1  | х  | х  | х  | х  |

| Four pixel with 8 bits each                                            | 1                   | 0  | х  | х  | х  | х  |

| Reserved                                                               | 1                   | 1  | х  | х  | х  | х  |

\*A, through A, are undefinable.

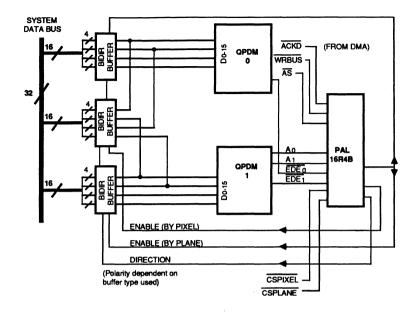

Ten maskable conditions in the Am95C60 can signal interrupts to the CPU over the INT output. Typically, this signal connects to a priority encoder that arranges the interrupts for servicing in preferred order. The encoder than easerts the relevant interrupt levels on the CPU's Interrupt Level Priority lines,  $ILP_0$  to  $ILP_2$ .

When the CPU detects an interrupt level greater than the current one, it waits until the end of the current instruction, saves its state, and generates an interrupt acknowledge bus cycle to find out which device has raised the interrupt. The device responds with either a vector number or by asserting AVEC, which requests an internally generated vector. The Am95C60 employs the autovector method to handle interrupt acknowledge. Both methods point to an interrupt service routine.

On entering the interrupt service routine, the CPU software reads the graphics processor's status register to find out which interrupts are outstanding. The CPU clears the bits for the interrupt it will service by writing to the graphics controller's interrupt acknowledge register and then it re-enables its interrupt system. Writing the register not only tells the graphics chip that the CPU has serviced the interrupt, but it also clears the relevant interrupt bits, which, when set, assert the interrupt line.

Because all Am95C60 controllers in a multi-unit system execute the same instruction simultaneously, any interrupt will be detected by all the devices, and flagged in their status registers. The 68020 reads the status register of one quad pixel data-flow manager, using its individual Chip Select address, to avoid having several chips drive the data bus at the same time. A Write signal to the interrupt acknowledge register of all the Am95C60s clears the interrupt on all the chips.□

Stuart Tindall is a field applications engineer specializing in graphics products. He works out of AMD's UK office in Warrington. Tindall received his electronic engineering degree from Liverpool University, UK.

Achim Strupat, a field application engineer in AMD's Southern California office, previously was a member of the Quad Pixel Dataflow Manager product-planning group in Sunnyvale, Calif. Strupat earned his MSEE at the Rheinisch Westfaelisch Technische Hochscule in Aachen, West Germany.

### CHAPTER 1 Overview

The four main functional blocks of the Am95C60 are the micro engine, system interface, display memory controller, and video timing controller

# **Graphics** controller draws 110,000 lines/sec

#### Controls four bit-mapped memory planes

# KA WAI LEUNG Advanced Micro Devices

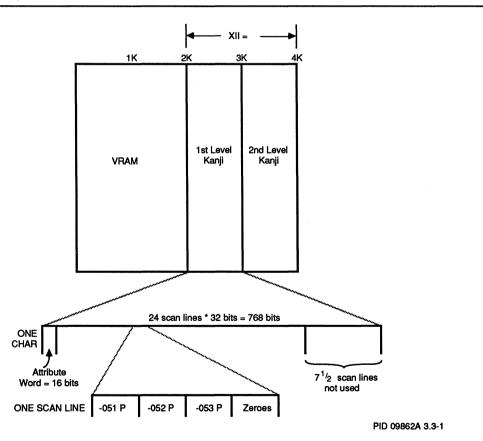

To meet the drawing-speed demands of bit-mapped graphics systems, AMD's Am95C'60 quad pixel dataflow AMD's Am95('60 quad pixel dataflow manager (QPDM) draws as many as 10,000 vectors/sec. The chip also places text at 45,000 cps and fills polygons at a rate of 20 nsec/pixel. This 20.MHz CMOS processor has four 16-bit-wide data-path units and a 16 bit-wide addrass-concourtion unit

16-bit-wide address-generation unit. These units equip the chip to control one to four bit-mapped memory planes for a screen resolution as fine as 2000×2000 pixels. Each displaymemory plane contains as many as 4k×4k bits.

The chin's four 16-bit data units work in parallel, obeying instructions that are decoded and executed in a 16-bit micro engine with a 50-nsec instruction time. In addition, parallel architecture lets you cascade as many as 64 95C'60s to support 256-memoryplane systems with no degradation in performance.

Graphics primitives To speed execution, the device uses hard-wired graphics algorithms to reduce the number of instructions associted with each operation. In con-trast, a programmable graphics processor requires the user to have a detailed knowledge of its internal ar-chitecture and to spend time develop-

chitecture and to spend time develop-ing software. The 95C60's instruction set sup-ports the implementation of such graphics standards as Computer Graphics Interface (CGI), Graphical Kernel System (GKS), and Graphics Device Interface (GDI). A micro engine handles instruction execution.

#### Functional blocks

The micro engine, one of four main functional blocks on the chip, uses a

ROM with microcode wide enough for parallel control of all the execution units. In addition, the engine has a branch sequencer. The second functional block is a

system interface that links the system bus with the various control blocks. Always a slave to the bus, the interface provides a 16-bit bidirectional data path that can be reconfigured to 8 bits for connection to an 8- or 16-bit host processor. To minimize the load host, a dedicated DMA controlon the ler can be used to manage data move-

During DMA operations, the 95C60 uses a 64-word-deep instruction FIFO buffer operating in flow-through mode to minimize CPU waits during instruction transfers. In addi-tion, block-in and block-out buffers tion, block-in and block-out outlers speed data transfer from system memory to the display memory. These block buffers use either flow-through or fly-by DMA.

The third functional block—the display-memory controller-generates display-memory timing and arbitrates uisplay-memory timing and arbitrates video refreshes, memory refreshes, and update accesses. To avoid video and update contentions for the dis-play memories, the 95C60 supports dual-port video RAMs.

#### Video RAMs

Video RAMs improve the updating of graphics memory by more than five times over standard dynamic RAMs. Using video RAMs lets the chip refresh a  $1280 \times 1024$ -pixel screen at 60 Hz noninterlaced, which translates into a 120-MHz pixel rate with more than 90% of the time available for display update.

display update. Another part of the display-memo-ry controller is a translator that lets the CPU use X/Y coordinates for background and window locations. This frees the CPU from having to convert X/Y screen coordinates to dealay memory locations. An addi display-memory locations. An addi-tional feature that reduces CPU inter-

vention is program mode, which lets you store program data, pointer, and stack values alongside the displayable screen

The display-memory controller also has a data-plane controller, which contains four 16-bit data-logic units and four 16-bit bidirectional barrelchiftory

The last main functional block is the video-timing controller, which gener-ates timing signals to control the video monitor and data transmission on the video bus. Twelve video-con-trol registers define horizontal timroi registers denne horizontai tim-ings, vertical timings, and operating mode. You can program the 95C60 to be the horizontal master or slave(s) and the vertical master or slave(s) of another video source in the system.

#### Block conv

One of the 95C60's most useful capabilities is block copy. Operating at 50-nsec/pixel, the chip moves large blocks of data within the bit map, allowing source and destination overlaps without contention or loss of data

During block copy, source data can be rotated in 90° increments, mirrored, and zoomed independently in X and Y directions. You can perform logical operations to the source pixel before it is written to the destination. before it is written to the destination. Because the 95C60 supports mask write in video RAMs, the user can preserve data integrity in selected memory planes during memory ac-

The block-copy feature also sup-ports one hardware window and many software windows. Unlike software

BEHIND THE DESIGN

#### **Bit-map design** called for video RAMs

AMD started designing the AMD started designing the Am95C60 at the beginning of 1982: in response to increasing demand for bit-mapped, high-resolution text and graphics displays. The objective was to build a high-per-formance graphics controller based on the company's bit-slice architecture. architecture.

The bit-slice approach lets the designer increase data width by cascading multiple bit-slice pro-cessors. In the 95C60, the pixel width (color resolution) can be increased by cascading 95C60s-one for every four bit planes-without sacrificing drawing performance. One of the biggest design chal-

lenges was keeping the die size <200k mil<sup>2</sup>. This task was complicated by the chip's amount of parallelism and its high degree of in-tegration. Because the initial design called for a display memo-ry that supported dynamic RAMs, the chip needed to incor-porate a large video-stream FIFO buffer. However, the emergence of video RAMs as the preferred type of bit-map memory lead to a decision to drop dynamic-RAM support and substitute on-chin support for video RAMs.

windows, the hardware window does

on or overwrite the image it replaces. When using multiple windows, you can designate the most frequently used window as the hardware window used window as the hardware window and all remaining windows as soft-ware windows. The 95C60 responds rapidly to window movements by altering pointers instead of bit-map contents

In addition to windowing, the chip supports panning, scrolling, and zooming of graphics primitives drawn zooming of graphics primitives drawn in various line styles. The 95C60 uses an antialiasing scheme that smooths out the jagged edges of lines, arcs, and circles by illuminating adjacent pixels.

Other 95C60 capabilities include Support of proportional spacing and fonts as large as  $63 \times 60$  pixels—30 times larger than the 9×14-pixel char-acter font of an IBM PC. This large font capability allows the chip to support such foreign-language character sets as Kanji, which requires 24×24 pixels to produce Japanese charac-

The 95C60 comes in a 144-pin pingrid-array package. Prices are \$198.57 for the 12-MHz version, \$250 \$198.57 for the 12-MHz version, \$250 for the 16-MHz unit, and \$278.57 for a 20-MHz device (100). Production quantities are available now; delivery, four to six weeks ARO.

more information For on the Am95C60 graphics controller.

Ka Wai Leung is senior strategic-development engineer at Advanced Micro Devices Inc, Box 3453, Sunny-vale, CA 94088. Phone (408) 749-3412.

# **CHAPTER 2**

# System Bus Interface

| 2.1 | Am9560 - 80186 INTERFACE DESIGN | 2-1  |

|-----|---------------------------------|------|

| 2.2 | VME BUS                         | 2-28 |

| 2.3 | 68020 BUS                       | 2-34 |

# CHAPTER 2 System Bus Interface

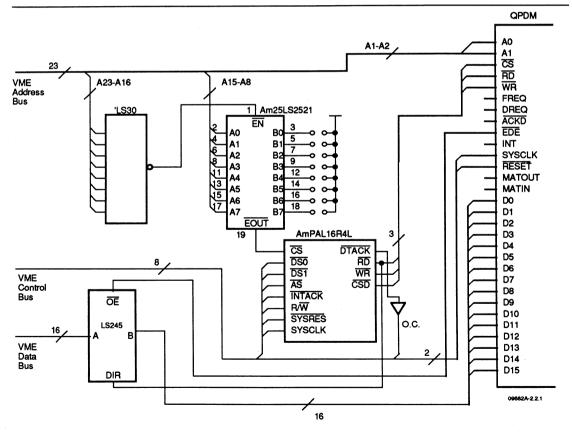

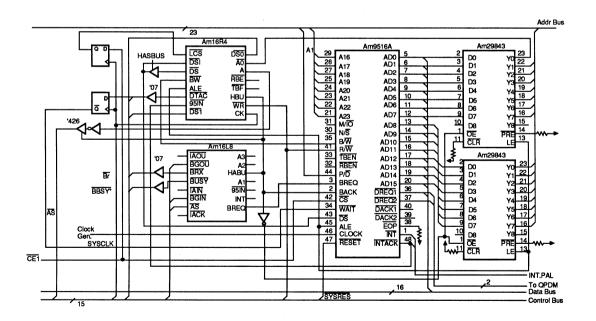

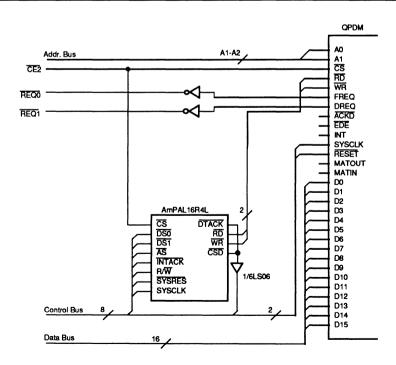

In this section, detailed descriptions of the System Bus Connections for three popular buses are presented. These are the 80186 microprocessor bus, the VME bus, and the 68020 microprocessor bus. We also include schematic diagrams and PAL device equations. While these designs have not actually been built and tested, they have undergone substantial "paper testing".

For a detailed analysis of a demonstration/evaluation board that has already been built and tested, please refer to Section 5.

# 2.1 Am9560 - 80186 INTERFACE DESIGN

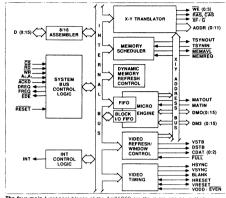

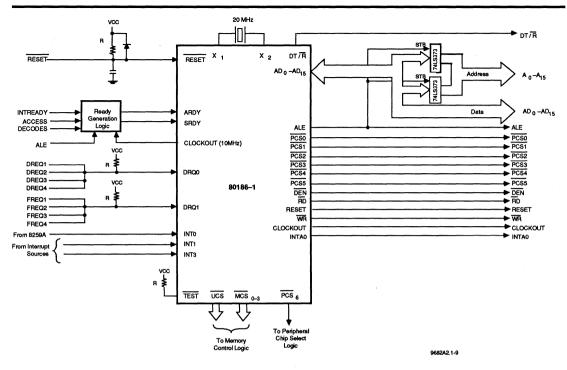

In this section, two designs employing the Am95C60 are discussed in detail. A single Am95C60 system (i.e., four bit planes) will first be discussed and then a four Am95C60 system (i.e., 16 bit planes) will conclude this section. The major theme in these designs is to keep chip count and cost to a minimum. The designs use a 10 MHz

80186 and a 20 MHz Am95C60. The features of both the Am95C60 and the 80186 help to achieve these goals.

# 2.1.1 Single QPDM Design

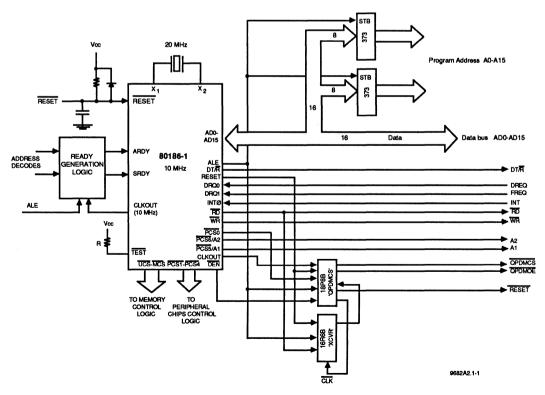

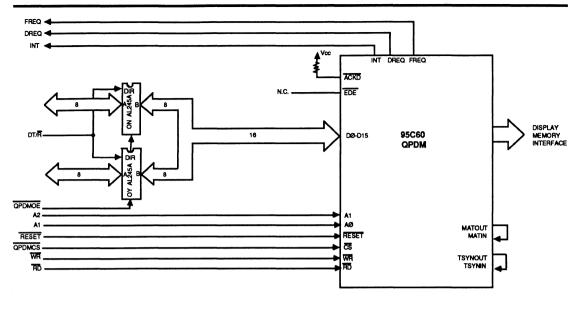

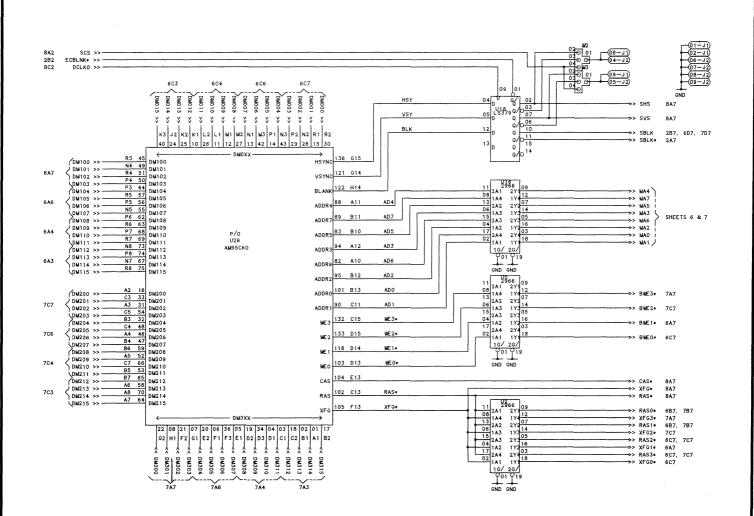

Figure 2.1-1, "Single QPDM Schematic", shows schematically how to connect a single QPDM.

# Read Cycle

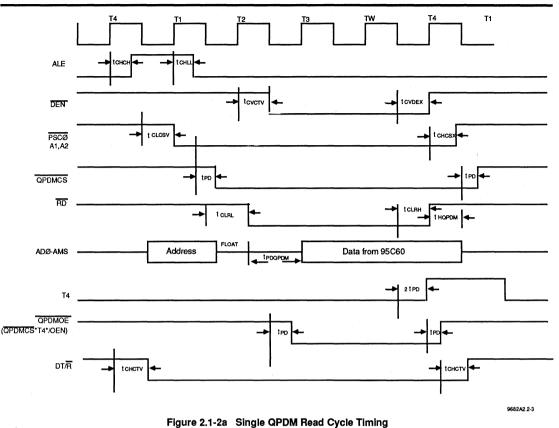

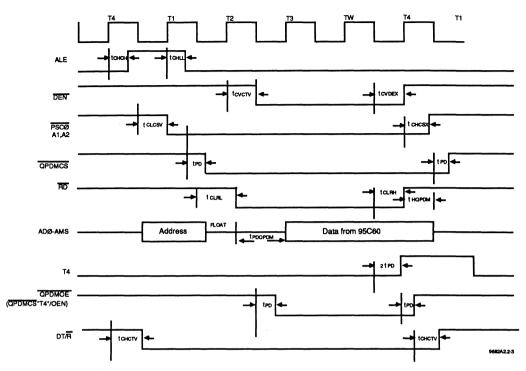

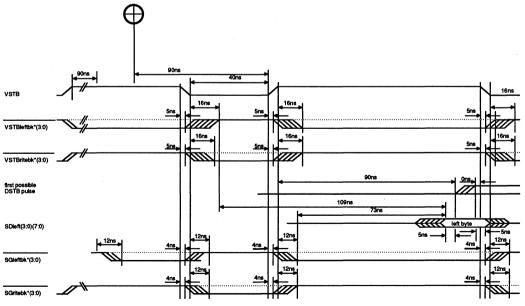

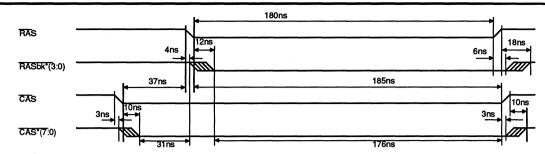

Figure 2.1-2a, "Single QPDM Read Cycle Timing", shows the QPDM read cycle when using a 10 MHz 80186. In this design the  $PCS_5$  and  $PCS_6$  output pins have been programmed to reflect the state of the A<sub>1</sub> and A<sub>2</sub> address lines and  $PCS_6$  is used to select the QPDM.

These outputs  $(A_1 \text{ and } A_2)$  are latched throughout the cycle. The address bits and  $PCS_0$  become valid simultaneously so that the address lines are not guaranteed stable at the Am95C60 when chip select goes active. This means that the QPDM chip select must be delayed

as a result of having to be qualified by ALE. This can be made more apparent by examining the PAL equations. The PAL device "QPDMCS" solves two problems: the set-up time of addresses to chip select, and the qualification of addresses with ALE. Figure 2.1-2a, "Single QPDM Read Cycle Timing", illustrates that after PCS<sub>0</sub> goes active and addresses A<sub>1</sub> and A<sub>2</sub> are latched (via PCS5 and PCS6), the PCS<sub>0</sub> to the QPDM is delayed by waiting for the falling edge of ALE. The RD signal generated by the 80186 is guaranteed active t<sub>CLRL</sub> ns after the falling edge of T2. In the worst case, this is 56 ns. The data from the QPDM is guaranteed valid 80 ns after RD becomes active. The allowable read access time is

200 ns -

$$(t_{CLRLmax} + t_{DVCLmin})$$

= 200 - (55 + 15)

= 130 ns.

The 80186 samples data on the falling edge of  $T_4$ . This means that data from the QPDM is presented to the 80186 in plenty of time to meet the 80186 set-up times of tDVCLmin (15 ns). The QPDM also guarantees that the read data will be held a minimum of 10 ns from the rising

edge of  $\overline{RD}$ . This provides more than adequate hold time ( $t_{cLDXmin} = 3 \text{ ns}$ ) for the processor. Figure 2.1-2a, "Single QPDM Read Cycle Timing", illustrates this quite clearly.

The only other parameter of concern during a read cycle is  $t_{RHAV}$  (not shown in the diagrams). This parameter is the minimum time from  $\overline{RD}$  inactive until addresses are active for the next bus cycle. If memory or peripheral devices cannot disable their output drivers in this time, data buffers will be required to prevent both the 80186 and the peripheral or memory device from driving the data/address lines concurrently. In most designs a data transceiver is required due to the dc characteristics of the QPDM. This can be attributed to the CMOS I/O structures of the QPDM. To guarantee the design, a data transceiver is used. This will be the case in a multiple Am95C60 design as well.

With this in mind, we must now examine the implications of using a data transceiver. The parameter of interest here is the minimum time from RD inactive until the addresses become active for the next cycle, which has a minimum value of 60 ns for a 10 MHz 80186. This means

Figure 2.1-2b Single 95C60 Schematic

|                           | MIN (ns) | MAX (ns) |

|---------------------------|----------|----------|

| <sub>нсн</sub> (80186-1)  |          | 30       |

| (80186-1)                 |          | 30       |

| исту (80186-1)            | 5        | 56       |

| (80186-1)                 | 10       | 56       |

| (80186-1)                 |          | 45       |

| (80186-1)                 | 5        | 32       |

| (B-Speed PAL)             |          | 15       |

| ์ <sub>คเ</sub> (80186-1) | 10       | 56       |

| ян (80186-1)              | 10       | 44       |

| (95C60-20)                | 10       |          |

| ром (95С60-20)            |          | 80       |

| сту (80186-1)             | 10       | 44       |

that the data and the associated driving data transceiver must be off the bus 60 ns after RD goes inactive. The EDE pin provided on the Am95C60 to control the output enable pin of the data transceivers goes inactive far too late in the read cycle to disable the transceiver and meet the tRHAV specification. The DEN signal of the 80186 can go inactive a  $t_{CVDEX}$  maximum of 56 ns after the falling edge of T<sub>4</sub>. The minimum  $t_{CLRH/RD}$  inactive delay is 10 ns. If we add to this set of parameters the maximum terz

9682A2.2-2

this already exceeds the t<sub>BHAV</sub> spec of 60 ns.

The solution is to synthesize a signal from the existing processor signals that will allow us to turn off the transceivers after the falling edge of  $T_4$  more quickly. The small state machine PAL device "XCVR" accomplishes this goal. Figure 2.1-3, "Transceiver Enable/Disable Timing", illustrates how the circuit works. An inverted CLK<sub>(out)</sub> clocks the entire state machine. The purpose of this state machine is to output a signal  $T_4$  at the beginning of state  $T_4$  of the 80186. ALE informs the circuit when state  $T_1$  has occurred. This signal counts through until we get to state  $T_w$ . This is a wait state that is automatically inserted by the 80186 when we read from or write to the Am95C60. The reason for a wait state will become clear when the topic of DMA is discussed.

When the cycle reaches  $T_w$ ,  $T_4$  is also qualified by the signal  $\overline{RD}$ . If we are not reading the Am95C60, we do not generate signal  $T_4$ . In the case of a write cycle, we have no  $t_{RHAV}$  specification, and the CPU signal  $\overline{DEN}$  is allowed to disable the data transceivers. More on this later.

Figure 2.1-3 Transceiver Enable/Disable Timing

| Transceiver Enable/Disable Timing                                                                                                                                 |          |          |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|--|

|                                                                                                                                                                   | MIN (ns) | MAX (ns) |  |

| t <sub>en</sub> (B-Speed PAL)                                                                                                                                     |          | 15       |  |

| t <sub>снин</sub> (80186-1)                                                                                                                                       |          | 30       |  |

| t <sub>cHU</sub> (80186-1)                                                                                                                                        |          | 30       |  |

| $\begin{array}{l} t_{_{\rm PD}} \; (\text{B-Speed PAL}) \\ t_{_{\rm CHLH}} \; (801861) \\ t_{_{\rm CHLL}} \; (801861) \\ t_{_{\rm CIRL}} \; (801861) \end{array}$ | 10       | 56       |  |

The bottom line is that if a read cycle is occurring, the data transceivers are disabled within

$3 \cdot t_{PDmax} + t_{PLZmax} = 3(15) + 15 = 60$  ns.

This meets the  $t_{RHAV}$  specification. The PAL equations are given in the listing XCVR for closer examination. Since the CPU data hold time  $t_{CLDX}$  (8 ns min) and the  $T_4$  transceiver turn off delay are relative to the same clock edge (falling edge of  $T_4$ ), and if we factor in the transceiver delay, the hold time at the processor is guaranteed. The DEN turn-on delay allows:

$$2 \cdot t_{\text{CLCL}} + t_{\text{CHLLmin}} - t_{\text{CVCTVmax}} - t_{\text{DVCL}} = 200 + 44 - 44 - 15 = 185 \text{ ns}$$

transceiver enable time prior to valid data required at the CPU. The PAL outputs, QPDMCS and QPDMOE, use 15 ns maximum of this time to enable the transceiver, and since the Am95C60 places data in the bus a maximum of 80 ns from the active edge of RD, the data will be present in plenty of time to meet the processor set-up time.

The DT/R signal is used to control the direction of the flow of the transceiver. The timing of this signal is no cause for concern.

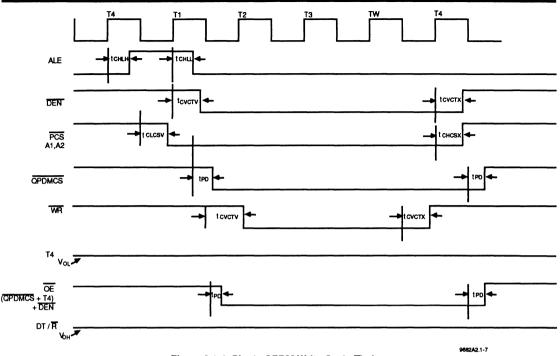

# Write Cycle

The write cycle of the 80186 is very similar. The timing is shown in Figure 2.1-4, "Single QPDM Write Cycle Timing". The WR signal is guaranteed active  $t_{CVCTV}$  ns from the falling edge of  $T_2$  and inactivated  $t_{CVCTV}$  ns from the falling edge of  $T_4$ . The QPDM requires a minimum WR pulse width of 70 ns, the data written to the QPDM must be valid at least 50 ns from the rising edge of WR, and the data must have a finite hold time. The chip select timing is identical to a RD bus cycle. The worst case pulse width of the WR is

$$3 \cdot t_{CLCL} - t_{CVCTXmin}$$

= 300 - (44 + 5)

= 251 ns

Figure 2.1-4 Single QPDM Write Cycle Timing

|                               | Parameter List |          |  |

|-------------------------------|----------------|----------|--|

|                               | MIN (ns)       | MAX (ns) |  |

| t <sub>снын</sub> (80186-1)   |                | 30       |  |

| t <sub>снц</sub> (80186-1)    |                | 30       |  |

| t <sub>сvстv</sub> (80186-1)  | 10             | 44       |  |

| t <sub>cvctx</sub> (80186-1)  | 5              | 44       |  |

| t <sub>clcsv</sub> (80186-1)  |                | 45       |  |

| t <sub>cHCSX</sub> (80186-1)  | 5              | 32       |  |

| ten (B-Speed PAL)             |                | 15       |  |

| t <sub>сvстv</sub> (80186-1)  | 5              | 56       |  |

| t <sub>cvctx</sub> (80186-1)  | 5              | 44       |  |

| twoppm (95C60-20)             | 70             |          |  |

| t <sub>наром</sub> (95С60-20) | 0              |          |  |

| t <sub>sopdm</sub> (95С60-20) | 50             |          |  |

Single QPDM Write Cycle Timing

This substantially exceeds the minimal 70 ns required by the QPDM. The write data is driven by the 80186 a maximum of 40 ns after the falling edge of  $T_2$ . The data transceivers are enabled a maximum of

$$t_{CHLLmax} + 2t_{PDmax}$$

= 30 + 2(15)

= 60 ns

from the rising edge of T<sub>1</sub>. Therefore, the data will be presented to the QPDM in plenty of time to meet the setup time of 50 ns to the rising edge of  $\overline{WR}$  (which occurs  $t_{CVCTX}$  ns from the falling edge of T<sub>4</sub>). The 80186 guarantees a data hold time of  $t_{WHDXmh}$  after the rising edge of

Another point to examine is that in this case we allow the DEN signal to disable the data transceivers by itself. This is because we don't have the tight  $t_{RHAV}$  specification present in the read cycles. Examining the PAL equations in QPDMCS makes this point clearer. DEN is disabled a minimum of

$$t_{\text{CLCHmin}} + t_{\text{CVCTXmin}} - t_{\text{CVCTXmax}}$$

= 44 + 5 - 44

= 5 ns

after  $\overline{WR}$  inactive. This, in combination with the delay to turn off the transceivers, ensures that we meet the hold time of the QPDM in relation to the rising edge of  $\overline{WR}$ . Also, since this last equation uses a minimum  $t_{cvcTx}$  with a maximum  $t_{cvcTx}$ , the hold time will be longer.

### DMA

QPDM DMA requests pose no special problem to the 80186. In fact, since the 80186 built-in DMA controller looks to the QPDM as a flow-through type, the interfacing is quite simple. The 80186 DMA cycles appear as normal processor read or write cycles to the QPDM. These types of read and write cycles have been covered in the preceding paragraphs. The only issue left to be considered is the choice of source or destination synchronized DMA transfers.

When the QPDM requires that large quantities of data be down loaded, destination synchronized transfers must be issued. In destination synchronized DMA transfers, the destination of the DMA data requests the DMA transfer. In this type of transfer, the QPDM is written to during the deposit cycle of the DMA transfer. The only parameter requiring special concern is the DMA request signal inactive time. To prevent unwanted DMA transfer cycles, the DMA requesting device must drop its DMA request at least two clock cycles before the end of the deposit cycle, regardless of the number of wait states inserted into the bus cycle. With a 10 MHz processor clock, the value for DRQ inactive from the start of  $T_2$ (assuming no wait states) is

$$t_{\text{CLCL}} - t_{\text{INVCLmin}} = 100 - 20$$

$$= 80 \text{ ns.}$$

Examining the QPDM specifications, DREQ and FREQ become inactive 50 ns maximum after WR to the QPDM. We have seen previously that the WR goes inactive 56 ns maximum after the falling edge of  $T_2$ . This is a total of 56 + 50 = 106 ns maximum after the falling edge of  $T_2$ , which means that in order to avoid unwanted DMA cycles, we must insert a single wait state into the cycle. The wait state provides an additional 100 ns so that the DRQ inactive time becomes 100 + 80 = 180 ns. Since DREQ or FREQ goes inactive a maximum of 106 ns, the 180 ns DRQ inactive time is more than adequate, and a single wait state is all that is required. No extra circuitry is required to insert this wait state, as we shall cover more fully in a later section.

When the QPDM has data to be transferred out via DMA, the DMA can be programmed to source synchronized mode. In a source-synchronized DMA transfer, the QPDM requests DMA transfer, and the QPDM is read during the fetch cycle of the DMA transfer. Please note that the source or destination synchronized transfer modes are selected by programming bits in the peripheral control register block internal to the 80186. This allows the user to change the mode of the DMA controller via software or on the fly. This means that we can edit the appropriate transfer mode for the QPDM depending on the transfer direction required. To ensure that DMA transfers do not occur when it is not desired, the DRQ signal must be driven inactive before the falling edge of  $T_1$  in the deposit cycle. This does not pose a problem because the QPDM will de-activate DREQ or FREQ 50 ns maximum after  $\overline{RD}$  to the QPDM. This occurs

after the falling edge of  $T_2$ , well before the falling edge of T, in the deposit cycle.

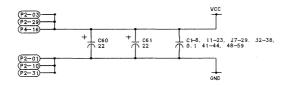

There are three other considerations regarding DMA in general. First, the DREQ and FREQ DMA request pins are open-drain and must be pulled up to  $V_{\infty}$  with resistors. Second,  $\overrightarrow{ACKD}$  is not used in this design and must also be pulled up. Third, the 20-bit source and destination pointers allow access to the complete 1M byte address space of the 80186, but when addressing I/O space, the upper four bits of the DMA pointer registers should be programmed to be 0. Otherwise, the programmed value (greater than 64K in I/O space) will be driven onto the address bus (an area of I/O space not seen by the processor). This could cause chip selection problems in any external logic that the user may wish to add to the design.

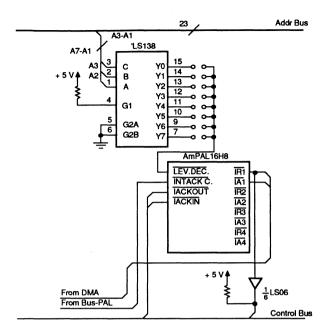

### Interrupts

The 80186 contains an integrated interrupt controller. Four external interrupt pins are available for use. If no more than four external interrupt sources are required, no external interrupt controller is needed. When using the internal interrupt controller, the interrupt types are fixed and cannot be changed. In response to an interrupt, the processor will jump to the vector address associated with the interrupt type. The addresses of the interrupt routines are stored in the interrupt vector table in low memory. These addresses are user supplied and controlled. On the 80186, the interrupt vector address is the interrupt type (or number) multiplied by four. This speeds up the interrupt response greatly, because no external bus cycles are required to fetch the interrupt types. Consult the 80186 data sheet for the vector types associated with the four external interrupt pins. The user can connect the QPDM INT pin to any of the four external INT pins of the 80186 according to the design requirements; INT, was chosen arbitrarily in this design. Please note that the execution of writes to the Interrupt Acknowledge register of the QPDM is used to clear interrupt requests. These steps should be an integral part of all QPDM interrupt service routines. A "1" must be programmed in the word for each interrupt that is to be cleared. A "0" bit has no effect. When all enabled interrupt requests have been acknowledged and cleared, the INT signal goes inactive. Consult the QPDM Technical Manual for further details.

# Miscellaneous

The peripheral chip select lines  $\overline{PCS}_5$  and  $\overline{PCS}_6$  have been programmed to provide latched address lines A<sub>1</sub> and A<sub>2</sub>. This is accomplished by programming the PACS and MPCS registers in the peripheral control block. These two latched address pins are connected to pins A<sub>0</sub> and A<sub>1</sub> of the QPDM and are used to access the internal registers of the QPDM. All the internal QPDM registers will appear at even addresses to the 80186.

In this design,  $\overrightarrow{PCS}_0$  is used to control  $\overrightarrow{CS}$  of the QPDM. Each  $\overrightarrow{PSC}_x$  line is active for one of seven contiguous 128 byte areas in memory space or I/O space above a programmed base address. Consult the PCS Address Ranges Table in the 80186 data sheet for the details regarding address partitioning. As stated earlier, the peripheral chip selects are controlled by two registers in the internal-peripheral control block of the 80186. These registers allow the base address of the peripherals to be set and allow the user to determine whether the addresses will be in memory space or I/O space. Both registers must be programmed by the user before the chip selects become active.

The 80186 includes a ready generation unit. This unit generates an integral ready signal for all accesses to memory or I/O addresses to which the internal chip select circuitry responds. For each chip select, 0-3 wait states may be inserted by the internal unit. Also, the ready generation circuits can be programmed to ignore the state of the external ready pins. In this case, only the internal ready state will be used by the processor. The ready generation circuit can also be programmed to respond to the external ready signal. This means that the ready circuitry will perform a logical AND function of the external and internal ready states and a ready will be provided only after both are true. In this QPDM design, the user may program the R<sub>0</sub>-R<sub>2</sub> bits in the PACS register for one wait state with no external ready required. Bits R<sub>n</sub>-R, of the MPCS register control the ready generation for PCS<sub>4-6</sub>. Bits R<sub>0</sub>-R<sub>2</sub> of the PACS register specify the ready mode for  $\overline{PCS}_{0.3}^{0}$ . Bit 7 of the MPCS register is used to select whether the peripheral chip select lines are mapped into memory or I/O space. After reset, the contents of both the MPCS and PACS registers are undefined: however, none of the PCS lines will be active until both the MPCS and PACS registers are accessed. Also on reset, only UCS (upper chip select) is active. It is programmed by reset to be active for the top 1K memory block, to insert 3 wait states to all memory fetches, and to factor external ready for every memory

access. Therefore, some kind of circuit must be included to generate an external ready until the ready generation logic is reprogrammed not to factor in external ready.

In this design, the lower 16 address lines are latched. This is done because the integrated chip selects perform the selection between the various memories and peripherals. Therefore, the upper four address bits can be ignored. The usage of these upper four bits will probably vary from design to design.

# 2.1.2 Multiple QPDM Design

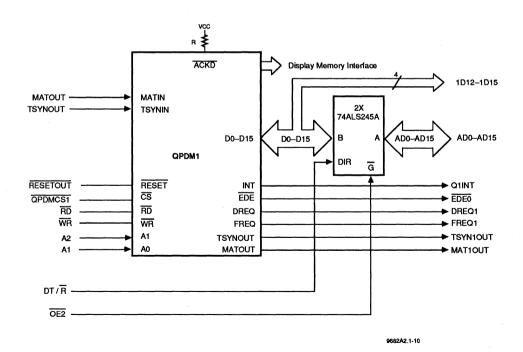

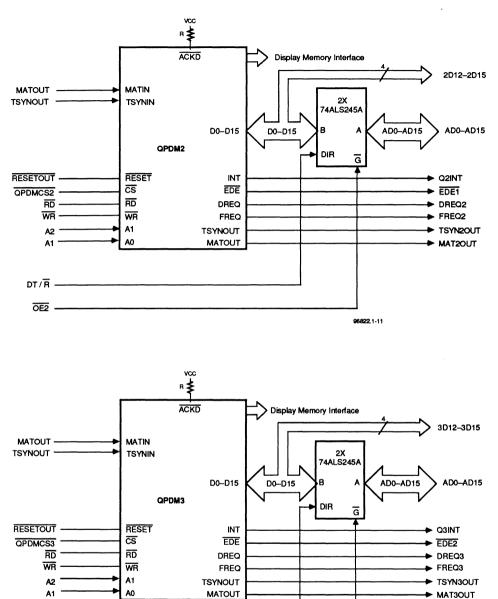

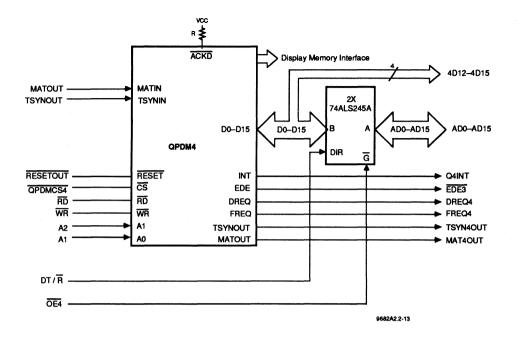

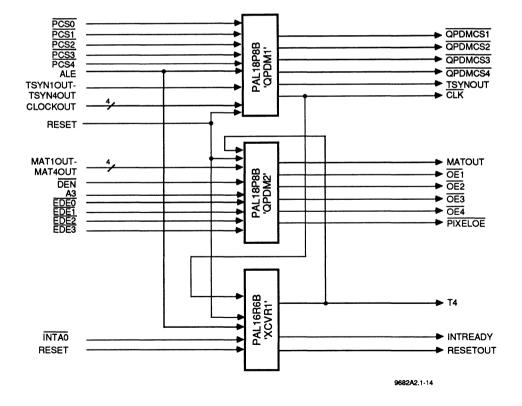

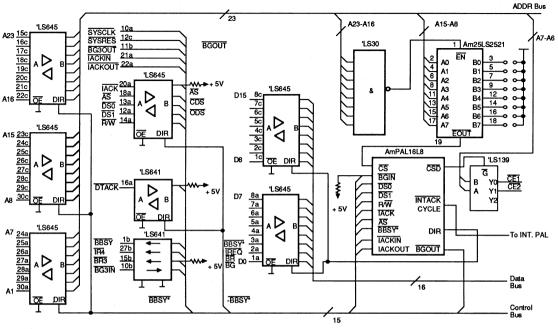

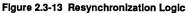

In this section, an extension of the previous design is discussed. A 16 bit plane, four QPDM system design is illustrated (Figure 2.1-5). First, a discussion on multiple QPDM operation is in order.

# Multiple QPDM Design Considerations

# Initialization and Broadcast

Since each QPDM handles up to four bit planes, a 16 plane system will require four QPDM devices. In general, all QPDMs are given each instruction simultaneously with identical parameters, so that the instruction can update each plane. In some cases, however, a means to differentiate between QPDMs and some planes within a single QPDM is necessary. To facilitate individual QPDM plane operation, each QPDM is assigned a QPDM number. This number is loaded into each QPDM using the "Set QPDM Position" instruction. Each QPDM must be assigned a unique number, via four separate set QPDM position instructions; one instruction is executed per QPDM. This means that it is necessary to provide chip select ( $\overline{CS}$ ) decoding for each individual QPDM and for all QPDMs as a group. In this design we would need five separate CS signals. The "Quad QPDM Chip Selects" shows the relationship between PCS, and the QPDM table chip selects in this example.

| Quad QPDM Chip Selects    |                       |  |  |

|---------------------------|-----------------------|--|--|

| Peripheral<br>Chip Select | QPDM(s)<br>t Selected |  |  |

| PCS                       | QPDM1                 |  |  |

| PCS                       | QPDM2                 |  |  |

| PCS,                      | QPDM3                 |  |  |

| PCS                       | QPDM4                 |  |  |

| PCS4                      | ALL (QPDM1-QPDM4)     |  |  |

CHAPTER 2 System Bus Interface

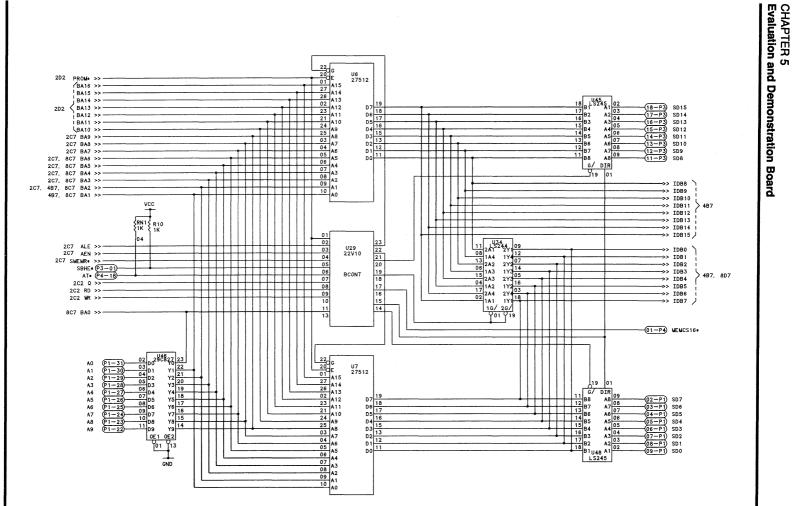

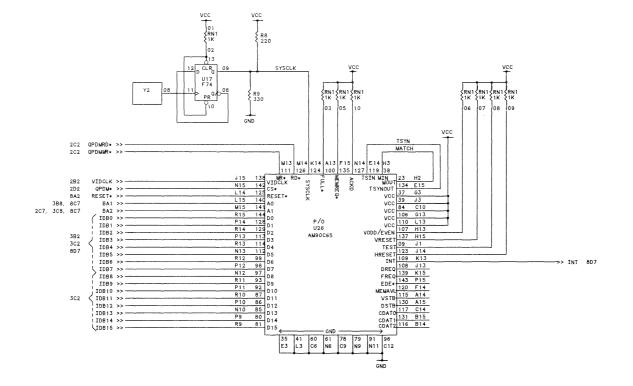

Figure 2.1-5 Quad QPDM Schematic

9682A2.1-12

### Figure 2.1-5 Quad QPDM Schematic (continued)

QPDM instructions are sent to each QPDM simultaneously. This is called broadcasting. Broadcasting of instructions is accomplished by chip selecting all QPDMs and writing to Port 0. Further details can be found in the QPDM Technical Manual. The hardware requirements for QPDM initialization and for broadcasting are a mechanism for individual chip selection as well as a global chip select.

# DMA Requests

DMA with a multiple QPDM system is fairly straightforward. Both FREQ and DREQ are open-drain outputs. Each QPDM in a system will release its FREQ or DREQ when it is ready so that a DMA request will be presented to the 80186. The FREQ controls DMA to the Instruction FIFO and DREQ controls DMA to and from the Data FIFO of the QPDM. In a multiple QPDM system, all the FREQ lines of the QPDMs are tied together through a pull-up resistor to DRQ, of the 80186. Similarly, all the DREQ lines are tied together through a pull-up resistor to the DRQ0 input of the CPU. In the case of a data transfer (DREQ), as long as any QPDM is not ready to continue with the transfer, the node will be pulled LOW. When the last QPDM becomes ready, the node goes HIGH and a DMA request will be seen at the 80186. The same is true of the instruction FIFO and the FREQ pins. As long as any QPDM is not ready to request more instructions, the node goes LOW. When the last QPDM becomes ready. the node will be pulled HIGH through the pull-up resistor and an instruction DMA request will be seen at the DRQ. pin of the CPU.

To summarize, one can see that all DMA to and from multiple QPDMs are synchronized by the open-drain AND connection. The open-drain AND ensures that all DREQ and FREQ requests of the QPDMs are active before the DMA request is seen at the processor. Above and beyond the previous discussion, the DMA cycles are the same as outlines in the single QPDM design.

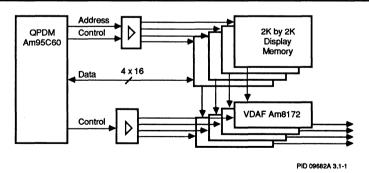

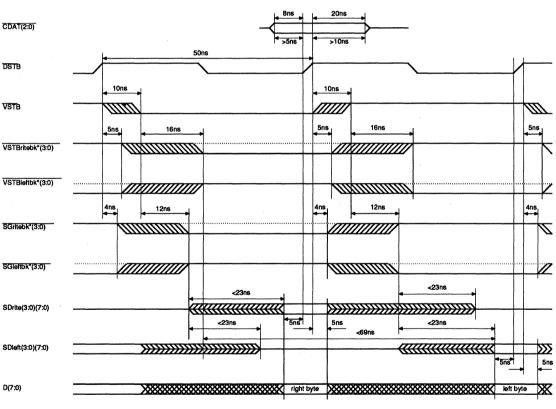

# Block Transfer to and from Display Memory

In the multiple QPDM design, provisions have been made for display memory accesses by plane (horizontal on a selected bit plane) and by pixel (reading all bits in all planes per pixel). In a by plane Block I/O instruction, only one plane in a single QPDM is selected for a read or write. In the read case, a provision must be made to keep all QPDMs in synchronization. To do this, the processor fakes a read operation on all the QPDMs. The inactive QPDMs (do not contain the bit plane accessed) leave EDE not active, so as not to cause contention with the data of the only active QPDM. The active QPDM, the one with a plane active for the instruction, places data on the bus as in a normal read cycle. In large systems, however,

we need external data transceivers. This is where the EDE (External Driver Enable) pin comes in handy. For the inactive QPDMs, the EDE pin does not go active to their corresponding bus transceivers. Only the active QPDM drives its EDE signal valid to its bus transceiver to allow its data onto the bus. Therefore, by adding a little more intelligence to the QPDM interface, synchronization is achieved and maintained even when only one bit plane in a single QPDM is to be accessed.

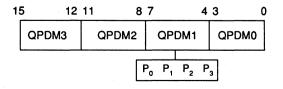

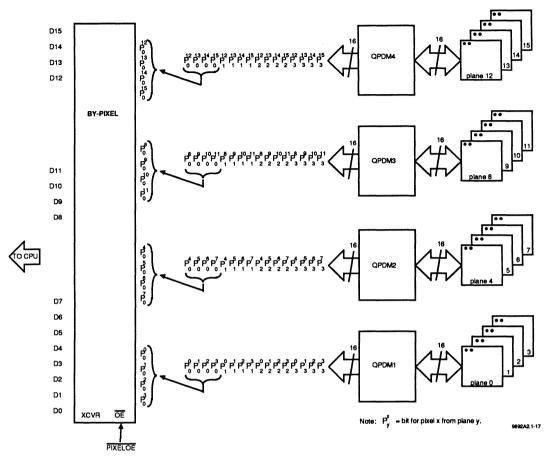

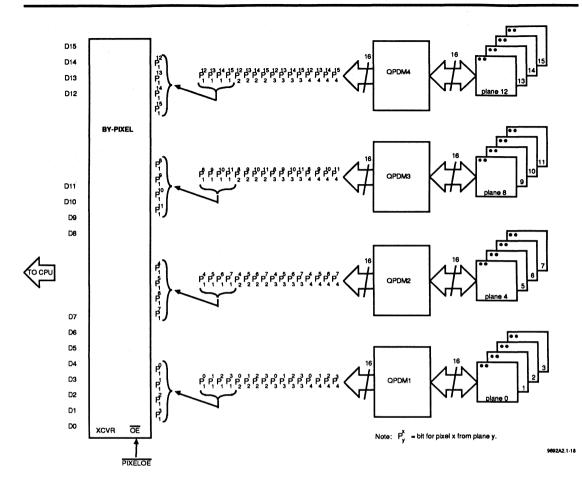

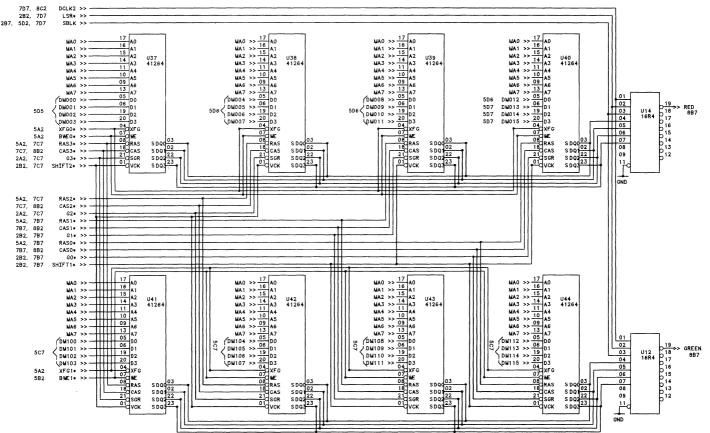

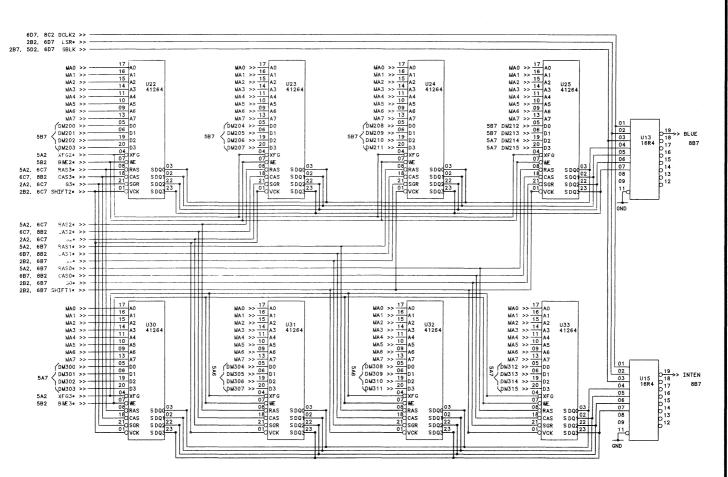

In a by pixel Block I/O, the user wishes to access all bits in all planes per pixel. This implies that all QPDMs contribute the bits of the planes that they control for that particular pixel. Synchronization, therefore, is not a problem, as all QPDMs will be active. In a multiple QPDM system, an extra set of transceivers must be provided to route the pixels from each QPDM to a single 16-bit data bus. These are shown on Sheet 8 of the Quad QPDM Schematic. For example, in this design each QPDM contributes four bits for each individual pixel. A mechanism has been provided in the QPDM to program the number of shifts necessary for the proper assembly of pixels. This is done by specifying the correct number (1, 2 or 4) dependent on the number of QPDMs in the system in the BOS field of the Input or Output Block instructions. To see how this works examine Figure 2.1-6, "By Pixel Read". On the first pixel's read cycle, each QPDM places 16 bits on its respective data bus, only four of which will be used. A 16-bit transceiver concatenates four bits from each QPDM to form a 16-bit data value. Following each cycle, each QPDM shifts its data four bits to the left. In this way the next pixel's four bits of data are positioned correctly in the data bus to be assembled into the 16-bit value at the transceiver. This process continues until all 16-bit values for the selected number of pixels have been read. From a hardware standpoint, all that is required is an extra transceiver and extra decoding logic to selectively enable or disable the set of transceivers depending upon the type of access (by plane or by pixel).

From a software point of view it is best if planes appear in consistent bit positions. What this means in hardware terms is that some consideration must be given to how the data bits of the "by pixel" transceiver are connected. The relationship between data bits and planes is fixed by the organization of operands in the Set Activity Bits instruction. Each of four QPDMs extract four bits as shown below:

Figure 2.1-6a By Pixel (Output Block) Read - First Cycle

There is no reasonable way to change this relationship; everything else will have to match. To make I/O by-pixel conform, one must wire the by-pixel data transceiver as shown in Figure 2.1-6, "By Pixel Read". Also see Chapter 13 of the QPDM Technical Manual, "The Relationship Between Data Bits and Pixels." It should be noted here that only pixels that are 16 planes or less can be processed in one pass; deeper bit planes would require multiple passes.

# Other Synchronization Concerns

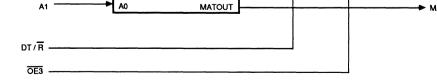

The synchronization of getting new words out of the instruction FIFO and reading and writing the data exchange FIFOs use the MAT<sub>N</sub> and MAT<sub>OUT</sub> pins. The MAT<sub>OUT</sub> pins of all the QPDMs are ANDed together. This composite signal goes HIGH only when all the QPDMs are ready to begin the next instruction. All QPDMs

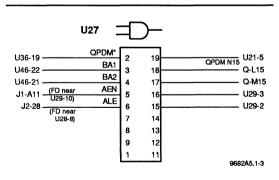

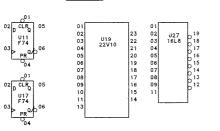

sample the composite  $MAT_{OUT}$  signal at the  $MAT_{IN}$  input. From an interface standpoint, all that is required is to AND the  $MAT_{OUT}$  pins and connect the composite signal to the  $MAT_{IN}$  pins. The AND is done in PAL device QPDM2.

In a similar fashion, the TSYN<sub>OUT</sub> and TSYN<sub>IN</sub> pin combination is used to synchronize the bit map display memory bus activities. The same hardware considerations discussed in the preceding paragraphs apply. The AND is done in PAL device QPDM1. Please note that even in a single QPDM system MAT<sub>IN</sub> and MAT<sub>OUT</sub> must be tied together, as are TSYN<sub>QUT</sub> and TSYN<sub>IN</sub>.

# 2.1.3 Hardware Overview

### **Read Cycles**

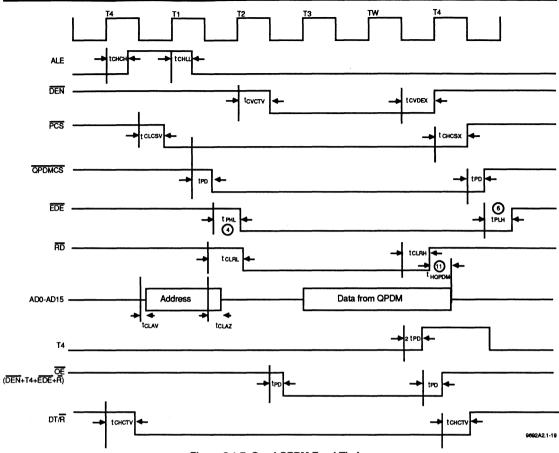

The multiple QPDM read is shown in Figure 2.1-7, "Quad QPDM Read Timing". The situation is sightly more

Figure 2.1-6b By Pixel (Output Block) Read - Second Cycle

complex than in the single QPDM case. We must modify the transceiver PAL device logic to factor in the  $\overline{\text{EDE}}$ signal discussed previously. The  $\overline{\text{EDE}}$  signal from the selected QPDM is guaranteed active a maximum of 50 ns after  $\overline{\text{CS}}$  to the selected QPDM goes active. This  $\overline{\text{EDE}}$ signal can be active a maximum of

$$t_{CHLLMAX} + t_{PDMAX} + t_{PHLMAX}$$

= 70 + 15 + 50

= 135 ns

from the rising edge of T<sub>1</sub>. DEN can go active a minimum of 5 ns from the rising edge of T<sub>2</sub>. This means that factoring in the EDE signal into the PAL equations can delay  $\overline{OE}$  to the transceiver a maximum of 30 ns. Note that again we are mixing minimum and maximum parameters of the 80186. In practice, the delay will be less than the calculated 30 ns. Remember from the single

QPDM design that we had 185 ns transceiver enable time prior to valid data required at the CPU. With the factoring in of the QPDM EDE signal, we have reduced this figure to a minimum of 155 ns. The PAL device circuit uses 15 ns maximum of this time, so that 140 ns still remains to enable the transceivers. Since the QPDM places data on its bus a maximum of 80 ns from the falling edge of read, we can see that the factoring in of the EDE signal really does not change things all that much. We still use the T<sub>4</sub> signal to disable the transceivers and meet the t<sub>RHAN</sub> specification of 60 ns. Examination of the PAL equations, QPDM1 and QPDM2, will clarify these points.

# Write Cycles

The write cycles remain the same as in the single QPDM design. Once the QPDM(s) have been chip selected, the write cycles are identical to the single QPDM case.

Figure 2.1-7 Quad QPDM Read Timing

| Quad QPDM Read Cycle<br>Parameter List |                   |          |  |  |

|----------------------------------------|-------------------|----------|--|--|

|                                        | MIN (ns)          | MAX (ns) |  |  |

| t <sub>снын</sub> (80186-1)            |                   | 30       |  |  |

| t <sub>сни</sub> (80186-1)             |                   | 30       |  |  |

| t <sub>сvстv</sub> (80186-1)           | 5                 | 56       |  |  |

| t <sub>cvpex</sub> (80186-1)           | 10                | 56       |  |  |

| t <sub>cLCSV</sub> (80186-1)           |                   | 45       |  |  |

| t <sub>cHCSX</sub> (80186-1)           | 5                 | 32       |  |  |

| t <sub>вы овом</sub> (95C60-20)        |                   | 50       |  |  |

| t <sub>PLHOPDM</sub> (95С60-20)        |                   | 65       |  |  |

| t <sub>cLRL</sub> (80186-1)            | 10                | 56       |  |  |

| t <sub>сцян</sub> (80186-1)            | 10                | 44       |  |  |

| t <sub>cLAV</sub> (80186-1)            | 5                 | 50       |  |  |

| t <sub>cLAZ</sub> (80186-1)            | t <sub>clax</sub> | 30       |  |  |

| t <sub>роором</sub> (95С60-20)         |                   | 80       |  |  |

| t <sub>норрм</sub> (95С60-20)          | 10                |          |  |  |

| t <sub>PD</sub> (B-Speed PAL)          |                   | 15       |  |  |

| t <sub>снстv</sub> (80186-1)           | 10                | 44       |  |  |

| t <sub>снстv</sub> (80186-1)           | 10                | 44       |  |  |

### Chip Select Logic

This design uses  $\overline{PCS}_{0.4}$  to enable one or all of the chip selects of the individual QPDMs. Note that in this design the address pins A<sub>1</sub> and A<sub>2</sub> are not latched via  $\overline{PCS}_5$  and  $\overline{PCS}_6$ . This means that  $\overline{PCS}_5$  and  $\overline{PCS}_6$  are free to select other peripheral devices. The address information required by the QPDM is now latched in the Am74LS373 latches and connected directly to the A<sub>0</sub> and A<sub>1</sub> inputs. Note again that the A<sub>2</sub> and A<sub>1</sub> CPU address pins have been connected to the A<sub>0</sub> and A<sub>1</sub> pins of the QPDM such that the internal registers appear at even address multiples.

The  $\overline{PCS}_x$  pins still need to be qualified by ALE to ensure that valid address data is present at the A<sub>0</sub> and A<sub>1</sub> pins of the QPDMs before a chip select goes active. ALE is inactive 30 ns maximum from the rising edge of T<sub>1</sub>, which means that the qualified QPDM chip selects are active a t<sub>en</sub> maximum of 15 ns later. This ensures valid addresses at the QPDM, as addresses are guaranteed valid by the CPU at least 20 ns before the falling edge of ALE.

To implement a global chip select to the QPDMs,  $\overrightarrow{PCS}_4$  was chosen. Whenever the user's code wishes to broadcast to all QPDMs, the I/O or memory addresses used will correspond to the fifth 128-byte area above the programmed base address (PBA) in the PACS register of the 80186. The logic to generate both single and global chip selects is easily implemented in a PAL device. Examine the QPDM1 PAL device listing. Whenever  $\overrightarrow{PCS}_4$  and  $\overrightarrow{ALE}$  are active, all the chip selects from the QPDMs will be active.

When the user wishes to access only a single QPDM, the address block assigned to the chip select for that particular QPDM is used.

# Block I/O "By Pixel" Control

In this design, two extra transceivers are included to allow the user to read all 16-bit planes controlled by all four QPDMs on a pixel-by-pixel basis. This means that some differentiation is necessary between the regular I/O transceiver and the "By Pixel" transceivers. This is accomplished by using address line  $A_3$  to enable the extra transceivers. To read data on a "By Pixel" basis using a block I/O QPDM instruction, the user addresses the global bank of addresses ( $PCS_4$ ), with address line  $A_3$  active HIGH. This chip select enables all the QPDMs so that each can contribute up to four bits to the 16-bit word to be read by the CPU. The assembly of these 4-bit nibbles occurs at the "By Pixel" data transceivers. These two transceivers are only enabled when address line  $A_3$  is active.

The same holds true for CPU writes on a "By Pixel" basis. In this case the 16 bits written by the CPU are disassembled by the "By Pixel" transceivers and four bits are presented to each QPDM to be inserted into the bit-map for the selected pixel.

Individual QPDM accesses with address line  $A_3$  LOW only enable the transceivers associated with the selected QPDM. Global QPDM accesses with address line  $A_3$ LOW enable only the eight transceivers associated with regular QPDM accesses. The "By Pixel" transceivers are not enabled. Therefore, with a little extra decoding logic, the user is given the capability to examine all the bit planes of one pixel in a single CPU access cycle.

One further point must be made clear. The Input and Output Block instructions of the QPDM are provided to allow the CPU to access directly into display memory. As discussed earlier, the CPU may access the display memory "By Plane" or "By Pixel". This brings up the point of activity bits. Each QPDM has four activity bits, one for each plane it controls. With the Set Activity Bits instruction the user can set or clear these bits in each QPDM in the design. If the activity bit for a plane is set to "1", the plane will operate normally. Write operations will conditionally write into the plane. If the activity bit for a plane is set to a "0", the plane will not be written to. The activity bits of a QPDM also affect the generation of the EDE (external driver enable) signal. During accesses to the Block I/O FIFO of the QPDM, the following equation determines whether or not an EDE signal is generated:

$$\overline{\mathsf{EDE}} = \overline{\mathsf{CS}} \cdot \mathsf{A}_1 \cdot \mathsf{A}_0 \cdot (\mathsf{AB}_0 + \mathsf{AB}_1 + \mathsf{AB}_2 + \mathsf{AB}_3)$$

where AB, - AB, are the activity bits for each plane the QPDM controls. What are the ramifications of the activity bits? During an Input Block instruction, data from the CPU will only be written to the planes whose activity bits are set. During an Output Block instruction, where the QPDM outputs display map data to the CPU, two cases arise. In the case of a by-plane read of display data, only one activity bit in one QPDM may be set. To repeat, in a system with multiple QPDMS, when executing a byplane Output Block instruction, make sure that only one QPDM has one activity bit set. If multiple QPDMs have their activity bits set, then their EDE pins will go active, enabling their data transceivers and bus contention will result. In the case of an output block by pixel, the software must be consistent to interpret the data bits from all the QPDMS. For a by pixel output, "1"s will be returned for all inactive planes. Therefore, the software must be consistent and keep track of all active planes so that it can interpret the data for the individual pixels.

# DMA

The DMA issues remain the same as in the single QPDM design.

# Interrupts

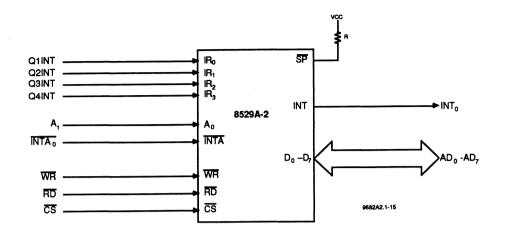

In this design an external interrupt controller is added. In the case of an external interrupt controller, several of the internal 80186 peripheral control registers must be reprogrammed. The internal interrupt controller must be in master mode. The cascade bit of the INT<sub>o</sub> control register must also be set. In this mode, whenever the interrupt presented to the INT<sub>o</sub> is acknowledged, the integrated interrupt controller will not provide the interrupt type for the interrupt. Instead, two interrupt-acknowledge bus cycles will be run, with the INT<sub>2</sub> pin of the 80186 now providing the interrupt-acknowledge pulses for the INT<sub>o</sub> requests. The 80186 will read the interrupt type from the lower eight bits of the address/data bus on the second interrupt-acknowledge cycle. In this design the INT, and INT, pins have been reconfigured to hook up to the external 8259A interrupt controller. The INT, and INT, lines are still used as direct interrupt inputs, identical to the single QPDM design. The 8259A can handle up to eight external interrupt requests. These eight, combined with the two direct input interrupt pins provide a total of 10 external interrupt requests. Also note that an interruptready signal must be returned to the CPU to prevent wait state generation during the interrupt-acknowledge cycles. This is provided via the PAL devices. We have also used PCS<sub>5</sub> to provide the chip-select logic to the external interrupt controller. The four INT pins of the QPDMs have been connected to the external 8259A. Software must be written to initialize the external 8259A and to set up the actual external interrupt vector numbers. More details can be found in the 8259A data sheet.

### **Miscellaneous**

The comments on peripheral chip selects in the single QPDM case also apply in this case. Remember to

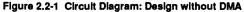

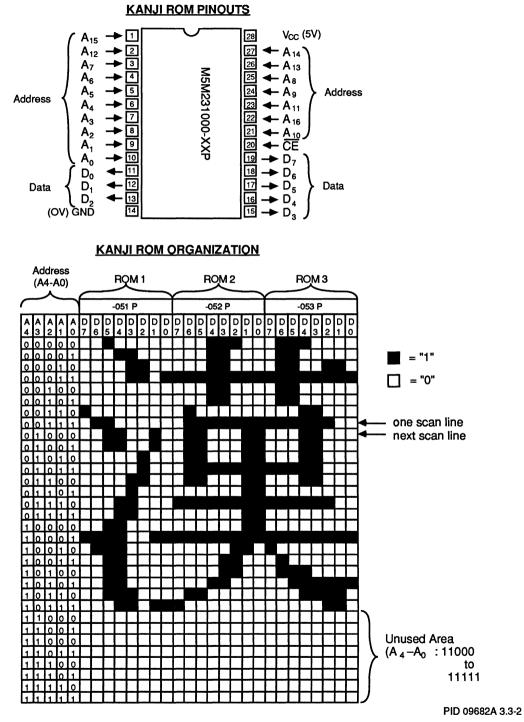

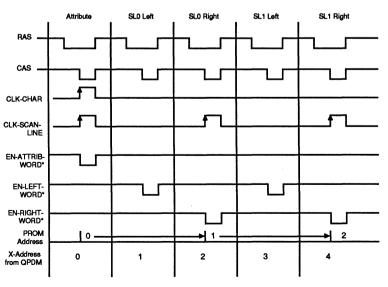

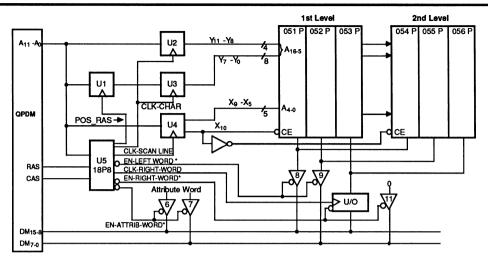

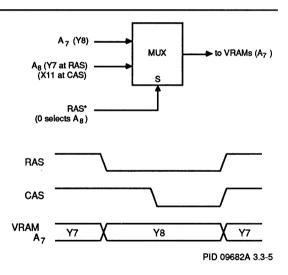

program the PACS and MPC<sub>s</sub> registers for the correct (one) number of wait states with no external ready. Consult the 80186 data sheet for bit patterns. The base address for the  $\overline{PCS}_x$  pins are programmed into the PACS register and each  $\overline{PCS}_x$  pin is assigned a 128 byte block relative to this base address. The  $\overline{PCS}_x$  pins respond only to the addresses in their individually assigned blocks. This means that each QPDM in the multiple QPDM design is assigned a 128-byte block of addresses. The global chip select takes up another 128-byte block.