# **B120 Data Sheet**

(Bridge120)

## **DAT0018C**

(Date: 10/28/99)

Genesis Microchip Inc. believes the information contained in this document to be accurate. However, this information is subject to change without any notice. Genesis Microchip Inc. does not assume any responsibility for its use, nor for infringement of patents or any other rights of third parties. This document implies no license under patents or copyrights. Trademarks in this document belong to their respective companies.

#### **Copyright Notice**

This manual is copyrighted. All rights are reserved. This document may not, in whole or part, be copied, photocopied, reproduced, translated, or reduced to any electronic medium or machine-readable form without prior written consent from Genesis Microchip Inc.

#### Genesis Microchip Inc.

165 Commerce Valley Dr. West, Thornhill, ON Canada L3T 7V8 Tel: (905) 889-5400 Fax: (905) 889-0035

1871 Landings Drive, Mountain View, CA, USA 94043 Tel: (650) 428-4277 Fax (650) 428-4288

www.genesis-microchip.com / info@genesis-microchip.on.ca

**Revision History:**

- March 1998 (First publication)

- August 1998 (General Update)

- October 1998 (Corrections)

- June 1999 (New Format)

- July 1999 (Added Related Documents)

- October 1999 (Incorporated Modified Electronical Characteristics for revision B and C)

**Related Documents**

- Bridge API Reference Manual Ver.1.00

- DAT-1018

- DSR-0018

- SED-0701

- SED-0700

- SED-0737

### B120 Flat Panel Monitor Controller

## **Table of Contents**

|    | Cha  | pter     |                                          | Page |

|----|------|----------|------------------------------------------|------|

| 1. | Ger  | neral E  | Description.                             | 4    |

|    | 1.1  | Sum      | mary                                     | 4    |

|    | 1.1  | Feat     | ures                                     | 4    |

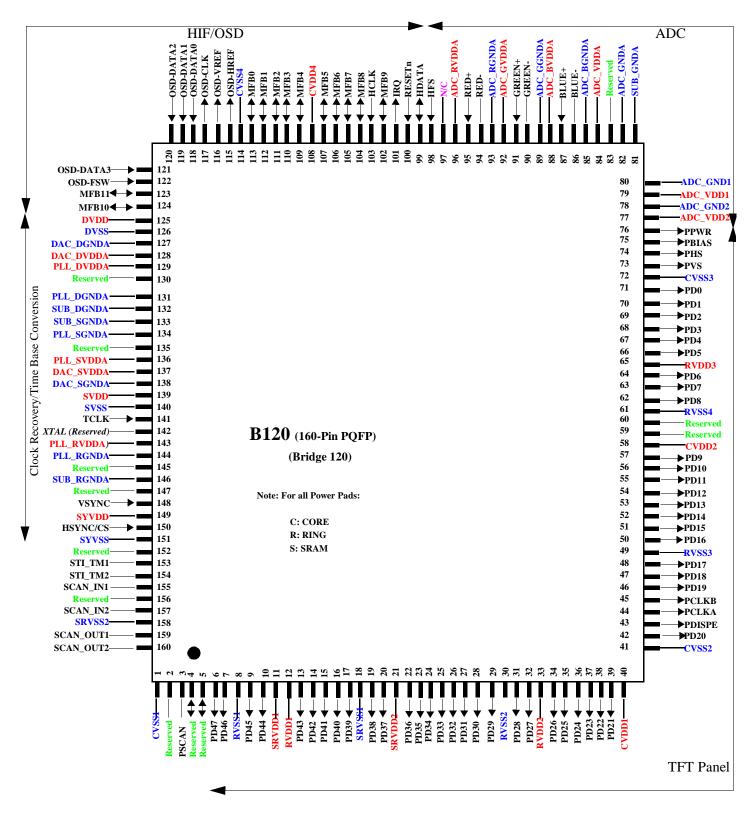

|    | 1.3  | Pin I    | Diagram                                  | 5    |

|    | 1.4  | Pin I    | Description (160-pin PQFP)               | 6    |

|    | 1.5  | Syste    | em-level Block Diagrams                  | 11   |

| 2. | Arc  | hitectu  | ural Description                         | 12   |

|    | 2.1  | Over     | all Architecture                         | 12   |

|    | 2.2  | CRT      | Interface                                | 16   |

|    |      | 2.2.1    | Pin Connection                           | 16   |

|    |      | 2.2.2    | Analog-to-Digital Converters             | 17   |

|    |      | 2.2.3    | Sync. Signal Support                     | 18   |

|    |      | 2.2.4    | Display Mode Support                     | 19   |

|    | 2.3  | Pane     | l Interface                              | 21   |

|    |      | 2.3.1    | Pin Connection                           | 21   |

|    |      | 2.3.2    | TFT Panel Interface Timing Specification | 23   |

|    |      | 2.3.3    | Power Manager                            | 27   |

|    |      | 2.3.4    | Panel Interface Drive Strength           | 28   |

|    | 2.4  | Host     | Interface                                | 29   |

|    |      | 2.4.1    | Pin Connection                           | 29   |

|    |      | 2.4.2    | Serial Communication Protocol            | 30   |

|    |      | 2.4.3    | Multi-Function Bus (MFB)                 | 31   |

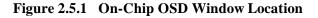

|    | 2.5  | OSD      | (On-Screen Display) Control              | 32   |

|    |      | 2.5.1    | On-Chip OSD                              | 32   |

|    |      | 2.5.2    | Built-in OSD Font                        | 34   |

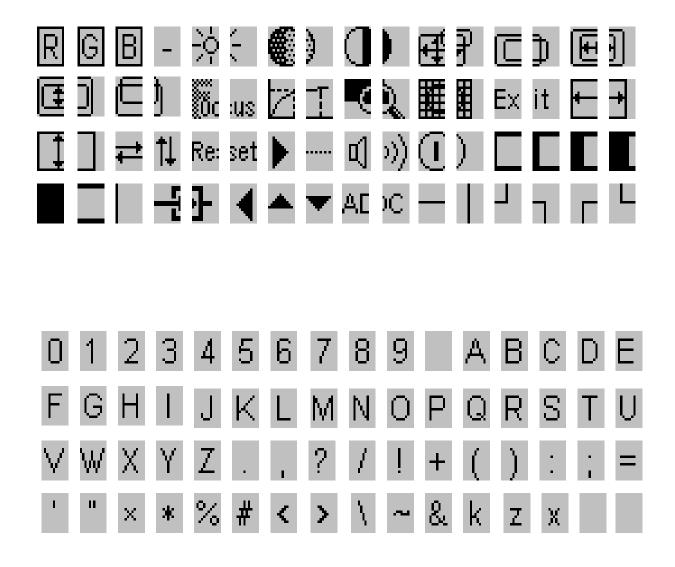

|    |      | 2.5.3    | External OSD Support                     | 35   |

| 3. | Eleo | ctrical  | Characteristics                          | 38   |

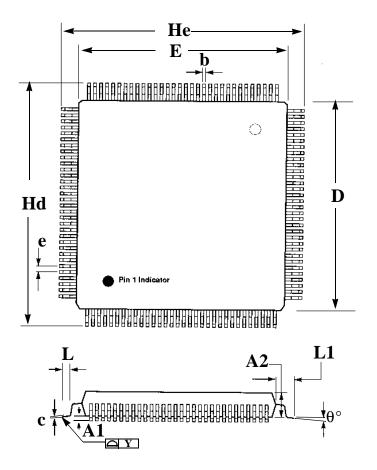

| 4. | Pac  | kage I   | Dimension                                | 39   |

| Ap | pend | lix: Lis | st of Tables and Figures                 | 40   |

## **1. General Description.**

### 1.1 Summary

Liquid Crystal Displays have advanced to the point of being comparable with CRT monitors in color capabilities, size, and resolution. In many applications, remote flat panel displays are more desirable than CRTs. However supporting the multi-sync feature of the CRT monitor on the fixed-resolution flat panel display imposes a technical challenge. The B120 chip developed by Paradise Electronics, Inc., a subsidiary of Genesis Microchip Inc., provides a flat-panel-monitor solution that is compatible with today's CRT standards.

#### **1.1 Features**

#### Single Chip Solution without External Frame Buffer

The B120 is a highly integrated single chip interface controller for flat panel monitors. Featuring three integrated 8 bit ADC's (analog-to-digital converters), Clock Generator, Image Processor, and Panel Controller, the chip allows monitor vendors to deliver multi-sync. flat-panelmonitors supporting up to 16.8 million colors and 1280 x 1024 resolutions. Besides the high level of integration, B120 requires no external frame buffer and therefore provides a simplified and cost-effective solution.

#### **CRT** interface

- Converts analog RGB signals up to 16.8 million colors

- Sync format support for IBM compatible PCs, Apple Macintosh, NEC PC98, and various Unix workstations. Hsync/Vsync and Csync supported.

- Supports DPMS for monitor power management.

#### Works with any Graphics Controller

- No special BIOS or software driver required.

#### **Compact 160 pin PQFP**

Standard, compact QFP package, along with the high level of integration, saves PCB space.

#### **TFT Panel Support**

- Supports a wide variety of active matrix TFT panels either one or two pixel(s) per clock mode up to SXGA panel resolution.

- Supports all panel interface types (Sync. only, Display Enable only, and Composite) at 4/6/8 bits per pixel up to 16.8 million colors.

- Spatial dithering increases number of colors.

- Programmable slew rate minimizes EMI.

#### Horizontal and Vertical up-scale engine

- Incoming CRT display resolutions, regardless of their aspect ratios, are expanded to fill the entire flat panel. This full-screen display capability significantly increases image size on the panel and maintains the CRT-like "look and feel."

#### Independent RGB Offset/Gain and Gamma RAM

- Allows end users to adjust contrast, brightness, color balance, black/white level, and gamma correction.

#### **Host Microcontroller Interface**

- Allows the host microcontroller interrupt-driven control of flat panel monitor through robust API (applications programming interface) calls.

#### **OSD** Support

- Supports an external OSD controller chip allowing the monitor vendor to maintain a familiar user interface.

- Built-in OSD (On Screen Display) controller with integrated 128-character font ROM.

#### Built-in High Speed Clock Recovery Circuit

- Generates clocks for the on-chip ADC and TFT pixel clock.

#### Advanced Test and Reliability Features

- Full Scan Logic for extremely high fault coverage

- Automated PCB assembly testing.

## 1.3 Pin Diagram

## 1.4 Pin Description (160-pin PQFP)

| <b>Table 1.4.1</b> | <b>Pin Description</b> | of the B120 |

|--------------------|------------------------|-------------|

| 1 abic 1.4.1       | I III Description      | of the Diao |

| Pin | Name      | In /<br>Out | Drive Current<br>(@10pF) | Description                                                                                                                                                                                                    |

|-----|-----------|-------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 77  | ADC_VDD2  | Out         |                          | Digital power for ADC encoding logic. Must be bypassed with 0.1 uF capacitor to pin 78 (ADC_GND2)                                                                                                              |

| 78  | ADC_GND2  |             |                          | Digital GND for ADC encoding logic. Must be directly connected to the digital system ground plane.                                                                                                             |

| 79  | ADC_VDD1  |             |                          | Digital power for ADC clocking circuit. Must be bypassed with 0.1 uF capacitor to pin 80 (ACD_GND1)                                                                                                            |

| 80  | ADC_GND1  |             |                          | Digital GND for ADC clocking circuit. Must be directly connected to the digital system ground plane.                                                                                                           |

| 81  | SUB_GNDA  |             |                          | Dedicated pin for substrate guard ring that protects the ADC reference system.<br>Must be directly connected to the analog system ground plane.                                                                |

| 82  | ADC_GNDA  |             |                          | Analog ground for ADC analog blocks that are shared by all three channels.<br>Includes bandgap reference, master biasing and full scale adjust. Must be<br>directly connected to analog system ground plane.   |

| 84  | ADC_VDDA  |             |                          | Analog power for ADC analog blocks that are shared by all three channels.<br>Includes bandgap reference, master biasing and full scale adjust. Must be<br>bypassed with 0.1 uF capacitor to pin 82 (ADC_GNDA). |

| 83  | Reserved  |             |                          | For internal testing purpose only. Do not connect.                                                                                                                                                             |

| 85  | ADC_BGNDA |             |                          | Analog ground for the blue channel. Must be directly connected to the analog system ground plane.                                                                                                              |

| 88  | ADC_BVDDA |             |                          | Analog power for the blue channel. Must be bypassed with 0.1 uF capacitor to pin 85 (BGNDA).                                                                                                                   |

| 86  | BLUE-     | In          |                          | Negative analog input for the Blue channel.                                                                                                                                                                    |

| 87  | BLUE+     | In          |                          | Positive analog input for the Blue channel.                                                                                                                                                                    |

| 89  | ADC_GGNDA |             |                          | Analog ground for the green channel . Must be directly connected to the analog system ground plane.                                                                                                            |

| 92  | ADC_GVDDA |             |                          | Analog power for the green channe. Must be bypassed with 0.1 uF capacitor to pin 89 (ADC_GGNDA).                                                                                                               |

| 90  | GREEN-    | In          |                          | Negative analog input for the Green channel.                                                                                                                                                                   |

| 91  | GREEN+    | In          |                          | Positive analog input for the Green channel.                                                                                                                                                                   |

| 93  | ADC_RGNDA |             |                          | Analog ground for the red channel. Must be directly connected to the analog system ground plane.                                                                                                               |

| 96  | ADC_RVDDA |             |                          | Analog power for the red channel. Must be bypassed with 0.1 uF capacitor to pin 93 (ADC_RGNDA).                                                                                                                |

| 94  | RED-      | In          |                          | Negative analog input for the Red channel.                                                                                                                                                                     |

| 95  | RED+      | In          |                          | Positive analog input for the Red channel.                                                                                                                                                                     |

| Host | Host Interface (HIF) / External On-Screen Display |             |                          |                                                                                                |  |  |

|------|---------------------------------------------------|-------------|--------------------------|------------------------------------------------------------------------------------------------|--|--|

| Pin  | Name                                              | In /<br>Out | Drive Current<br>(@10pF) | Description                                                                                    |  |  |

| 98   | HFS                                               | in          |                          | Host Frame Sync. Frames the packet on the serial channel.                                      |  |  |

| 103  | HCLK                                              | in          |                          | Clock signal input for the 3-wire serial communication.                                        |  |  |

| 99   | HDATA                                             | in/out      | 8 mA                     | Data signal for the 3-wire serial communication                                                |  |  |

| 100  | RESETn                                            | in          |                          | Resets the B120 chip to a known state when low.                                                |  |  |

| 101  | IRQ                                               | out         | 4 mA                     | Interrupt request output                                                                       |  |  |

| 115  | OSD-HREF                                          | out         | 4 mA                     | HSYNC output for an external OSD controller chip.                                              |  |  |

| 116  | OSD-VREF                                          | out         | 4 mA                     | VSYNC output for an external OSD controller chip.                                              |  |  |

| 117  | OSD-Clk                                           | out         | 4 mA                     | Clock output for an external OSD controller chip.                                              |  |  |

| 118  | OSD-Data0                                         | in          |                          | Data input 0 from an external OSD controller.                                                  |  |  |

| 119  | OSD-Data1                                         | in          |                          | Data input 1 from an external OSD controller.                                                  |  |  |

| 120  | OSD-Data2                                         | in          |                          | Data input 2 from an external OSD controller.                                                  |  |  |

| 121  | OSD-Data3                                         | in          |                          | Data input 3 from an external OSD controller.                                                  |  |  |

| 122  | OSD-FSW                                           | in          |                          | External OSD window display enable. Displays data from external OSD con-<br>troller when high. |  |  |

| 123  | MFB11                                             | in/out      | 8 mA                     | Multi-Function Bus 11. One of twelve multi-function signals MFB[11:0].                         |  |  |

| 124  | MFB10                                             | in/out      | 8 mA                     | Multi-Function Bus 10. One of twelve multi-function signals MFB[11:0].                         |  |  |

| 102  | MFB9                                              | in/out      | 8 mA                     | Multi-Function Bus 9. One of twelve multi-function signals MFB[11:0].                          |  |  |

| 104  | MFB8                                              | in/out      | 8 mA                     | Multi-Function Bus 8. One of twelve multi-function signals MFB[11:0].                          |  |  |

| 105  | MFB7                                              | in/out      | 8 mA                     | Multi-Function Bus 7. One of twelve multi-function signals MFB[11:0].                          |  |  |

| 106  | MFB6                                              | in/out      | 8 mA                     | Multi-Function Bus 6. One of twelve multi-function signals MFB[11:0].                          |  |  |

| 107  | MFB5                                              | in/out      | 8 mA                     | Multi-Function Bus 5. One of twelve multi-function signals MFB[11:0].                          |  |  |

| 109  | MFB4                                              | in/out      | 8 mA                     | Multi-Function Bus 4. One of twelve multi-function signals MFB[11:0].                          |  |  |

| 110  | MFB3                                              | in/out      | 8 mA                     | Multi-Function Bus 3. One of twelve multi-function signals MFB[11:0].                          |  |  |

| 111  | MFB2                                              | in/out      | 8 mA                     | Multi-Function Bus 2. One of twelve multi-function signals MFB[11:0].                          |  |  |

| 112  | MFB1                                              | in/out      | 8 mA                     | Multi-Function Bus 1. One of twelve multi-function signals MFB[11:0].                          |  |  |

| 113  | MFB0                                              | in/out      | 8 mA                     | Multi-Function Bus 0. One of twelve multi-function signals MFB[11:0].                          |  |  |

| Pin | Name            | In /<br>Out | Drive Current<br>(@10pF) | Description                                                                                                                                    |  |

|-----|-----------------|-------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 125 | DVDD            |             |                          | Digital power for Destination DDS (direct digital synthesizer). Must be bypassed with a 0.1 uF capacitor to digital ground plane.              |  |

| 127 | DAC_DGNDA       |             |                          | Analog ground for Destination DDS DAC. Must be directly connected to the analog system ground plane.                                           |  |

| 128 | DAC_DVDDA       |             |                          | Analog power for Destination DDS DAC. Must be bypassed with a 0.1 uF capaci-<br>tor to pin 127 (DAC_DGNDA)                                     |  |

| 129 | PLL_DVDDA       |             |                          | Analog power for the Destination DDS PLL. Must be bypassed with a 0.1 uF capacitor to pin 131 (PLL_DGNDA)                                      |  |

| 130 | Reserved        |             |                          | For testing purposes only. Do not connect.                                                                                                     |  |

| 131 | PLL_DGNDA       |             |                          | Analog ground for the Destination DDS PLL. Must be directly connected to the analog system ground plane.                                       |  |

| 132 | SUB_DGNDA       |             |                          | Dedicated pin for the substrate guard ring that protects the Destination DDS.<br>Must be directly connected to the analog system ground plane. |  |

| 133 | SUB_SGNDA       |             |                          | Dedicated pin for the substrate guard ring that protects the Source DDS. Must be directly connected to the analog system ground plane.         |  |

| 134 | PLL_SGNDA       |             |                          | Analog ground for the Source DDS PLL. Must be directly connected to the analog system ground.                                                  |  |

| 135 | Reserved        |             |                          | For testing purposes only. Do not connect.                                                                                                     |  |

| 136 | PLL_SVDDA       |             |                          | Analog power for the Source DDS PLL. Must be bypassed with a 0.1 uF capaci-<br>tor to pin 134 (PLL_SGNDA)                                      |  |

| 137 | DAC_SVDDA       |             |                          | Analog power for the Source DDS DAC. Must be bypassed with a 0.1 uF capaci-<br>tor to pin 138 (DAC_SGNDA)                                      |  |

| 138 | DAC_SGNDA       |             |                          | Analog ground for the Source DDS DAC. Must be directly connected to the analog system ground.                                                  |  |

| 139 | SVDD            |             |                          | Digital power for the Source DDS. Must be bypassed with a 0.1 uF capacitor to digital ground plane.                                            |  |

| 141 | TCLK            | In          |                          | Reference clock (TCLK) input from the 50 Mhz crystal oscillator.                                                                               |  |

| 142 | XTAL            | Out         |                          | Not used. This pin must be connected to pin 144 (PLL_RGNDA)                                                                                    |  |

| 143 | PLL_RVDDA       |             |                          | Analog power for the Reference DDS PLL. Must be bypassed with a 0.1 uF capacitor to pin 144 (PLL_RGNDA)                                        |  |

| 144 | PLL_RGNDA       |             |                          | Analog ground for the Reference DDS PLL. Must be directly connected to the analog system ground plane.                                         |  |

| 145 | Reserved        |             |                          | For testing purposes only. Do not connect.                                                                                                     |  |

| 146 | SUB_RGNDA       |             |                          | Dedicated pin for the substrate guard ring that protects the Reference DDS.<br>Must be directly connected to the analog system ground plane.   |  |

| 148 | VSYNC           | In          |                          | CRT Vsync input. TTL Schmitt trigger input.                                                                                                    |  |

| 150 | HSYNC/<br>CSYNC | In          |                          | CRT Hsync or CRT composite sync input. TTL Schmitt trigger input.                                                                              |  |

Drive current of the panel output pins are programmable.

| TFT Panel Interface |      |             |                          |                      |  |

|---------------------|------|-------------|--------------------------|----------------------|--|

| Pin                 | Name | In /<br>Out | Drive Current<br>(@10pF) | Description          |  |

| 6                   | PD47 | out         | 2 mA ~ 20 mA             | Panel data output 47 |  |

| 7                   | PD46 | out         | 2 mA ~ 20 mA             | Panel data output 46 |  |

| 9                   | PD45 | out         | 2 mA ~ 20 mA             | Panel data output 45 |  |

| 10                  | PD44 | out         | 2 mA ~ 20 mA             | Panel data output 44 |  |

| 13                  | PD43 | out         | 2 mA ~ 20 mA             | Panel data output 43 |  |

| 14                  | PD42 | out         | 2 mA ~ 20 mA             | Panel data output 42 |  |

| 15                  | PD41 | out         | 2 mA ~ 20 mA             | Panel data output 41 |  |

| 16                  | PD40 | out         | 2 mA ~ 20 mA             | Panel data output 40 |  |

| 17                  | PD39 | out         | 2 mA ~ 20 mA             | Panel data output 39 |  |

| 19                  | PD38 | out         | 2 mA ~ 20 mA             | Panel data output 38 |  |

| 20                  | PD37 | out         | 2 mA ~ 20 mA             | Panel data output 37 |  |

| 22                  | PD36 | out         | 2 mA ~ 20 mA             | Panel data output 36 |  |

| 23                  | PD35 | out         | 2 mA ~ 20 mA             | Panel data output 35 |  |

| 24                  | PD34 | out         | 2 mA ~ 20 mA             | Panel data output 34 |  |

| 25                  | PD33 | out         | 2 mA ~ 20 mA             | Panel data output 33 |  |

| 26                  | PD32 | out         | 2 mA ~ 20 mA             | Panel data output 32 |  |

| 27                  | PD31 | out         | 2 mA ~ 20 mA             | Panel data output 31 |  |

| 28                  | PD30 | out         | 2 mA ~ 20 mA             | Panel data output 30 |  |

| 29                  | PD29 | out         | 2 mA ~ 20 mA             | Panel data output 29 |  |

| 31                  | PD28 | out         | 2 mA ~ 20 mA             | Panel data output 28 |  |

| 32                  | PD27 | out         | 2 mA ~ 20 mA             | Panel data output 27 |  |

| 34                  | PD26 | out         | 2 mA ~ 20 mA             | Panel data output 26 |  |

| 35                  | PD25 | out         | 2 mA ~ 20 mA             | Panel data output 25 |  |

| 36                  | PD24 | out         | 2 mA ~ 20 mA             | Panel data output 24 |  |

| 37                  | PD23 | out         | 2 mA ~ 20 mA             | Panel data output 23 |  |

| 38                  | PD22 | out         | 2 mA ~ 20 mA             | Panel data output 22 |  |

| 39                  | PD21 | out         | 2 mA ~ 20 mA             | Panel data output 21 |  |

| 42                  | PD20 | out         | 2 mA ~ 20 mA             | Panel data output 20 |  |

| 46                  | PD19 | out         | 2 mA ~ 20 mA             | Panel data output 19 |  |

| 47                  | PD18 | out         | 2 mA ~ 20 mA             | Panel data output 18 |  |

| 48                  | PD17 | out         | 2 mA ~ 20 mA             | Panel data output 17 |  |

| 50                  | PD16 | out         | 2 mA ~ 20 mA             | Panel data output 16 |  |

| 51                  | PD15 | out         | 2 mA ~ 20 mA             | Panel data output 15 |  |

| 52                  | PD14 | out         | 2 mA ~ 20 mA             | Panel data output 14 |  |

| 53                  | PD13 | out         | 2 mA ~ 20 mA             | Panel data output 13 |  |

| 54                  | PD12 | out         | 2 mA ~ 20 mA             | Panel data output 12 |  |

| 55                  | PD11 | out         | 2 mA ~ 20 mA             | Panel data output 11 |  |

| 56                  | PD10 | out         | 2 mA ~ 20 mA             | Panel data output 10 |  |

| 57                  | PD9  | out         | 2 mA ~ 20 mA             | Panel data output 9  |  |

| 62                  | PD8  | out         | 2 mA ~ 20 mA             | Panel data output 8  |  |

| 63                  | PD7  | out         | 2 mA ~ 20 mA             | Panel data output 7  |  |

| 64 | PD6    | out | 2 mA ~ 20 mA | Panel data output 6                                                                              |

|----|--------|-----|--------------|--------------------------------------------------------------------------------------------------|

| 66 | PD5    | out | 2 mA ~ 20 mA | Panel data output 5                                                                              |

| 67 | PD4    | out | 2 mA ~ 20 mA | Panel data output 4                                                                              |

| 68 | PD3    | out | 2 mA ~ 20 mA | Panel data output 3                                                                              |

| 69 | PD2    | out | 2 mA ~ 20 mA | Panel data output 2                                                                              |

| 70 | PD1    | out | 2 mA ~ 20 mA | Panel data output 1                                                                              |

| 71 | PD0    | out | 2 mA ~ 20 mA | Panel data output 0                                                                              |

| 43 | PDispE | out | 2 mA ~ 20 mA | This output provides a panel display enable signal that is active when flat panel data is valid. |

| 74 | PHS    | out | 2 mA ~ 20 mA | This output provides the panel line clock signal.                                                |

| 73 | PVS    | out | 2 mA ~ 20 mA | This output provides the frame start signal.                                                     |

| 44 | PCLKA  | out | 2 mA ~ 20 mA | This output is used to drive the flat panel shift clock.                                         |

| 45 | PCLKB  | out | 2 mA ~ 20 mA | Same as PCLKA above. The polarity and the phase of this signal is independently programmable.    |

| 75 | Pbias  | out | 8 mA         | This output is used to turn on / off the panel bias power or controls back-light.                |

| 76 | Ppwr   | out | 8 mA         | This output is used to control the power to a flat panel.                                        |

| Test Pi | Test Pins |        |               |                                                                                                                                                                                                 |  |  |

|---------|-----------|--------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin#    | Name      | In/Out | Drive Current | Description                                                                                                                                                                                     |  |  |

| 3       | PSCAN     | In     |               | Enable automatic PCB assembly test. When this input is pulled high, the automatic PCB assembly test mode is entered. An internal pull-down resistor drives this input low for normal operation. |  |  |

| 155     | SCAN_IN1  | In     |               | Scan input 1 used for automatic PCB assembly testing.                                                                                                                                           |  |  |

| 157     | SCAN_IN2  | In     |               | Scan input 2 used for automatic PCB assembly testing.                                                                                                                                           |  |  |

| 159     | SCAN_OUT1 | Out    |               | Scan output 1 used for automatic PCB assembly testing.                                                                                                                                          |  |  |

| 160     | SCAN_OUT2 | Out    |               | Scan output 2 used for automatic PCB assembly testing.                                                                                                                                          |  |  |

| 153     | Reserved  |        |               |                                                                                                                                                                                                 |  |  |

| 154     | Reserved  |        |               |                                                                                                                                                                                                 |  |  |

| Digital VDD / VSS for the Core Circuitry, Host Interface, and Panel/Memory Interface |                                                                                                           |  |  |

|--------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--|--|

| Pins                                                                                 | Description                                                                                               |  |  |

| 65, 40, 33, 12                                                                       | PVDD4 ~ PVDD1 for Panel / memory interface. Connect to +3.3V. Needs to be the same voltage as the CVDD's. |  |  |

| 149, 108, 58, 21, 11                                                                 | CVDD6-5, CVDD3-1 for core circuitry. Connect to +3.3V. Needs to be the save voltage as the PVDD's.        |  |  |

| 158, 151, 140, 126, 114, 72, 61, 49, 41, 30, 18, 8, 1                                | Digital grounds for core circuitry and panel / memory interface.                                          |  |  |

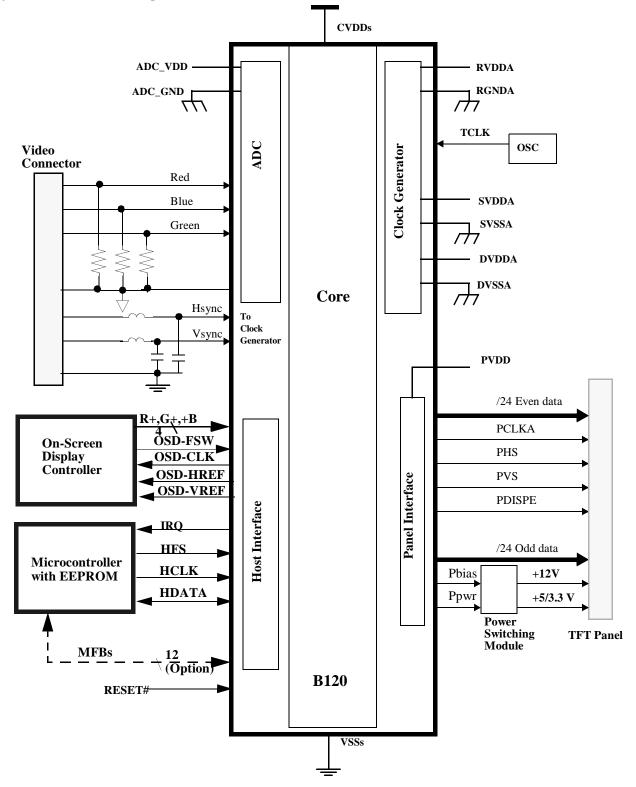

## 1.5 System-level Block Diagrams

Figure 1.5.1 Typical Stand-alone configuration with External OSD Controller

## 2. Architectural Description

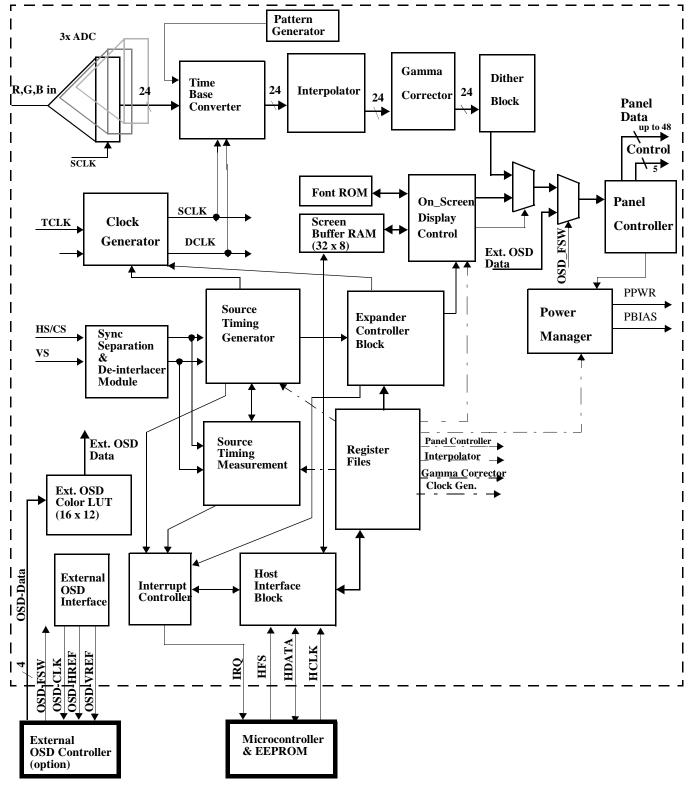

### 2.1 Overall Architecture

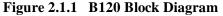

Figure 2.1.1 on the previous page is the overall block diagram of the B120 chip.

For the following discussion, refer to Figure 2.1.2 Flow of Source Video Signal

#### Initialization Upon Power-up

The microcontroller has timing parameters of a panel and various display modes stored in the EPROM/EEPROM.

The panel type and the other configuration options are read during initialization. The panel type and configuration will determine the capabilities of the destination display device (or a TFT LCD panel) which will be used to build the Device Descriptor. The specifications of the panel type selected are read from a serial EEPROM.

The supported video mode table is also read from the serial EEPROM. Timing information in each entry of the mode table will be used to define the Mode Descriptor.

#### Source Timing Measurement

When it receives the active CRT signal (R, G, B, and Sync. signals), the Source Timing Measurement unit starts measuring the horizontal and vertical timing of the incoming signal using the Sync. signals and the TCLKi as reference. Horizontal measurement occurs by measuring a minimum and maximum value for each parameter to account for TCLKi sampling granularity. Vertical parameters are measured in terms of horizontal lines. Minimum and maximum measurements are not needed in this case. Once the input timing is measured by the hardware, the Source Timing Descriptor is created and used to make several decision under program control.

#### Stand-Alone Mode

If the source timing is invalid due to one of the sync signals missing or being out of range, the firmware puts the chip in a stand-alone mode. The timing characteristics of the source are ignored in Stand-Alone mode. The panel will be driven at the maximum allowable specifications as defined in the Device Descriptor. Also, instead of using the source video data, the internal static test patterns will be displayed on the panel.

The B120 will remain in Stand-Alone mode until a valid source timing measurement is obtained or a DPMS state is entered under program control.

#### Determining the Source Display Mode

If the Source Timing Descriptor contains valid timing, it is compared to the modes listed in the mode table by the microcontroller. The micro-controller will select the mode that most closely matches the measured timing. If an exact match occurs, all previously adjusted screen position and size settings will be restored. If an exact match does not occur, user input from a front panel keypad on the monitor will adjust the screen position and size. These settings will be saved in the serial EEPROM so that when the same video mode timing is acquired again in the future, no additional front panel keypad entry will be required.

#### Generating Source Timing

Information from the Mode Descriptor, Device Descriptor, and Source Timing Descriptor are used to create a Source Descriptor. The B120 will re-generate the source video timing based on this information. From this, the video source display size, position and ADC sampling clock are determined. They are used by the ADC unit to digitize the incoming analog video data.

If the source display size is smaller than the panel size, the B120 will expand the source data to full-panel resolution. Interpolation may be performed to improve the display quality of the expanded image. This operation occurs without the use of external memory. As a result, the frame rate of the panel will always be the same as the frame rate of the source video.

| Condition                                                                                                                               | Result                                                                                                                                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input source resolution is smaller than destination panel size.<br>For example, source pixel rate is 50-MHz SVGA and panel size is XGA. | Input source data is displayed on the panel. Called <u>Normal</u><br><u>Mode</u> .                                                                          |

|                                                                                                                                         | Time base conversion occurs and the source is expanded and<br>interpolated to fill the entire panel. Called Expansion opera-<br>tion in Normal Mode.        |

|                                                                                                                                         | Destination (Panel) will have a higher pixel rate than the source. However, the destination and the source will have the same vertical refresh rate(72 Hz). |

| Input source resolution is same as destination panel size.<br>For example, source pixel rate is 75-MHz XGA and panel size is XGA        | Input source data is displayed on the panel. Called Normal Mode.                                                                                            |

|                                                                                                                                         | Since input resolution equals output resolution, no Expansion is required. Called Native operation in Normal Mode.                                          |

|                                                                                                                                         | Destination pixel rate and frame rate will be the same as source.                                                                                           |

| Input source resolution larger than destination panel size.                                                                             | The firmware will either turn off the panel or display a static                                                                                             |

| For example, source pixel rate is 65 MHz XGA and panel size is SVGA.                                                                    | pattern from the on-chip pattern generator of the B120 chip.<br>The former is called <u>Sleep Mode</u> and the latter is <u>Stand-alone</u>                 |

|                                                                                                                                         | Mode.                                                                                                                                                       |

#### Table 2.1.1 B120 Status in Various Source Display Mode / LCD Type Conditions

#### Image Processing

The B120 contains three independent lookup tables for gamma correction which are programmable through the host interface port. In addition, panel data dithering is available to support panels with data width less than 8 bits per pixel.

#### Programming the B120

Implementations using the B120 will rely on an Application Programming Interface(API) to program the B120. The API is a library of routines that will perform all the low level register and bit manipulations providing a layer of abstraction so that applications written for one family of Paradise products will be easily supported on others. In addition, each descriptor (Mode, Source timing, Device, Source and Destination) be created with a single call.

Refer to the API reference manual for more details.

Figure 2.1.2 B120 Control Flow Chart

## 2.2 CRT Interface

#### 2.2.1 Pin Connection

The CRT signals are to be connected to the B120 chip as shown in Table 2.2.1 and Table 2.2.2.

Table 2.2.1 Pin Connection for CRT Connector with HSync/Vsync

| B120 Pin Name (Pin Number) | CRT Signal Name                                | Polarity     |

|----------------------------|------------------------------------------------|--------------|

| Red+(#95)                  | Red                                            |              |

| Red- (#94)                 | N/A (Tie to Analog GND for Red on the board)   |              |

| Green+ (#91)               | Green                                          |              |

| Green- (+90)               | N/A (Tie to Analog GND for Green on the board) |              |

| Blue+ (#87)                | Blue                                           |              |

| Blue- (#86)                | N/A (Tie to Analog GND for Blue on the board)  |              |

| HSYNC/CS (#150)            | Horizontal Sync                                | Programmable |

| VSYNC (#148)               | Vertical Sync                                  | Programmable |

| Table 2.2.2 Pin Connection for CRT Connector with Composite Syn | <b>Table 2.2.2</b> | Pin Connection for CRT Connector with Compo | osite Sync |

|-----------------------------------------------------------------|--------------------|---------------------------------------------|------------|

|-----------------------------------------------------------------|--------------------|---------------------------------------------|------------|

| B120 Pin Name (Pin Number) | CRT Signal Name                                              |

|----------------------------|--------------------------------------------------------------|

| Red+ (#95)                 | Red                                                          |

| Red- (#94)                 | N/A (Tie to Analog GND for Red on the board)                 |

| Green+ (#91)               | Green                                                        |

| Green- (#90)               | N/A (Tie to Analog GND for Green on the board)               |

| Blue+ (#87)                | Blue                                                         |

| Blue- (#86)                | N/A (Tie to Analog GND for Blue on the board)                |

| HSYNC/CS (#150)            | Composite Sync<br>(TTL, no sync during vertical sync period) |

#### 2.2.2 Analog-to-Digital Converters

The B120 chip has three ADC's (analog-to-digital converters), one for each color (red, green, and blue). The characteristics of the ADC's is summarized in Table 2.2.3.

#### Table 2.2.3 ADC Characteristics

|                                                                                        | MIN    | ТҮР                                    | MAX         | NOTE                                      |

|----------------------------------------------------------------------------------------|--------|----------------------------------------|-------------|-------------------------------------------|

| RGB Track & Hold Amplifiers                                                            |        |                                        |             |                                           |

| Band Width<br>User Controlled bw<3:2>= 11<br>bw<3:2>= 10<br>bw<3:2>= 01<br>bw<3:2>= 00 |        | 160 MHz<br>100 MHz<br>85 MHz<br>60 MHz |             |                                           |

| Settling Time to 1/2 %                                                                 |        | 8.5 ns                                 |             | Full Scale Input = 0.75V, BW=160MHz (*)   |

| Full Scale Adjust Range @ R,G,B Inputs                                                 | 0.45 V |                                        | 0.95 V      |                                           |

| Full Scale Adjust Sensitivity                                                          |        | +/- 1 LSB                              |             | Measured @ ADC Output (**)                |

| Zero Scale Adjust Range                                                                |        |                                        |             | Guaranteed to remove all Internal Offsets |

| Zero Scale Adjust Sensitivity                                                          |        | +/- 1 LSB                              |             | Measured @ ADC Output                     |

| ADC + RGB Track & Hold Amplifiers                                                      |        |                                        |             |                                           |

| Sampling Frequency (fs)                                                                | 20 MHz |                                        | 110 MHz     |                                           |

| DNL                                                                                    |        |                                        | +/- 0.9 LSB | fs = 80 MHz, Guranteed no Missing Codes   |

| INL                                                                                    |        | +/- 1.5 LSB                            |             | fs = 80 MHz                               |

| Channel to Channel Matching                                                            |        | +/- 0.5 LSB                            |             |                                           |

| Effective Number of Bits (ENOB)                                                        |        | 7 Bits                                 |             | fin = 1 MHz, fs = 80 MHz Vin= -1 db below |

|                                                                                        |        |                                        |             | full scale = $0.75$ V                     |

| Power Dissipation                                                                      |        | 400 mW                                 |             | fs = 110 MHz, Vdd = 3.3V                  |

| Shut Down Current                                                                      |        |                                        | 100uA       |                                           |

(\*) Guaranteed by design (\*\*) Independent of full scale R,G,B input

#### NOTE 1: When the sampling frequency is 120 MHz.

The ADC of the B120 uses a differential input. The built-in pre-amplifier converts single ended RGB inputs from a video source into differential signal pairs, Red+/Red-, Green+/Green-, and Blue+/Blue-. (On the B120-based printed circuit board, Red-/Green-/Blue- pins must be tied to analog ground plane.) The 0V input is converted to -1V differential signal while the full-scale voltage ( $0.6V \sim 0.9V$ ) is converted to +1V. The zero-level (or the black level) and the full-scale (or the white level) of each color can be adjusted independently.

The offset is adjusted in 16 / 256 steps (4-bit value for Rev AA silicon, 8 bits for Rev BB) in the following manner:

Supply black input to the Red+/Green+/Blue+ pins of the B120 chip. If this 0V input is not converted to -1V, then offset adjustment is needed. When the voltage is lower than -1V, then the underflow bit of the B120 gets set. In this case, add a positive offset till this underflow condition is eliminated. In the meantime, when the voltage is equal to or higher than -1V, the underflow bit does not get set. In this condition, reduce the offset till underflow occurs. Then increase the offset value by one.

As far as the full-scale, it can be adjusted in 16 / 512 steps (4-bit value for Rev AA silicon, 9 bits for Rev BB) as follows:

Supply white input to the Red+/Green+/Blue+ pins of the B120 chip. If this full-scale input is not converted to +1V, In this case, increase the gain value till the overflow condition is eliminated. In the meantime, when the voltage is equal to or higher than +1V, the overflow bit does not get set. In this condition, reduce the gain till overflow occurs. Then increase the gain value by one.

#### 2.2.3 Sync. Signal Support

The type (HSync/VSync vs. Composite Sync) and the polarity of the sync signals are automatically detected by the B120 chip. The monitor application program requests this information using API calls and uses the information for source image timing determination as described in Section 2.1. The change in Sync. signal (polarity and timing) is also to be detected by the B120 chip and is communicated to the monitor application program via an interrupt.

The only type of composite sync. supported by the B120 chip is TTL composite sync. that has no composite sync. pulse during the vertical sync period.

#### 2.2.4 Display Mode Support

The B120 can support standard VGA/VESA/Macintosh display modes shown in Table 2.2.4 depending on an LCD panel specification. By default, all data input is expanded to full-panel-screen resolution.

Note that the display mode support is dependent on the specification of the TFT LCD panel used in a given flat-panel monitor as explained in Table 2.2.5 and Table 2.2.6. As long as the conditions in Table 2.2.5 and Table 2.2.6 are met, the B120 can support higher (or lower) vertical/horizontal/pixel frequencies than those values shown in Table 2.2.4.

| Resolution  | Pixel Frequency (MHz) | Horizontal Frequency (kHz) | Vertical Frequency (Hz) | Standard  |

|-------------|-----------------------|----------------------------|-------------------------|-----------|

| 360 x 400   | 14                    | 31.25                      | 70                      | VGA       |

| 720 x 400   | 28                    | 31.25                      | 70                      | VGA       |

| 320 x 200   | 12.5                  | 31.25                      | 70                      | VGA       |

| 640 x 200   | 25                    | 31.25                      | 70                      | VGA       |

| 640 x 350   | 25                    | 31.25                      | 70                      | VGA       |

| 640 x 480   | 25                    | 37.5                       | 60                      | VGA/VES   |

|             | 30.24                 | 35.00                      | 67.00                   | Macintosh |

|             | 31.5                  | 37.9                       | 72                      | VESA      |

|             | 31.5                  | 37.5                       | 75                      | VESA      |

| 800 x 600   | 36.0                  | 35.2                       | 56                      | VESA      |

|             | 40.0                  | 37.9                       | 60                      | VESA      |

|             | 50.0                  | 48.1                       | 72                      | VESA      |

|             | 49.5                  | 46.7                       | 75                      | VESA      |

| 832 x 624   | 57.29                 | 49.80                      | 74.60                   | Macintosl |

| 1024 x 768  | 65.0                  | 48.4                       | 60                      | VESA      |

|             | 75.0                  | 56.5                       | 70                      | VESA      |

|             | 78.8                  | 60.0                       | 75                      | VESA      |

|             | 80.00                 | 60.24                      | 75.00                   | Macintosl |

| 1152 x 864  | 80.00                 | 54.35                      | 60                      | VESA      |

|             | 94.2                  | 64.00                      | 70                      | VESA      |

|             | 108.00                | 67.50                      | 75.0                    | VESA      |

| 1280 x 1024 | 110.0                 | 60.31                      | 60                      | VESA      |

#### Table 2.2.4 Display Mode Table on an SXGA TFT LCD Panel

As stated earlier, the display mode support depends on the specification of the panel. The parameters that affect the displaymode support are listed in Table 2.2.5 and Table 2.2.6.

#### Table 2.2.5 LCD Parameter Requirements for Display Mode Support (1)

The following table is applicable when a display mode resolution is smaller than a panel resolution,

| LCD Parameter                                        | Requirement                                                                                                                |

|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| Max. panel clock (pixel clock) frequency             | Must be higher than the pixel-clock frequency of a given display mode.                                                     |

| Min. hor. total (in pixels) x Min. pixel clock cycle | Must be shorter than the horizontal period (1/Hor. Freq.) of a given display mode.                                         |

| Min./max. vertical total (in lines)                  | Min./max. vertical total must cover the value calculated from the following equa-<br>tion:                                 |

|                                                      | Displayed vertical size on LCD x source vertical total / source vertical size                                              |

|                                                      | where source vertical total and source vertical size are vertical total and vertical display size of a given display mode. |

| Horizontal/vertical display sizes                    | The vertical display size must be bigger than that of a given display mode.                                                |

#### Table 2.2.6 LCD Parameter Requirements for Display Mode Support (2)

The following table is applicable when a display mode resolution is the same as the panel resolution.

| LCD Parameter                              | Requirement                                                                             |

|--------------------------------------------|-----------------------------------------------------------------------------------------|

| Max. panel clock (pixel clock) frequency   | Must be higher than the pixel-clock frequency of a given display mode.                  |

| Min. and max. horizontal total (in pixels) | The min./max. horizontal total must cover the horizontal total of a given display mode. |

| Min. and max. vertical total (in lines)    | The min./max. vertical total must cover the vertical total of a given display mode.     |

As far as the color depth is concerned, refer to Table 2.2.7 below and Figure 2.1.1 on page 12.

#### Table 2.2.7Color Depth

| Signal                             | Color Depth                               |

|------------------------------------|-------------------------------------------|

| Data Input to ADC                  | Up to 8 bits/color                        |

| ADC output Time Base Converter     | 8 bits/color                              |

| Interpolator output                | 8 bits/color                              |

| Gamma (LUT) output to Dither Block | 8 bits/color                              |

| Panel interface output             | Panel color depth dependent <sup>*1</sup> |

NOTE 1: When data color depth is deeper than panel color depth, dithering may be enabled (programming option).

## **2.3 Panel Interface**

The B120 chip interfaces directly with all of today's commonly used active matrix flat panels with 640x480, 800x600, 1024x768 and 1280x1024 resolutions. The resolution and the aspect ratio are NOT limited to specific values.

#### 2.3.1 Pin Connection

The pin connection between various types of LCD panels and the B120 is listed in Table 2.3.1.

| B120     | Pin | TFT (one pix | el/clock) |    | TFT (two p | oixel/clock) |

|----------|-----|--------------|-----------|----|------------|--------------|

| Pin Name | No. |              | bit 4 bit |    | 8 bit      | 6 bit        |

| PD35     | 23  |              |           |    | OB7        | OB5          |

| PD34     | 24  |              |           |    | OB6        | OB4          |

| PD33     | 25  |              |           |    | OB5        | OB3          |

| PD32     | 26  |              |           |    | OB4        | OB2          |

| PD31     | 27  |              |           |    | OB3        | OB1          |

| PD30     | 28  |              |           |    | OB2        | OB0          |

| PD29     | 29  |              |           |    | OG7        | OG5          |

| PD28     | 31  |              |           |    | OG6        | OG4          |

| PD27     | 32  |              |           |    | OG5        | OG3          |

| PD26     | 34  |              |           |    | OG4        | OG2          |

| PD25     | 35  |              |           |    | OG3        | OG1          |

| PD24     | 36  |              |           |    | OG2        | OG0          |

| PD23     | 37  |              |           |    | OR7        | OR5          |

| PD22     | 38  |              |           |    | OR6        | OR4          |

| PD21     | 39  |              |           |    | OR5        | OR3          |

| PD20     | 42  |              |           |    | OR4        | OR2          |

| PD19     | 46  |              |           |    | OR3        | OR1          |

| PD18     | 47  |              |           |    | OR2        | OR0          |

| PD17     | 48  | B7           | B5        | B3 | EB7        | EB5          |

| PD16     | 50  | B6           | B4        | B2 | EB6        | EB4          |

| PD15     | 51  | B5           | B3        | B1 | EB5        | EB3          |

| PD14     | 52  | B4           | B2        | BO | EB4        | EB2          |

| PD13     | 53  | B3           | B1        |    | EB3        | EB1          |

| PD12     | 54  | B2           | BO        |    | EB2        | EB0          |

| PD11     | 55  | G7           | G5        | G3 | EG7        | EG5          |

| PD10     | 56  | G6           | G4        | G2 | EG6        | EG4          |

| PD9      | 57  | G5           | G3        | G1 | EG5        | EG3          |

| PD8      | 62  | G4           | G2        | GO | EG4        | EG2          |

| PD7      | 63  | G3           | G1        |    | EG3        | EG1          |

| PD6      | 64  | G2           | G0        |    | EG2        | EG0          |

| PD5      | 66  | R7           | R5        | R3 | ER7        | ER5          |

| PD4      | 67  | R6           | R4        | R2 | ER6        | ER4          |

| PD3      | 68  | R5           | R3        | R1 | ER5        | ER3          |

| PD2      | 69  | R4           | R2        | R0 | ER4        | ER2          |

| PD1      | 70  | R3           | R1        |    | ER3        | ER1          |

| PD0      | 72  | R2           | R0        |    | ER2        | ERO          |

Table 2.3.1 Panel Pin Connection (E:Even (first pixel), O:Odd (second pixel))

| B120<br>Pin Name | Pin<br>No. |     | pixel/clock)<br>6 bit 4 bit |               | TFT (two pi<br>8 bit 6  | xel/clock)<br>bit |

|------------------|------------|-----|-----------------------------|---------------|-------------------------|-------------------|

| PDispE           | 43         | PDE | PDE                         | PDE           | PDE                     | PDE               |

| PHsync           | 74         | PHs | PHs                         | PHs           | PHs                     | PHs               |

| PVsync           | 73         | PVs | PVs                         | PVs           | PVs                     | PVs               |

| PCLKA            | 44         | CLK | CLK                         | CLK           | CLKA                    | CLKA              |

| PCLKB            | 45         |     |                             |               | (CLKB)                  | (CLKB)            |

| PD47             | 6          |     |                             |               | OB1                     |                   |

| PD46             | 7          |     |                             |               | OB0                     |                   |

| PD45             | 9          |     |                             |               | OG1                     |                   |

| PD44             | 10         |     |                             |               | OG0                     |                   |

| PD43             | 13         |     |                             |               | OR1                     |                   |

| PD42             | 14         |     |                             |               | OR0                     |                   |

| PD41             | 15         | B1  |                             |               | EB1                     |                   |

| PD40             | 16         | B0  |                             |               | EB0                     |                   |

| PD39             | 17         | G1  |                             |               | EG1                     |                   |

| PD38             | 19         | GO  |                             |               | EG0                     |                   |

| PD37             | 20         | R1  |                             |               | ER1                     |                   |

| PD36             | 22         | R0  |                             |               | ER0                     |                   |

| Pbias            | 75         |     |                             | switched BLVD | D (+12V)                |                   |

| Ppower           | 76         |     |                             | switched PVDI | <b>D</b> (+5 <b>V</b> ) |                   |

#### Table 2.3.1 Panel Pin Connection (E:Even (first pixel), O:Odd (second pixel))

If the color depth of the data is larger than the panel color depth, dithering operation may be enabled. This dithering operation is also an API programming option.

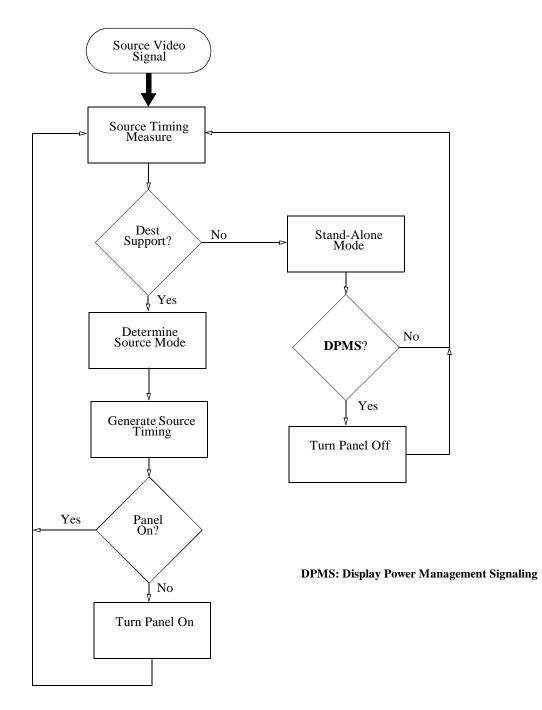

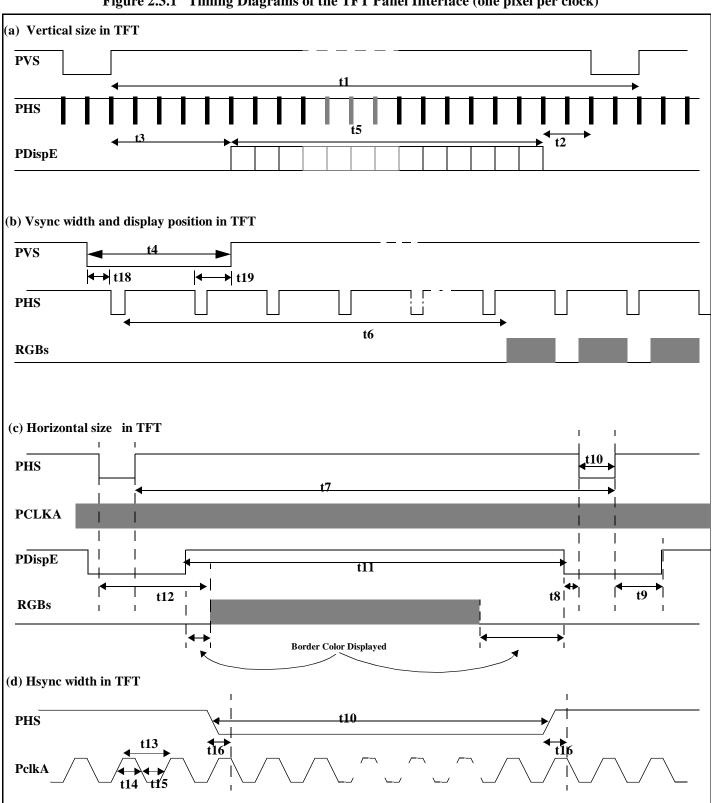

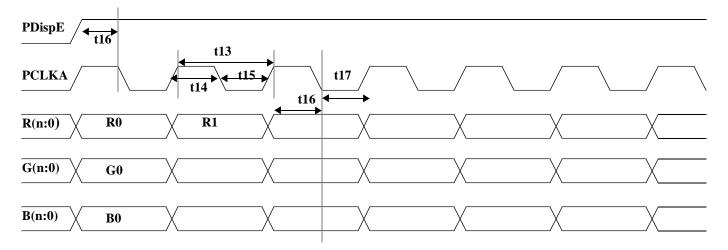

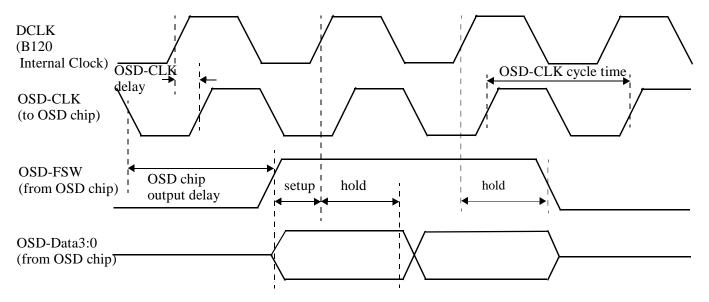

#### 2.3.2 TFT Panel Interface Timing Specification

The TFT panel interface timing parameters of the B120 chip are listed in the table below. Refer to three timing diagrams of Figure 2.3.1 and Figure 2.3.2 for the timing parameter definition.

#### Table 2.3.2 B120 TFT Panel Interface Timing

(numbers in [] are for two pixels/clock mode)

| Signal 1            | Name                   |     | min                    | typical                            | max                   | unit <sup>*1</sup> |

|---------------------|------------------------|-----|------------------------|------------------------------------|-----------------------|--------------------|

| PVS                 | period                 | t1  | 0                      |                                    | 2048                  | lines              |

|                     |                        |     |                        | 16.67                              | -                     | ms                 |

|                     | frequency              |     |                        | 60                                 | -                     | Hz                 |

|                     | front porch            | t2  | 0                      |                                    | 2048                  | lines              |

|                     | back porch             | t3  | 0                      |                                    | 2048                  | lines              |

|                     | pulse width            | t4  | 0                      |                                    | 2048                  | lines              |

|                     | PDispE                 | t5  | 0                      | panel height                       | 2048                  | lines              |

|                     | Disp. start<br>from VS | t6  | 0                      |                                    | 2048                  | lines              |

|                     | PVS set up to<br>PHS   | t18 | 1                      |                                    | 2048                  | pclk               |

|                     | PVS hold from<br>PHS   | t19 | 1                      |                                    | 2048                  | pclk               |

| PHS                 | period                 | t7  | 0                      |                                    | 2048 [1024]           | pclk               |

|                     | front porch            | t8  | 0                      |                                    | 2048                  | pclk               |

|                     | back porch             | t9  | 0                      |                                    | 2048                  | pclk               |

|                     | pulse width            | t10 | 0                      |                                    | 2048                  | pclk               |

|                     | PDispE                 | t11 | 0                      | panel width                        | 2048 [1024]           | pclk               |

|                     | Disp. start<br>from HS | t12 | 0                      |                                    | 2048                  | pclk               |

| PclkA,              | Frequency              | t13 |                        |                                    | 120 [60]              | MHz                |

| PclkB <sup>*4</sup> | Clock (H) *2           | t14 | DCLK/2 - 3 [DCLK - 3]  |                                    | DCLK/2 - 2 [DCLK - 2] | ns                 |

|                     | Clock (L) *2           | t15 | DCLK/2 - 3 [DCLK - 3]  |                                    | DCLK/2 - 2 [DCLK - 2] | ns                 |

|                     | type                   |     | -                      | one pels/clock<br>[two pels/clock[ | -                     |                    |

| Data                | set up <sup>*3</sup>   | t16 | DCLK/2 - 5 [(DCLK - 5] |                                    | DCLK/2 - 2 [DCLK - 2] | ns                 |

|                     | hold <sup>*3</sup>     | t17 | DCLK/2 - 5 [(DCLK - 5] |                                    | DCLK/2 - 2 [DCLK - 2] | ns                 |

|                     | width                  |     | 3 bits                 | 18bits [36 bits]                   | 24bits [48bits]       | bits/pixel         |

#### NOTES

\*1:The pclk is the panel shift clock.

- \*2: The DCLK stands for Destination Clock (DCLK) period. is equal to:

- pclk period. in one pixel/clock mode,

- twice the pclk period in two pixels/clock mode.

The drive current of the panel interface signals is programmable as shown in Table 1.4.1 on page 6. The drive current is to be programmed through the API upon the chip initialization. Output current is programmable from 2 mA to 20 mA in increments of 2 mA. Drive strength should be programmed to match the load presented by the cable and input of the panel. Values shown are based on a loading of 20 pF and a drive strength of 8 mA.

\*3: The same setup/hold time spec. to the pclk also applies to the PHS and the PDispE signals. The setup time (t16) and the hold time (t17) listed in this table are for the case in which no clock-to-data skew is added: The PVS/PHS/PDispE/PData signals are asserted on the rising edge of the Pclk.

Note that the polarity of the Pclk and its skew are programmable. Clock to Data skew can be adjusted in sixteen 800-ps increments. In combination with the Pclk polarity inversion, the clock-to-data phase can be adjusted in total of 31 steps.

\*4: The polarity of the PclkA and the PclkB are independently programmable.

\*5: The microcontroller must have all the timing parameters of the panel used for the monitor. The parameters are to be stored in a non-volatile memory. As can be seen from this table, the wide range of timing programmability of the B120 panel interface makes it possible to support various kinds of panels known today:

One pixel/clock and two pixels/clock; DE-only type, Sync-only type, and composite type; up to 8 bits/color.

Figure 2.3.1 Timing Diagrams of the TFT Panel Interface (one pixel per clock)

#### (a) Two pixel per clock mode in TFT

#### (b) One pixel per clock mode in TFT

Figure 2.3.2 Data latch timing of the TFT Panel Interface

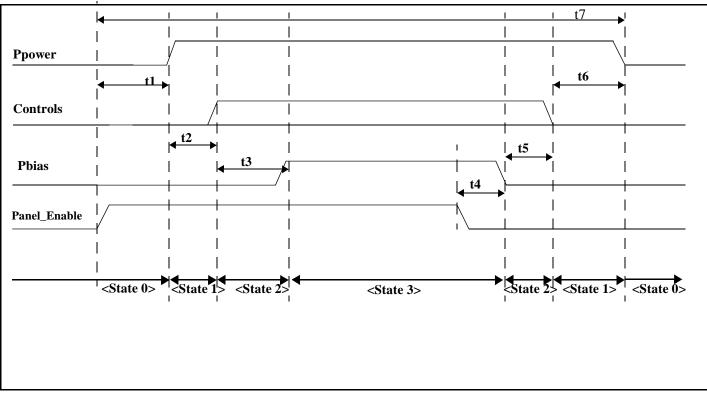

#### 2.3.3 Power Manager

LCD panels require logic power, panel bias power, and control signals to be sequenced in a specific order. Otherwise, a severe damage may occur and disable the panel permanently. The B120 has a built-in power sequencer, the Power Manager that prevents this kind of damage.

The Power Manager controls the power up/down sequences for LCD panels within the four states described below. Also see the timing diagram, Figure 2.3.3.

#### State 0 (Power Down)

The Pbias signal and the Ppower signal are low (inactive). The panel controls and data are forced low. This is the final state in power down sequence. PM is kept in state 0 until the panel is enabled.

#### State 1 (Power On)

Intermediate step 1. The Ppower is high (active), the Pbias is low (inactive), and the panel interface is forced low (inactive).

#### **State 2 (Panel Drive Enabled)**

Intermediate step 2. The Ppower is high (active), the Pbias is low (inactive), and the panel interface is active.

#### State 3 (Panel Fully Active)

Final step in power up sequence with Ppower and Pbias high (active), and the panel interface active. PM is kept in this state until the panel is disabled. The panel can be disabled through either an API call under program control or automatically by the B120 to prevent damage to the panel.

Figure 2.3.3 Panel Power Sequence

All of the six timing parameters (t1  $\sim$  t6) in Figure 2.3.3 are independently programmable from one step to eight steps in length utilizing the API call from the monitor application program.

One-step length is in the range of 511 \* X \* (TCLKi cycle) or (TCLKi cycle) \* 32193 \* X where X is any positive integer value equal to or smaller than 256. TCLKi is the reference clock to the gmB120 chip and ranges from 20 MHz to 50 MHz in frequency. This programmability provides enough flexibility to meet a wide range of power sequencing requirements by various panels.

| Timing Symbol | Description                                       |

|---------------|---------------------------------------------------|

| t1            | From Power_Enable to Ppower active                |

| t2            | Ppower active to all control signals active       |

| t3            | All control signals active to Pbias active        |

| t4            | From panel on to Pbias inactive                   |

| t5            | From Pbias inactive to control signals inactive   |

| t6            | From control signals inactive to Ppower inactive. |

| t7            | Panel power on/off cycle.                         |

|               | The minimum value is the sum of t1 ~ t6.          |

Table 2.3.3 Panel Power Sequence Timing Definition

As is the case with other panel timing parameters, the microcontroller must have the power-sequencing parameters of the panel stored in the EEPROM.

#### 2.3.4 Panel Interface Drive Strength

As mentioned previously, the B120 has programmable output pads for the TFT panel interface. Three groups of panel interface pads (panel clock, data, and control) have independent control and are programmed using API calls. See the API reference manual for details.

Table 2.3.4 Panel Interface Pad Drive Strength

| Value (4 bits) | Drive Strength in mA               |

|----------------|------------------------------------|

| 0              | Outputs are in tri-state condition |

| 1              | 2 mA                               |

| 2              | 4 mA                               |

| 3, 4           | 6 mA                               |

| 5, 8           | 8 mA                               |

| 6, 9           | 10 mA                              |

| 7, 10          | 12 mA                              |

| 11, 12         | 14 mA                              |

| 13             | 16 mA                              |

| 14             | 18 mA                              |

| 15             | 20 mA                              |

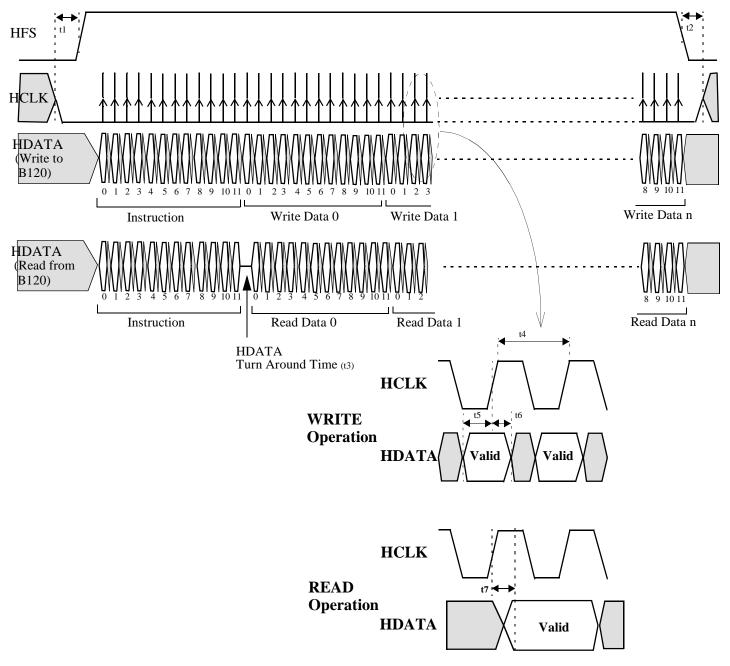

## 2.4 Host Interface

2.4.1 Pin Connection

The host microcontroller of the B120 consists of three signal for serial communication and one IRQ (interrupt request signal). In addition, the B120 has a reset pin that sets the chip to a known state when the pin is pulled low. Those signals are listed in Table 2.4.1.

| Signal Name (Pin Number) | Description                                                                                                                                                                                              |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HFS (#98)                | Host Frame Sync. that enables the serial communication when driven high by the microcontroller. The B120 chip has an internal pull-down resistor on chip. Thus, the default state of this signal is low. |

| HCLK (#103)              | Serial clock driven by the microcontroller in the write operation. May be con-<br>nected to an external pull-up resistor.                                                                                |

| HDATA (#99)              | Serial data driven:                                                                                                                                                                                      |

|                          | - by the microcontroller in the write operation,                                                                                                                                                         |

|                          | - by the B120 in the read operation.                                                                                                                                                                     |

|                          | May be connected to an external pull-up resistor.                                                                                                                                                        |

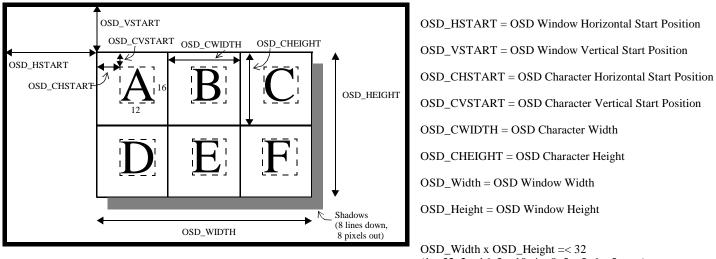

| IRQ (#102)               | IRQ pin driven by the B120 chip. The polarity is programmable.                                                                                                                                           |