### Features:

- 2.7V ~ 5.5V Operation Voltage

- Support Fixed Frequency or Resonance PWM Control

- 85 % High Efficiency

- Built-in PWM Dimming

- Programmable Striking Voltage

- Latched Open Lamp Protection

- ON/OFF Control with zero Standby Current

- Rail-to-Rail Totem Pole Output

- Low Power CMOS Process

- Winding/Piezoelectric Transformer driving Algorithm

### Applications:

- Cold Cathode Fluorescent Lamps system

- External Electrode Fluorescent Lamps system

- Personal Digital Assistants

- Digital Camera

- Tablet PC

- Navigation Devices (GPS Equipment)

- Notebook Computer

- LCD Monitor

- Video Phone/ Door Phone

### Recommended Operating Condition:

| Supply Voltage                | 2.7 ~ 5.5 V  |

|-------------------------------|--------------|

| Operating Ambient Temperature | 0 ~ 70       |

| Operating Frequency           | 30K ~ 400K H |

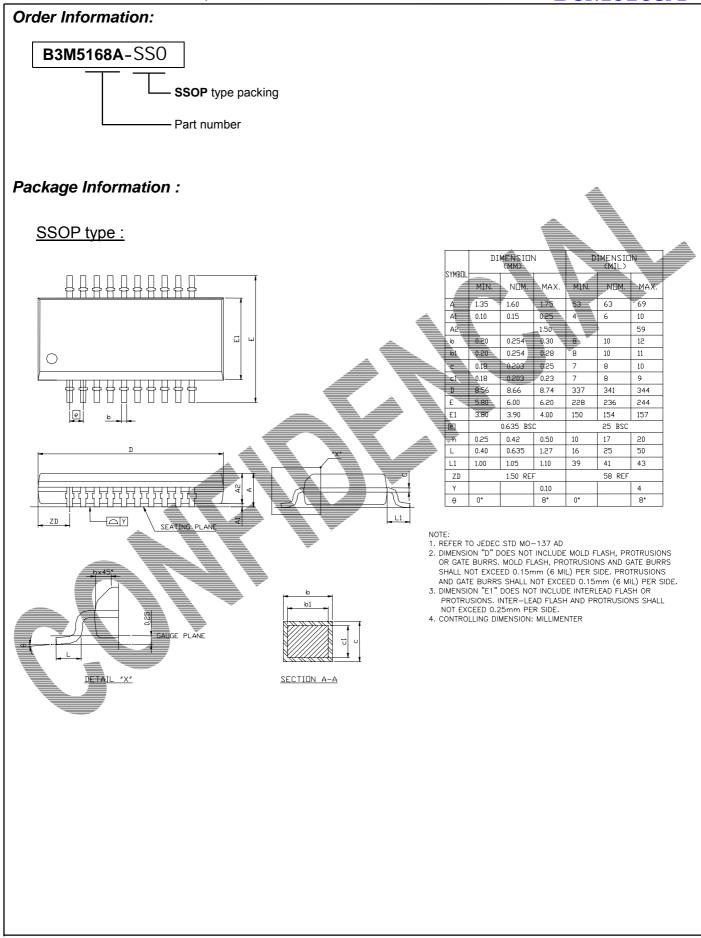

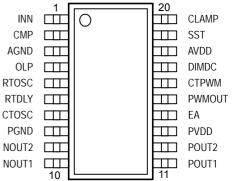

## Functional Block Diagram:

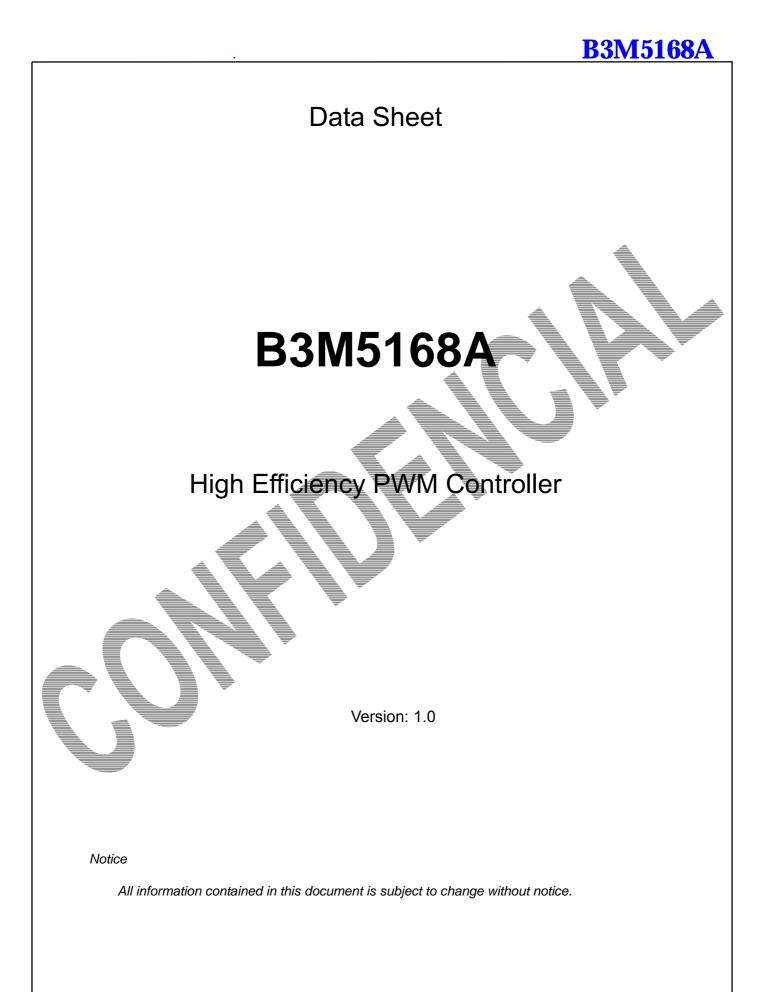

### Pin Layout:

## General Description:

B3M5168A integrated circuit provides the essential features for PWM control in a small 20 pin SSOP package. New developed PWM configuration provides a general solution to control circuitry to regulate the current of the lamps. B3M5168A senses the lamp current directly to enable the built in PWM dimming. If no current flow into the lamp, B3M5168A provides a continuous AC output to ensure the successful ignition. PWM dimming is started immediately while the lamp is ignited. B3M5168A includes a clamped striking voltage control loop to protect the transformer while ignition and the lamp current monitor provides the most reliable latched open lamp protection.

### Functional Description:

- **UVLO:** The under-voltage-lookout circuit turns the output driver off when supply voltage drops too low. System is shut down with all outputs turned to logic high level.

- **Band Gap Reference:** An internal trimmed band-gap reference provides a high accuracy, supply and temperature insensitive voltage reference. By amplifying or dividing this voltage can generate the other required references.

- **Over Voltage Clamping:** while a > 1.5V is sensed by CLAMP pin, an internal ~ 80uA current will flow into the pin INN, the inverting input of the error amplifier, to reduce the output.

- **On/Off Function:** The EA pin provides the function to turn on and off the output without shut down the supply voltage. An internal 80K ohm pulled low resistor is connected here. All of the outputs are forced to logic high when the chip is turned off.

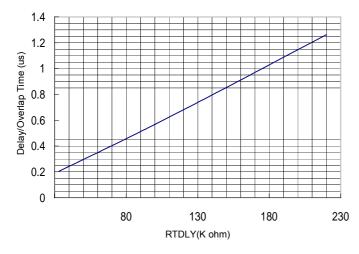

- Set the Delay/Overlap: The period of the internal delay generation circuitry dependent on the resistance of  $R_{RTDLY}$ . The control requires timing circuitry, the required period of ignition, PWM dimming PWM frequency and the delay/overlap for switching. The resistor  $R_{RTDLY}$  connected to pin RTDLY and the internal 1.25V determines a reference current  $I_{REE1}$

The Delay/Overlap time  $T_{Delay}$  and  $T_{Overlap}$  in typical case; 5V, 25°C operation, can be found from bellow:

RTDLY vs. Delay/Overlap Time

Set the Lamp Operation Frequency: Another resistor R<sub>RTOSC</sub> connected to pin RTOSC determines the reference current I<sub>REF2</sub> as equation (2)

$$I_{\text{REF2}} = \frac{1.25V}{R_{\text{RTOSC}}}....(2)$$

The lamp frequency is:

$$F_{LAMP} = \frac{1.6 \times I_{REF2}}{C_{CTOSC}}.....(3)$$

For a 55KHz operation if a 100K ohm resistor is used as the R<sub>RTOSC</sub> resistor. A 350pF capacitor is required to connect to pin CTOSC.

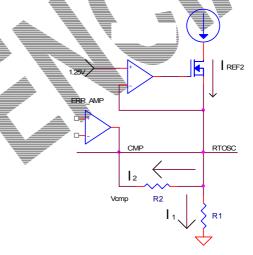

Voltage Controlled Lamp Frequency: B3M5168A provides the variable lamp frequency control scheme for resonance application. The bellowing diagram shows an example of such operation:

The reference current  $I_{\mathsf{REF2}},$  which determines the lamp frequency, can be controlled as:

$$I_{REF2} = \frac{1.25V - V_{cmp}}{R2} + \frac{1.25V}{R1}.....(4)$$

The lamp frequency is then varied with the output of the error amplifier.

#### The Power On Initialization and Open Lamp Protection:

A current mirror provides current with value  $\sim 0.05 \text{ x } I_{\text{REF1}}$  to charge the SST pin. The slope of  $\Delta V / \Delta T$  can be determined by

$$\frac{\Delta V}{\Delta T} = \frac{0.0625}{R_{\text{RTDLY}} \times C_{\text{SST}}}....(5)$$

A ~ 180uA current flow in to the inverting input of the error amplifier to force the output of PWM controller to be zero as the initial condition while the voltage of pin SST < 0.5V. Open lamp protection is triggered while pin SST >1.5V. The ignition operates while the voltage of SST located between 0.5V and 1.5V, and it

can be calculated as equation (6)

$T_{\text{STRIKE}} = 16 \times R_{\text{RTDLY}} \times C_{\text{SST}}$ .....(6)

In the case of  $R_{RTDLY}$ = 82K ohm.

A 1.0 uF capacitor connected on the pin SST can set an ~ 1 Sec period for striking the lamp. If the voltage of OLP pin less than 300mV, or larger than 1.5V after this period, the latched protection function will latch the output drivers to PVDD high level. The latched situation can be released while the system is re-started.

**PWM Dimming:** To compare the input of pin DIMDC and the 0.5V ~ 1.5V ramp wave makes the PWM pulses for PWM dimming. The ramp wave generator generates

**Pin Description:**

a ramp wave with peak =1.5V and valley =0.5V. Its frequency can be set as equation (7)

$$F_{PWM} = \frac{0.625}{R_{RTDLY} \times C_{CTPWM}}.....(7)$$

The output of pin PWMOUT is pulled to VDD to make the dark portion of the output bursts and the floating state to make the bright portion. A less than 0.5V input on pin DIMDC will make the PWMOUT to be floating to obtain 100% brightness. B3M5168A provides the continuous high voltage to strike the lamp. It sends the PWM pulses and turns off the controller while the voltage of OLP pin > 300mV.

| Pin | Names  | I/O   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----|--------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | INN    | I     | The inverting input of the error amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2   | CMP    | 0     | Output of the error amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3   | AGND   | I/O   | The ground pin of analog control circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 4   | OLP    | Ι     | Lamp current detection pin, the open lamp situation is detected if a less than 300mV input is sensed.                                                                                                                                                                                                                                                                                                                                                                 |

| 5   | RTOSC  | I/O   | An external resistor connected here makes a reference current which determines the clock timing of the output drivers.                                                                                                                                                                                                                                                                                                                                                |

| 6   | RTDLY  | I/O   | An external resistor connected here makes a reference current which determines the delay and<br>overlap timing of the output drivers. With this reference current and different capacitors can<br>set the period of ignition, the frequency of PWM dimming.                                                                                                                                                                                                           |

| 7   | CTOSC  | 1/0   | With the RTOSC pin made reference current and an external capacitor connected here can se the lamp operation frequency.                                                                                                                                                                                                                                                                                                                                               |

| 8   | PGND   | _ I/Ò | The ground pin of the output drivers.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 9   | NOUT2  | 0     | The number 2 output driver of driving the NMOSFET switch.                                                                                                                                                                                                                                                                                                                                                                                                             |

| 10  | NOUT1  | þ     | The number 1 output driver of driving the NMOSFET switch.                                                                                                                                                                                                                                                                                                                                                                                                             |

| 11  | POUT1  | 0     | The number 1 output driver of driving the PMOSFET switch.                                                                                                                                                                                                                                                                                                                                                                                                             |

| 12  | POUT2  | 0     | The number 2 output driver of driving the PMOSFET switch.                                                                                                                                                                                                                                                                                                                                                                                                             |

| 13  | PVDD   | Щ     | The power supplies input of output drivers.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 14  | EA     | ī     | ON/OFF control pin, 1.2V threshold with an internal 80K $\pm$ 15% ohm pull low resistor.                                                                                                                                                                                                                                                                                                                                                                              |

| 15  | PWMOUT | 0     | The output of PWM dimming. An ~ 2000hm pull to AVDD switch can be used to turn off the lamp with low frequency.                                                                                                                                                                                                                                                                                                                                                       |

| 16  | СТРИМ  | I/O   | With the RTDLY pin made reference current and an external capacitor connected here can set the PWM dimming operation frequency and a 0.5V ~ 1.5V triangle wave output is generated fo PWM input                                                                                                                                                                                                                                                                       |

| 17  | DIMDC  | I     | PWM dimming control input. A PWM output comes out by comparing this DC input and the triangle wave that is generated by CTPWM.                                                                                                                                                                                                                                                                                                                                        |

| 18  | AVDD   | Ι     | The power supply of analog voltage control circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 19  | SST    | 0     | With the RTDLY pin made reference current and an external capacitor connected here can set<br>the required period of ignition and the timing of initialization. The controller is forced to reset<br>mode while SST <0.3V. During reset mode, a ~ 180uA current will flow into the INN pin to<br>disable the output of the error amplifier CMP to turn off the controller. The open lamp<br>protection function will be enabled after this node is charged to > 1.5V. |

| 20  | CLAMP  | I     | Over voltage clamping and protection. If $a > 1.5$ V voltage is detected. A ~ 80uA current will flow into the INN pin to reduce the output of the error amplifier CMP to clamp the output voltage.                                                                                                                                                                                                                                                                    |

## Absolute Ratings: (if Ta=25 )

| Parameter                      | Symbol | Ratings       | Unit | Remarks |

|--------------------------------|--------|---------------|------|---------|

| Control Supply Voltage         | AVDD   | -0.3~+ 6      | V    |         |

| Analog Ground                  | AGND   | ±0.3          | V    |         |

| Driver Supply Voltage          | PVDD   | -0.3~+ 6      | V    | Ta=25°C |

| Driver Ground                  | PGND   | ±0.3          | V    |         |

| Input Voltage                  |        | -0.3~ VDD+0.3 | V    |         |

| Operating Ambient Temperature  | Та     | 0~ +70        | °C   |         |

| Operating Junction Temperature |        | +150          | °C   |         |

| Storage Temperature            |        | -55~+150      | °C   |         |

## DC/AC Characteristics:

| perating Junction Temperation           | ure                |            |       | +150    | °C                    |        |      |

|-----------------------------------------|--------------------|------------|-------|---------|-----------------------|--------|------|

| Storage Temperature                     |                    |            | -5    | 55~+150 | °C                    |        |      |

| Characteristics:                        |                    |            |       |         |                       |        |      |

| Parameter                               | Test               | Condition  | IS    | Min.    | Тур.                  | Max.   | Unit |

| Supply Voltages                         |                    |            |       |         |                       |        |      |

| AVDD (note1)                            |                    |            |       | 2.7 🦼   |                       | 5.5    | V    |

| PVDD (note1)                            |                    |            |       | 2.7     |                       | 5.5    |      |

| Chip Consumed Current                   | 5V Supp<br>Ta=25°C | ly Voltage |       |         | 1.5                   |        | mĂ   |

| Reference Voltage                       |                    | 4          |       |         | $L_{-}$               |        | -    |

| Output voltage                          | Measure            | INN        |       | 1.2125  | 1.25                  | 1.2875 | V    |

| Line regulation                         | VDD=2.7            | ~5.5 V     |       |         | 2                     | 20     | mV   |

| Under Voltage Look Out                  | Ę                  |            |       |         |                       |        |      |

| Positive Going Threshold                | Ta=25°C            |            |       | 2.4     | 2.5                   | 2.6    | V    |

| Hysteresis 🦼                            | Note4              |            |       | 0.01    | 0.1                   | 0.2    | V    |

| Ramp Wave Generator and                 | Lamp Fr            | equency    |       | Ţ.      |                       |        |      |

| Operating Frequency                     |                    |            |       | 30      |                       | 400    | KHz  |

| Output peak                             | Note2              |            |       |         | 1.5                   |        | V    |

| Output valley                           |                    |            |       |         | 0.25                  |        | V    |

| Error Amplifier                         |                    |            |       |         | •                     |        | •    |

| Input voltage                           |                    |            |       | 0.1     |                       | 3      | V    |

| Open loop gain                          | Note3              |            |       | 60      | 80                    |        | dB   |

| Unit gain band width                    | Ť                  |            |       | 1       | 1.5                   |        | MHz  |

| SST Power On Initialization             | and Ope            | en Lamp Ei | nable |         |                       |        |      |

| Output current                          |                    |            |       |         | 25/R <sub>RTDLY</sub> |        | mA   |

| Power On Reset                          |                    | , Ta=25°C  |       |         | 0.3                   |        | V    |

| Open Lamp Detection                     | VDD-0V             | , iu-20 0  |       |         | 1.5                   |        | V    |

| Enable                                  |                    |            |       |         | 1.0                   |        | v    |

| Open Lamp Protection                    |                    |            |       |         | 1                     | 1      | 1    |

| OLP pin Open lamp                       | VDD=5V             | , Ta=25°C  |       |         | 300                   |        | mV   |

| detection lower threshold               | Note 4             | ,          |       |         |                       |        |      |

| Hysterisis                              |                    |            |       |         | 20                    |        | mV   |

| Over Voltage Clamping                   |                    |            |       |         |                       | 1      |      |

| CLAMP pin detection lower               |                    |            |       |         | 1.5                   |        | V    |

| threshold                               | VDD=5V             | , Ta=25°C  |       |         |                       |        |      |

| Hysterisis                              |                    |            |       |         | 20                    |        | mV   |

| INN pin driving current On/Off Function |                    |            |       |         | 180                   |        | uA   |

|                                         |                    |            |       |         | 10                    |        | V    |

| The threshold of EA pin                 |                    | , Ta=25°C  |       |         | 1.2                   |        | V    |

| Internal pulled low                     | vDD=9V             | , 1a-20 C  |       |         | 82K                   |        | Ω    |

| resistance                              |                    |            |       |         |                       |        |      |

| PWM dimming                                                                 |                       |          |     |      |    |

|-----------------------------------------------------------------------------|-----------------------|----------|-----|------|----|

| Ramp Wave Peak                                                              |                       |          | 1.5 |      | V  |

| Ramp Wave Valley                                                            |                       |          | 0.5 |      | V  |

| PWM Frequency                                                               |                       | 10       |     | 100K | Hz |

| 100 % Brightness Dimming<br>Voltage on pin DIMDC                            |                       |          |     | 0.5  | V  |

| 0 % Brightness Dimming<br>Voltage on pin DIMDC                              | VDD=5V, Ta=25°C       | 1.5      |     |      | V  |

| Pulled high resistance of Pin<br>PWMOUT output for making<br>the dark burst |                       |          | 200 |      | Ω  |

| Pin PWMOUT output for<br>making the bright burst                            |                       | Floating |     |      |    |

| Output                                                                      |                       |          |     |      |    |

| CMOS output impedance                                                       | (Note3, Note4)        |          | 50  | A    | Ω  |

| Rising Time                                                                 | VDD=5V, 1000pF(Note3, |          | 110 |      | ns |

| Falling Time                                                                | Note4)                |          | 100 |      | ns |

Note 1. AVDD and PVDD must be set to an equal supply voltage VDD in typical application.

Note 2. The lamp operation frequency is the half of the ramp wave frequency.

Note 3. Only verified by simulation. Not 100% tested.

Note 4. The voltages of the output drivers are VDD in each off states.

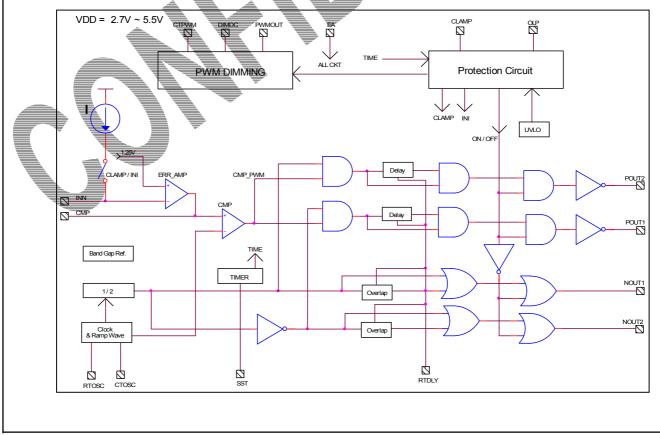

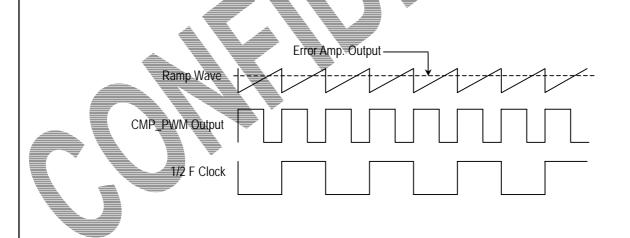

#### **Timing Diagram**

B3M5168A uses new developed fixed frequency driving methodology. The lower side switches, NMOSFET, are driven by fixed frequency and fixed > 50% duty cycle signals. The upper side switches, PMOSFET, are driven by fixed frequency PWM controlled signals. The detail timing relationship is shown as bellow:

If the lamp operation frequency is set to higher than resonant frequency of the LC tank, symmetry switching operation can be performed. A well-controlled delay and overlap timing relationship play the key role of this control scheme. It can be set through using proper resistor connected on RTDLY pin.