Ver 1.1

# **Radiation-Hardened LVDS Serializer**

# Datasheet

Part Number: B54LVDS217ARH

# Page of Revise Control

| Version<br>No. | Publish<br>Time | Revised<br>Chapter | <b>Revise Introduction</b>                   | Note |

|----------------|-----------------|--------------------|----------------------------------------------|------|

| 1.0            | 03.24.2018      |                    |                                              |      |

| 1.1            | 10.09.2018      | 6.2                | Advance Absolute Maximum ratings information |      |

|                |                 |                    |                                              |      |

|                |                 |                    |                                              |      |

|                |                 |                    |                                              |      |

|                |                 |                    |                                              |      |

|                |                 |                    |                                              |      |

B54LVDS217ARH

# TABLE OF CONTENTS

| 1.  | Features                                  | .1 |

|-----|-------------------------------------------|----|

| 2.  | General Description                       | .1 |

| 3.  | Function Block Diagram                    | .1 |

| 4.  | Packages and Pin Description Descriptions | .2 |

| 5.  | Pin List                                  | .3 |

| 6.  | Detailed Description                      | .4 |

|     | 6.1 Storage Condition                     | .4 |

|     | 6.2 Absolute Maximum Ratings              | .4 |

|     | 6.3 Recommended Operation Conditions      | .5 |

| 7.  | Specifications                            | .5 |

| 8.  | Package Specifications                    | 11 |

| 9.  | Appendix I Application Information        | 12 |

| 10. | Appendix II Replaced Product              | 14 |

# 1. Features

- 15 to 75 MHz shift clock support

- Low power consumption

- Power-down mode <216µW (max)

- Cold sparing all pins

- Narrow bus reduces cable size and cost

- Up to 1.575 Gbps throughput

- Up to 197 Megabytes/sec bandwidth

- 325 mV (typ) swing LVDS devices for low EMI

- PLL requires no external components

- Rising edge strobe

- Packaging: 48-lead flatpack (dual in-line)

- Compatible with ANSI/TIA/EIA 644-1996 LVDS Standard

- Operating temperature:  $-55^{\circ}C \sim -$ +125°C

- ESD feature (human body model): 2000V

- Electrical latch up feature: 200mA

- Total ionizing dose: ≥100Krad(Si)

- Single event latch-up threshold: ≥75MeV·cm2/mg

# 2. General Description

The B54LVDS217ARH Serializer converts 21 bits of CMOS/TTL data into three LVDS (Low Voltage Differential Signaling) data streams. A phase-locked transmit clock is transmitted in parallel with the data streams over a fourth LVDS link. Every cycle of the transmit clock 21 bits of input data are sampled and transmitted. At a transmit clock frequency of 75MHz, 21 bits of TTL data are transmitted at a rate of 525 Mbps per LVDS data channel. Using a 75MHz clock, the data throughput is 1.575 Gbit/s (197Mbytes/sec).

The B54LVDS217ARH Serializer allows the use of wide, high speed TTL interfaces while reducing overall EMI and cable size.

All pins have Cold Spare buffers. These buffers will be high impedance when VDD is tied to Vss.

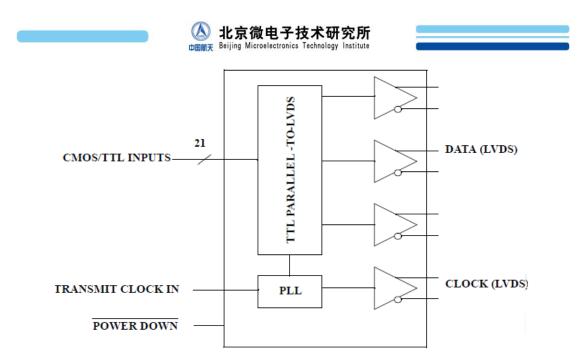

# **3. Function Block Diagram**

B54LVDS217ARH function block diagram is shown in figure 1.

Figure 1. B54LVDS217ARH Serializer Block Diagram

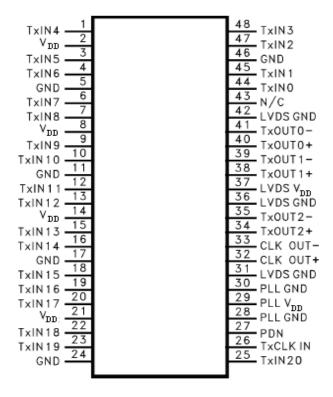

# 4. Packages and Pin Description Descriptions

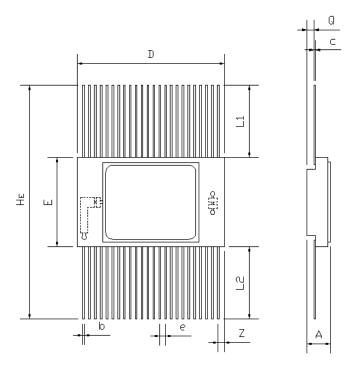

The provided package is: FP48

B54LVDS0217ARH - pin configuration is shown in Figure 2.

Figure2. B54LVDS217ARH Pinout

| Name     | I/O | No | Description                                         |

|----------|-----|----|-----------------------------------------------------|

| TxIN     | Ι   | 21 | TTL level input                                     |

| TxOUT+   | 0   | 3  | Positive LVDS differential data output              |

| TxOUT-   | 0   | 3  | Negative LVDS differential data output              |

| TxCLK IN | I   | 1  | TTL level clock input. The rising edge acts as data |

| TXCLK IN | 1   | 1  | strobe. Pin name TxCLK IN                           |

| CLKOUT+  | 0   | 1  | Positive LVDS differential clock output             |

| CLK OUT- | 0   | 1  | Negative LVDS differential clock output             |

|          |     |    | TTL level input. Assertion (low input)              |

| PDN      | Ι   | 1  | TRISTATEs the clock and data outputs, ensuring      |

|          |     |    | low current at power down.                          |

| VDD      | Ι   | 4  | Power supply pins for TTL inputs and logic          |

| GND      | Ι   | 5  | Ground pins for TTL inputs and logic                |

| PLL VDD  | Ι   | 1  | Power supply pins for PLL                           |

| PLL GND  | Ι   | 2  | Ground pins for PPL                                 |

| LVDS VDD | Ι   | 1  | Power supply pin for LVDS output                    |

| LVDS GND | Ι   | 3  | Ground pins for LVDS outputs                        |

### Table 1 B54LVDS217ARH Pin Function Descriptions

# 5. Pin List

#### Table 2 B54LVDS217ARH Pin list

| Pin<br>No | Name  | Dir | Description           | Pin<br>No | Name     | Dir | Description            |

|-----------|-------|-----|-----------------------|-----------|----------|-----|------------------------|

| 1         | TxIN4 | Ι   | Data Input 4          | 25        | TxIN20   | Ι   | Data Input 20          |

| 2         | VDD   | Р   | Digital power supply  | 26        | CLK_IN   | Ι   | clock input            |

| 3         | TxIN5 | Ι   | Data Input 5          | 27        | PDN      | Ι   | Power down(low active) |

| 4         | TxIN6 | Ι   | Data Input 6          | 28        | PLL GND  | Р   | PLL ground supply      |

| 5         | GND   | Р   | Digital ground supply | 29        | PLL VDD  | Р   | PLL power supply       |

| 6         | TxIN7 | Ι   | Data Input 7          | 30        | PLL GND  | Р   | PLL ground supply      |

| 7         | TxIN8 | Ι   | Data Input 8          | 31        | LVDS GND | Р   | LVDS ground supply     |

|    |        |   |                       |    | 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - |   |                             |

|----|--------|---|-----------------------|----|-----------------------------------------------------------------------------------------------------------------|---|-----------------------------|

| 8  | VDD    | Р | Digital power supply  | 32 | CLK_OUT+                                                                                                        | 0 | Positive LVDS clock output  |

| 9  | TxIN9  | Ι | Data Input 9          | 33 | CLK_OUT-                                                                                                        | 0 | Negative LVDS clock output  |

| 10 | TxIN10 | Ι | Data Input 10         | 34 | TxOUT2+                                                                                                         | 0 | Positive LVDS data output 2 |

| 11 | GND    | Р | Digital ground supply | 35 | TxOUT2-                                                                                                         | 0 | Negative LVDS data output 2 |

| 12 | TxIN11 | Ι | Data Input 11         | 36 | LVDS GND                                                                                                        | Р | LVDS ground supply          |

| 13 | TxIN12 | Ι | Data Input 12         | 37 | LVDS VDD                                                                                                        | Р | LVDS power supply           |

| 14 | VDD    | Р | Digital power supply  | 38 | TxOUT1+                                                                                                         | 0 | Positive LVDS data output 1 |

| 15 | TxIN13 | Ι | Data Input 13         | 39 | TxOUT1-                                                                                                         | 0 | Negative LVDS data output 1 |

| 16 | TxIN14 | Ι | Data Input 14         | 40 | TxOUT0+                                                                                                         | 0 | Positive LVDS data output 0 |

| 17 | GND    | Р | Digital ground supply | 41 | TxOUT0-                                                                                                         | 0 | Negative LVDS data output 0 |

| 18 | TxIN15 | Ι | Data Input 15         | 42 | LVDS GND                                                                                                        | Р | LVDS ground supply          |

| 19 | TxIN16 | Ι | Data Input 16         | 43 | NC                                                                                                              |   | No connection               |

| 20 | TxIN17 | Ι | Data Input 17         | 44 | TxIN0                                                                                                           | Ι | Data Input 0                |

| 21 | VDD    | Р | Digital power supply  | 45 | TxIN1                                                                                                           | Ι | Data Input 1                |

| 22 | TxIN18 | Ι | Data Input 18         | 46 | GND                                                                                                             | Р | Digital ground supply       |

| 23 | TxIN19 | Ι | Data Input 19         | 47 | TxIN2                                                                                                           | Ι | Data Input 2                |

| 24 | GND    | Р | Digital ground        | 48 | TxIN3                                                                                                           | Ι | Data Input 3                |

#### ▲ 北京微电子技术研究所 Beijing Microelectronics Technology Institute

# 6. Detailed Description

# **6.1 Storage Condition**

Packaged product should be stored in the ventilate warehouse with ambient temperature  $15^{\circ}C \sim 25^{\circ}C$  and relative humidity less than 65%. There should be no acid, alkali or other radiant gas in the environment.

# **6.2 Absolute Maximum Ratings**

- a) Supply voltage range to ground potential (V\_{DD}) : -0.3V  $\sim\!\!4.0V$

- b) DC input voltage range (V\_in) : -0.3V  $\sim$  (V\_DD+0.3V)

- c) Storage temperature  $(T_{stg})$  : -65  $^\circ\!\!\!C \sim 150 ^\circ\!\!\!\!C$

- d) Power dissipation  $(P_D)$  : 2W

- e) Lead temperature  $(T_h, 10s)$  : 260°C

- f) Thermal resistance  $(R_{th(J-C)})$  : 10°C/W

- g) Junction temperature  $(T_J)$  : +150°C

- h) DC input current ( $I_I$ ) :  $\pm 10mA$

**NOTES**: "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the device should be operated at these limits. "Electrical Characteristics" specify conditions for device operation.

### **6.3 Recommended Operation Conditions**

- a) Supply voltage relative to ground(VDD): 3.0 V to 3.6 V

- b) DC input voltage, VIN and PDN: 0 to VDD

- c) Case temperature range :  $-55^{\circ}$ C to  $+125^{\circ}$ C

# 7. Specifications

All electrical characteristics are shown in table 3.

#### Table3 B54LVDS217ARH electrical characteristics

#### **DC ELECTRICAL CHARACTERISTICS**

|        |                             | CONDITION                             | LIN  |      |      |

|--------|-----------------------------|---------------------------------------|------|------|------|

| SYMBOL | PARAMETER                   | $(VDD = 3.0V \pm 0.3V;$               | MINI | MAV  | UNIT |

|        |                             | $-55^{\circ}C < TC < +125^{\circ}C$ ) | MIN  | MAX  |      |

| VIH    | High level input voltage    |                                       | 2.0  | VDD  | V    |

| VIL    | Low level input voltage     |                                       | GND  | 0.8  | V    |

| IIH    | High-level input current    | VIN = 3.6V; VDD = 3.6V                | -10  | +10  | μΑ   |

| IIL    | Low-level input current     | VIN = 0V; VDD = 3.6V                  | -10  | +10  | μΑ   |

| VCL    | Input clamp voltage         | ICL = -18mA                           |      | -1.5 | V    |

| ICS    | Cold Spare Leakage current  | VIN = 3.6V; VDD = VSS                 | -20  | +20  | μΑ   |

| VOD    | Differential Output Voltage | $RL = 100\Omega$                      | 250  | 400  | mV   |

| Δνοd   | Change in VOD between complimentary output states | $RL = 100\Omega$                        |       | 35    | mV |  |

|--------|---------------------------------------------------|-----------------------------------------|-------|-------|----|--|

| VOS    | Offset Voltage                                    | $RL = 100\Omega$                        | 1.120 | 1.410 | V  |  |

| ΔVOS   | Change in VOS between complimentary output states | $RL = 100\Omega$                        |       | 35    | mV |  |

| IOZ    | Output Three-State Current                        | PWR DWN = 0V $VOUT = 0V  or  VDD$       | -10   | +10   | μΑ |  |

| ICSOUT | Cold Spare Leakage Current                        | VIN=3.6V, VDD = VSS                     | -20   | +20   | μΑ |  |

| IOS    | Output Short Circuit Current                      | VOUT+ or VOUT- = $0V$                   |       | 5mA   | mA |  |

| ICCL   | Transmitter supply current with loads             | $RL = 100\Omega, CL = 5pF,$ $f = 50MHz$ |       | 65.0  | mA |  |

| ICCZ   | Power down current                                | DIN = VSS, $PDN = 0V$ ,<br>f = 0Hz      |       | 60.0  | μΑ |  |

# AC SWITCHING CHARACTERISTICS

|                     |                                   | CONDITION                      |       |      |      |

|---------------------|-----------------------------------|--------------------------------|-------|------|------|

| SYMBOL              | PARAMETER                         | $(VDD = 3.0V \pm 0.3V, TA =$   | MIN   | MAX  | UNIT |

|                     |                                   | -55℃to +125℃)                  |       |      |      |

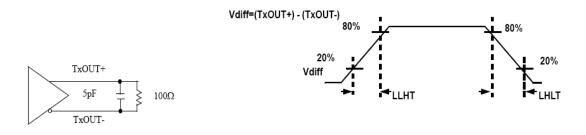

| LLHT                | LVDS Low-to-High Transition       | Figure 3                       |       | 1.5  | ns   |

|                     | Time                              | i iguie 5                      |       | 1.5  | 115  |

| LHLT                | LVDS High-to-Low Transition       | Figure 3                       |       | 1.5  | ns   |

| LILI                | Time                              | Figure 5                       |       | 1.5  | 115  |

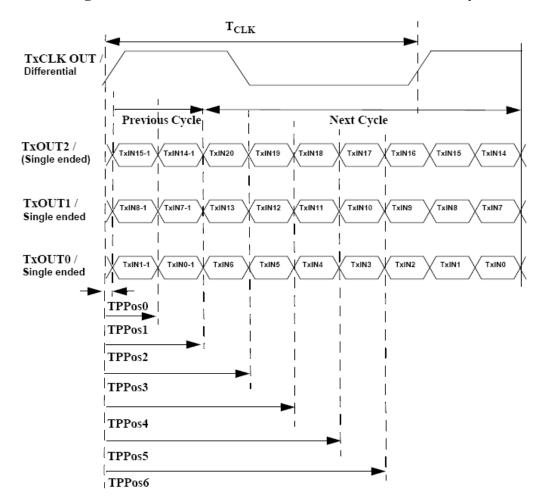

| TPPos0 <sup>a</sup> | Transmitter Output Pulse Position |                                | -0.22 | 0.23 | ns   |

| 111.050             | for Bit 0                         |                                | -0.22 | 0.23 | 115  |

| TPPos1 <sup>a</sup> | Transmitter Output Pulse Position |                                | 1.68  | 2.13 | ns   |

| 111051              | for Bit 1                         |                                | 1.00  | 2.15 | 115  |

| TPPos2 <sup>a</sup> | Transmitter Output Pulse Position |                                | 3.59  | 4.04 | ns   |

| 111052              | for Bit 2                         | V <sub>DD</sub> =3.0V ,f=75MHz | 5.59  | 4.04 | 115  |

| TPPos3 <sup>a</sup> | Transmitter Output Pulse Position | Figure9                        | 5.49  | 5.94 | ns   |

| 111085              | for Bit3                          |                                | 5.49  | 5.94 | 115  |

| TPPos4 <sup>a</sup> | Transmitter Output Pulse Position |                                | 7.40  | 7.85 | 20   |

| 111054              | for Bit 4                         |                                | 7.40  | 1.05 | ns   |

| TPPos5 <sup>a</sup> | Transmitter Output Pulse Position |                                | 9.30  | 9.75 | 20   |

| IFF0S5              | for Bit 5                         |                                | 9.30  | 9.75 | ns   |

| TPPos6 <sup>a</sup> | Transmitter Output Pulse Position |                                 | 11.21            | 11.66            | ns  |

|---------------------|-----------------------------------|---------------------------------|------------------|------------------|-----|

| 111 080             | for Bit 6                         |                                 | 11.21            | 11.00            | 115 |

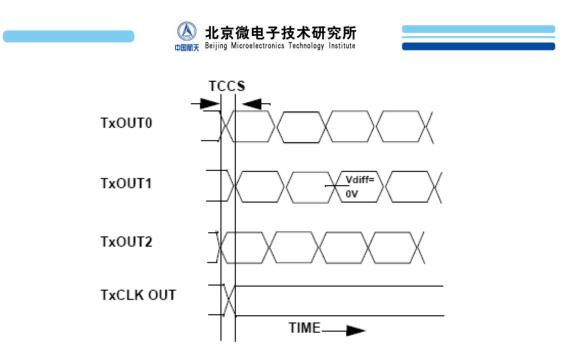

| TCCS                | Channel to Channel skew           | V <sub>DD</sub> =3.0V, Figure10 |                  | 0.45             | ns  |

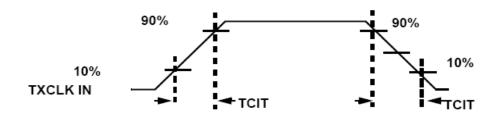

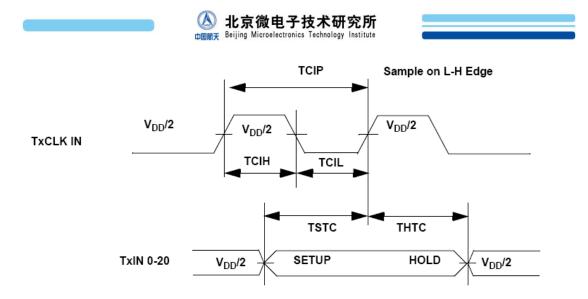

| TCIP <sup>b</sup>   | TxCLK IN Period                   | Figure5                         | 13.3             | 66.7             | ns  |

| TCIH <sup>b</sup>   | T-CLU IN IL: -1 Time              | <b>F</b> igure <b>5</b>         | 0.35             | 0.65             |     |

| ICIH                | TxCLK IN High Time                | Figure5                         | t <sub>CIP</sub> | t <sub>CIP</sub> | ns  |

| TCIL <sup>b</sup>   | TxCLK IN Low Time                 | Ei aura 5                       | 0.35             | 0.65             | ns  |

| ICIL                |                                   | Figure5                         | t <sub>CIP</sub> | t <sub>CIP</sub> |     |

| TSTC <sup>b</sup>   | TxIN Setup to TxCLK IN            | f=15MHz ,Figure5                | 1.0              |                  |     |

| 1510                |                                   | f=75MHz ,Figure5                | 0.5              |                  | ns  |

| THTC <sup>b</sup>   |                                   | f=15MHz ,Figure5                | 0.7              |                  |     |

| IHIC                | TxIN Hold to TxCLK IN             | f=75MHz ,Figure5                | 0.5              |                  | ns  |

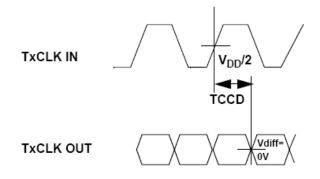

| TCCD                | TxCLK IN to TxCLK OUT Delay       | $V_{DD} = 3.0V$ , Figure6       | 0.5              | 2.5              | ns  |

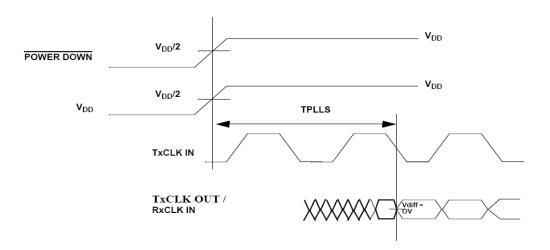

| TPLLS               | Transmitter Phase Lock Loop Set   | V <sub>DD</sub> =3.0V, Figure7  |                  | 10               | ms  |

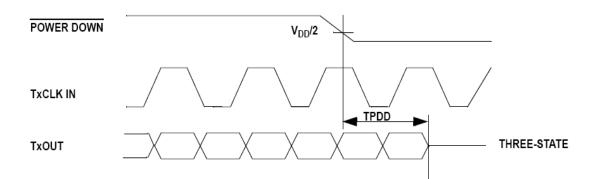

| TPDD                | Transmitter Powerdown Delay       | V <sub>DD</sub> =3.0V, Figure8  |                  | 100              | ns  |

| a: Guarante         | ed by design.                     |                                 | •                | •                |     |

| b: Guarante         | ed by characterization            |                                 |                  |                  |     |

北京微电子技术研究所 中国版表 Beijing Microelectronics Technology Institute

# **AC Timing Diagrams**

Figure 3. B54LVDS217ARH Output Load and Transition Times

Figure 4. B54LVDS217ARH Input Clock Transition Time

Figure6. B54LVDS217ARH Clock-to-Clock Out Delay

Figure 7. B54LVDS217ARH Phase Lock Loop Set Time

Figure8. B54LVDS217ARH Transmitter Powerdown Delay

Figure 9. B54LVDS217ARH Output Pulse Position Measurement

Figure 10. B54LVDS217ARH Channel-to-Channel Skew

# 8. Package Specifications

| Table 4 Package | e Size |

|-----------------|--------|

|-----------------|--------|

| Ch-al  | Value (unit: mm) |        |        |  |  |  |

|--------|------------------|--------|--------|--|--|--|

| Symbol | Min              | Normal | Max    |  |  |  |

| A      |                  |        | 3.40   |  |  |  |

| b      | 0.20             |        | 0.51   |  |  |  |

| С      | 0.07             |        | 0.22   |  |  |  |

| е      |                  | 0.635  |        |  |  |  |

| D      | 15.675           |        | 16.075 |  |  |  |

| E      | 9.452            |        | 9.852  |  |  |  |

| L1     | 1.924            |        | 8.024  |  |  |  |

| L2     | 1.924            |        | 8.024  |  |  |  |

| $H_E$  | 13.70            |        | 25.50  |  |  |  |

| Q      | 0.13             |        | 0.55   |  |  |  |

| Ζ      |                  |        | 1.27   |  |  |  |

# 9. Appendix I Application Information

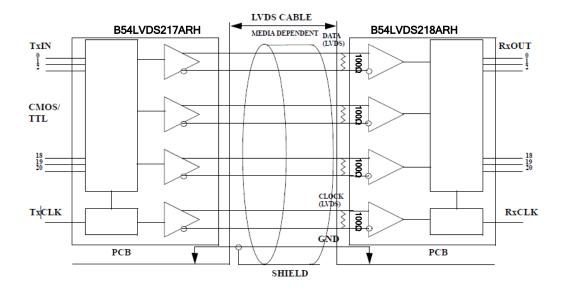

### **Typical Application**

The CHANNEL LINK devices (B54LVDS217ARH and B54LVDS218ARH) are intended to be used in a wide variety of data transmission applications. The use of serialized LVDS data lines in these applications allows for efficient signal transmission over a narrow bus width, thereby reducing cost, power, and space. Depending upon the application the interconnecting media may vary. For example, for lower data rate (clock rate) and shorter cable lengths (< 2m), the media electrical performance is less critical. For higher speed/long distance applications the media's performance becomes more critical. Certain cable constructions provide tighter skew (matched electrical length between the conductors and pairs). Additional applications information can be found in the following Interface Application Notes:

#### > Cables

A cable interface between the transmitter and receiver needs to support the differential LVDS pairs. The ideal cable/connector interface would have a constant  $100 \Omega$  differential impedance throughout the path. It is also recommended that cable skew remain below 100ps (@  $\geq 60$  MHz clock rate) to maintain a sufficient data

sampling window at the receiver. Some of the more commonly used cable types for point-to-point applications include flat ribbon, flex, twisted pair and Twin-Coax.

All are available in a variety of configurations and options. Flat ribbon cable, flex and twisted pair generally perform well in short point-to-point applications while Twin-Coax is good for short and long applications. When using ribbon cable, it is recommended to place a ground line between each differential pair to act as a barrier to noise coupling between adjacent pairs. For Twin-Coax cable applications, it is recommended to utilize a shield on each cable pair.

#### > Termination

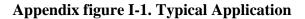

Use of current mode drivers requires a terminating resistor across the receiver inputs. The CHANNEL LINK chipset will normally require a single  $100 \Omega$  resistor between the true and complement lines on each differential pair of the receiver input. The actual value of the termination resistor should be selected to match the differential mode characteristic impedance ( $90 \Omega$  to  $120 \Omega$  typical) of the cable. Figure I-1 shows an example. Surface mount resistors are recommended to avoid the additional inductance that accompanies leaded resistors. These resistors should be placed as close as possible to the receiver input pins to reduce stubs and effectively terminate the differential lines.

#### Unused inputs

All unused inputs at the TxIN inputs of the driver must then be tied to VSS.

#### Cold Spare

All pins have Cold Spare buffers. These buffers will be high impedance when VDD is tied to VSS. But the CMOS outputs (pin 3,5,11,and 14) should not be used as cold spared pins when VDD is not tied to VSS.

#### Bypassing capacitor

Bypassing capacitors are needed to reduce the impact of switching noise which could limit performance. For a conservative approach three parallel-connected decoupling capacitors (Multi-Layered Ceramic type in surface mount form factor) between each V<sub>DD</sub> and the ground plane(s) are recommended. The three capacitor values are 0.1  $\mu$  F, 0.01  $\mu$  F and 0.001  $\mu$  F. An example is shown in Figure I-2. The designer should employ wide traces for power and ground and ensure each

capacitor has its own via to the ground plane. If board space is limiting the number of bypass capacitors, the PLL Vcc should receive the most filtering/bypassing. Next would be the LVDS Vcc pins and finally the logic Vcc pins

Appendix figure I-2. B54LVDS217ARH Decoupling Configuration

#### Clock jitter

The CHANNEL LINK devices employ a PLL to generate and recover the clock transmitted across the LVDS interface. The width of each bit in the serialized LVDS data stream is one-seventh the clock period. For example, a 75 MHz clock has a period of 13.33 ns which results in a data bit width of 1.90 ns. Differential skew ( $\Delta t$  within one differential pair), interconnect skew ( $\Delta t$  of one differential pair to another) and clock jitter will all reduce the available window for sampling the LVDS serial data streams. Care must be taken to ensure that the clock input to the transmitter be a clean low noise signal, especially low frequency component less than 1MHz. Individual bypassing of each V<sub>cc</sub> to ground will minimize the noise passed on to the PLL, thus creating a low jitter LVDS clock. These measures provide more margin for channel to channel skew and interconnect skew as a part of the overall jitter/skew budget.

# **10. Appendix II Replaced Product**

| Device Type   | Substituted Device Type |

|---------------|-------------------------|

| B54LVDS217ARH | Aeroflex UT54LVDS217    |

# Service & Support:

Address:No.2 Siyingmen N. Road. Donggaodi. Fengtai District. Beijing,China. Department: Department of international cooperation Telephone: +86(0)10-68757343 Email: gjhz@mxtronics.com Fax: +86(0)10-68757706 Zip code: 100076