**3GHz Radiation hardened wideband integer-N frequency synthesizer**

# Datasheet

Part Number: B9702RH

## **Page of Revise Control**

| Version<br>No. | Publish<br>Time | Revised<br>Chapter | Revise Introduction | Note |

|----------------|-----------------|--------------------|---------------------|------|

| 1.0            | 2018/03/07      |                    | Initial Revision    |      |

|                |                 |                    |                     |      |

|                |                 |                    |                     |      |

|                |                 |                    |                     |      |

|                |                 |                    |                     |      |

|                |                 |                    |                     |      |

|                |                 |                    |                     |      |

|                |                 |                    |                     |      |

## **TABLE OF CONTENTS**

| 1. | Features1                              |

|----|----------------------------------------|

| 2. | General Description                    |

| 3. | Function Block Diagram1                |

| 4. | Packages and Pin Descriptions          |

| 5. | Detailed Description7                  |

|    | 5.1 Function Description7              |

|    | 5.2 Storage Condition                  |

|    | 5.3 Absolute Maximum Ratings 12        |

|    | 5.4 Recommended Operation Conditions12 |

| 6. | Specifications12                       |

| 7. | Package Specifications15               |

## 1. Features

#### Scrubbing features

- $\div 10/11$  dual modulus prescaler

- Internal phase detector

- Serial, parallel or hardwired programmable

- Low phase noise

- Compatible with PE9702

- Package: 44-lead CQFJ

#### Electrical characteristics

- 3.15V to 3.45V supply voltage

- RF input frequency range : 0.5GHz ~ 3.0GHz

- Reference input frequency range:

### **2.** General Description

$\leq 100 \text{MHz}$

#### Reliability features

- Operating temperature : -55°C  $\sim$  +125°C

- ESD(human body model) : 2000V

- Total ionizing dose :

- $\geq 100 \text{Krad}(\text{Si})$

- Single event latch-up threshold :  $\geq 75 MeV \text{ cm}^2/\text{mg}$

- Single event upset threshold :  $\geq 37 MeV \cdot cm^2/mg$

The B9702RH is a high performance integer-N PLL capable of frequency synthesizer up to 3GHz with superior phase noise performance. It features a 10/11 dual modulus prescaler, counters and a phase comparator as shown in Figure 3-1. Counter values are programmable through either a serial or parallel interface and can also be directly hard wired.

The B9702RH is optimized for space applications. Single Event Latch up (SEL) is better than 75MeV cm<sup>2</sup>/mg, and Single Event Upset (SEU) is better than  $37MeV \text{ cm}^2/\text{mg}$ . It is offering excellent RF performance and intrinsic radiation tolerance. The normalized phase noise floor is -217dBc/Hz.

## **3. Function Block Diagram**

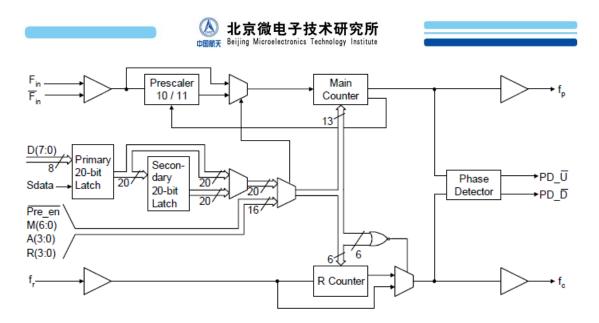

B9702RH function block diagram is shown in figure 3-1.

Figure 3-1 B9702RH function block digram

## 4. Packages and Pin Descriptions

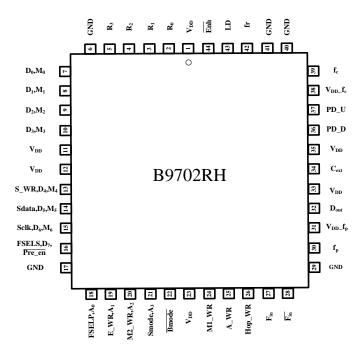

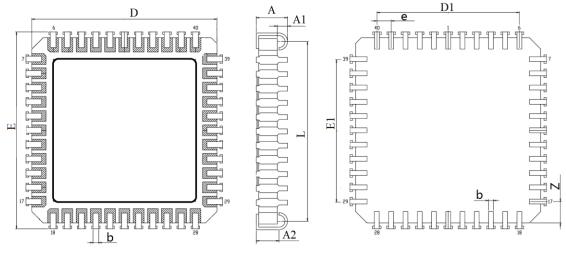

The provided package is: 44-lead CQFJ.

B9702RH 44-lead CQFJ pin configuration is shown in Figure 4-1, in top view the pin P1 is in the middle of the up side, the pins are arranged in anticlockwise order.

Figure 4-1 44-lead CQFJ pin configuration

| Pin No. | Pin Name        | Description                                                                                                                                                                                | Interface<br>Mode | Туре            |

|---------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------|

| 1       | V <sub>DD</sub> | Power supply input. Input may<br>range from 3.15 V to 3.45 V.<br>Bypassing recommended.                                                                                                    | ALL               | V <sub>DD</sub> |

| 2       | R0              | R counter bit0 (LSB)                                                                                                                                                                       | Direct            | Ι               |

| 3       | R1              | R counter bit1                                                                                                                                                                             | Direct            | Ι               |

| 4       | R2              | R counter bit2                                                                                                                                                                             | Direct            | Ι               |

| 5       | R3              | R counter bit3                                                                                                                                                                             | Direct            | Ι               |

| 6       | GND             | Ground                                                                                                                                                                                     | ALL               | GND             |

|         | D0              | Parallel data bus bit0 (LSB)                                                                                                                                                               | Parallel          | Ι               |

| 7       | M0              | M counter bit0 (LSB)                                                                                                                                                                       | Direct            | Ι               |

| 0       | D1              | Parallel data bus bit1                                                                                                                                                                     | Parallel          | Ι               |

| 8       | M1              | M counter bit1                                                                                                                                                                             | Direct            | Ι               |

|         | D2              | Parallel data bus bit2                                                                                                                                                                     | Parallel          | Ι               |

| 9       | M2              | M counter bit2                                                                                                                                                                             | Direct            | Ι               |

| 10      | D3              | Parallel data bus bit3                                                                                                                                                                     | Parallel          | Ι               |

| 10      | M3              | M counter bit3                                                                                                                                                                             | Direct            | Ι               |

| 11      | V <sub>DD</sub> | Same as pin1                                                                                                                                                                               | ALL               | V <sub>DD</sub> |

| 12      | V <sub>DD</sub> | Same as pin1                                                                                                                                                                               | ALL               | V <sub>DD</sub> |

| 13      | S_WR            | Serial load enable input. While<br>S_WR is "low", Sdata can be<br>serially clocked. Primary<br>register data is transferred to<br>the secondary register on<br>S_WR or Hop_WR rising edge. | Serial            | I               |

|         | D4              | Parallel data bus bit4                                                                                                                                                                     | Parallel          | Ι               |

|         | M4              | M counter bit4                                                                                                                                                                             | Direct            | Ι               |

| 14      | Sdata           | Binary serial data input.Input<br>data entered MSB first                                                                                                                                   | Serial            | Ι               |

|         | D5              | Parallel data bus bit5                                                                                                                                                                     | Parallel          | Ι               |

## Talble 4-1 B9702RH Pin Function Descriptions

|    | M5     | M counter bit5                                                                                                                                                                       | Direct   | Ι   |

|----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----|

| 15 | Sclk   | Serial clock input. Sdata is<br>clocked serially into the 20-bit<br>primary register (E_WR"low")<br>or the 8-bit enhancement<br>register (E_WR"high") on the<br>rising edge of Sclk. | Serial   | Ι   |

|    | D6     | Parallel data bus bit6                                                                                                                                                               | Parallel | Ι   |

|    | M6     | M counter bit6                                                                                                                                                                       | Direct   | Ι   |

| 16 | FSELS  | Selects contents of primary<br>register (FSELS=1) or<br>secondary register (FSELS=0)<br>for programming of internal<br>counters while in Serial<br>Interface Mode.                   | Serial   | Ι   |

| 16 | D7     | Parallel data bus bit7                                                                                                                                                               | Parallel | Ι   |

|    | Pre_en | Prescaler enable, active "low".<br>When "high", Fin bypasses the<br>prescaler.                                                                                                       | Direct   | Ι   |

| 17 | GND    | Ground                                                                                                                                                                               | ALL      | GND |

| 18 | FSELP  | Selects contents of primary<br>register (FSELP=1) or<br>secondary register (FSELP=0)<br>for programming of internal<br>counters while in Parallel<br>Interface Mode.                 | Parallel | Ι   |

|    | A0     | A counter bit0 (LSB)                                                                                                                                                                 | Direct   | Ι   |

|    | E_WR   | Enhancement register write<br>enable.While E_WR is "high",<br>Sdata can be serially clocked<br>into the enhancement register<br>on the rising edge of Sclk.                          | Serial   | I   |

| 19 |        | Enhancement register<br>write.D[7:0] are latched into the<br>enhancement register on the<br>rising edge of E_WR                                                                      | Parallel | Ι   |

|    | A1     | A counter bit1                                                                                                                                                                       | Direct   | Ι   |

|    | C               | AD 示 版 名 J 32 不 切 52 / / / の の の の の の の の の の の の の の の の                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | e               |          |

|----|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------|

| 20 | M2_WR           | M2 write. D[3:0] are latched<br>into the primary register<br>(R[5:4], M[8:7]) on the rising<br>edge of M2_WR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Parallel        | Ι        |

|    | A2              | A counter bit2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Direct          | Ι        |

| 21 | Smode           | Selects serial bus interface<br>mode (Bmode=0, Smode=1) or<br>Parallel Interface Mode<br>(Bmode=0, Smode=0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Serial,Parallel | Ι        |

|    | A3              | A counter bit3 (MSB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Direct          | Ι        |

| 22 | Bmode           | Selects direct interface mode (Bmode=1).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ALL             | Ι        |

| 23 | V <sub>DD</sub> | V <sub>DD</sub> Same as pin1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                 | $V_{DD}$ |

| 24 | M1_WR           | M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>M1_WR<br>WR<br>WR<br>WR<br>WR<br>WR<br>WR<br>WR<br>WR<br>WR<br>WR<br>WR<br>WR<br>W |                 | Ι        |

| 25 | A_WR            | A_WR A_WR A_WR A_WR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                 | Ι        |

| 26 | Hop_WR          | Hop write. The contents of the<br>primary register are latched into<br>the secondary register on the<br>rising edge of Hop_WR.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Serial,Parallel | Ι        |

| 27 | Fin             | Prescaler input from the VCO.3.0 GHz max frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ALL             | Ι        |

| 28 | Fin             | Prescaler complementary input.<br>A bypass capacitor in series<br>with a 51 $\Omega$ resistor should be<br>placed as close as possible to<br>this pin and be connected<br>directly to the ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ALL             | Ι        |

| 29 | GND             | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ALL             | GND      |

| 30 | fp              | Monitor pin for main divider                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ALL             | 0        |

🕓 北京微电子技术研究所

|    | c                   | 中国航天 Beijing Microelectronics Technology Institute                                                                                                                                                                                   |                 |                 |

|----|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------|

|    |                     | output. Switching activity can<br>be disabled through<br>enhancement register<br>programming or by floating or<br>grounding VDD pin 31.                                                                                              |                 |                 |

| 31 | V <sub>DD</sub> _fp | VDD for fp. Can be left<br>floating or connected to GND<br>to disable the fp output                                                                                                                                                  | ALL             | V <sub>DD</sub> |

| 32 | Dout                | Data Out. The MSEL signal and<br>the raw prescaler output are<br>available on Dout                                                                                                                                                   | Serial,Parallel | 0               |

| 33 | $V_{DD}$            | Same as pin 1                                                                                                                                                                                                                        | ALL             | $V_{DD}$        |

| 34 | Cext                | Logical "NAND" of PD_U and<br>PD_D terminated through an on<br>chip, $2 k\Omega$ series resistor.<br>Connecting Cext to an external<br>capacitor will low pass filter the<br>input to the inverting amplifier<br>used for driving LD | ALL             | 0               |

| 35 | $V_{DD}$            | Same as pin1                                                                                                                                                                                                                         | ALL             | $V_{DD}$        |

| 36 | PD_D                | PD_D is pulse down when fp leads fc.                                                                                                                                                                                                 | ALL             | О               |

| 37 | PD_U                | PD_U is pulse down when fc leads fp.                                                                                                                                                                                                 | ALL             | 0               |

| 38 | V <sub>DD</sub> _fc | VDD for fc. Can be left floating<br>or connected to GND to disable<br>the fc output.                                                                                                                                                 | ALL             | V <sub>DD</sub> |

| 39 | fc                  | Monitor pin for reference<br>divider output. Switching<br>activity can be disabled through<br>enhancement register<br>programming or by floating or<br>grounding VDD pin 38                                                          | ALL             | 0               |

| 40 | GND                 | Ground                                                                                                                                                                                                                               | ALL             | GND             |

| 41 | GND                 | Ground                                                                                                                                                                                                                               | ALL             | GND             |

| 42 | fr                  | Reference frequency input                                                                                                                                                                                                            | ALL             | Ι               |

| 43 | LD                  | Lock detect and open drain                                                                                                                                                                                                           | ALL             | 0               |

💧 北京微电子技术研究所

|    |     | ▲ 北京微电子技术研究所<br>■■表 Beijing Microelectronics Technology Institute |                 |   |

|----|-----|-------------------------------------------------------------------|-----------------|---|

|    |     | logical inversion of CEXT.                                        |                 |   |

|    |     | When the loop is in lock, LD is                                   |                 |   |

|    |     | high impedance, otherwise LD                                      |                 |   |

|    |     | is a logic low ("0").                                             |                 |   |

|    |     | Enhancement mode. When                                            |                 |   |

| 44 | Enh | asserted low ("0"),                                               | Serial,Parallel | т |

| 44 | Enn | enhancement register bits are                                     | Seriai, raranei | 1 |

|    |     | functional.                                                       |                 |   |

## **5. Detailed Description**

#### **5.1 Function Description**

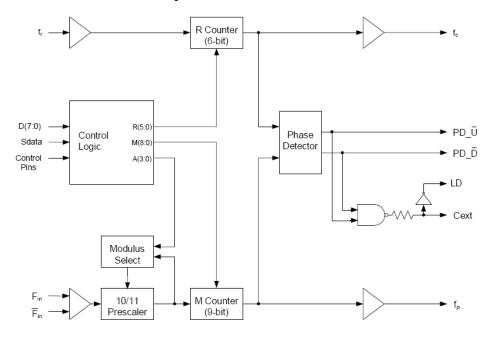

The B9702RH consists of a prescaler, counters, a phase detector, and control logic. The dual modulus prescaler divides the VCO frequency by either 10 or 11, depending on the value of the modulus select. Counters "R" and "M" divide the reference and prescaler output, respectively, by integer values stored in a 20-bit register. An additional counter ("A") is used in the modulus select logic. The phase-frequency detector generates up and down frequency control signals. The control logic includes a selectable chip interface. Data can be written via serial bus, parallel bus, or hardwired directly to the pins. There are also various operational and test modes and a lock detect output.

Figure 5-1 B9702RH function block diagram

#### 1) Main Counter Chain

#### Normal Operating Mode

The main counter chain divides the RF input frequency, Fin, by an integer derived from the user-defined values in the "M" and "A" counters. It is composed of the 10/11 dual modulus prescaler, modulus select logic, and 9-bit M counter. Setting Pre\_en "low" enables the 10/11 prescaler. Setting Pre\_en "high" allows Fin to bypass the prescaler and powers down the prescaler. The output from the main counter chain, fp, is related to the VCO frequency, Fin, by the following equation:

$$f_P = F_{in} / \left[ 10 \times (M+1) + A \right]$$

where  $A \leq M + 1, 1 \leq M \leq 511$

When the loop is locked, Fin is related to the reference frequency, fr, by the following equation:

$$F_{in} = \left[10 \times (M+1) + A\right] \times \left(f_r / (R+1)\right)$$

where  $A \leq M+1$ ,  $1 \leq M \leq 511$

A consequence of the upper limit on A is that Fin must be greater than or equal to 90 x (fr / (R+1)) to obtain contiguous channels. Programming the M Counter with the minimum value of "1" will result in a minimum M Counter divide ratio of "2".

In Direct Interface Mode, main counter inputs M7 and M8 are internally forced low. In this mode, the M value is limited to  $1 \le M \le 127$ .

#### **Prescaler Bypass Mode**

Setting Pre\_en "high" allows Fin to bypass and power down the prescaler. In this mode, the 10/11 prescaler and A register are not active, and the input VCO frequency is divided by the M counter directly. The following equation relates Fin to the reference frequency, fr:

$$F_{in} = (M+1) \times \left( f_r / (R+1) \right)$$

where  $1 \leq M \leq 511$

In Direct Interface Mode, main counter inputs M7 and M8 are internally forced low. In this mode, the M value is limited to  $1 \le M \le 127$ .

#### 2) Reference Counter

The reference counter chain divides the reference frequency, fr, down to the phase detector comparison frequency, fc. The output frequency of the 6-bit R Counter is related to the reference frequency by the following equation:

$f_{c} = (f_{r} / (R+1))$ where  $0 \leq R \leq 63$

Note that programming R with "0" will pass the reference frequency, fr, directly to the phase detector.

In Direct Interface Mode, R Counter inputs R4 and R5 are internally forced low ("0"). In this mode, the R value is limited to  $0 \le R \le 15$ .

#### **3)** Register Programming

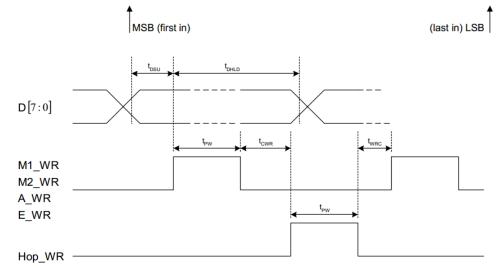

#### **Parallel Interface Mode**

Parallel Interface Mode is selected by setting the Bmode input "low" and the Smode input "low". Parallel input data, D[7:0], are latched in a parallel fashion into one of three 8-bit primary register sections on the rising edge of M1\_WR, M2\_WR, or A\_WR per the mapping shown in Table 5-1.The contents of the primary register are transferred into a secondary register on the rising edge of Hop\_WR according to the timing diagram shown in Figure 5-2. Data is transferred to the counters as shown in Table 5-1.

The secondary register acts as a buffer to allow rapid changes to the VCO frequency. This double buffering for "ping-pong" counter control is programmed via the FSELP input. When FSELP is "high", the primary register contents set the counter inputs. When FSELP is "low", the secondary register contents are utilized. Parallel input data, D[7:0], are latched into the enhancement register on the rising edge of E\_WR according to the timing diagram shown in Figure 5-2. This data provides control bits as shown in Table 5-2 with bit functionality enabled by asserting the Enh input "low".

#### Serial Interface Mode

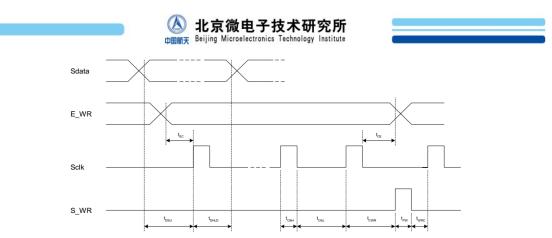

Serial Interface Mode is selected by setting the Bmode input "low" and the Smode input "high". While the E\_WR input is "low" and the S\_WR input is "low", serial input data (Sdata input), B0 to B19, is clocked serially into the primary register on the rising edge of Sclk, MSB (B0) first. The contents from the primary register are transferred into the secondary register on the rising edge of either S\_WR or Hop\_WR according to the timing diagram shown in Figure 5-3. Data is transferred to the counters as shown in Table 5-1.

The double buffering provided by the primary and secondary registers allows for "ping-pong" counter control using the FSELS input. When FSELS is "high", the primary register contents set the counter inputs. When FSELS is "low", the secondary register contents are utilized. While the E\_WR input is "high" and the S\_WR input is "low", serial input data (Sdata input), B0 to B7, is clocked serially into the

enhancement register on the rising edge of Sclk, MSB (B0) first. The enhancement register is double buffered to prevent inadvertent control changes during serial loading, with buffer capture of the serially-entered data performed on the falling edge of E\_WR according to the timing diagram shown in Figure 5-2.After the falling edge of E\_WR, the data provides control bits as shown in Table 5-2 with bit functionality enabled by asserting the Enh input "low".

#### **Direct Interface Mode**

Direct Interface Mode is selected by setting the Bmode input "high".

Counter control bits are set directly at the pins as shown in Table 5-1.In Direct Interface Mode, main counter inputs M7 and M8, and R Counter inputs R4 and R5 are internally forced low ("0").

| Interface<br>Mode | Enh                                                          | Bmode | Smode | R <sub>5</sub> | R₄             | M <sub>8</sub>        | M7             | Pre_en         | M <sub>6</sub> | M₅             | M4             | M <sub>3</sub> | M <sub>2</sub> | M1             | Mo             | R <sub>3</sub>         | R <sub>2</sub>  | R <sub>1</sub>  | R <sub>0</sub>  | <b>A</b> <sub>3</sub> | <b>A</b> <sub>2</sub> | <b>A</b> 1      | A <sub>0</sub>  |

|-------------------|--------------------------------------------------------------|-------|-------|----------------|----------------|-----------------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|------------------------|-----------------|-----------------|-----------------|-----------------------|-----------------------|-----------------|-----------------|

| Parallel          | Parallel 1 0 0 M2_WR rising edge load M1_WR rising edge load |       |       |                |                | A_WR rising edge load |                |                |                |                |                |                |                |                |                |                        |                 |                 |                 |                       |                       |                 |                 |

| Parallel          |                                                              | 0     | v     | D <sub>3</sub> | D <sub>2</sub> | D <sub>1</sub>        | D <sub>0</sub> | D <sub>7</sub> | D <sub>6</sub> | D <sub>5</sub> | D <sub>4</sub> | D <sub>3</sub> | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> | D <sub>7</sub>         | D <sub>6</sub>  | D <sub>5</sub>  | D <sub>4</sub>  | D <sub>3</sub>        | D <sub>2</sub>        | D <sub>1</sub>  | D <sub>0</sub>  |

| Serial*           | 1                                                            | 0     | 1     | Bo             | B <sub>1</sub> | B <sub>2</sub>        | B <sub>3</sub> | B4             | B₅             | B <sub>6</sub> | B <sub>7</sub> | Bs             | B9             | <b>B</b> 10    | B11            | <b>B</b> <sub>12</sub> | B <sub>13</sub> | B <sub>14</sub> | B <sub>15</sub> | B <sub>16</sub>       | B <sub>17</sub>       | B <sub>18</sub> | B <sub>19</sub> |

| Direct            | 1                                                            | 1     | x     | 0              | 0              | 0                     | 0              | Pre_en         | M <sub>6</sub> | M₅             | M4             | M <sub>3</sub> | M <sub>2</sub> | M1             | Mo             | R <sub>3</sub>         | R <sub>2</sub>  | R <sub>1</sub>  | R <sub>0</sub>  | A <sub>3</sub>        | A <sub>2</sub>        | A <sub>1</sub>  | A <sub>0</sub>  |

Table 5-1. Primary Register Programming

\*Serial data clocked serially on Sclk rising edge while E\_WR "low" and captured in secondary register on S\_WR rising edge.

MSB (first in)

(last in) LSB

| Interface<br>Mode | Enh | Bmode | Smode | Reserved       | Reserved              | Reserved              | Power<br>down  | Counter<br>Ioad | MSEL<br>output | Prescaler<br>output | f <sub>c</sub> , f <sub>p</sub> OE |  |

|-------------------|-----|-------|-------|----------------|-----------------------|-----------------------|----------------|-----------------|----------------|---------------------|------------------------------------|--|

| Parallel          | 0   | 0     | 0     |                | E_WR rising edge load |                       |                |                 |                |                     |                                    |  |

| Parallel          | 0   |       | v     | D <sub>7</sub> | D <sub>6</sub>        | D <sub>5</sub>        | D <sub>4</sub> | D <sub>3</sub>  | D <sub>2</sub> | D <sub>1</sub>      | Do                                 |  |

| Serial*           | 0   | 0     | 1     | B <sub>0</sub> | B <sub>1</sub>        | <b>B</b> <sub>2</sub> | B <sub>3</sub> | B <sub>4</sub>  | B <sub>5</sub> | B <sub>6</sub>      | B <sub>7</sub>                     |  |

Table 5-2. Enhancement Register Programming

\*Serial data clocked serially on Sclk rising edge while E\_WR "high" and captured in the double buffer on E\_WR falling edge.

Figure 5-2. Parallel Interface Mode Timing Diagram

Figure 5-3. Serial Interface Mode Timing Diagram

#### 4) Enhancement Register Bit Functionality

The functions of the enhancement register bits are shown below with all bits active high.

| Bit fu | nction                            | Description                                                                                           |

|--------|-----------------------------------|-------------------------------------------------------------------------------------------------------|

| Bit 0  | Reserved**                        |                                                                                                       |

| Bit 1  | Reserved**                        |                                                                                                       |

| Bit 2  | Reserved**                        |                                                                                                       |

| Bit 3  | Power down                        | Power down of all functions except programming interface.                                             |

| Bit 4  | MSEL output                       | Drives the internal dual modulus prescaler modulus select (MSEL)onto the Dout output.                 |

| Bit 5  | Counter load                      | Immediate and continuous load of counter<br>programming as directed by the Bmode and Smode<br>inputs. |

| Bit 6  | Prescaler output                  | Dirves the raw internal prescaler output(fmain)onto the Dout output.                                  |

| Bit 7  | f <sub>p</sub> ,f <sub>c</sub> OE | f <sub>p</sub> ,f <sub>c</sub> outputs disabled                                                       |

Table 5-3. Enhancement Register Bit Functionality

\*\*program to 0

#### 5) Phase Dector

The phase detector is triggered by rising edges from the main Counter (fp) and the reference counter (fc). It has two outputs, namely PD\_U, and PD\_D. If the divided VCO leads the divided reference in phase or frequency (fp leads fc), PD\_D pulses "low". If the divided reference leads the divided VCO in phase or frequency (fr leads fp), PD\_U pulses "low". The width of either pulse is directly proportional to phase offset between the two input signals, fp and fc. The phase detector gain is 430 mV /

radian. PD\_U and PD\_D are designed to drive an active loop filter which controls the VCO tune voltage.

PD\_U pulses result in an increase in VCO frequency and PD\_D results in a decrease in VCO frequency. A lock detect output, LD is also provided, via the pin Cext. Cext is the logical "NAND" of PD\_U and PD\_D waveforms, which is driven through a series 2k ohm resistor. Connecting Cext to an external shunt capacitor provides integration. Cext also drives the input of an internal inverting comparator with an open drain output. Thus LD is an "AND" function of PD\_U and PD\_D. See Figure1 for a schematic of this circuit.

#### **5.2 Storage Condition**

Packaged product should be stored in the ventilate warehouse with ambient temperature  $10^{\circ}C \sim 30^{\circ}C$  and relative humidity less than 70%. There should be no acid, alkali or other radiant gas in the environment.

#### **5.3 Absolute Maximum Ratings**

- a) Supply voltage (V<sub>DD</sub>) : -0.3 V  $\sim 3.9$  V

- b) Voltage on any input (V\_I) : -0.3 V  $\,\sim\,$  V\_{DD}+0.3V

- c) Operating temperature range  $(T_A)$  : -55 °C  $\sim 125$  °C

- d) Storage temperature range  $(T_{stg})$  : -65 °C  $\sim$  150 °C

- e) Maximum Junction Temperature  $(T_J)$  : 150°C

- f) Thermal resistance junction to case  $(R_{th(J-C)}) : 5^{\circ}C/W$

- g) Lead temperature  $10s (T_h) : 260^{\circ}C$

#### **5.4 Recommended Operation Conditions**

- a) Supply voltage ( $V_{DD}$ ) : 3.15V ~ 3.45V

- b) Case operation temperature range  $(T_A)$  : -55 °C ~ 125 °C

## 6. Specifications

All electrical characteristics are shown in table 6-1 and table 6-2.  $V_{DD}$ =3.3V,  $T_A$ = -55 °C to 125 °C, unless otherwise noted.

| Symbol                   | Parameter                                         | Conditions                                 | Min                  | Тур | Max                 | Units |  |  |  |  |  |

|--------------------------|---------------------------------------------------|--------------------------------------------|----------------------|-----|---------------------|-------|--|--|--|--|--|

|                          | Operational supply current                        |                                            |                      |     |                     |       |  |  |  |  |  |

| I <sub>dd</sub>          | Prescaler disabled                                | V <sub>DD</sub> =3.15 to 3.45V             |                      | 15  |                     | mA    |  |  |  |  |  |

|                          | Prescaler enabled                                 |                                            |                      | 32  | 37                  | mA    |  |  |  |  |  |

| Digital Inputs           | s : All except f <sub>r</sub> , F <sub>in</sub> , |                                            |                      |     |                     |       |  |  |  |  |  |

| V <sub>IH</sub>          | High level input<br>voltage                       | V <sub>DD</sub> =3.15 to 3.45V             | $0.7 \times V_{DD}$  |     |                     | V     |  |  |  |  |  |

| V <sub>IL</sub>          | Low level input<br>voltage                        | V <sub>DD</sub> =3.15 to 3.45V             |                      |     | 0.3×V <sub>DD</sub> | V     |  |  |  |  |  |

| I <sub>IH</sub>          | High level input<br>current                       | V <sub>IH</sub> =V <sub>DD</sub> =3.45V    |                      |     | +70                 | uA    |  |  |  |  |  |

| I <sub>IL</sub>          | Low level input<br>current                        | V <sub>IL</sub> =0, V <sub>DD</sub> =3.45V | -1                   |     |                     | uA    |  |  |  |  |  |

| Reference Di             | Reference Divider input: f <sub>r</sub>           |                                            |                      |     |                     |       |  |  |  |  |  |

| I <sub>IHR</sub>         | High level input<br>current                       | V <sub>IH</sub> =V <sub>DD</sub> =3.45V    |                      |     | +100                | uA    |  |  |  |  |  |

| I <sub>ILR</sub>         | Low level input<br>current                        | V <sub>IL</sub> =0, V <sub>DD</sub> =3.45V | -100                 |     |                     | uA    |  |  |  |  |  |

| R0 Input: R <sub>0</sub> |                                                   |                                            |                      |     |                     |       |  |  |  |  |  |

| I <sub>IHR</sub>         | High level input<br>current                       | V <sub>IH</sub> =V <sub>DD</sub> =3.45V    |                      |     | +70                 | uA    |  |  |  |  |  |

| I <sub>ILR</sub>         | Low level input<br>current                        | V <sub>IL</sub> =0, V <sub>DD</sub> =3.45V | -5                   |     |                     | uA    |  |  |  |  |  |

| Counter and j            | phase detector outputs: f <sub>c</sub>            | , f <sub>p</sub>                           |                      |     |                     |       |  |  |  |  |  |

| V <sub>OLD</sub>         | Output voltage Low                                | I <sub>out</sub> =6mA                      |                      |     | 0.4                 | V     |  |  |  |  |  |

| V <sub>OHD</sub>         | Output voltage High                               | I <sub>out</sub> =-3mA                     | V <sub>DD</sub> -0.4 |     |                     | V     |  |  |  |  |  |

| Lock detect of           | outputs: Cext, LD                                 |                                            |                      |     |                     |       |  |  |  |  |  |

| V <sub>OLC</sub>         | Output voltage Low,<br>Cext                       | I <sub>out</sub> =100uA                    |                      |     | 0.4                 | V     |  |  |  |  |  |

#### Table 6-1 B9702RH DC characteristics

#### ▲ 北京微电子技术研究所 ■ Beijing Microelectronics Technology Institute

| V <sub>OHC</sub>  | Output voltage High,<br>Cext | Iout=-100uA           | V <sub>DD</sub> -0.4 |     | V |

|-------------------|------------------------------|-----------------------|----------------------|-----|---|

| V <sub>OLLD</sub> | Output voltage Low,<br>LD    | I <sub>out</sub> =6mA |                      | 0.4 | V |

#### Table 6-2 B9702RH AC characteristics

| Symbol                                                  | Parameter                                                                                                  | Conditions                                    | Min | Max  | Units |  |  |  |

|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-----|------|-------|--|--|--|

| Control interface and latches(see figure 3-1, 5-2, 5-3) |                                                                                                            |                                               |     |      |       |  |  |  |

| $\mathbf{f}_{clk}$                                      | Serial data clock frequency                                                                                | Note1                                         |     | 10   | MHz   |  |  |  |

| t <sub>clkH</sub>                                       | Serial clock HIGH time                                                                                     |                                               | 30  |      | ns    |  |  |  |

| t <sub>clkL</sub>                                       | Serial clock LOW time                                                                                      |                                               | 30  |      | ns    |  |  |  |

| t <sub>DSU</sub>                                        | Sdata set-up time after Sclk rising edge,<br>D[7:0] set-up time to M1_WR, M2_WR,<br>A_WR, E_WR rising edge |                                               | 10  |      | ns    |  |  |  |

| t <sub>DHLD</sub>                                       | Sdata hold time after Sclk rising edge,<br>D[7:0] hold time to M1_WR, M2_WR,<br>A_WR, E_WR rising edge     |                                               | 10  |      | ns    |  |  |  |

| $t_{\rm PW}$                                            | S_WR, M1_WR, M2_WR, A_WR, E_WR<br>pulse width                                                              |                                               | 30  |      | ns    |  |  |  |

| t <sub>CWR</sub>                                        | Sclk rising edge to S_WR rising<br>edge.S_WR, M1_WR, M2_WR, A_WR<br>falling edge to Hop_WR rising edge     |                                               | 30  |      | ns    |  |  |  |

| t <sub>CE</sub>                                         | Sclk falling edge to E_WR transition                                                                       |                                               | 30  |      | ns    |  |  |  |

| t <sub>wrc</sub>                                        | S_WR falling edge to Sclk rising edge.<br>Hop_WR falling edge to S_WR, M1_WR,<br>M2_WR, A_WR rising edge   |                                               | 30  |      | ns    |  |  |  |