# 50 $\Omega$ nominal input / conjugate matched balun to ST S2-LP, 433 MHz with integrated harmonic filter

Flip-Chip (6 bumps) package

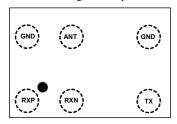

Pinout diagram - Top view

#### **Features**

- 50  $\Omega$  nominal input / conjugate matched to ST S2-LP for 433 MHz frequency operation

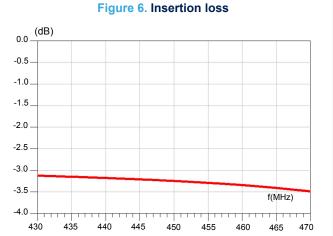

- · Low insertion loss

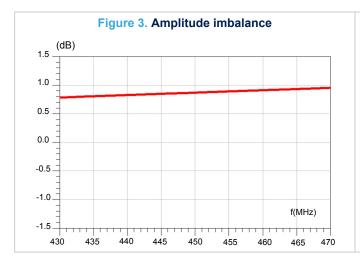

- · Low amplitude imbalance

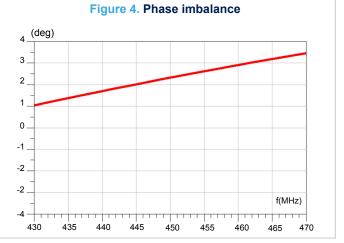

- · Low phase imbalance

- · Small footprint

- Very low profile < 620 μm after reflow</li>

- High RF performance

- · RF BOM and area reduction

- ECOPACK<sup>®</sup>2 compliant component

### **Applications**

- 433 MHz impedance matched balun filter

- Optimized for ST S2-LP sub GHz RFIC

### **Description**

This device is an ultra-miniature balun. The BALF-SPI2-02D3 integrates matching network and harmonics filter. Matching impedance has been customized for the ST S2-LP transceiver. The BALF-SPI2-02D3 uses STMicroelectronics IPD technology on non-conductive glass substrate which optimize RF performance.

**Product status**

BALF-SPI2-02D3

# 1 Characteristics

Table 1. Absolute maximum ratings (T<sub>amb</sub> = 25 °C)

| Symbol           | Parameter                                                                                                                                         | Value       | Unit |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------|

| P <sub>IN</sub>  | Input power RF <sub>IN</sub>                                                                                                                      | 20          | dBm  |

| V <sub>ESD</sub> | ESD ratings human body model (JESD22-A114), all I/O one at a time while others connected to GND  ESD ratings machine model (JESD22-A115), all I/O |             | V    |

|                  |                                                                                                                                                   |             |      |

| T <sub>OP</sub>  | Operating temperature                                                                                                                             | -40 to +105 | °C   |

Table 2. Impedances (T<sub>amb</sub> = 25 °C)

| Symbol Parameter |                                         | Value |                  |      | - Unit |

|------------------|-----------------------------------------|-------|------------------|------|--------|

| Syllibol         | r ai dilletei                           | Min.  | Тур.             | Max. | Oilit  |

| Z <sub>RX</sub>  | Nominal differential RX balun impedance |       | matched ST S2-LP | -    | Ω      |

| Z <sub>TX</sub>  | Nominal TX filter impedance             | _     | matched ST S2-LP |      |        |

| Z <sub>ANT</sub> | Antenna impedance                       | -     | 50               | -    | Ω      |

Table 3. Electrical characteristics and RF performances ( $T_{amb}$  = 25 °C)

| Symbol               | Parameter                                                     | Test condition     | Value |      |      | Unit |

|----------------------|---------------------------------------------------------------|--------------------|-------|------|------|------|

|                      | Falanielei                                                    | rest condition     | Min.  | Тур. | Max. | Unit |

| f                    | Frequency range                                               |                    |       | 433  |      | MHz  |

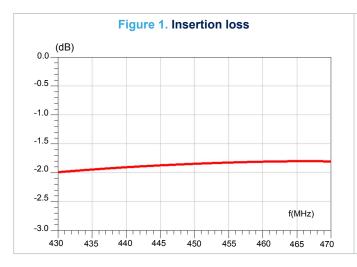

| IL <sub>RX-ANT</sub> | Insertion loss in bandwidth without mismatch                  | n loss (RX balun)  |       | 1.95 | 2.20 | dB   |

| IL <sub>TX-ANT</sub> | Insertion loss in bandwidth without mismatch loss (TX filter) |                    |       | 3.15 | 3.60 | dB   |

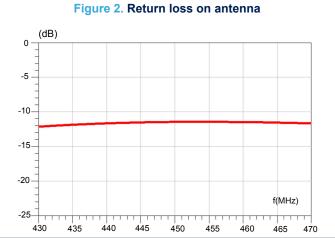

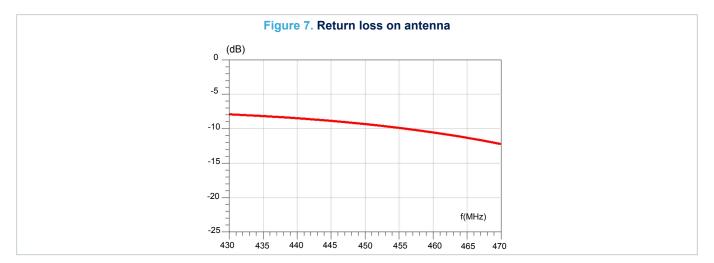

| RL <sub>RX-ANT</sub> | Input return loss in bandwidth (RX balun)                     |                    |       | 12   |      | dB   |

| RL <sub>TX-ANT</sub> | Input return loss in bandwidth (TX filter)                    |                    |       | 8.0  |      | dB   |

| Ф <sub>imb</sub>     | Output phase imbalance (RX balun)                             |                    |       |      | 2.1  | o    |

| A <sub>imb</sub>     | Output amplitude imbalance (RX balun)                         |                    | -1.1  |      | 1.1  | dB   |

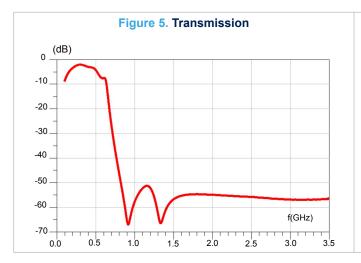

|                      | Harmonic levels (TX filter)                                   | Attenuation at 2fo | 52    | 58   |      | dB   |

|                      |                                                               | Attenuation at 3fo | 53    | 63   |      |      |

| Att                  |                                                               | Attenuation at 4fo | 54    | 55   |      |      |

| All                  |                                                               | Attenuation at 5fo | 54    | 55   |      |      |

|                      |                                                               | Attenuation at 6fo | 55    | 56   |      |      |

|                      |                                                               | Attenuation at 7fo | 56    | 57   |      |      |

DS12508 - Rev 1 page 2/13

### 1.1 RF measurements (Rx balun)

DS12508 - Rev 1 page 3/13

# 1.2 RF measurements (Tx filter)

DS12508 - Rev 1 page 4/13

# 1.3 ST S2-LP application diagram example

Digital interface GPIO3 GPIO2 GPIO0 CSN VBATT SCLK SDI SDO VDDRXDIG RXP RXN VDDSMPS SMPS1 SMPS2 17 16 15 14 13 XOUT XIN SDN RX\_P RX\_N VDDANASYNTH VRSYNTH VREFVCO VDDVCOTX TX VRRF GND SHUTDOWN GND BALF-SPI2 25 S2-LP C21 VSMPS2

Figure 8. ST S2-LP application diagram example

DS12508 - Rev 1 page 5/13

# 2 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK® specifications, grade definitions and product status are available at: www.st.com. ECOPACK® is an ST trademark.

### 2.1 Flip-Chip 6 bumps package information

Diam: b

Figure 9. Flip-Chip 6 bumps package outline (bottom and side view)

Table 4. Flip-Chip 6 bumps dimensions (in mm)

| Parameter | Min.  | Тур.  | Max.  |

|-----------|-------|-------|-------|

| Α         | 0.580 | 0.630 | 0.680 |

| A1        | 0.180 | 0.205 | 0.230 |

| A2        | 0.380 | 0.400 | 0.420 |

| b         | 0.230 | 0.255 | 0.280 |

| D         | 2.050 | 2.100 | 2.150 |

| D1        |       | 1.210 |       |

| D2        |       | 0.500 |       |

| E         | 1.500 | 1.550 | 1.600 |

| E1        |       | 1.060 |       |

| fD1       |       | 0.195 |       |

| fD2       |       | 0.195 |       |

| fE1       |       | 0.195 |       |

| fE2       |       | 0.295 |       |

DS12508 - Rev 1 page 6/13

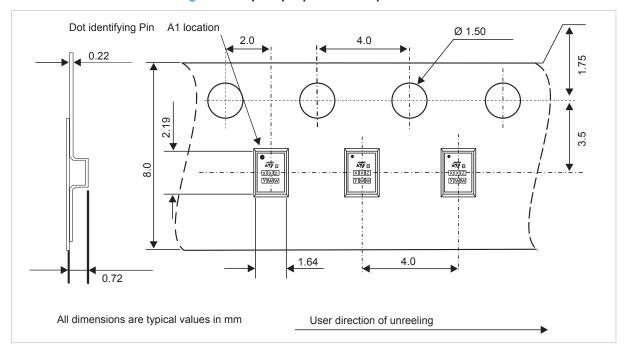

### 2.2 Flip-chip 6 bumps packing information

Figure 10. Marking

Figure 11. Flip Chip tape and reel specifications

DS12508 - Rev 1 page 7/13

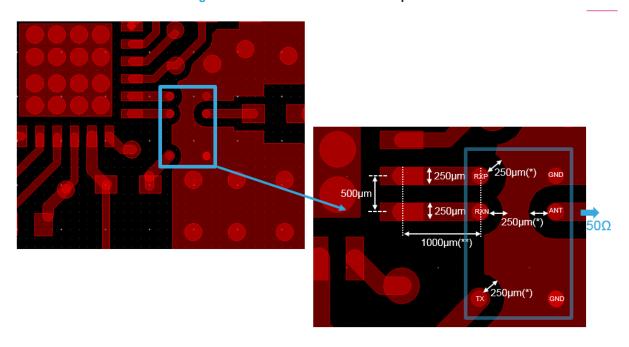

# 3 PCB assembly recommendations

### 3.1 Land pattern

Figure 12. Recommended balun land pattern

Note: (\*)Clearance 250 μm is needed to ensure good sensitivity.

(\*\*)1000 μm length between S2-LP & balun (between center QFN pads to center IPD pads).

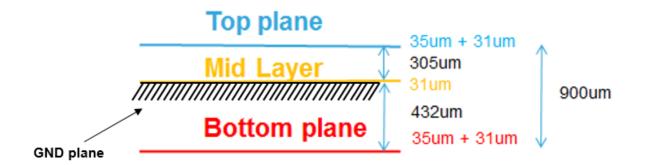

Figure 13. PCB stack-up recommendations

DS12508 - Rev 1 page 8/13

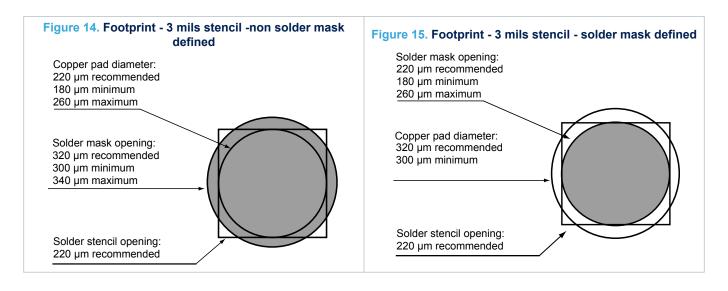

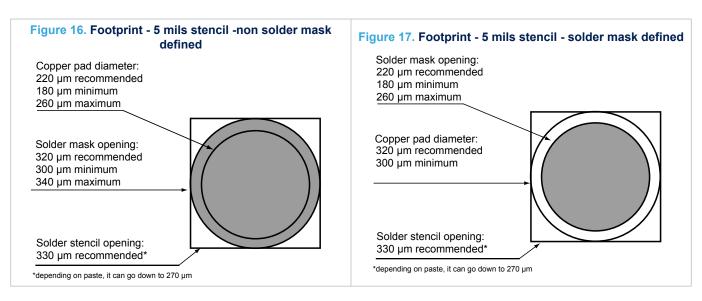

#### 3.2 Stencil opening design

#### 3.3 Solder paste

- 1. Halide-free flux qualification ROL0 according to ANSI/J-STD-004.

- 2. "No clean" solder paste is recommended.

- 3. Offers a high tack force to resist component movement during high speed.

- 4. Use solder paste with fine particles: powder particle size 20-38 μm.

DS12508 - Rev 1 page 9/13

#### 3.4 Placement

- 1. Manual positioning is not recommended.

- 2. It is recommended to use the lead recognition capabilities of the placement system, not the outline centering

- 3. Standard tolerance of ±0.05 mm is recommended.

- 4. 1.0 N placement force is recommended. Too much placement force can lead to squeezed out solder paste and cause solder joints to short. Too low placement force can lead to insufficient contact between package and solder paste that could cause open solder joints or badly centered packages.

- 5. To improve the package placement accuracy, a bottom side optical control should be performed with a high resolution tool.

- For assembly, a perfect supporting of the PCB (all the more on flexible PCB) is recommended during solder paste printing, pick and place and reflow soldering by using optimized tools.

#### 3.5 PCB design preference

- 1. To control the solder paste amount, the closed via is recommended instead of open vias.

- 2. The position of tracks and open vias in the solder area should be well balanced. A symmetrical layout is recommended, to avoid any tilt phenomena caused by asymmetrical solder paste due to solder flow away.

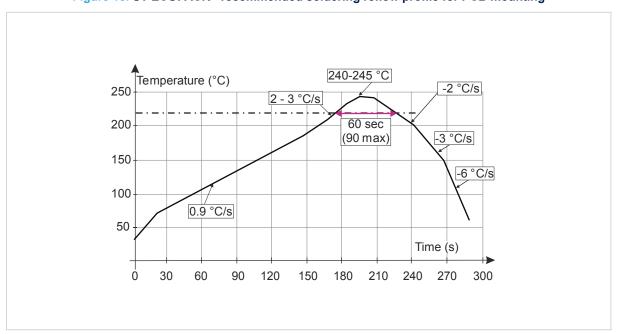

### 3.6 Reflow profile

Figure 18. ST ECOPACK® recommended soldering reflow profile for PCB mounting

Note: Minimize air convection currents in the reflow oven to avoid component movement.

Note: More information is available in the application note:

• AN2348 Flip-Chip: "Package description and recommendations for use"

DS12508 - Rev 1 page 10/13

# 4 Ordering information

Table 5. Ordering information

| Order code     | Marking | Package           | Weight | Base qty. | Delivery mode |

|----------------|---------|-------------------|--------|-----------|---------------|

| BALF-SPI2-02D3 | TN      | Flip-Chip 6 bumps | 3.4 mg | 5000      | Tape and reel |

DS12508 - Rev 1 page 11/13

# **Revision history**

**Table 6. Document revision history**

| Date        | Revision | Changes          |

|-------------|----------|------------------|

| 02-May-2018 | 1        | Initial release. |

DS12508 - Rev 1 page 12/13

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2018 STMicroelectronics - All rights reserved

DS12508 - Rev 1 page 13/13