#### BCM81724

# 8 x 56 Gb/s PAM-4 to 16 x 25 Gb/s NRZ Forward and Reverse Gearbox with 8 x 56 Gb/s PAM-4 Pass-Through Mode PHY

#### Overview

The Broadcom <sup>®</sup> BCM81724 is a single-chip 8 × 56 Gb/s to  $16 \times 25$  Gb/s NRZ forward and reverse gearbox with 8 × 56 Gb/s PAM-4 Pass-Through mode PHY. It supports both the PAM-4 and NRZ data formats. It supports Retimer, Forward, and Reverse Gearbox modes. It also supports 1G, 10G, 25G, 40G, 50G, 100G, 200G, and 400G line-card applications.

On-chip clock synthesis is performed by a low-cost 156.25-MHz reference clock through high-frequency, low-jitter phase-locked loops (PLLs).

The BCM81724 is fabricated in advanced low-power 16-nm CMOS technology.

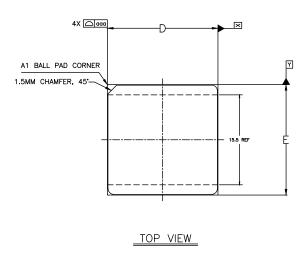

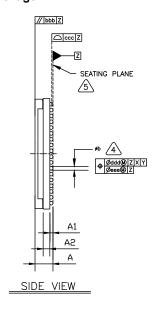

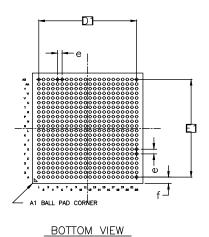

The BCM81724 is available in a 19 mm × 19 mm, 0.8-mm pitch, 484-ball BGA, RoHS-compliant package.

### **Applications**

- ASIC-to-module interface 16 × 25 Gb/s front-panel application

- ASIC-to-module interface 8 × 56 Gb/s front-panel application

- High-density 10G, 25G, 40G, 50G, 100G, 200G, and 400G front-panel line-card applications

#### **Features**

- Host-side interface: 30 dB (both NRZ and PAM-4 modes)

- Line-side interface:

- 35 dB (NRZ mode)

- 20 dB (PAM-4 mode)

- Chip-to-module (C2M) compliant

- Forward and Reverse Gearbox mode and Retimer mode

- Supports forward error correction (FEC)

- Supports CR mode in Reverse Gearbox mode

- Integrated AC-coupling capacitors on the system-side and line-side receivers

- Multiple standard and line rate support for both PAM-4 and NRZ

- Continuous auto-adaptive equalizer

- Line- and system-side loopbacks

- PRBS generator/error checker

- Eye monitoring per lane on the line side, accessed through MDIO

- SNR measurements per lane on the host side, accessed through MDIO

- Single low-cost REFCLK input

- Single-ended and differential recovered clock outputs

- Supports SGMII pass-through

- Interoperates with Broadcom ASIC and merchant switch silicon

- Low-power 16-nm CMOS design

- 19 mm × 19 mm BGA, 0.8-mm ball pitch package

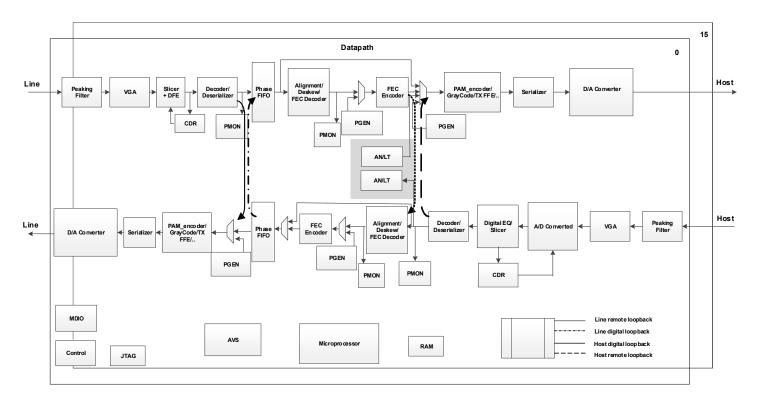

Host Line BCM81724 Lane 0 Lane 0 25G NRZ/ 25G NRZ/ PLL 56G PAM-4 56G PAM-4 Auto-Negotiation/Link Training Loop Loop FEC Encoder/Decoder back back **ASIC** Module Forward/Reverse Gearbox Lane 15 Lane 7 CDR 25G NRZ/ 25G NRZ/ 56G PAM-4 56G PAM-4 Power PRBS BERT **REFCLK JTAG** Control Supplies **MDIO** 156.25 MHz 0.8V 1.8V

Figure 1: BCM81724 Block Diagram for Reverse Gearbox and Retimer Modes

#### NOTE:

- a. Line-side remote loopback (line-side shallow loopback).

- b. Line-side digital loopback (acting host-side deep loopback).

- c. Host-side digital loopback (acting line-side deep loopback).

- d. Host-side remote loopback (host-side shallow loopback).

Loopbacks can be configured on a per-lane basis.

## **Table of Contents**

| Chapter 1: Functional Description                 | 4  |

|---------------------------------------------------|----|

| 1.1 Reverse, Retimer, and Forward Gearbox Modes   | 4  |

| 1.2 Device Functions                              | 10 |

| 1.2.1 Host-Side Interface                         | 11 |

| 1.2.2 Line-Side Interface                         | 11 |

| 1.3 Adaptive Voltage Scaling                      |    |

| 1.4 Loss of Signal and Signal Detector            |    |

| 1.5 Reset                                         |    |

| 1.6 Microcode Loading                             |    |

| Chapter 2: Ball Assignments and Descriptions      |    |

| 2.1 Functional Ball Descriptions                  |    |

| 2.2 Ballout Location Diagram                      |    |

| Chapter 3: Management Interfaces                  |    |

| 3.1 MDIO Access                                   |    |

| 3.2 MDIO (Slave) Interface                        |    |

| 3.2.1 MDIO Frame Format                           | 25 |

| Chapter 4: Register Summary                       | 26 |

| 4.1 Chip-Level Registers                          |    |

| 4.2 System-Side Registers                         |    |

| 4.3 Line-Side Registers                           | 48 |

| Chapter 5: Electrical Characteristics             | 72 |

| Chapter 6: Reference Clock                        | 77 |

| 6.1 Reference Clock Pins                          | 77 |

| 6.2 Reference Clock PCB Design Guidelines         | 78 |

| Chapter 7: Recovered Clock                        | 79 |

| Chapter 8: Decoupling Recommendations             | 81 |

| Chapter 9: Power-Sequencing Requirements          | 83 |

| Chapter 10: Mechanical Information                | 84 |

| 10.1 Package Outline Drawing                      | 84 |

| 10.2 Thermal Characteristics                      | 85 |

| 10.3 Electrostatic Discharge Handling Precautions | 85 |

| Chapter 11: Ordering Information                  | 86 |

| Revision History                                  | 87 |

| 81724-DS200; September 10, 2020                   | 87 |

### **Chapter 1: Functional Description**

For the BCM81724, lane 0 and lane 1 are grouped together and share the same PLL. Although they share one PLL, lane 0 and lane 1 can operate at different frequencies with each using different OSR settings (1, 2, or 4). For example, when lane 0 is set to 25G, lane 1 can be set only to 25G, 12.5G, or 6.25G. The same is true for lane 2/lane 3, lane 4/lane 5, and lane 6/lane 7 pairs.

### 1.1 Reverse, Retimer, and Forward Gearbox Modes

Table 1 describes the Reverse, Retimer, and Forward Gearbox modes of the BCM81724.

Table 1: Reverse, Retimer, and Forward Gearbox Operating Modes for 400G Slice (Host-Side 8 × 50G/8 × 25G to Line-Side 8 × 50G/16 × 25G)

| Operating Mode<br>(Front-Panel Ports) | Logical Function (Per Port) | Host-Side SerDes<br>Mode Per Port  | FEC on Host ASIC                 | Line-Side SerDes<br>Mode Per Port          | FEC Required for Line Side             | FEC Function Inside PHY                                                              |  |

|---------------------------------------|-----------------------------|------------------------------------|----------------------------------|--------------------------------------------|----------------------------------------|--------------------------------------------------------------------------------------|--|

| 1 port of 400GbE                      | Reverse gearbox             | 400GAUI-8 (8 × 50G)                | CL-119 FEC (RS-544 over 8 lanes) | 400GAUI-16 (16 × 25G)                      | CL-119 FEC (RS-544 over 16 lanes)      | Retiming (bit mux)                                                                   |  |

| 2 ports of 200GbE                     | Reverse gearbox             | 200GAUI-4 (4 × 50G)                | CL-119 FEC (RS-544 over 4 lanes) | 200GAUI-8 (8 × 25G)                        | CL-119 FEC (RS-544 over 8 lanes)       | Retiming (bit mux)                                                                   |  |

| 4 ports of 100GbE                     | Reverse gearbox             | 100GAUI-2 (2 × 50G)                | CL-91 FEC (RS-544 over 2 lanes)  | CAUI-4 and 100GAUI-4<br>(4 × 25G) (optics) | No FEC/CL-91 FEC<br>(RS-528)/CL-91 FEC | Terminate CL-91 FEC (RS-544) from host side, and generate no                         |  |

|                                       |                             |                                    |                                  | 100G-CR4 (4 × 25G)<br>(copper) with AN/LT  | (RS-544) over 4 lanes                  | FEC/CL-91 FEC (RS-528) for line side or retiming (bit mux)                           |  |

| 8 ports of 50G/C                      | Reverse gearbox             | 50GAUI-1 (50G)                     | CL-134 (RS-544                   | LAUI-2 (2 × 25G) (optics)                  | No FEC/FC-FEC/                         | Terminate CL-134 FEC from host side, and generate no FEC/FC-FEC/RS-528 for line side |  |

|                                       | (50G Consortium)            |                                    | over 1 lane)                     | 50G-CR2 (2 × 25G)<br>(copper) with AN/LT   | RS-528 over 2 lanes                    |                                                                                      |  |

| 4 ports of 40GbE                      | Reverse gearbox             | XLPPI-2 (22 × 20G)                 | (No FEC)                         | XLPPI-4 (4 × 10G) (optics)                 | (No FEC)                               | Retiming (bit mux)                                                                   |  |

|                                       |                             |                                    |                                  | 40G-CR4 (4 × 10G)<br>(copper) with AN/LT   |                                        |                                                                                      |  |

| 1 port of 400GbE                      | Retimer                     | 400GAUI-8 (8 × 50G)                | CL-119 FEC (RS-544 over 8 lanes) | 400GAUI-8 (8 × 50G)<br>(optics)            | CL-119 FEC (RS-544 over 8 lanes)       | Retiming                                                                             |  |

|                                       |                             | 400G (8 × 50G) (copper) with AN/LT |                                  |                                            |                                        |                                                                                      |  |

Table 1: Reverse, Retimer, and Forward Gearbox Operating Modes for 400G Slice (Host-Side 8 × 50G/8 × 25G to Line-Side 8 × 50G/16 × 25G) (Continued)

| Operating Mode<br>(Front-Panel Ports) |                  | Host-Side SerDes<br>Mode Per Port | FEC on Host ASIC                       | Line-Side SerDes<br>Mode Per Port          | FEC Required for Line Side             | FEC Function Inside PHY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|---------------------------------------|------------------|-----------------------------------|----------------------------------------|--------------------------------------------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 2 ports of 200GbE                     | Retimer          | 200GAUI-4 (4 × 50G)               | CL-119 FEC (RS-544<br>over 4 lanes)    | 200GAUI-4 (4 × 50G)<br>(optics)            | CL-119 FEC (RS-544 over 4 lanes)       | Retiming or                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|                                       |                  |                                   |                                        | 200G (4 × 50G) (copper) with AN/LT         |                                        | RS544 FEC terminate and regenerate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| 1 port of 200GbE                      | Retimer          | 200GAUI-8 (8 × 25G)               | CL-119 FEC (RS-544<br>over 8 lanes)    | 200GAUI-8 (8 × 25G)<br>(optics)            | CL-119 FEC (RS-544 over 8 lanes)       | Retiming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 4 ports of 100GbE                     | Retimer          | 100GAUI-2 (2 × 50G)               | CL-91 FEC (RS-544<br>over 2 lanes)     | 100GAUI-2 (2 × 50G)<br>(optics)            | CL-91 FEC (RS-544 over 2 lanes)        | Retiming or                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|                                       |                  |                                   |                                        | 100G (2 × 50G) (copper) with AN/LT         |                                        | RS544 FEC terminate and regenerate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| 2 ports of 100GbE                     | Retimer          | CAUI-4 and 100GAUI-4<br>(4 × 25G) | No FEC/CL-91 FEC<br>(RS-528)/CL-91 FEC | CAUI-4 and 100GAUI-4<br>(4 × 25G) (optics) | No FEC/CL-91 FEC<br>(RS-528)/CL-91 FEC | Retiming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|                                       |                  |                                   | (RS-544), over 4 lanes                 | 100G (4 × 25G) (copper) with AN/LT         | (RS-544) over 4 lanes                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 2 ports of 40GbE                      | Retimer          | XLPPI-4 (4 × 10G)                 | (No FEC)                               | XLPPI-4 (4 × 10G) (optics)                 | (No FEC)                               | Retiming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|                                       |                  |                                   |                                        | 40G (4 × 10G) (copper) with AN/LT          |                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 8 ports of 50GbE                      | Retimer          | 50GAUI-1 (50G)                    | CL-134 (RS-544 over                    | 50GAUI-1 (optics)                          | CL-134 (RS-544 over                    | Retiming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|                                       |                  |                                   | 1 lane)                                | 50G (copper) with AN/LT                    | vith AN/LT 1 lane)                     | or<br>RS544 FEC terminate and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|                                       |                  |                                   |                                        |                                            |                                        | regenerate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| 4 ports of 50G/C                      | Retimer          | LAUI-2 (2 × 25G)                  | No FEC/FC-FEC/RS-                      | LAUI-2 (2 × 25G) (optics)                  | No FEC/FC-FEC/                         | Retiming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|                                       | (50G Consortium) |                                   | FEC over 2 lanes                       | 50G (2 × 25G) (copper)<br>with AN/LT       | RS-FEC over 2 lanes                    | , and the second |  |

| 8 ports of 25GbE                      | Retimer (IEEE    | 25GAUI (25G)                      | No FEC/FC-FEC/RS-                      | 25GAUI (optics)                            | No FEC/FC-FEC/                         | Retiming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|                                       | and Consortium)  |                                   | FEC over 1 lane                        | 25G (copper) with AN/LT                    | RS-FEC over 1 lane                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 8 ports of 10GbE                      | Retimer          | SFI (10G)                         | (No FEC)                               | 10G SFI (optics)                           | (No FEC)                               | Retiming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|                                       |                  |                                   |                                        | 10G SFI (copper)                           |                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 1 port of 400GbE                      | Forward gearbox  | 400GAUI-16 (16 × 25G)             | CL-119 FEC (RS-544 over 16 lanes)      | 400GAUI-8 (8 × 50G)                        | CL-119 FEC (RS-544 over 8 lanes)       | Retiming (bit mux)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| 2 ports of 200GbE                     | Forward gearbox  | 200GAUI-8 (8 × 25G)               | CL-119 FEC (RS-544 over 8 lanes)       | 200GAUI-4 (4 × 50G)                        | CL-119 FEC (RS-544 over 4 lanes)       | Retiming (bit mux)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

Table 1: Reverse, Retimer, and Forward Gearbox Operating Modes for 400G Slice (Host-Side 8 × 50G/8 × 25G to Line-Side 8 × 50G/16 × 25G) (Continued)

| Operating Mode (Front-Panel Ports) | •                                | Host-Side SerDes<br>Mode Per Port          | FEC on Host ASIC                                                | Line-Side SerDes<br>Mode Per Port                            | FEC Required for Line Side         | FEC Function Inside PHY                                                                                                 |

|------------------------------------|----------------------------------|--------------------------------------------|-----------------------------------------------------------------|--------------------------------------------------------------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| 4 ports of 100GbE                  | 3                                | CAUI-4 and 100GAUI-4<br>(4 × 25G) (optics) | No FEC/CL-91 FEC<br>(RS-528)/CL-91 FEC<br>(RS-544) over 4 lanes | 100GAUI-2 (2 × 50G)<br>100G (4 × 25G) (copper)<br>with AN/LT | CL-91 FEC (RS-544<br>over 2 lanes) | Terminate CL-91 FEC (RS-544) from host side, and generate no FEC/CL-91 FEC (RS-528) for line side or retiming (bit mux) |

| -                                  | Forward gearbox (50G Consortium) | LAUI-2 (2 × 25G)<br>(optics)               | No FEC/FC-FEC/<br>RS-528 over 2 lanes                           | 50GAUI-1 (50G)<br>50G (2 × 25G) (copper)<br>with AN/LT       | CL-134 (RS-544<br>over 1 lane)     | Terminate CL-134 FEC from host side, and generate no FEC/FC-FEC/RS-528 for line side                                    |

| 4 ports of 40GbE                   | Forward gearbox                  | XLPPI-4 (4 × 10G)<br>(optics)              | (No FEC)                                                        | XLPPI-2 (22 × 20G)<br>40G (4 × 10G) (copper)<br>with AN/LT   | (No FEC)                           | Retiming (bit mux)                                                                                                      |

Table 2 and Table 3 show the SerDes mapping of the BCM81724 working as Reverse Gearbox, Retimer, and Gearbox modes.

Table 2: SerDes Mapping, Reverse Gearbox Mode

| Operating Mode<br>(Front-Panel Ports) | Logical Function (Per Port)    | Port Number  | Host-Side<br>SerDes Lanes | Line-Side<br>SerDes Lanes |

|---------------------------------------|--------------------------------|--------------|---------------------------|---------------------------|

| 1 port of 400GbE                      | Reverse gearbox (PAM-4 to NRZ) | Port 1       | H0 to H7                  | L0 to L15                 |

| 2 ports of 200GbE                     | Reverse gearbox (PAM-4 to NRZ) | Port 1       | H0 to H3                  | L0 to L7                  |

|                                       |                                | Port 2       | H4 to H7                  | L8 to L15                 |

| 4 ports of 100GbE                     | Reverse gearbox (PAM-4 to NRZ) | Port 1       | H0 to H1                  | L0 to L3                  |

|                                       |                                | Port 2       | H2 to H3                  | L4 to L7                  |

|                                       |                                | Port 3       | H4 to H5                  | L8 to L11                 |

|                                       |                                | Port 4       | H6 to H7                  | L12 to L15                |

| 8 ports of 50G/C                      | Reverse gearbox (PAM-4 to NRZ) | Port 1       | H0                        | L0 to L1                  |

|                                       |                                | Port 2       | H1                        | L2 to L3                  |

|                                       |                                | Port 3       | H2                        | L4 to L5                  |

|                                       |                                | Port 4       | H3                        | L6 to L7                  |

|                                       |                                | Port 5       | H4                        | L8 to L9                  |

|                                       |                                | Port 6       | H5                        | L10 to L11                |

|                                       |                                | Port 7       | H6                        | L12 to L13                |

|                                       |                                | Port 8       | H7                        | L14 to L15                |

| 4 ports of 40GbE                      | Reverse gearbox (NRZ to NRZ)   | Port 1       | H0 to H1                  | L0 to L3                  |

|                                       |                                | Port 2       | H2 to H3                  | L4 to L7                  |

|                                       |                                | Port 3       | H4 to H5                  | L8 to L11                 |

|                                       |                                | Port 4       | H6 to H7                  | L12 to L15                |

| 1 port of 400GbE                      | Retimer (PAM-4 to PAM-4)       | Port 1       | H0 to H7                  | L8 to L15                 |

| 2 ports of 200GbE                     | Retimer (PAM-4 to PAM-4)       | Port 1       | H0 to H3                  | L0 to L3                  |

|                                       |                                | Port 2       | H4 to H7                  | L8 to L11                 |

| 1 port of 200GbE                      | Retimer (NRZ to NRZ)           | Port 1       | H0 to H7                  | L0 to L3 and L8 to L11    |

| 4 ports of 100GbE                     | Retimer (PAM-4 to PAM-4)       | Port 1       | H0 to H1                  | L0 to L1                  |

|                                       |                                | Port 2       | H2 to H3                  | L2 to L3                  |

|                                       |                                | Port 3       | H4 to H5                  | L8 to L9                  |

|                                       |                                | Port 4       | H6 to H7                  | L10 to L11                |

| 2 ports of 100GbE                     | Retimer (NRZ to NRZ)           | Port 1       | H0 to H3                  | L0 to L3                  |

|                                       |                                | Port 2       | H4 to H7                  | L8 to L11                 |

| 2 ports of 40GbE                      | Retimer (NRZ to NRZ)           | Port 1       | H0 to H3                  | L0 to L3                  |

|                                       |                                | Port 2       | H4 to H7                  | L8 to L11                 |

| 8 ports of 50GbE                      | Retimer (PAM-4 to PAM-4)       | Ports 1 to 8 | H0 to H7                  | L0 to L3 and L8 to L11    |

| 4 ports of 50G/C                      | Retimer (NRZ to NRZ)           | Port 1       | H0 to H1                  | L0 to L1                  |

|                                       |                                | Port 2       | H2 to H3                  | L2 to L3                  |

|                                       |                                | Port 3       | H4 to H5                  | L8 to L9                  |

|                                       |                                | Port 4       | H6 to H7                  | L10 to L11                |

| 8 ports of 25GbE                      | Retimer (NRZ to NRZ)           | Ports 1 to 8 | H0 to H7                  | L0 to L3 and L8 to L11    |

| 8 ports of 10GbE                      | Retimer (NRZ to NRZ)           | Ports 1 to 8 | H0 to H7                  | L0 to L3 and L8 to L11    |

Table 3: SerDes Mapping, Forward Gearbox Mode

| Operating Mode<br>(Front-Panel Ports) | Logical Function (Per Port)    | Port Number  | Host-Side<br>SerDes Lanes | Line-Side<br>SerDes Lanes |

|---------------------------------------|--------------------------------|--------------|---------------------------|---------------------------|

| 1 port of 400GbE                      | Forward gearbox (NRZ to PAM-4) | Port 1       | L0 to L15                 | H0 to H7                  |

| 2 ports of 200GbE                     | Forward gearbox (NRZ to PAM-4) | Port 1       | L0 to L7                  | H0 to H3                  |

|                                       |                                | Port 2       | L8 to L15                 | H4 to H7                  |

| 4 ports of 100GbE                     | Forward gearbox (NRZ to PAM-4) | Port 1       | L0 to L3                  | H0 to H1                  |

|                                       |                                | Port 2       | L4 to L7                  | H2 to H3                  |

|                                       |                                | Port 3       | L8 to L11                 | H4 to H5                  |

|                                       |                                | Port 4       | L12 to L15                | H6 to H7                  |

| 8 ports of 50GbE                      | Forward gearbox (NRZ to PAM-4) | Port 1       | L0 to L1                  | H0                        |

|                                       |                                | Port 2       | L2 to L3                  | H1                        |

|                                       |                                | Port 3       | L4 to L5                  | H2                        |

|                                       |                                | Port 4       | L6 to L7                  | H3                        |

|                                       |                                | Port 5       | L8 to L9                  | H4                        |

|                                       |                                | Port 6       | L10 to L11                | H5                        |

|                                       |                                | Port 7       | L12 to L13                | H6                        |

|                                       |                                | Port 8       | L14 to L15                | H7                        |

| 4 ports of 40GbE                      | Forward gearbox (NRZ to PAM-4) | Port 1       | L0 to L3                  | H0 to H1                  |

|                                       |                                | Port 2       | L4 to L7                  | H2 to H3                  |

|                                       |                                | Port 3       | L8 to L11                 | H4 to H5                  |

|                                       |                                | Port 4       | L12 to L15                | H6 to H7                  |

| 1 port of 400GbE                      | Retimer (PAM-4 to PAM-4)       | Port 1       | H0 to H7                  | L8 to L15                 |

| 2 ports of 200GbE                     | Retimer (PAM-4 to PAM-4)       | Port 1       | L0 to L3                  | H0 to H3                  |

|                                       |                                | Port 2       | L8 to L11                 | H4 to H7                  |

| 1 port of 200GbE                      | Retimer (NRZ to NRZ)           | Port 1       | L0 to L3 and L8 to L11    | H0 to H7                  |

| 4 ports of 100GbE                     | Retimer (PAM-4 to PAM-4)       | Port 1       | L0 to L1                  | H0 to H1                  |

|                                       |                                | Port 2       | L2 to L3                  | H2 to H3                  |

|                                       |                                | Port 3       | L8 to L9                  | H4 to H5                  |

|                                       |                                | Port 4       | L10 to L11                | H6 to H7                  |

| 2 ports of 100GbE                     | Retimer (NRZ to NRZ)           | Port 1       | L0 to L3                  | H0 to H3                  |

|                                       |                                | Port 2       | L8 to L11                 | H4 to H7                  |

| 2 ports of 40GbE                      | Retimer (NRZ to NRZ)           | Port 1       | L0 to L3                  | H0 to H3                  |

|                                       |                                | Port 2       | L8 to L11                 | H4 to H7                  |

| 8 ports of 50GbE                      | Retimer (PAM-4 to PAM-4)       | Ports 1 to 8 | L0 to L3 and L8 to L11    | H0 to H7                  |

| 4 ports of 50G/C                      | Retimer (NRZ to NRZ)           | Port 1       | L0 to L1                  | H0 to H1                  |

|                                       |                                | Port 2       | L2 to L3                  | H2 to H3                  |

|                                       |                                | Port 3       | L8 to L9                  | H4 to H5                  |

|                                       |                                | Port 4       | L10 to L11                | H6 to H7                  |

| 8 ports of 25GbE                      | Retimer (NRZ to NRZ)           | Ports 1 to 8 | L0 to L3 and L8 to L11    | H0 to H7                  |

| 8 ports of 10GbE                      | Retimer (NRZ to NRZ)           | Ports 1 to 8 | L0 to L3 and L8 to L11    | H0 to H7                  |

Figure 2 shows the detailed block diagram of the BCM81724.

Figure 2: Detailed Block Diagram

### 1.2 Device Functions

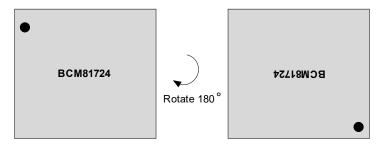

The BCM81724 can function as a reverse gearbox or a forward gearbox. To operate in the Reverse Gearbox mode, use the device as is. To operate in the Forward Gearbox mode, the chip must be physically rotated by 180 degrees as shown in Figure 3.

Figure 3: Reverse Gearbox Mode to Forward Gearbox Mode

Reverse Gearbox Mode

Forward Gearbox Mode

In the BCM81724, lane 0 and lane 1 are grouped together and share the same PLL. Although they share one PLL, lane 0 and lane 1 can operate at different frequencies with each using different OSR settings (1, 2, or 4). For example, when lane 0 is set to 25G, lane 1 can be set only to 25G, 12.5G, or 6.25G. The same is true for the lane 2/lane 3, lane 4/lane 5, and lane 6/lane 7 pairs.

In all operating modes, the transmitter clock frequency is locked to the opposite side recovered clock frequency. For example, the system-side transmitter clock frequency is locked to the line-side recovered clock frequency, and the line-side transmitter clock frequency is locked to the system-side recovered clock frequency.

**NOTE:** The lane-swap feature is not available on the BCM81724. However, P/N polarity swaps are available on both the system-side and line-side transmitter and receiver paths to help with PCB routing.

#### 1.2.1 Host-Side Interface

The host-side interface receiver is a high-performance, ADC-based digital equalizer, which includes an analog peaking filter (PF) and a variable gain amplifier (VGA) in analog front end as well as a high-performance analog-to-digital converter (ADC) with digital equalizer of feed-forward equalizer (FFE) and a clock and data recovery (CDR) circuitry.

The analog PF, enabled by a programmable continuous-time linear equalizer (CTLE), provides first-order equalization by boosting the high-frequency content to compensate for the intersymbol interference (ISI) on the incoming data. The peak of the peaking filter can be adjusted by the registers for various backplane channel characteristics. After the analog PF, the signal is further enhanced through a VGA, and the gain is automatically controlled by a gain control loop for best ADC performance.

A high-performance ADC is implemented after the PF and VGA stages. The incoming data is sampled at baud rate, and the digitalized samples are subsequently postprocessed by the digital equalizer (EQ) prior to slicing. The digital equalizer has a multiple-taps baud rate FFE, which equalizes the sampled signal. The equalizer is continuously adapted to the incoming signal variation with the least mean squared (LMS) algorithm.

The timing recovery block recovers both the phase and frequency of the incoming data stream. Further, it determines the optimal sampling phase for obtaining the best-recovered signal after equalization. Data is determined at the slicer with optimal timing by a fully adapted timing recovery block. All RX EQ and analog parameters are automatically configured and adapted for best CDR and EQ operation using a combination of hardware and firmware running in a microcontroller.

There is an integrated on-die AC-coupling capacitor on the host-side receiver (see Section 2.1, Functional Ball Descriptions, for the common-mode and maximum peaking voltage restrictions).

The host-side interface can support backplane channels with 30-dB insertion loss (in Nyquist frequency). The transmitters are based on a high-resolution digital-to-analog converter (DAC) and are compliant to the CEI-28G/56G-LR specifications. The TX equalization is provided by a conventional multiple-tap TXFIR structure.

Host-side interfaces have a pseudorandom bit sequence (PRBS) generator as well as checker capability.

#### 1.2.2 Line-Side Interface

The analog PF, enabled by a programmable continuous-time linear equalizer (CTLE), provides first-order equalization by boosting the high-frequency content to compensate for the intersymbol interference (ISI) on the incoming data. The peak of the peaking filter can be adjusted by the registers for various backplane channel characteristics. After the analog PF, the signal is further enhanced through a VGA, and the gain is automatically controlled by a gain control loop for best ADC performance.

A multitap decision feedback equalizer (DFE)/timing recovery is implemented after the PF and VGA stages, where it continuously adapts to the incoming signal with the least mean squared (LMS) algorithm, and together with a CDR block, recover both the phase and frequency of the incoming data stream and determine the optimal sampling phase for obtaining the best-recovered signal after equalization.

The line-side interface receiver is an analog equalizer, including a PF, a VGA, and a multiple-tap decision feedback equalizer (DFE) with a CDR circuit synchronizing the receiver with the incoming data stream.

There is an integrated on-die AC-coupling capacitor on the line-side receiver (see Section 2.1, Functional Ball Descriptions, for the common-mode and maximum peaking voltage restrictions). The line-side interface is compliant to the CEI-28G/56G-LR specifications and can support long-reach (LR) 35-dB insertion loss (at Nyquist frequencies) in NRZ mode and 20-dB insertion loss (at Nyquist frequencies) in PAM-4 mode.

The line-side interface transmitters are based on a high-resolution digital-to-analog converter (DAC) and are compliant to the CEI-28G/56G-LR specifications. The TX equalization is provided by a conventional multiple-tap TXFIR structure.

Line-side interfaces have a pseudorandom bit sequence (PRBS) generator as well as checker capability.

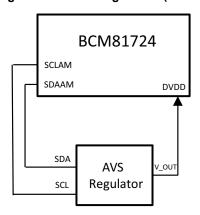

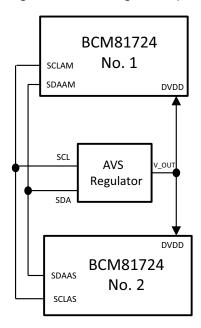

### 1.3 Adaptive Voltage Scaling

The BCM81724 implements Broadcom Serial Control (BSC) interface to achieve lower digital power consumption through adaptive voltage scaling (AVS). The BSC master interface is compatible with the I<sup>2</sup>C standard. The hardware configuration (as shown in Figure 4) is realized by connecting an AVS voltage regulator, with a slave I<sup>2</sup>C-compatible port, to the BCM81724 master BSC pins (SCLAM, SDAAM), and by connecting the output of the AVS regulator to the BCM81724 DVDD power rail. The AVS process is controlled automatically by the firmware, where the AVS algorithm is part of firmware and, when enabled, the firmware controls the AVS regulator's output voltage to adapt to the lowest DVDD voltage possible, at chip live operating condition, while still ensuring proper chip operation. The lowest digital power consumption is achieved by maintaining the lowest DVDD voltage possible at live chip operating condition.

**NOTE:** The BSC is I<sup>2</sup>C compliant and supports both standard I<sup>2</sup>C mode (100 kHz) and fast I<sup>2</sup>C mode (400 kHz).

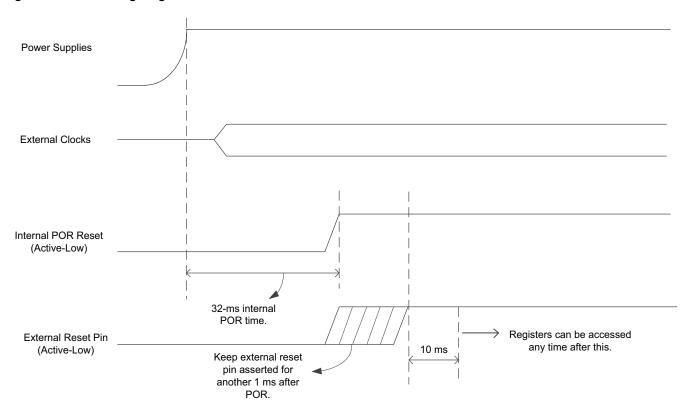

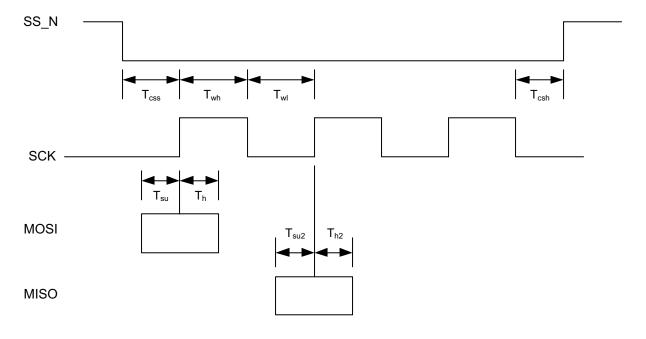

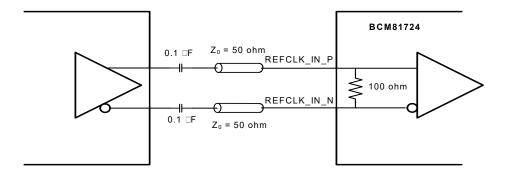

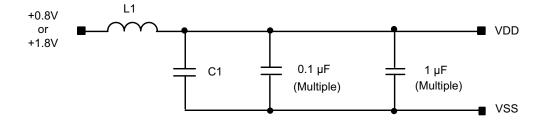

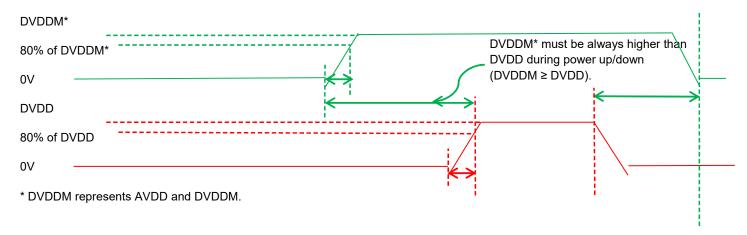

Figure 4: AVS Configuration (One Regulator for One Package)