# 2.5V to 4.5V, 0.6A 1ch

## Synchronous Buck Converter Integrated FET

#### **BD9161FVM**

#### General Description

ROHM's high efficiency step-down switching regulator BD9161FVM is a power supply designed to produce 1.2volts (low voltage) from 3.3volts power supply line. Offers high efficiency with our original pulse skip control technology and synchronous rectifier. Employs a current mode control system to provide faster transient response to sudden change in load.

#### Features

- Offers fast transient response with current mode PWM control system.

- Offers highly efficiency for all load range with synchronous rectifier (Nch/Pch FET)

- Incorporates 100% Duty function.

- Incorporates soft-start function.

- Incorporates thermal protection and ULVO functions.

- Incorporates short-current protection circuit with time delay function.

- Incorporates shutdown function Icc=0µA (Typ.)

#### Kev Specifications

| Input voltage range:         | 2.5V to 4.5V   |

|------------------------------|----------------|

| Output voltage range:        | 1.0V to 3.3V   |

| Output current:              | 0.6A(Max.)     |

| Switching frequency:         | 1MHz(Typ.)     |

| Pch FET ON resistance:       | 0.35Ω (Typ.)   |

| Nch FET ON resistance:       | 0.37Ω (Typ.)   |

| Standby current:             | 0μA (Typ.)     |

| Operating temperature range: | -25°C to +85°C |

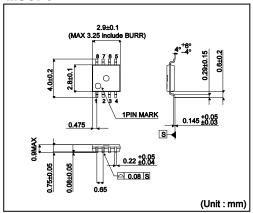

#### Package

MSOP8: 2.90 mm x 4.00 mm x 0.83 mm

#### Applications

Power supply for HDD, DVD and for LSI of CPU, ASIC

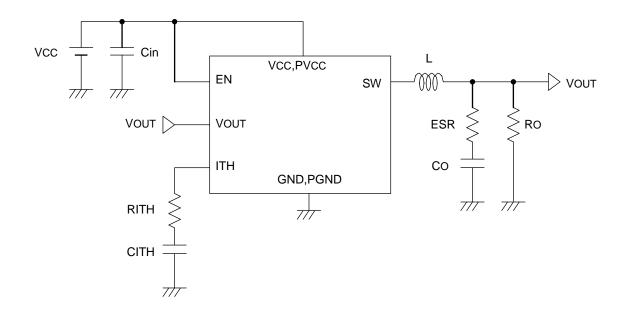

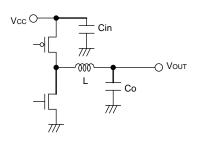

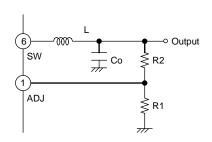

#### Typical Application Circuit

Fig.1 Typical application circuit

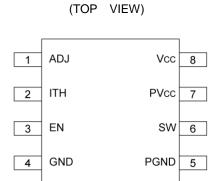

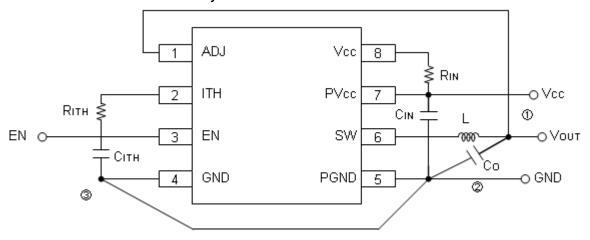

#### ●Pin Configuration

Fig.2 Pin Configuration

#### **●**Pin Description

|         | T        | T                                                       |  |  |  |

|---------|----------|---------------------------------------------------------|--|--|--|

| Pin No. | Pin name | PIN function                                            |  |  |  |

| 1       | ADJ      | Output voltage Feedback pin (Adjustable)                |  |  |  |

| 2       | ITH      | GmAmp output pin/Connected phase compensation capacitor |  |  |  |

| 3       | EN       | Enable pin (Active High)                                |  |  |  |

| 4       | GND      | Ground                                                  |  |  |  |

| 5       | PGND     | Nch FET source pin                                      |  |  |  |

| 6       | SW       | Pch/Nch FET drain output pin                            |  |  |  |

| 7       | PVcc     | Pch FET source pin                                      |  |  |  |

| 8       | Vcc      | VCC power supply input pin                              |  |  |  |

|         |          |                                                         |  |  |  |

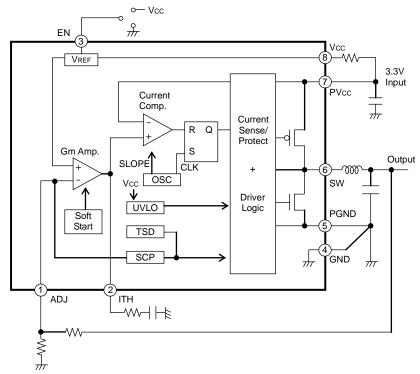

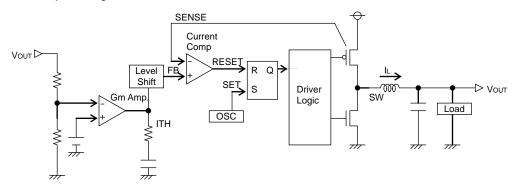

#### ●Block Diagram

Fig.3 Block Diagram

● Absolute Maximum Ratings(Ta=25°C)

| Parameter                   | Symbol | Rating        | Unit |

|-----------------------------|--------|---------------|------|

| VCC voltage                 | Vcc    | -0.3 to +7 *1 | V    |

| PVCC voltage                | PVcc   | -0.3 to +7 *1 | V    |

| EN Voltage                  | EN     | -0.3 to +7    | V    |

| SW, ITH Voltage             | SW,ITH | -0.3 to +7    | V    |

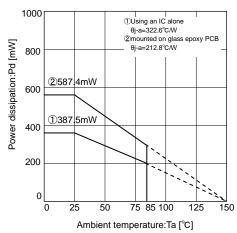

| Power Dissipation 1         | Pd1    | 387.5*2       | mW   |

| Power Dissipation 2         | Pd2    | 587.4*3       | mW   |

| Operating temperature range | Topr   | -25 to +85    | °C   |

| Storage temperature range   | Tstg   | -55 to +150   | °C   |

| EN voltage                  | Tjmax  | +150          | °C   |

<sup>\*1</sup> Pd should not be exceeded.

**Operating Ratings**(Ta=25°C)

| Dorometer                      | Cumbal |      | l limit |      |      |  |

|--------------------------------|--------|------|---------|------|------|--|

| Parameter                      | Symbol | Min. | Тур.    | Max. | Unit |  |

| VCC voltage                    | VCC*4  | 2.5  | 3.3     | 4.5  | V    |  |

| PVCC voltage                   | PVCC*4 | 2.5  | 3.3     | 4.5  | V    |  |

| EN voltage                     | EN     | 0    | -       | Vcc  | V    |  |

| Output Voltage Setting Range   | SW,ITH | 1.0  | -       | 3.3  | V    |  |

| SW, ITH average output current | Isw*4  | ı    | -       | 0.6  | Α    |  |

<sup>\*4</sup> Pd should not be exceeded.

#### Electrical Characteristics

⊚(Ta=25°C, Vcc=PVcc=3.3V, EN=Vcc, unless otherwise specified.)

| Parameter                                 | Cymbol | Limits |      |       | Unit | Conditions       |

|-------------------------------------------|--------|--------|------|-------|------|------------------|

| Parameter                                 | Symbol | Min.   | Тур. | Max.  | Unit | Conditions       |

| Standby current                           | ISTB   | -      | 0    | 10    | μA   | EN=GND           |

| Bias current                              | Icc    | -      | 200  | 400   | μA   |                  |

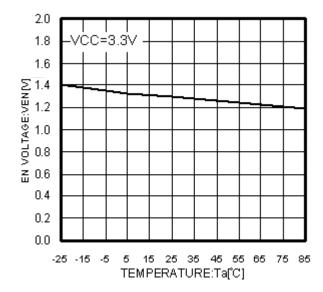

| EN Low voltage                            | VENL   | -      | GND  | 0.8   | V    | Standby mode     |

| EN High voltage                           | VENH   | 2.0    | Vcc  | -     | V    | Active mode      |

| EN input current                          | IEN    | -      | 1    | 10    | μA   | VEN=3.3V         |

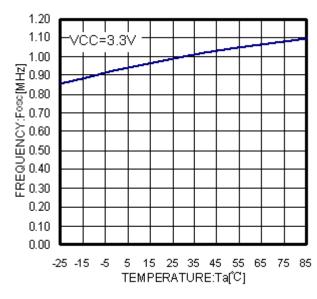

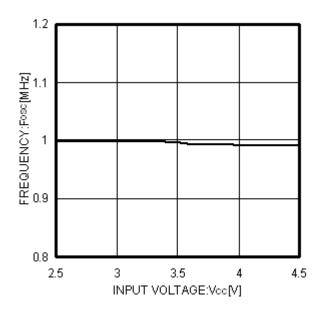

| Oscillation frequency                     | Fosc   | 0.8    | 1    | 1.2   | MHz  |                  |

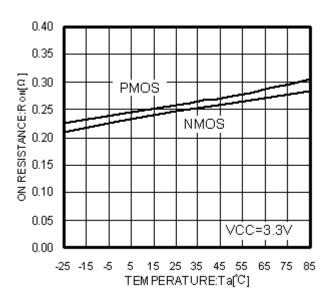

| Pch FET ON resistance                     | RONP   | -      | 0.35 | 0.6   | Ω    | PVcc=3.3V        |

| Nch FET ON resistance                     | Ronn   | -      | 0.37 | 0.68  | Ω    | PVcc=3.3V        |

| Output voltage                            | Vout   | 0.784  | 0.8  | 0.816 | V    |                  |

| ITH sink current                          | ITHSI  | 10     | 20   | -     | μA   | Vout =H          |

| ITH source current                        | Ітнѕо  | 10     | 20   | -     | μA   | Vout =L          |

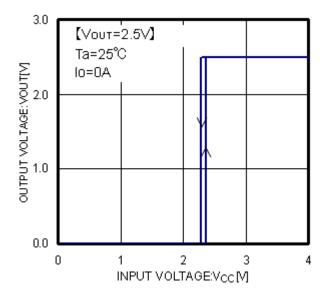

| UVLO threshold voltage                    | VUVLO1 | 2.2    | 2.3  | 2.4   | V    | Vcc=H→L          |

| UVLO hysteresis voltage                   | VUVLO2 | 2.22   | 2.35 | 2.5   | V    | Vcc=L→H          |

| Soft start time                           | Tss    | 0.5    | 1    | 2     | ms   |                  |

| Timer latch time                          | TLATCH | 1      | 2    | 3     | ms   | SCP/TSD operated |

| Output Short circuit<br>Threshold Voltage | VSCP   | -      | 0.4  | 0.56  | V    | Vout =H→L        |

<sup>\*2</sup> Derating in done 3.1mW/°C for temperatures above Ta=25°C.

<sup>\*3</sup> Derating in done 4.7mW/°C for temperatures above Ta=25°C, Mounted on 70mm×70mm×1.6mm Glass Epoxy PCB.

#### **●**Typical Performance Curves

Fig.4 Vcc-Vout

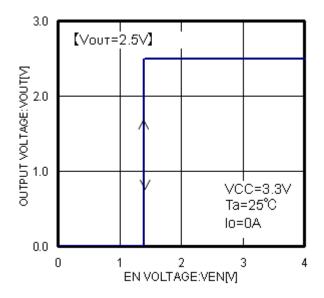

Fig.5 Ven-Vout

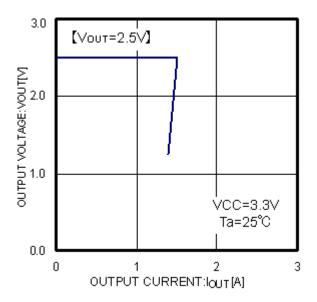

Fig.6 lout-Vout

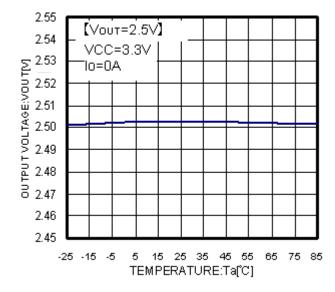

Fig.7 Ta-Vout

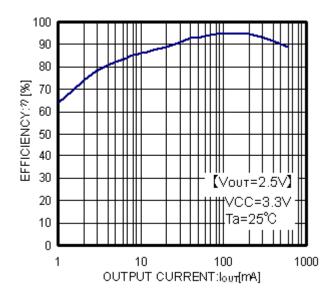

Fig.8 Efficiency

Fig.9 Ta - Fosc

Fig.10 Ta-VEN

Fig.11 Ta-Icc

Fig.12 Vcc-Fosc

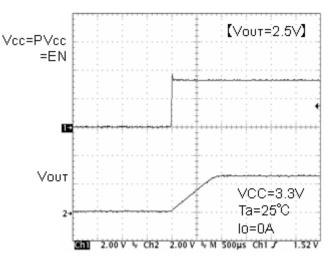

Fig.13 Soft start waveform

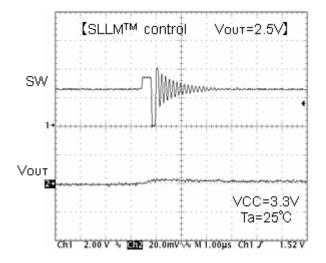

Fig.14 SW waveform Io=10mA

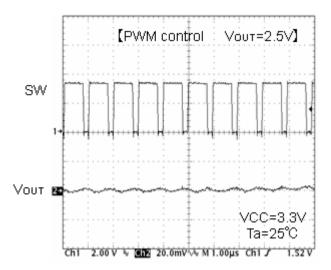

Fig.15 SW waveform Io=500mA

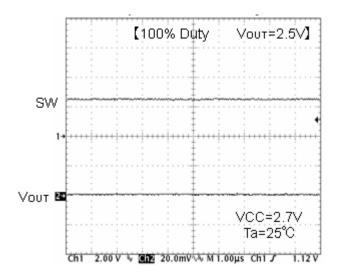

Fig. 16 SW waveform Io=600mA

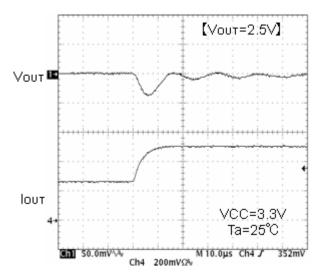

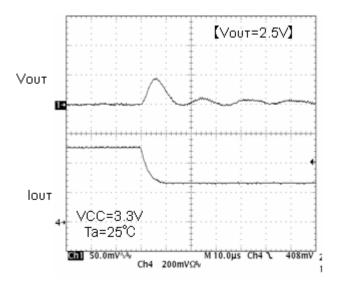

Fig. 17 Transient response Io=250→500mA(10µs)

Fig.18 Transient response Io=500→250mA(10µs)

#### Application Information

#### Operation

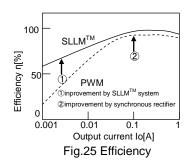

BD9161FVM is a synchronous rectifying step-down switching regulator that achieves faster transient response by employing current mode PWM control system. It utilizes switching operation in PWM (Pulse Width Modulation) mode for heavier load, while it utilizes SLLM<sup>TM</sup> (Simple Light Load Mode) operation for lighter load to improve efficiency.

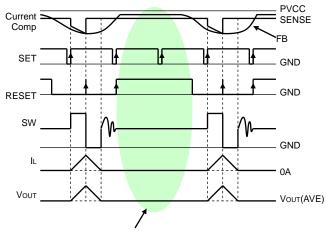

#### OCurrent mode PWM control

Synthesizes a PWM control signal with a inductor current feedback loop added to the voltage feedback.

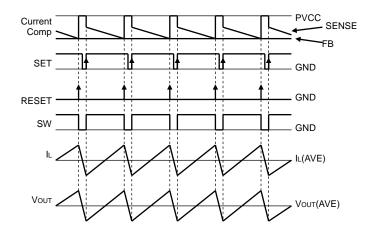

• PWM (Pulse Width Modulation) control

The oscillation frequency for PWM is 1 MHz. SET signal form OSC turns ON a P-channel MOS FET (while a N-channel MOS FET is turned OFF), and an inductor current  $I_L$  increases. The current comparator (Current Comp) receives two signals, a current feedback control signal (SENSE: Voltage converted from  $I_L$ ) and a voltage feedback control signal (FB), and issues a RESET signal if both input signals are identical to each other, and turns OFF the P-channel MOS FET (while a N-channel MOS FET is turned ON) for the rest of the fixed period. The PWM control repeats this operation.

#### SLLM<sup>TM</sup> (Simple Light Load Mode) control

When the control mode is shifted from PWM for heavier load to the one for lighter load or vise versa, the switching pulse is designed to turn OFF with the device held operated in normal PWM control loop, which allows linear operation without voltage drop or deterioration in transient response during the mode switching from light load to heavy load or vise versa.

Although the PWM control loop continues to operate with a SET signal from OSC and a RESET signal from Current Comp, it is so designed that the RESET signal is held issued if shifted to the light load mode, with which the switching is tuned OFF and the switching pulses are thinned out under control. Activating the switching intermittently reduces the switching dissipation and improves the efficiency.

#### • 100% Duty control

Max duty is 100%. (@ Pch MOS FET always ON) In usual PWM control, in case output voltage cannot keep (ex, drop of input voltage), oscillation frequency becomes lower and finally it becomes 100% duty. The output voltage is a value that depends only by on a voltage hang from the input voltage to Pch MOS FET, and can keep the output voltage even with the low input voltage.

Fig.19 Diagram of current mode PWM control

Fig.20 PWM switching timing chart

Not switching Fig.21 SLLM<sup>TM</sup> switching timing chart

#### **Description of Operations**

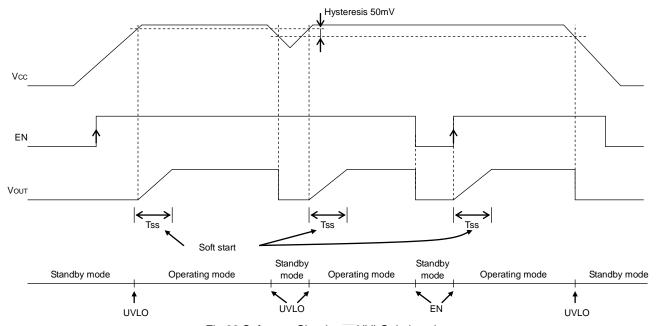

Soft-start function

EN terminal shifted to "High" activates a soft-starter to gradually establish the output voltage with the current limited during startup, by which it is possible to prevent an overshoot of output voltage and an inrush current.

#### Shutdown function

With EN terminal shifted to "Low", the device turns to Standby Mode, and all the function blocks including reference voltage circuit, internal oscillator and drivers are turned to OFF. Circuit current during standby is 0µF (Typ.).

#### UVLO function

Detects whether the input voltage sufficient to secure the output voltage of this IC is supplied. And the hysteresis width of 50 mV (Typ.) is provided to prevent output chattering.

Fig.22 Soft start, Shutdown, UVLO timing chart

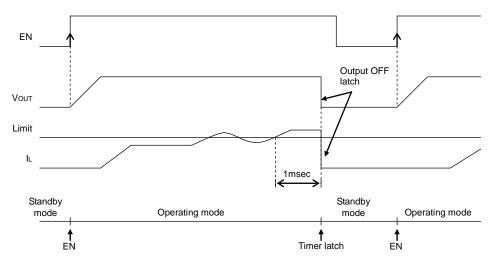

• Short-current protection circuit with time delay function

Turns OFF the output to protect the IC from breakdown when the incorporated current limiter is activated continuously for the fixed time (TLATCH) or more. The output thus held tuned OFF may be recovered by restarting EN or by re-unlocking UVLO.

Fig.23 Short-current protection circuit with time delay timing chart

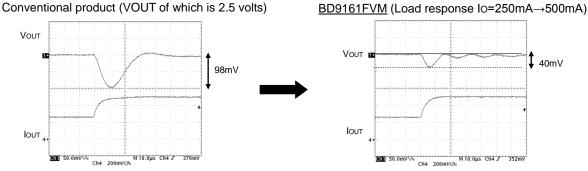

#### Information on Advantages

Advantage 1: Offers fast transient response with current mode control system.

Voltage drop due to sudden change in load was reduced by about 50%.

Fig.24 Comparison of transient response

Advantage 2 : Offers high efficiency for all load range.

· For lighter load:

Utilizes the current mode control mode called SLLM<sup>TM</sup> for lighter load, which reduces various dissipation such as switching dissipation (P<sub>SW</sub>), gate charge/discharge dissipation, ESR dissipation of output capacitor (P<sub>ESR</sub>) and on-resistance dissipation (P<sub>RON</sub>) that may otherwise cause degradation in efficiency for lighter load.

Achieves efficiency improvement for lighter load.

For heavier load:

Utilizes the synchronous rectifying mode and the low on-resistance MOS FETs incorporated as power transistor.

ON resistance of P-channel MOS FET: 0.35  $\Omega$  (Typ.) ON resistance of N-channel MOS FET: 0.37  $\Omega$  (Typ.)

Achieves efficiency improvement for heavier load.

Offers high efficiency for all load range with the improvements mentioned above.

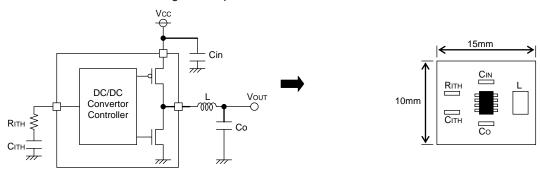

Advantage 3: • Supplied in smaller package due to small-sized power MOS FET incorporated.

Allows reduction in size of application products

• Output capacitor Co required for current mode control: 10  $\mu$ F ceramic capacitor Inductance L required for the operating frequency of 1 MHz: 4.7  $\mu$ H inductor

Reduces a mounting area required.

Fig.26 Example application

#### **Switching Regulator Efficiency**

```

VOUT×IOUT ×100[%]=

POUT ×100[%]=

Pout

×100[%]

Vin×lin

Pin

Ρουτ+Ροα

Efficiency may be improved by reducing the switching regulator power dissipation factors P_D\alpha as follows:

Dissipation factors:

1) ON resistance dissipation of inductor and FET: PD(I<sup>2</sup>R)

2) Gate charge/discharge dissipation: PD(Gate)

3) Switching dissipation: PD(SW)

4) ESR dissipation of capacitor : PD(ESR)

5) Operating current dissipation of IC: PD(IC)

1)PD(I^2R)=IOUT^2x(RCOIL+RON) (RCOIL[\Omega]: DC resistance of inductor, RON[\Omega]: ON resistance of FET

IOUT[A]: Output current.)

2)PD(Gate)=CgsxfxV (Cgs[F]: Gate capacitance of FET, f[H]: Switching frequency, V[V]: Gate driving voltage of FET)

Vin<sup>2</sup>xCRSSxIOUTxf

3)PD(SW)=

(CRSS[F]: Reverse transfer capacitance of FET, IDRIVE[A]: Peak current of gate.)

IDRIVE

4)PD(ESR)=IRMS<sup>2</sup>×ESR (IRMS[A] : Ripple current of capacitor, ESR[\Omega] : Equivalent series resistance.)

```

#### Consideration on Permissible Dissipation and Heat Generation

5)PD(IC)=VinxIcc (Icc[A] : Circuit current.)

Efficiency ŋ may be expressed by the equation shown below:

As this IC functions with high efficiency without significant heat generation in most applications, no special consideration is needed on permissible dissipation or heat generation. In case of extreme conditions, however, including lower input voltage, higher output voltage, heavier load, and/or higher temperature, the permissible dissipation and/or heat generation must be carefully considered.

For dissipation, only conduction losses due to DC resistance of inductor and ON resistance of FET are considered. Because the conduction losses are considered to play the leading role among other dissipation mentioned above including gate charge/discharge dissipation and switching dissipation.

P=Iout<sup>2</sup>x(Ron) Ron=DxRonp+(1-D)xRonn

D: ON duty (=Vout/Vcc)

RONP: ON resistance of P-channel MOS FET RONN: ON resistance of N-channel MOS FET

IOUT: Output current

Fig.27 Thermal derating curve (MSOP8)

≒127.7[mV]

```

If Vcc=3.3V, Vout=2.5V Ronp=0.35\Omega, Ronn=0.37\Omega Iout=0.6A, for example, D=Vout/Vcc=2.5/3.3=0.758 Ron=0.758×0.35+(1-0.758)×0.37 =0.2653+0.08954 =0.35484[\Omega] P=0.6<sup>2</sup>×0.35484

```

As RONP is greater than RONN in this IC, the dissipation increases as the ON duty becomes greater. With the consideration on the dissipation as above, thermal design must be carried out with sufficient margin allowed.

#### **Selection of Components Externally Connected**

Fig.28 Output ripple current

The inductance significantly depends on output ripple current. As seen in the equation (1), the ripple current decreases as the inductor and/or switching frequency increases.

$$\Delta IL = \frac{(Vcc-Vout) \times Vout}{L \times Vcc \times f} [A] \cdot \cdot \cdot (1)$$

Appropriate ripple current at output should be 20 to 30% more or less of the maximum output current.

$$\Delta$$

IL=0.25×IouTmax. [A] · · · (2)

$$L = \frac{(Vcc-VouT)\times VouT}{(Vcc-VouT)\times VouT}$$

[H] · · · (3)

(ΔIL: Output ripple current, and f: Switching frequency)

\* Current exceeding the current rating of the inductor results in magnetic saturation of the inductor, which decreases efficiency. The inductor must be selected allowing sufficient margin with which the peak current may not exceed its current rating.

If Vcc=3.3V, Vout=2.5V, f=1MHz,  $\Delta$ IL=0.25×0.6A=0.15A

$$L \ge \frac{(3.3-2.5)\times 2.5}{0.15\times 3.3\times 1M} \ge 4.04\mu$$

\* Select the inductor of low resistance component (such as DCR and ACR) to minimize dissipation in the inductor for better efficiency.

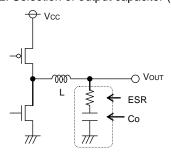

#### 2. Selection of output capacitor (CO)

Fig.29 Output capacitor

Output capacitor should be selected with the consideration on the stability region and the equivalent series resistance required to smooth ripple voltage. Output ripple voltage is determined by the equation (4):

$$\Delta V_{OUT} = \Delta I_{L} \times ESR[V] \cdot \cdot \cdot (4)$$

(ΔIL: Output ripple current, ESR: Equivalent series resistance of output capacitor)

\*Rating of the capacitor should be determined allowing sufficient margin against output voltage. Less ESR allows reduction in output ripple voltage.

Inappropriate capacitance may cause problem in startup. A 10μF to 100μF ceramic capacitor is recommended.

#### 3. Selection of input capacitor (Cin)

Fig.30 Input capacitor

Input capacitor to select must be a low ESR capacitor of the capacitance sufficient to cope with high ripple current to prevent high transient voltage. The ripple current IRMS is given by the equation (5):

IRMS=IOUT×

$$\frac{\sqrt{\text{VOUT}(\text{VCC-VOUT})}}{\text{VCC}}$$

[A] · · · (5)

< Worst case > IRMS(max.)

When VCC is twice the Vout,

$$\frac{\text{IOUT}}{2}$$

If Vcc=3.3V, Vout=2.5V, and Ioutmax.=0.6A

IRMS=0.6x

$$\frac{\sqrt{2.5(3.3-2.5)}}{5}$$

=0.284[ARMS]

A low ESR 10µF/10V ceramic capacitor is recommended to reduce ESR dissipation of input capacitor for better efficiency.

#### 4. Determination of RITH, CITH that works as a phase compensator

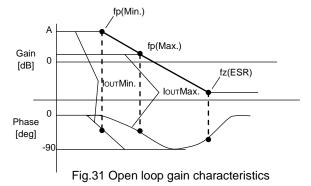

As the Current Mode Control is designed to limit a inductor current, a pole (phase lag) appears in the low frequency area due to a CR filter consisting of a output capacitor and a load resistance, while a zero (phase lead) appears in the high frequency area due to the output capacitor and its ESR. So, the phases are easily compensated by adding a zero to the power amplifier output with C and R as described below to cancel a pole at the power amplifier.

$$fp = \frac{1}{2\pi \times Ro \times Co}$$

$$fz(ESR) = \frac{1}{2\pi \times ESR \times Co}$$

#### Pole at power amplifier

When the output current decreases, the load resistance Ro increases and the pole frequency lowers.

$$fp(Min.) = \frac{1}{2\pi \times ROMax. \times CO}$$

[Hz] — with lighter load

$$fp(Max.) = \frac{1}{2\pi \times ROMin. \times CO}$$

[Hz] — with heavier load

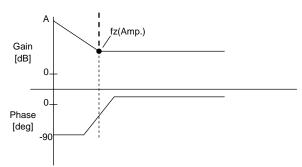

#### Zero at power amplifier

Increasing capacitance of the output capacitor lowers the pole frequency while the zero frequency does not change. (This is because when the capacitance is doubled, the capacitor ESR reduces to half.)

$$f_{Z(Amp.)} = \frac{1}{2\pi \times RITH. \times CITH}$$

Fig.32 Error amp phase compensation characteristics

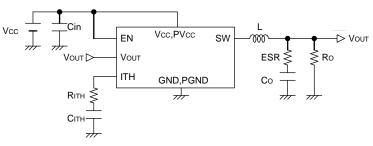

Fig.33 Typical application

Stable feedback loop may be achieved by canceling the pole fp (Min.) produced by the output capacitor and the load resistance with CR zero correction by the error amplifier.

$$fz(Amp.) = fp(Min.)$$

$$\frac{1}{2\pi \times RITH \times CITH} = \frac{1}{2\pi \times ROMax. \times CO}$$

#### 5. Determination of output voltage

The output voltage VouT is determined by the equation (6):

Vout=(R2/R1+1)xVadJ···(6) VadJ: Voltage at ADJ terminal (0.8V Typ.) With R1 and R2 adjusted, the output voltage may be determined as required. (Adjustable output voltage range: 1.0V to 3.3V)

Use 1 k $\Omega$  to 100 k $\Omega$  resistor for R1. If a resistor of the resistance higher than 100 k $\Omega$  is used, check the assembled set carefully for ripple voltage etc.

Fig.34 Determination of output voltage

#### **BD9161FVM Cautions on PC Board Layout**

Fig.35 Board layout

- ① For the sections drawn with heavy line, use thick conductor pattern as short as possible.

- ② Lay out the input ceramic capacitor CIN closer to the pins PVCC and PGND, and the output capacitor Co closer to the pin PGND.

- 3 Lay out CITH and RITH between the pins ITH and GND as neat as possible with least necessary wiring.

**Recommended Component Lists With Above Applications**

| Symbol | Part              | Value                  |       | Manufacturer | Series            |

|--------|-------------------|------------------------|-------|--------------|-------------------|

|        | Coil              | 4.7µH                  |       | TDK          | VLF5014AT-4R7M1R1 |

| L      | Coil              |                        |       | Sumida       | CMD6D11B          |

| Rin    | Resistance        | 10Ω                    |       | ROHM         | MCR03 Series      |

| CIN    | Ceramic capacitor | 10μF                   |       | Kyocera      | CM316X5R106K10A   |

| Co     | Ceramic capacitor | 10µF                   |       | Kyocera      | CM316X5R106K10A   |

|        | Ceramic capacitor | V <sub>OUT</sub> =1.0V | 820pF | murata       | GRM18 Series      |

|        |                   | V <sub>OUT</sub> =1.2V | 560pF | murata       | GRM18 Series      |

| Сітн   |                   | V <sub>OUT</sub> =1.5V | 470pF | murata       | GRM18 Series      |

|        |                   | V <sub>OUT</sub> =1.8V | 470pF | murata       | GRM18 Series      |

|        |                   | V <sub>OUT</sub> =2.5V | 330pF | murata       | GRM18 Series      |

|        | Resistance        | V <sub>OUT</sub> =1.0V | 6.8kΩ | ROHM         | MCR03 Series      |

|        |                   | V <sub>OUT</sub> =1.2V | 8.2Ω  | ROHM         | MCR03 Series      |

| RITH   |                   | V <sub>OUT</sub> =1.5V | 12kΩ  | ROHM         | MCR03 Series      |

|        |                   | V <sub>OUT</sub> =1.8V | 12kΩ  | ROHM         | MCR03 Series      |

|        |                   | V <sub>OUT</sub> =2.5V | 15kΩ  | ROHM         | MCR03 Series      |

<sup>\*</sup> The parts list presented above is an example of recommended parts. Although the parts are sound, actual circuit characteristics should be checked on your application carefully before use. Be sure to allow sufficient margins to accommodate variations between external devices and this IC when employing the depicted circuit with other circuit constants modified. Both static and transient characteristics should be considered in establishing these margins. When switching noise is substantial and may impact the system, a low pass filter should be inserted between the VCC and PVCC pins, and a schottky barrier diode established between the SW and PGND pins.

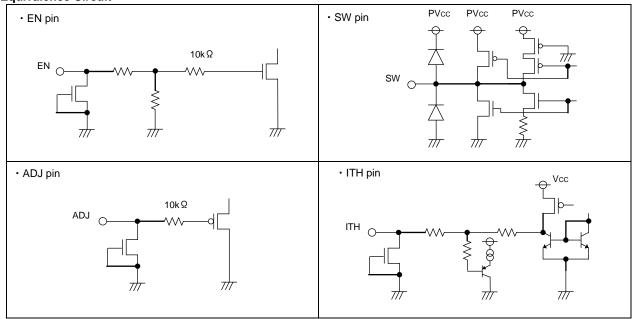

#### ●I/O Equivalence Circuit

Fig.36 I/O equivalence circuit

#### Operational Notes

#### 1. Absolute Maximum Ratings

While utmost care is taken to quality control of this product, any application that may exceed some of the absolute maximum ratings including the voltage applied and the operating temperature range may result in breakage. If broken, short-mode or open-mode may not be identified. So if it is expected to encounter with special mode that may exceed the absolute maximum ratings, it is requested to take necessary safety measures physically including insertion of fuses.

#### 2. Electrical potential at GND

GND must be designed to have the lowest electrical potential In any operating conditions.

#### 3. Short-circuiting between terminals, and mismounting

When mounting to pc board, care must be taken to avoid mistake in its orientation and alignment. Failure to do so may result in IC breakdown. Short-circuiting due to foreign matters entered between output terminals, or between output and power supply or GND may also cause breakdown.

#### 4. Operation in Strong electromagnetic field

Be noted that using the IC in the strong electromagnetic radiation can cause operation failures.

#### 5. Thermal shutdown protection circuit

Thermal shutdown protection circuit is the circuit designed to isolate the IC from thermal runaway, and not intended to protect and guarantee the IC. So, the IC the thermal shutdown protection circuit of which is once activated should not be used thereafter for any operation originally intended.

#### 6. Inspection with the IC set to a pc board

If a capacitor must be connected to the pin of lower impedance during inspection with the IC set to a pc board, the capacitor must be discharged after each process to avoid stress to the IC. For electrostatic protection, provide proper grounding to assembling processes with special care taken in handling and storage. When connecting to jigs in the inspection process, be sure to turn OFF the power supply before it is connected and removed.

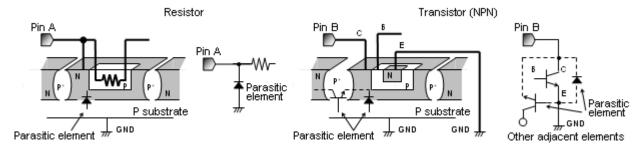

#### 7. Input to IC terminals

This is a monolithic IC with  $P^+$  isolation between P-substrate and each element as illustrated below. This P-layer and the N-layer of each element form a P-N junction, and various parasitic element are formed.

If a resistor is joined to a transistor terminal as shown in Fig 37:

OP-N junction works as a parasitic diode if the following relationship is satisfied; GND>Terminal A (at resistor side), or GND>Terminal B (at transistor side); and

Oif GND>Terminal B (at NPN transistor side),

a parasitic NPN transistor is activated by N-layer of other element adjacent to the above-mentioned parasitic diode. The structure of the IC inevitably forms parasitic elements, the activation of which may cause interference among circuits, and/or malfunctions contributing to breakdown. It is therefore requested to take care not to use the device in such manner that the voltage lower than GND (at P-substrate) may be applied to the input terminal, which may result in activation of parasitic elements.

Fig.37 Simplified structure of monorisic IC

#### 8. Ground wiring pattern

If small-signal GND and large-current GND are provided, It will be recommended to separate the large-current GND pattern from the small-signal GND pattern and establish a single ground at the reference point of the set PCB so that resistance to the wiring pattern and voltage fluctuations due to a large current will cause no fluctuations in voltages of the small-signal GND. Pay attention not to cause fluctuations in the GND wiring pattern of external parts as well.

#### Status of this document

The Japanese version of this document is formal specification. A customer may use this translation version only for a reference to help reading the formal version.

If there are any differences in translation version of this document formal version takes priority

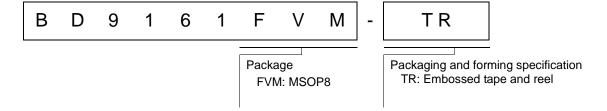

#### Ordering Information

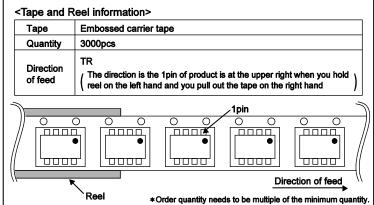

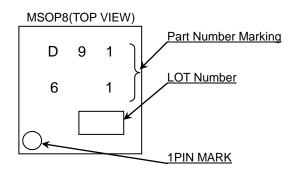

#### Physical Dimension, Tape and Reel information

#### MSOP8

#### Marking Diagram

### **Notice**

#### Precaution for circuit design

- 1) The products are designed and produced for application in ordinary electronic equipment (AV equipment, OA equipment, telecommunication equipment, home appliances, amusement equipment, etc.). If the products are to be used in devices requiring extremely high reliability (medical equipment, transport equipment, aircraft/spacecraft, nuclear power controllers, fuel controllers, car equipment including car accessories, safety devices, etc.) and whose malfunction or operational error may endanger human life and sufficient fail-safe measures, please consult with the ROHM sales staff in advance. If product malfunctions may result in serious damage, including that to human life, sufficient fail-safe measures must be taken, including the following:

- [a] Installation of protection circuits or other protective devices to improve system safety

- [b] Installation of redundant circuits in the case of single-circuit failure

- 2) The products are designed for use in a standard environment and not in any special environments. Application of the products in a special environment can deteriorate product performance. Accordingly, verification and confirmation of product performance, prior to use, is recommended if used under the following conditions:

- [a] Use in various types of liquid, including water, oils, chemicals, and organic solvents

- [b] Use outdoors where the products are exposed to direct sunlight, or in dusty places

- [c] Use in places where the products are exposed to sea winds or corrosive gases, including Cl2, H2S, NH3, SO2, and NO2

- [d] Use in places where the products are exposed to static electricity or electromagnetic waves

- [e] Use in proximity to heat-producing components, plastic cords, or other flammable items

- [f] Use involving sealing or coating the products with resin or other coating materials

- [g] Use involving unclean solder or use of water or water-soluble cleaning agents for cleaning after soldering

- [h] Use of the products in places subject to dew condensation

- 3) The products are not radiation resistant.

- Verification and confirmation of performance characteristics of products, after on-board mounting, is advised.

- 5) In particular, if a transient load (a large amount of load applied in a short period of time, such as pulse) is applied, confirmation of performance characteristics after on-board mounting is strongly recommended. Avoid applying power exceeding normal rated power; exceeding the power rating under steady-state loading condition may negatively affect product performance and reliability.

- 6) De-rate Power Dissipation (Pd) depending on Ambient temperature (Ta). When used in sealed area, confirm the actual ambient temperature.

- 7) Confirm that operation temperature is within the specified range described in product specification.

- 8) Failure induced under deviant condition from what defined in the product specification cannot be guaranteed.

#### Precaution for Mounting / Circuit board design

- 1) When a highly active halogenous (chlorine, bromine, etc.) flux is used, the remainder of flux may negatively affect product performance and reliability.

- 2) In principle, the reflow soldering method must be used; if flow soldering method is preferred, please consult with the Company in advance.

Regarding Precaution for Mounting / Circuit board design, please specially refer to ROHM Mounting specification

#### ● Precautions Regarding Application Examples and External Circuits

- 1) If change is made to the constant of an external circuit, allow a sufficient margin due to variations of the characteristics of the products and external components, including transient characteristics, as well as static characteristics.

- 2) The application examples, their constants, and other types of information contained herein are applicable only when the products are used in accordance with standard methods. Therefore, if mass production is intended, sufficient consideration to external conditions must be made.

#### Precaution for Electrostatic

This product is Electrostatic sensitive product, which may be damaged due to Electrostatic discharge. Please take proper caution during manufacturing and storing so that voltage exceeding Product maximum rating won't be applied to products. Please take special care under dry condition (e.g. Grounding of human body / equipment / solder iron, isolation from charged objects, setting of lonizer, friction prevention and temperature / humidity control).

#### ● Precaution for Storage / Transportation

- 1) Product performance and soldered connections may deteriorate if the products are stored in the following places:

- [a] Where the products are exposed to sea winds or corrosive gases, including Cl2, H2S, NH3, SO2, and NO2

- [b] Where the temperature or humidity exceeds those recommended by the Company

- [c] Storage in direct sunshine or condensation

- [d] Storage in high Electrostatic

- 2) Even under ROHM recommended storage condition, solderability of products out of recommended storage time period may be degraded. It is strongly recommended to confirm solderability before using products of which storage time is exceeding recommended storage time period.

- 3) Store / transport cartons in the correct direction, which is indicated on a carton as a symbol. Otherwise bent leads may occur due to excessive stress applied when dropping of a carton.

- 4) Use products within the specified time after opening a dry bag.

#### Precaution for product label

QR code printed on ROHM product label is only for internal use, and please do not use at customer site. It might contain a internal part number that is inconsistent with an product part number.

#### Precaution for disposition

When disposing products please dispose them properly with a industry waste company.

#### Precaution for Foreign exchange and Foreign trade act

Since concerned goods might be fallen under controlled goods prescribed by Foreign exchange and Foreign trade act, please consult with ROHM in case of export.

#### Prohibitions Regarding Industrial Property

- 1) Information and data on products, including application examples, contained in these specifications are simply for reference; the Company does not guarantee any industrial property rights, intellectual property rights, or any other rights of a third party regarding this information or data. Accordingly, the Company does not bear any responsibility for:

- [a] infringement of the intellectual property rights of a third party

- [b] any problems incurred by the use of the products listed herein.

- 2) The Company prohibits the purchaser of its products to exercise or use the intellectual property rights, industrial property rights, or any other rights that either belong to or are controlled by the Company, other than the right to use, sell, or dispose of the products.