# **LED Driver Series for LCD Backlight**

# White backlight LED drivers for medium to large LCD panels (SWREG type)

BD9202EFS No.09040EAT01

#### Description

BD9202EFS is the LED driver IC which loads the step-up DCDC controller and the constant electric current driver of 8ch. As for the constant electric current driver, PWM modulated light of 10bit gradation (1024stages) is possible with the register setting from 4 line serial interfaces.

Because it can adjust brightness with every channel, back light is controlled in every area according to the light and shade of the picture, rise of contrast ratio is actualized.

### Features

- 1)8ch constant electric current driver built-in

- Largest drive electric current 150mA/CH \*2

- •10bit gradation (1024 stages) modulated light is possible by register setting

- •To input the standard CLK of PWM from outside is possible (BCT\_SYNC\_IN terminal)

- •Because it is high output resisting pressure (60V), the multi-stage connection of LED is possible

- Detecting abnormal mode with LED opening detection

- 2)Step-up DCDC controller built-in

- 3) UVLO function

- 4) 4 line serial interface

- 5) HTSSOP-A44 Package

#### Applications

For the equipment of loading LCD indicator of TV, monitor and note PC and the like

# ● Absolute maximum rating (Ta=25°C)

| Parameter                                                                                                                                              | Symbol                                                                                                                                             | Rating              | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|

|                                                                                                                                                        | VCC                                                                                                                                                | 36                  | V    |

| Power supply voltage                                                                                                                                   | CPUVDD                                                                                                                                             | 5.5                 | V    |

|                                                                                                                                                        | VREG                                                                                                                                               | 5.5                 | V    |

| LED1∼8 terminal voltage                                                                                                                                | VLED1~8                                                                                                                                            | 60                  | V    |

| EN,LOADSW terminal voltage                                                                                                                             | VEN,VLOADSW                                                                                                                                        | 36                  | V    |

| FAIL1,FAIL2 terminal voltage                                                                                                                           | VFAIL1,VFAIL2                                                                                                                                      | 7                   | V    |

| VREF,ISET,VSET,TEST,BRT,RT,<br>CS,UVLO,COMP,CP1,CP2,TOUT1,<br>TOUT2,SWOUT,OVP,CT_SYNC_IN,<br>CT_SYNC_OUT,BCT_SYNC_IN,<br>BCT_SYNC_OUT terminal voltage | VVREF, VISET, VVSET, VTEST, VBRT, VRT, VCS, VUVLO, VCOMP,VCP1,VCP2,VTOUT1, VTOUT2,VSWOUT,VOVPVCT_SYNC_IN, VCT_SYNC_OUT,VBCT_SYNC_IN, VBCT_SYNC_OUT | -0.3~5.5<<br>VREG   | >    |

| CPUDI,CPUCLK,CPUCS,CPUDO terminal voltage                                                                                                              | VCPUDI, VCPUCLK, VCPUCS, VCPUDO                                                                                                                    | -0.3~5.5<<br>CPUVDD | V    |

| Power Dissipation                                                                                                                                      | Pd                                                                                                                                                 | 4.5 *1              | W    |

| Operating Temperature Range                                                                                                                            | Topr                                                                                                                                               | -40 <b>~</b> +85    | °C   |

| Storage Temperature Range                                                                                                                              | Tstg                                                                                                                                               | -55 <b>~</b> +150   | °C   |

| LED Maximum Current                                                                                                                                    | ILED                                                                                                                                               | 150 *2 *3           | mA   |

<sup>\*1</sup>At the time of mounting 2 layer glass epoxy base-plate of 70mm×70mm×1.6mm, 36.0mW is reduced at 1 °C above Ta=25.

<sup>\*2</sup> When the VF variation of LED is large, the loss quantity with the driver will increase, because there are times when package temperature rises, please do the base-plate design after considering heat dissipation measure sufficiently.

<sup>\*3</sup>It is the electric current quantity per 1ch.

●Operating condition (Ta=25°C)

| Parameter                               | Symbol      | Voltage range | Unit |

|-----------------------------------------|-------------|---------------|------|

| David a surah walta wa                  | VREG        | 5.25~5.5      | V    |

| Power supply voltage                    | CPUVDD      | 2.7~5.5       | ٧    |

| CT oscillation frequency setting range  | fCT         | 300~800       | kHz  |

| CT_SYNC_IN input frequency range *4*5   | FCT_SYNC_IN | fCT~800       | kHz  |

| BCT oscillation frequency setting range | fBCT        | 100~1000      | kHz  |

| BCT_SYNC_IN input frequency range *4*5  | FBCT_SYNC_I | fBCT~1000     | kHz  |

| VSET Input potential                    | VSET        | 0.9~2.4       | V    |

<sup>\*4</sup> When not using external frequency input, please connect the terminal of CT\_SYNC\_IN, BCT\_SYNC\_IN to GND.

\*5When using external frequency input, please do not do the operation that is changed to internal oscillation frequency on midway.

# Electric characteristic

((Unless otherwise specified Ta=25°C, VCC=24V, VREG=5V, CPUVDD=3V)

| Parameter                                 | Symbol      | Limit         |               | Unit          | Condition |                                                                     |

|-------------------------------------------|-------------|---------------|---------------|---------------|-----------|---------------------------------------------------------------------|

|                                           | Зуппоот     | Min           | Тур           | Max           | Offic     | Condition                                                           |

| [All the circuit electric currents]       |             |               |               | ı             | ı         | 1,000,041/                                                          |

| Circuit electric currents                 | Icc         | 6             | 13            | 21            | mA        | VCC=24V<br>CPUVDD=3V, EN=3V<br>LED1~8=OFF                           |

| Stand-by electric current                 | IST         | -             | 0             | 10            | uA        | EN=0V                                                               |

| [VREG section]                            |             |               |               |               |           |                                                                     |

| VREG Output voltage                       | VREG        | 4.8           | 5             | 5.2           | V         | Io=0mA,CREG=2.2uF                                                   |

| VREG VREG sink electric current           | IREG        | 5             | 12            | 20            | mA        | At the time of external impressing of VREG=5.25VAt LED1~8=OFF,EN=3V |

| VREF Output voltage                       | VREF        | 1.57          | 1.60          | 1.63          | V         | Io=0uA                                                              |

| [Switching section]                       |             |               |               |               |           |                                                                     |

| SWOUT Source value of resistance          | RONH        | -             | 7             | -             | Ω         | ION=-10mA                                                           |

| SWOUT Sink value of resistance            | RONL        | -             | 2             | -             | Ω         | ION=10mA                                                            |

| [OCP section]                             | T           |               |               | 1             | 1         |                                                                     |

| Over-current protective operating voltage | VOLIMIT     | 0.1           | 0.2           | 0.3           | V         | Vcs=Sweep up                                                        |

| [Error amplifier section]                 |             |               |               |               |           |                                                                     |

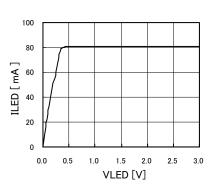

| LED Control voltage                       | VLED        | 0.55          | 0.75          | 0.95          | V         |                                                                     |

| COMP Sink electric current                | ICOMPSINK   | 40            | 100           | 200           | uA        | VLED=2V,Vcomp=1V                                                    |

| COMP Source electric current              | ICOMPSOURCE | -200          | -100          | -40           | uA        | VLED=0V,Vcomp=1V                                                    |

| [CT Oscillator section]                   |             |               |               |               |           |                                                                     |

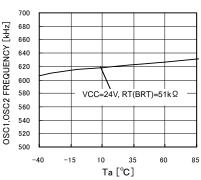

| CT Oscillation frequency                  | FCT         | 500           | 600           | 700           | kHz       | RT=51kΩ                                                             |

| CT_SYNC_IN input High voltage             | VSYNC_INH   | VREG<br>× 0.7 | -             | VREG<br>+0.3  | V         |                                                                     |

| CT_SYNC_IN input low voltage              | VSYNC_INL   | -0.3          | -             | VREG<br>×0.3  | V         |                                                                     |

| CT_SYNC_OUT output high voltage           | VSYNC_OUTH  | VREG<br>-1.0  | VREG<br>-0.15 | -             | V         | IOL=-1mA                                                            |

| CT_SYNC_OUT output low voltage            | VSYNC_OUTL  | -             | 0.1           | 0.5           | V         | IOL=1mA                                                             |

| [BCT Oscillator section]                  |             |               |               |               |           |                                                                     |

| BCT Oscillation frequency                 | FBCT        | 500           | 600           | 700           | kHz       | BRT=51kΩ                                                            |

| BCT_SYNC_IN input High voltage            | VBSYNC_INH  | VREG<br>×0.7  | -             | VREG<br>+0.3  | V         |                                                                     |

| BCT_SYNC_IN input low voltage             | VBSYNC_INL  | -0.3          | -             | VREG<br>× 0.3 | V         |                                                                     |

| BCT_SYNC_OUT output high voltage          | VBSYNC_OUTH | VREG<br>-1.0  | VREG<br>-0.15 | -             | V         | IOL=-1mA                                                            |

| BCT_SYNC_OUT output low voltage           | VBSYNC_OUTL | -             | 0.1           | 0.5           | V         | IOL=1mA                                                             |

| (OVP section) OVP section                 |             |               |               |               |           |                                                                     |

| Over-voltage detection reference voltage  | VOVP        | 1.85          | 2.0           | 2.15          | V         | VOVP=Sweep up                                                       |

| OVP Hysteresis voltage                    | VOVPHYS     | 0.4           | 0.5           | 0.6           | V         | VOVP=Sweep down                                                     |

| [UVLO section]                            |             |               |               |               |           | ·                                                                   |

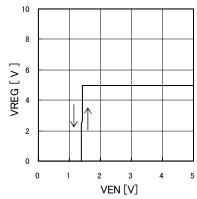

| UVLO (VREG) Detection voltage             | VUVLO_VREG  | 2.6           | 2.9           | 3.2           | V         | VREG=Sweep down                                                     |

| UVLO (VREG) Hysteresis voltage            | VUHYS_VREG  | 50            | 100           | 200           | mV        | VREG=Sweep up                                                       |

| UVLO(EXT) Detection voltage               | VUVLO_EXT   | 1.7           | 1.9           | 2.1           | V         | UVLO=sweep down                                                     |

| UVLO(EXT) Hysteresis voltage              | VUHYS_EXT   | 50            | 100           | 200           | mV        | UVLO=sweep up                                                       |

|                                                    | 0 1 1    |                | Limit |                |      | O a maditi a m                               |

|----------------------------------------------------|----------|----------------|-------|----------------|------|----------------------------------------------|

| Parameter                                          | Symbol   | Min            | Тур   | Max            | Unit | Condition                                    |

| 【LOADSW section】                                   |          |                |       |                |      |                                              |

| LOADSW ON value of resistance                      | RON_LOAD | 1.2            | 2.0   | 2.2            | kΩ   | ILOAD=1mA                                    |

| [Filter(CP1,CP2) section]                          |          |                |       |                |      |                                              |

| CP Detection voltage                               | VCP      | 1.8            | 2.0   | 2.2            | V    | CP1,CP2=Sweep up                             |

| CP Charging current                                | ICP      | -2.0           | -1.0  | -0.5           | uA   | CP1,CP2=0V                                   |

| 【LED output (LED1∼8) section】                      |          |                |       |                |      |                                              |

| LED Electric current absolute variation            | ⊿ILED    | -              | -     | (5)            | %    | ILED=75mA,VSET=1.65V<br>RISET=130kΩ          |

| ISET Clamp voltage                                 | VISET    | 1.8            | 2.0   | 2.2            | V    | when input VSET>VISET                        |

| Open detection voltage                             | VOPEN    | 0.05           | 0.20  | 0.35           | V    | VLED=Sweep down                              |

| Short detection voltage                            | VSHORT   | 3.5            | 4.0   | 4.5            | ٧    | VLED=Sweep up                                |

| [Logic input(EN,CPUCS,CPUCLK,CPUDI)]               | 1        |                |       |                |      |                                              |

| Input High voltage                                 | VINH     | 0.7×<br>CPUVDD | -     | CPUVDD<br>+0.3 | ٧    |                                              |

| Input Low voltage                                  | VINL     | -0.3           | -     | 0.3×<br>CPUVDD | ٧    |                                              |

| Input influx electric current (CPUCS,CPUCLK,CPUDI) | IIN      | -5             | 0     | 5              | uA   | VIN=5V(CPUCS,<br>CPUCLK,CPUDI),<br>CPUVDD=5V |

| Input influx electric current (EN)                 | IEN      | 13             | 25    | 38             | uA   | VEN=5V(EN)                                   |

| [Logic output section(CPUDO)]                      |          |                |       |                |      |                                              |

| output High voltage                                | VOUTH    | 2.4            | 2.7   | -              | V    | IOL=-1mA,CPUVDD=3V                           |

| output Low voltage                                 | VOUTL    | -              | 0.25  | 0.6            | V    | IOL=1mA,CPUVDD=3V                            |

| [FAIL1,2outut open drain]                          |          |                |       |                |      |                                              |

| FAIL Low voltage                                   | VOL      | 0.07           | 0.14  | 0.28           | V    | IOL=1mA                                      |

<sup>\*</sup> This product is not designed for protection against radioactive rays.

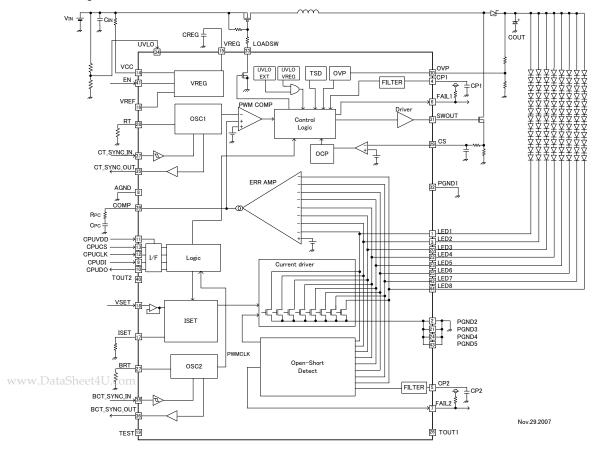

# Block diagram

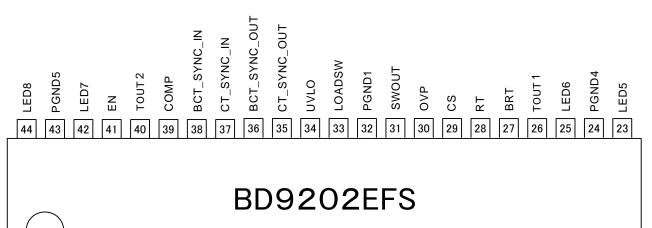

# ●Pin configuration

10 11 13 16 19 20 21 22 CPUVDD CPUCLK CPUCS LED1 PGND2 CPUDO FAIL1 FAIL2 CPUDI PGND3 LED2 CP1 AGND VCC CP2VREG VREF ISET VSET TEST LED3 LED4

# ●Terminal number, terminal name

| PIN<br>No. | Terminal<br>name | Function                                                        | PIN<br>No. | Terminal name | Function                                                                  |

|------------|------------------|-----------------------------------------------------------------|------------|---------------|---------------------------------------------------------------------------|

| (1)        | LED1             | LED output terminal1                                            | (23)       | LED5          | LED output terminal 5                                                     |

| (2)        | PGND2            | GND2 for LED                                                    | (24)       | PGND4         | GND4 for LED                                                              |

| (3)        | LED2             | LED output terminal2                                            | (25)       | LED6          | LED output terminal 6                                                     |

| (4)        | CP1              | Condenser connected terminal for filter setting 1               | (26)       | TOUT1         | Output terminal 1 for test monitor 1                                      |

| (5)        | CP2              | Condenser connected terminal for filter setting 2               | (27)       | BRT           | BCT oscillation frequency setting resistant connected terminal            |

| (6)        | FAIL1            | Malfunction detection output 1                                  | (28)       | RT            | CT oscillation frequency setting resistant connected terminal             |

| (7)        | FAIL2            | Malfunction detection output 2                                  | (29)       | CS            | DC/DC output electric current detection terminal                          |

| (8)        | AGND             | Small signal section GND                                        | (30)       | OVP           | DC/DC Over-voltage detection terminal                                     |

| (9)        | CPUDI            | Serial interface DATA input terminal                            | (31)       | SWOUT         | DC/DC Switching output terminal                                           |

| (10)       | CPUDO            | Serial interface DATA output terminal                           | (32)       | PGND1         | GND1 for LED                                                              |

| (11)       | CPUVDD           | Serial interface Power supply terminal                          | (33)       | LOADSW        | Load switch control terminal                                              |

| (12)       | CPUCLK           | Serial interface CLK input terminal                             | (34)       | UVLO          | It is the prevention detection terminal for miss operating at low voltage |

| (13)       | CPUCS            | Serial interface CS input terminal                              | (35)       | CT_SYNC_OUT   | CT Synchronization signal output terminal                                 |

| (14)       | VCC              | Power supply terminal                                           | (36)       | BCT_SYNC_OUT  | BCT Synchronization signal output terminal                                |

| (15)       | VREG             | Series regulator output terminal                                | (37)       | CT_SYNC_IN    | CT Synchronization signal input terminal                                  |

| (16)       | VREF             | Reference voltage output terminal                               | (38)       | BCT_SYNC_IN   | BCT Synchronization signal input terminal                                 |

| (17)       | ISET             | LED fixed electric current setting resistant connected terminal | (39)       | COMP          | Error amplifier output terminal                                           |

| (18)       | VSET             | DC modulated light voltage input terminal                       | (40)       | TOUT2         | Output terminal 2 for test monitor                                        |

| (19)       | TEST             | Test mode change terminal                                       | (41)       | EN            | Enabling terminal                                                         |

| (20)       | LED3             | Output terminal 3                                               | (42)       | LED7          | LED output terminal 7                                                     |

| (21)       | PGND3            | GND3 for LED                                                    | (43)       | PGND5         | GND5 for LED                                                              |

| (22)       | LED4 com         | LED output terminal 4                                           | (44)       | LED8          | LED output terminal 8                                                     |

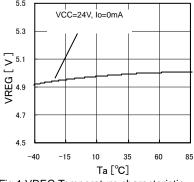

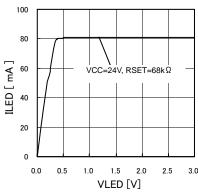

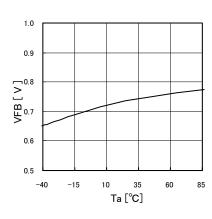

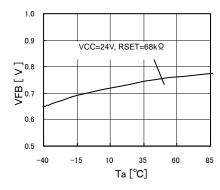

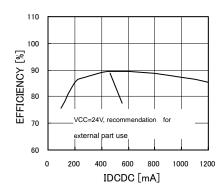

●The reference data (Unless otherwise specified VCC=24V and Ta=25 °C)

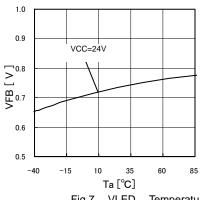

Fig.1 VREG Temperature characteristic

Fig.4 ILED depending on VLED

Fig.7 VLED Temperature characteristic

Fig.10 Short detection temperature characteristic

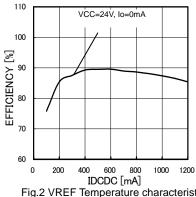

Fig.2 VREF Temperature characteristic

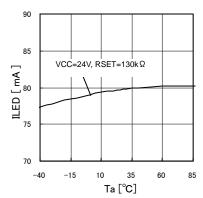

Fig.5 ILED Temperature characteristic

Fig.8 ICC-VCC characteristic

Fig.11 Open detection temperature characteristic

OSC1,OSC2 Temperature Fig.3 re characteristic

Fig.6 VSET Constant electric current characteristic

Fig.9 EN Threshold voltage

Fig.12 Efficiency

## Functional explanation

#### O VREG

The fixed voltage of 5V is generated from VCC. It starts when it becomes EN=H.

UVLO (Under Voltage LOCK Out) is built in by VREG, When it is below 2.9V (typ), the internal circuit stops.

When it is above 3.0V (typ), the internal circuit operation starts.

Please connect Creg=2.2 µ F to the VREG terminal, as a capacity for phase compensation.

In order to make IC heat generation decrease, impressing voltage into the VREG terminal from outside, it is possible to decrease the loss with the regulator inside IC.

In this case, as for the impressing voltage, please impress that of above output voltage (5.25V5.5V) of the internal regulator.

#### O UVLO (Under Voltage Lock Out)

There are UVLO (REG) which detects VREG voltage① and UVLO (VCC) ② which detects VCC voltage in UVLO. When each UVLO is below specified value, the internal circuit is made to stop. (The logic section is reset.)

| Detecting circuit                     | Detection object | Detection      | Cancellation    |  |

|---------------------------------------|------------------|----------------|-----------------|--|

| UVLO (VREG)                           | VREG             | Below2.9V(typ) | Above 3.0V(typ) |  |

| UVLO (VCC) VCC partial pressure input |                  | Below1.9V(typ) | Above 2.0V(typ) |  |

Please do not connect VCC terminal (> 5.25V) to the UVLO terminal (for VCC detection) directly. Because there is a possibility of destruction, please be sure to input with partial pressure.

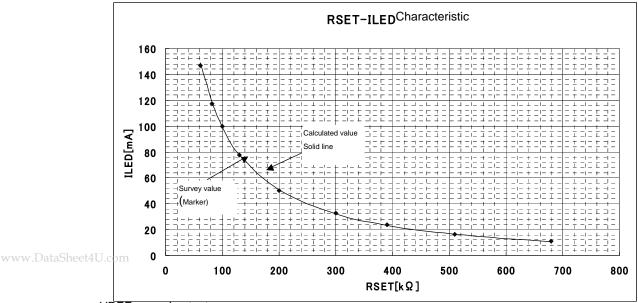

#### O Fixed electric current driver

Fixed current value of the fixed electric current driver can be got by constant doubling the standard electric current which is decided by the resistance (RSET) of being connected to ISET and the voltage which are input into the VSET terminal. In addition continual electric current variable (analog modulated light) is possible by changing VSET voltage from outside.

In addition, it is possible to do PWM modulated light by the fact that the data is input to the internal register from the serial interface section. It is possible to set the Duty value of PWM for each channel.

· Setting of fixed current value

Fixed current value (DC value) of the LED driver is a relational expression below.

ILED=  $\{VSET/(RSET[k\Omega]+20[k\Omega])\} \times 7980-8[mA]$

However, when VSET voltage is above 2V, it reaches the point where it is clamped with 2V inside IC, fixed current value above that does not increase.

In addition, please input VSET in the range of 0.6V-2.4V.

VREF normal output

In VREG block, VREF (1.6V (typ.)of reference voltage output is provided.

The necessity of doing the voltage impression from outside by the fact that this terminal is connected to the VSET terminal is gone. However, because the voltage variation of VREF is to be reflected on the variation of LED fixed electric current directly, so that please pay attention to it.

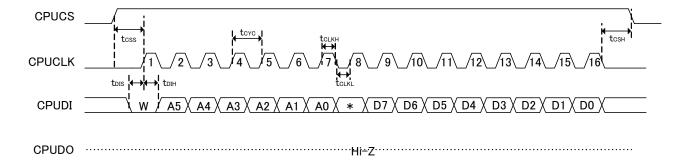

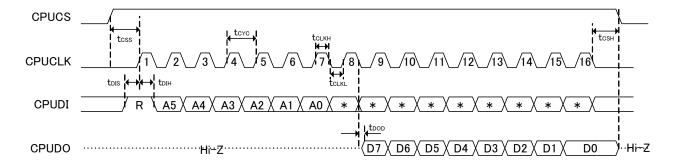

# O Serial interface section

This IC is controlled by 4 line serial interfaces of CPUCLK, CPUCS, CPUDI and CPUDO. The data entry format and timing are shown below.

# In the case of WRITE

# In the case of READ

- It does not correspond to the continual entry of the data. It is necessary to set CPUCS into L in every address.

- There is no function of the automatic increment of address.

- · Address width is correspondence to 6bit, but please do not access the address other than 00h-11h absolutely.

# AC electric quality

| Function                | C. made al   |     | Unit |     |       |

|-------------------------|--------------|-----|------|-----|-------|

| Function                | Symbol       | Min | Тур  | Max | Offic |

| CPUCLK Periods          | tcyc         | 100 | -    | -   | ns    |

| CPUCLK high level width | tclkh        | 35  | -    | -   | ns    |

| CPUCLK low level width  | tclkl        | 35  | -    | -   | ns    |

| CPUDI input set up time | tois         | 50  | -    | -   | ns    |

| CPUDI input hold time   | toih         | 50  | -    | -   | ns    |

| CPUCS input set up time | tcss         | 50  | -    | -   | ns    |

| CPUCS input hold time   | <b>t</b> csH | 50  | -    | -   | ns    |

| CPUDO Output delay time | tDOD         | -   | -    | 40  | ns    |

(Output load: 15pF)

# Register map

| Addres<br>s | R/W | Initial value | Register name | Bit7           | Bit6           | Bit5           | Bit4           | Bit3           | Bit2           | Bit1           | Bit $\phi$     | Function                                                  |

|-------------|-----|---------------|---------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|-----------------------------------------------------------|

| 00H         | R/W | 00h           | PWMCNT        | PWMRS<br>T     | -              | -              | -              | -              | -              | PARADRV        | PWMEN          | PWM control register                                      |

| 01H         | R/W | 00h           | LEDEN         | LED8EN         | LED7EN         | LED6EN         | LED5EN         | LED4EN         | LED3EN         | LED2EN         | LED1EN         | LED ON/OFF Control register                               |

| 02H         | R/W | 00h           | SETPWM1<br>1  | PWM<br>LED1[7] | PWM<br>LED1[6] | PWM<br>LED1[5] | PWM<br>LED1[4] | PWM<br>LED1[3] | PWM<br>LED1[2] | PWM<br>LED1[1] | PWM<br>LED1[0] | Register 1 for setting LED1 PWM (Subordinate bit setting) |

| 03H         | R/W | 00h           | SETPWM<br>12  | -              | -              | ı              | -              | -              | -              | PWM<br>LED1[9] | PWM<br>LED1[8] | Register 2 for setting LED1 PWM (Superior bit setting)    |

| 04H         | R/W | 00h           | SETPWM<br>21  | PWM<br>LED2[7] | PWM<br>LED2[6] | PWM<br>LED2[5] | PWM<br>LED2[4] | PWM<br>LED2[3] | PWM<br>LED2[2] | PWM<br>LED2[1] | PWM<br>LED2[0] | Register 1 for setting LED2 PWM (Subordinate bit setting) |

| 05H         | R/W | 00h           | SETPWM<br>22  | -              | -              | ı              | -              | -              | -              | PWM<br>LED2[9] | PWM<br>LED2[8] | Register 2 for setting LED2 PWM (Superior bit setting)    |

| 06H         | R/W | 00h           | SETPWM<br>31  | PWM<br>LED3[7] | PWM<br>LED3[6] | PWM<br>LED3[5] | PWM<br>LED3[4] | PWM<br>LED3[3] | PWM<br>LED3[2] | PWM<br>LED3[1] | PWM<br>LED3[0] | Register 1 for setting LED3 PWM (Subordinate bit setting) |

| 07H         | R/W | 00h           | SETPWM<br>32  | -              | -              | -              | -              | -              | -              | PWM<br>LED3[9] | PWM<br>LED3[8] | Register 2 for setting LED3 PWM (Superior bit setting)    |

| H80         | R/W | 00h           | SETPWM<br>41  | PWM<br>LED4[7] | PWM<br>LED4[6] | PWM<br>LED4[5] | PWM<br>LED4[4] | PWM<br>LED4[3] | PWM<br>LED4[2] | PWM<br>LED4[1] | PWM<br>LED4[0] | Register 1 for setting LED4 PWM (Subordinate bit setting) |

| 09H         | R/W | 00h           | SETPWM<br>42  | -              | -              | -              | -              | -              | -              | PWM<br>LED4[9] | PWM<br>LED4[8] | Register 2 for setting LED4 PWM (Superior bit setting)    |

| 0AH         | R/W | 00h           | SETPWM<br>51  | PWM<br>LED5[7] | PWM<br>LED5[6] | PWM<br>LED5[5] | PWM<br>LED5[4] | PWM<br>LED5[3] | PWM<br>LED5[2] | PWM<br>LED5[1] | PWM<br>LED5[0] | Register 1 for setting LED5 PWM (Subordinate bit setting) |

| 0BH         | R/W | 00h           | SETPWM<br>52  | -              | -              | -              | -              | -              | -              | PWM<br>LED5[9] | PWM<br>LED5[8] | Register 2 for setting LED5 PWM (Superior bit setting)    |

| 0CH         | R/W | 00h           | SETPWM<br>61  | PWM<br>LED6[7] | PWM<br>LED6[6] | PWM<br>LED6[5] | PWM<br>LED6[4] | PWM<br>LED6[3] | PWM<br>LED6[2] | PWM<br>LED6[1] | PWM<br>LED6[0] | Register 1 for setting LED6 PWM (Subordinate bit setting) |

| 0DH         | R/W | 00h           | SETPWM<br>62  | -              | -              | -              | -              | -              | -              | PWM<br>LED6[9] | PWM<br>LED6[8] | Register 2 for setting LED6 PWM (Superior bit setting)    |

| 0EH         | R/W | 00h           | SETPWM<br>71  | PWM<br>LED7[7] | PWM<br>LED7[6] | PWM<br>LED7[5] | PWM<br>LED7[4] | PWM<br>LED7[3] | PWM<br>LED7[2] | PWM<br>LED7[1] | PWM<br>LED7[0] | Register 1 for setting LED7 PWM (Subordinate bit setting) |

| 0FH         | R/W | 00h           | SETPWM<br>72  | -              | -              | -              | -              | -              | -              | PWM<br>LED7[9] | PWM<br>LED7[8] | Register 2 for setting LED7 PWM (Superior bit setting)    |

| 10H         | R/W | 00h           | SETPWM<br>81  | PWM<br>LED8[7] | PWM<br>LED8[6] | PWM<br>LED8[5] | PWM<br>LED8[4] | PWM<br>LED8[3] | PWM<br>LED8[2] | PWM<br>LED8[1] | PWM<br>LED8[0] | Register 1 for setting LED8 PWM (Subordinate bit setting) |

| 11H         | R/W | 00h           | SETPWM<br>82  | -              | -              | -              | -              | -              | -              | PWM<br>LED8[9] | PWM<br>LED8[8] | Register 2 for setting LED8 PWM (Superior bit setting)    |

All registers are reset by each condition below.

- ①UVLO(VREG) < 2.9V(typ.)

- ②UVLO(EXT) < 1.9V(typ.)

- 3Thermal shutdown detection (Tj>175°C)

- ④Register PWMRST=1( exclude PWMRST itself)

### ●ADDR=00h

PWMCNT(PWM Control register : Read/Write)

| Bit           | 7      | 6        | 5        | 4        | 3        | 2        | 1       | 0     |

|---------------|--------|----------|----------|----------|----------|----------|---------|-------|

| Register name | PWMRST | not_used | not_used | not_used | not_used | not_used | PARADRV | PWMEN |

| Initial value | 0      | 0        | 0        | 0        | 0        | 0        | 0       | 0     |

| PWMEN | PWM mode control  |

|-------|-------------------|

| 0     | disable (Default) |

| 1     | PWM mode enable   |

| PARADRV | LED output control                                 |  |  |  |

|---------|----------------------------------------------------|--|--|--|

| 0       | To control LED1-LED8 independently                 |  |  |  |

| 1       | To control LED1and 2, LED3 and 4, LED5 and 6, LED7 |  |  |  |

|         | and 8 simultaneously                               |  |  |  |

| PWMRST | PWM logic reset control   |

|--------|---------------------------|

| 0      | Normal Function (Default) |

| 1      | Logic reset               |

When it makes PWMRST = '1', PWM Logic and all registers (the PWMRST register is excluded) is reset.

To make normal operation, it is necessary to reset if make PWMRST= '0'.

When it makes PARADRV= '1', because LED1 and LED2 (LED3 and LED4, LED5 and LED6, LED7 and LED8) operate synchronously (following the setting of LED of odd number turn), when you use the output of LED1 and LED2 (LED3and LED4, LED5 and LED6, LED7 and LED8) by short-circuiting, it operates as each heavy-current driver of ILEDMAX=300mA.

#### ●ADDR=01h

LEDEN(LED ON/OFF Control register : Read/Write)

| Bit           | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|---------------|--------|--------|--------|--------|--------|--------|--------|--------|

| Register name | LED8EN | LED7EN | LED6EN | LED5EN | LED4EN | LED3EN | LED2EN | LED1EN |

| Initial value | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

| LED1(~8)EN | LED1 (~8) output control |

|------------|--------------------------|

| 0          | OFF (Default)            |

| 1          | Usual ON                 |

When doing PWM modulated light with PWMEN of ADDR=00h, if LED1 of ADDR=01h (8) EN is designated as 1, it becomes regular ON. (LED1 (8) EN takes precedence.) So after that, if LED1 (8) EN is designated as 0, it returns to the PWM modulated light that is set at beginning.

#### ●ADDR=02h

SETPWM11(Register 1 for setting LED1 PWM (Subordinate bit setting): Read/Write)

|               | - 9     |        | 1       |         |         |         |         |         |

|---------------|---------|--------|---------|---------|---------|---------|---------|---------|

| Bit           | 7       | 6      | 5       | 4       | 3       | 2       | 1       | 0       |

| Register      | PWMLED1 | PWMLED | PWMLED1 | PWMLED1 | PWMLED1 | PWMLED1 | PWMLED1 | PWMLED1 |

| name          | [7]     | 1[6]   | [5]     | [4]     | [3]     | [2]     | [1]     | [0]     |

| Initial value | 0       | 0      | 0       | 0       | 0       | 0       | 0       | 0       |

### ●ADDR=03h

SETPWM12((Register 2 for setting LED1 PWM (superior bit setting) : Read/Write)

| Bit           | 7        | 6        | 5        | 4        | 3        | 2        | 1              | 0              |

|---------------|----------|----------|----------|----------|----------|----------|----------------|----------------|

| Register name | not used | PWMLED1<br>[9] | PWMLED1<br>[8] |

| Initial value | 0        | 0        | 0        | 0        | 0        | 0        | 0              | 0              |

It sets Duty of PWM modulated light with the total 10bit of Bit70 of ADDR=02h and Bit1-0 of ADDR=03h. To set the subordinate position 8bit with ADDR=02h and the Superior position 2bit with ADDR=03h. (Chart below)

| PWMLED1<br>[9:0] | LED1 Pulse width        |

|------------------|-------------------------|

| "000000000"      | Usual 'L' (Default)     |

| "000000001"      | PWMCLK 1 Clock width    |

| "0000000010"     | PWMCLK 2 Clock width    |

| "000000011"      | PWMCLK 3 Clock width    |

| ~                | ~                       |

| "1111111100"     | PWMCLK 1020 Clock width |

| "1111111101"     | PWMCLK 1021 Clock width |

| "1111111110"     | PWMCLK 1022 Clock width |

| "1111111111"     | PWMCLK 1023 Clock width |

# ●ADDR=04h~11h

The setting method is similar to LED1 of ADDR=02h,03h is described above with the PWM pulse width setting register of LED28.

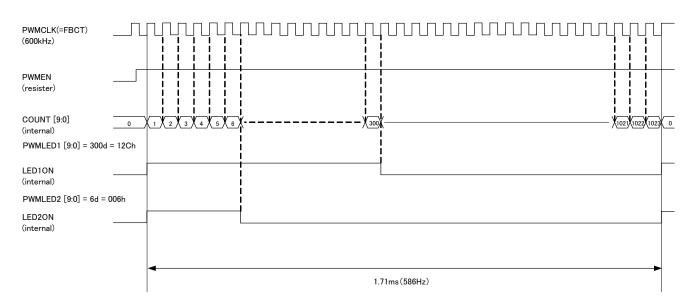

#### **PWM Setting example**

- When count [ 9:0 ] becomes 1, LEDON will become High and then LED lights up. When COUNT [ 9:0 ] reaches to the value that is set by PWM pulse, LEDON will become Low and the light goes out.

- ※ COUNT [9:0] =1 with Illumination timing of each channel becomes being identical.

- When setting of pwm modulated light is modified, it is reflected being at the point where COUNT [ 9:0 ] is reset to 0 (It is not immediately reflection with register entry)

- O Register setting example of LED illuminations

- When illuminates LED3 and LED8 regular (100% illumination)

- ① (ADDR,DATA)=(01h,84h)

- → Operation of regular illumination

- When it does PWM modulated light with 40% to LED3, and 80% to LED8,

1024 × 40%=409 , 1024 × 80%=819

Because (409)DEC=(199)HEX, (819)DEC=(333)HEX

$\bigcirc$  (ADDR,DATA)=(06h,99h)

(ADDR,DATA)=(07h,01h)

→Setting LED3 to 40%

② (ADDR,DATA)=(10h, 33h)

(ADDR, DATA) = (11h, 03h)

→Setting LED8 to 80%

③ (ADDR,DATA)=(00h,01h)

→Operation of modulated light

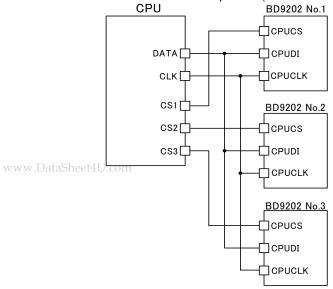

# O The method connected control wire when plural IC is used

Connected method of the control wire when plural BD9202EFS is controlled with one CPU is shown. You connect CPUCLK and CPUDI in parallel (note the ability of respective drive), CPUCS wires in each BD9202EFS.

#### OBooster DC/DC Controller

LED Series Numeric

It detects the LED cathode voltage, or the LED voltage, and controls the output voltage to be 0.75 (Typ.). The booster only operates when the LED output is operating. When multiple LED outputs are operating, the LED VF controls the LED output of the highest line to be 0.75V (Typ.). Therefore, the voltages of other LED outputs are higher by the variation of VF. Furthermore, you must be aware that the LED inline numerics have the following limits. At open detection, 85% of the OVP configured voltage becomes the trigger, so the maximum value of output voltage during normal operation is

$51V=60 \times 0.85$ , and 51V/VF>maximum N.

Over voltage Protection Circuit OVP

Inputs the output voltage to the OVP terminal with resistive divide. The configured value of OVP should be determined by the series numeric of the LED and the VF variance. When determining the OVP configured voltage, the open detection trigger, OVP × 0.85 should be considered. The switching operation stops when OVP is detected. Furthermore, if the output voltage falls to 80% of the OVP configuration voltage within the filter time tcp1 determined by CP1, OVP is released. If OVP continues for over tcp1, the error detection flag FAIL1 turns to Low, it latches with the switching operation in the stopped position.

When the output voltage side is ROVP1 and the GND side is ROVP2, the OVP detection voltage is:

VOVP=(ROVP1+ROVP2)/ROVP2 × 2.0V

When ROVP1=560k  $\Omega$  and ROVP2=20k  $\Omega$ , OVP activates when VOUT=58V or more.

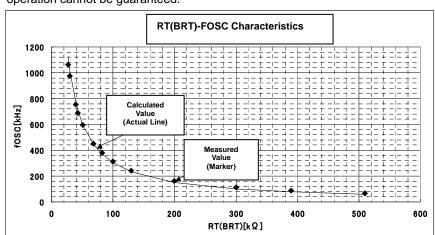

Booster DC/DC Converter Oscillation Frequency and LED Driver PWM Standard Frequency By attaching resistance to RT (BRT), it is possible to configure triangular wave oscillation frequency. The RT (BRT) determines the charge and discharge current corresponding to the internal condenser, and the frequency changes. Configure the RT (BRT) resistance by referring to the theoretical formula below. We recommend a range of  $30k\Omega$  ~ $300k\Omega$ . Configurations outside of the frequency range in the chart below can result in stopping switching, and operation cannot be guaranteed.

$$fosc = \frac{3.04 \times 10^4}{RT(BRT)[k\Omega]}[kHz]$$

- Internal Oscillation Frequency Output Terminal CT\_SYNC\_OUT and External Synchronous Terminal CT\_SYNC\_IN The internal oscillation frequency output terminal CT\_SYNC\_ OUT outputs the internal oscillator's clock configured by the RT terminal. However, there is no output when there is a CLK input in the external synchronous terminal CT\_SYNC\_IN. The external synchronous terminal CT\_SYNC\_IN can be the operational frequency of the DC/DC converter by externally inputting CLK. At this time, the external input frequency should be configured to be higher than the internal oscillation frequency. Furthermore, there should be no switching between the external synchronous and internal oscillator during operation.

- Soft Start

There is no soft start function with this IC. At startup, stand-up occurs with control by the current value configured by OCP (over-current detection).

Over-current Protection Circuit (OCP)

The current flowing through the coil is changed to voltage by the sense resistance Rcs, and when the CS terminal is over 0.2V (typ), the switching operation is stopped.

OCP detection is in pulse-by-pulse format, and is detected at every switching cycle and reset at the next clock.

When detection continues longer than the time configured at tCP1, FAIL1=L and it latches with the switching operation www.DataShin the stopped position.

#### O Error Detection Output Function

Outputs errors detected by protection circuits to FAIL1 and FAIL2 terminals. FAIL1 or FAIL2 switch to Low after the

filter time configured at CP1 or CP2, when they detect OVP or OCP (FAIL1) or LED open/short (FAIL2). (Because

FAIL1 terminal is open collector output, it is used with external pull-up.)

The filter time for CP1 and CP2 is expressed as:

$$Tcp1(cp2) = \frac{Ccp1 \times 2V}{1\mu A}$$

#### [Protection Functions]

| Protection Function | Detection             | Release               | Type       | Logic at detection |       |

|---------------------|-----------------------|-----------------------|------------|--------------------|-------|

| Flotection Function | Detection             | Release               | туре       | FAIL1              | FAIL2 |

| UVLO (VREG)         | VREG<2.9V             | VREG>3.0V             | Hysteresis | Н                  | Н     |

| UVLO (EXT)          | UVLO<1.9V             | UVLO>2.0V             | Hysteresis | Н                  | Н     |

| TSD                 | Tj>175℃               | Tj<150℃               | Hysteresis | Н                  | Н     |

| OVP                 | VOVP>2.0V &<br>t>tCP1 | VOVP<1.5V             | Latch      | L                  | Н     |

| OCP                 | VCS≧0.2V &<br>t>tCP1  | VCS<0.2V              | Latch      | L                  | Н     |

| LED open detection  | VLED<0.2V & VOVP>1.7V | VLED>0.2V & VOVP<1.6V | Latch      | Н                  | L     |

| LED short detection | VLED≧4.0V             | VLED<4.0V             | Latch      | Н                  | L     |

To clear the latch type, the logic section must be reset.

| Protection Function    | Operation at protection function detection |        |                  |                  |  |  |

|------------------------|--------------------------------------------|--------|------------------|------------------|--|--|

| Protection Function    | DCDC                                       | LOADSW | LED Dr           | Internal logic   |  |  |

| UVLO (VREG)            | Stop                                       | ON     | All CH stop      | Reset            |  |  |

| UVLO (EXT)             | Stop                                       | ON     | All CH stop      | Reset            |  |  |

| TSD                    | Stop                                       | ON     | All CH stop      | Reset            |  |  |

| OVP                    | Stop                                       | OFF    | (All CH stop) *2 | Normal operation |  |  |

| OCP                    | Current limit                              | OFF    | Normal operation | Normal operation |  |  |

| LED open detection *1  | Stop                                       | ON     | All CH stop      | Normal operation |  |  |

| LED short detection *1 | Stop                                       | ON     | All CH stop      | Normal operation |  |  |

- \*1 LED open and short detection is only valid with operating channels, and all CH turn to OFF when 1-ch error is detected. Furthermore, it is only valid in the ON areas during PWM operation.

- \*2 Because the DC/DC converter stops and there is no voltage supply for the LED, the light will be turned off.

#### Selection of External Parts

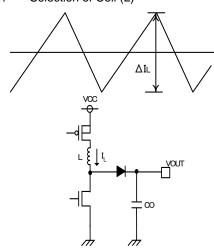

# 1. Selection of Coil (L)

The value of the coil greatly affects the input ripple current. As presented in formula (1), the larger the coil and the higher the switching frequency, the lower the ripple current.

$$\Delta IL = \frac{(VOUT - VcO) \times Vcc}{L \times VOUT \times f} [A] \qquad \cdots \qquad (1)$$

When efficiency is expressed as in formula (2), the input peak current is as shown in formula (3).

$$\eta = \frac{VOUT \times IOUT}{Vcc \times Icc} \qquad \cdots \qquad (2)$$

$$ILMAX = Icc + \frac{\Delta IL}{2} = \frac{VOUT \times IOUT}{Vcc \times \eta} + \frac{\Delta IL}{2} \cdot \cdot \cdot \cdot (3)$$

- If current that is stronger than the coil's fixed current value flows through the coil, there is magnetic saturation in the coil, lowering efficiency.

- A margin large enough should be considered during selection, so that the peak current does not exceed the coil's fixed current value.

- X To lessen loss from the coil and improve efficiency, coils with low resistance components (DCR and ACR) should be selected.

## 2. Selection of Output Condenser (Co)

The stability domain of the output voltage and equivalent series resistance necessary to smooth out the ripple voltage should be considered when choosing a condenser for the output side.

The output ripple voltage is determined by formula (4).

$$\Delta VOUT = ILMAX \times RESR + \frac{1}{Co} \times \frac{IOUT}{\eta} \times \frac{1}{f} [V] \qquad \cdots \qquad (4)$$

( $\Delta$ IL: output ripple current, ESR: equivalent series resistance of Co,  $\eta$ : efficiency)

%The condenser's fixed value should be selected with enough margin for the output voltage.

## 3. Selection of Input Condenser (Cin)

The input condenser selected should have low ESR with enough capacity to be compatible large ripple current, in order to prevent large transient voltage. The ripple current IRMS can be derived from formula (5).

$$IRMS = IOUT \times \frac{)(VOUT - VCC)}{VOUT} \times VOUT$$

$$[A] \qquad \cdots \qquad (5)$$

Furthermore, because it relies heavily on the characteristics of the power used for input, the wiring pattern on the substrate and MOSFET gate drain capacity, the usage temperature, load range and MOSFET conditions must be adequately confirmed.

### 4. Selection of MOSFET for Load Switch, and its Soft Start

Because there are no switches on the route between the VCC and the VO with regular boost applications, in case of an output short circuit the coil or rectification diode may be damaged. To prevent this from happening, a PMOSFET load switch should inserted between the VCC and the coil. PMOSFET with better ability to withstand pressure between gate-source and drain-source than VCC should be selected.

To initiate soft start of the load switch, insert capacity between the gate and source.

# 5. Selection of Switching MOSFET

There are no problems as long as the absolute maximum rating of the current rating is L and the pressure threshold and rectification diode of C are at least VF, but in order to actualize high-speed switching, one with small gate capacity (injected charge amount) should be selected.

- \* Excess of over current protection configuration recommended

- \* Higher efficiency can be gained if one with smaller ON resistance is selected.

#### 6. Selection of Rectification Diode

Select a Schottky barrier diode with higher current ability than the current rating of L and higher reverse pressure threshold than the threshold of C, particularly with low forward voltage VF.

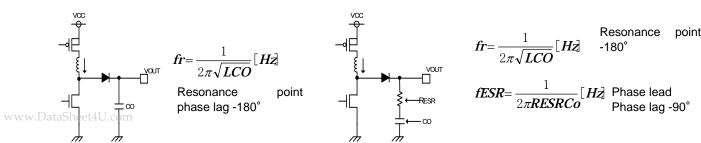

#### Phase Compensation Configuration Method

# Stability of Applications

Feedback stability conditions for reverse feedback are as follows:

Phase-lag of less than 150° (phase margin of over 30°) when gain is 1 (0dB)

Furthermore, DC/DC converter applications have been sampled by the switching frequency, so the GBW of the entire line is configured at less than 1/10 of the switching frequency. To sum up, the characteristics aimed for by applications are as outlined below:

- Phase-lag less than 150° (phase margin over 30°) when gain is 1 (0dB)

- The GBW (frequency of gain 0dB) at that time is less than 1/10 of switching frequency

Therefore, to improve the response with GBW limitations, it is necessary to make the switching frequency higher.

The trick to secure stability by phase compensation is to cancel out the second phase lag  $(-180^{\circ})$  generated by LC resonance with two phase leads (insert two phase leads).

Phase leads are by the output condenser's ESR component or the error amp output Comp terminal's CR.

With DC/DC converter applications, there is always a LC resonance circuit at the output, so the phase lag at that section is  $180^{\circ}$ . If the output condenser has large ESR (several  $\Omega$ ), such as an aluminum electrolysis condenser, a phase lead of  $+90^{\circ}$  is generated, and the phase lag is  $-90^{\circ}$ . When using an output condenser with low ESR such as a ceramic condenser, insert R for the ESR component.

With the changes in phase characteristics by caused by ESR, the number of phase leads to be inserted is one.

The frequency configuration to insert phase lead should ideally be configured close to the LC resonance frequency in order to cancel LC resonance.

This configuration is for simplicity, and no detailed calculations have been carried out, so there are times when adjustments on the actual product are necessary. These characteristics change depending on substrate layout and load conditions, so ample confirmation is necessary during design for mass production.

#### Electricity Consumption Calculations

$Pc(N) = ICC*VCC + 2*Ciss*VREG*Fsw*Vcc*[VLED*N + \Delta Vf*(N-1)]*ILED*[VLED*N + \Delta Vf*(N-1)]*ILED*[VLED*N + \Delta Vf*(N-1)]*[VLED*N + \Delta Vf*($

ICC : Maximum circuit current

VCC : Power voltage

Ciss : External FET capacity

Vsw : SW gate voltage

Fsw : SW frequency

Rload : LOAD SW ON resistance

Iload : LOAD SW maximum inflowing current

$\begin{array}{lll} \text{VLED} & : \text{LED control voltage} \\ \text{N} & : \text{LED parallel numeric} \\ \Delta \, \text{Vf} & : \text{LED Vf variance} \\ \text{ILED} & : \text{LED output current} \\ \end{array}$

### <Sample calculation>

When Pc(8)=21mA × 30V+500pF × 5V × 600kHz × 30V+[0.95V × 8+  $\Delta$  Vf × 7] × 75mA  $\Delta$  Vf=1.2V (about 0.1V each), Pc(8)=0.63W+0.045W+1.2W =1.875W

Because this IC has a built-in driver circuit, there is a considerable amount of heat generated. Careful consideration is necessary for substrate and heat dissipation design.

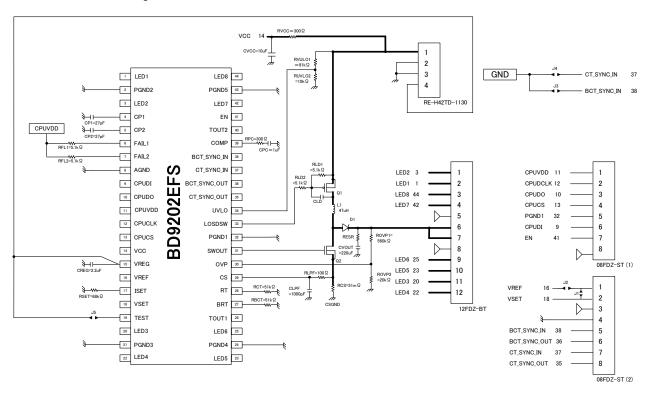

# ● PCB Board Circuit Diagram

- O The CVCC and CREG decoupling condensers should be placed as close as possible to the IC pin.

- O Because high current can flow through CSGND and PGND1~4, they should all be wired independently with low impedance.

- O Do not apply noise to 17-pin ISET, 18-pinVSET, 27-pin BRT, 28-pin RT and 39-pin COMP.

- O 1-pin LED, 3-pin LED2, 20-pin LED3, 22-pin LED4, 23-pin LED5, 25-pin LED6, 31-pin SWOUT, 35-pin CT\_CYNC\_OUT, 36-pin BCT\_SYNC\_OUT, 42-pin LED7 and 44-pin LED8 switch, so make sure they do not affect the surrounding pattern.

- O The thick-lined areas should be laid out as short as possible with broad pattern.

- During normal use, the jumper configurations are J1~J4=Short and J5=open.

# External Parts for PCB Board

| Name       | Туре              | Parts Number      | Connecting Point             | Size | Maker   | Pieces/Board |

|------------|-------------------|-------------------|------------------------------|------|---------|--------------|

| Connector  | For SPI/IF        | 22 05 2081        | -                            | -    | Molex   | 2            |

|            | For LED Board I/F | 22 05 2121        | -                            | -    | Molex   | 1            |

|            | For Power Supply  | 22 01 2045        | -                            | -    | Molex   | 1            |

| Ceramic    | -                 | -                 | CSS                          | 1005 | murata  | 1            |

|            | 27pF              | GRM1882C1H270JA01 | CP1, CP2                     | 1608 | murata  | 2            |

|            | 1000pF            | GRM15XB11H102KA86 | CLPF                         | 1005 | murata  | 1            |

|            | 10uF              | GRM55D31106KA87   | CVCC                         | 5750 | murata  | 1            |

|            | 2.2uF             | GRM188R71A225KE15 | CREG                         | 1608 | murata  | 1            |

|            | 1uF               | GRM188R71A105KA61 | CPC                          | 1608 | murata  | 1            |

|            | -                 | -                 | CLD                          | 3225 | murata  | 1            |

| Tantal     | 220uF             | UVR5A221MPD       | CVOUT                        | -    | Rubicon | 1            |

| Resistance | 5.1kΩ             | MCR03Series5101   | RLD1 , RLD2 ,<br>RFL1 , RFL2 | 1608 | ROHM    | 4            |

|            | -                 | -                 | RESR                         | 3216 | -       | 1            |

|            | 51mΩ              | MCR10SeriesR051   | RCS                          | 2012 | ROHM    | 1            |

|            | 100Ω              | MCR03Series1000   | RLPF                         | 1608 | ROHM    | 1            |

|            | 300Ω              | MCR03Series3000   | RPC , RVCC                   | 1608 | ROHM    | 1            |

|            | 10kΩ              | MCR03Series1002   | RUVLO2                       | 1608 | ROHM    | 1            |

|            | 20kΩ              | MCR03Series2002   | ROVP2                        | 1608 | ROHM    | 1            |

|            | 51kΩ              | MCR03Series5102   | RCT , RBCT                   | 1608 | ROHM    | 2            |

|            | 68kΩ              | MCR03Series6802   | RSET                         | 1608 | ROHM    | 1            |

|            | 91kΩ              | MCR03Series9102   | RUVLO1                       | 1608 | ROHM    | 1            |

|            | 560kΩ             | MCR03Series5603   | ROVP1                        | 1608 | ROHM    | 1            |

| PMOS       | -                 | RSS090P03FU6TB    | Q1                           | -    | ROHM    | 1            |

| NMOS       | -                 | TPC8213-H         | Q2                           | •    | TOSHIBA | 1            |

| Indactance | 47uH              | C12-K7.5L EJ      | L1                           | -    | Mitsumi | 1            |

| Diode      | -                 | RB160L-60TE25     | D1                           | -    | ROHM    | 1            |

The values above are fixed, and have been verified for operation at VCC=24V, LED12-series 8-parallel and ILED=150mA.

Therefore, the optimal values can vary depending on usage conditions, so fixed values should be determined with careful consideration.

# ●In/Output Equivalent Circuit 1

| 1.LED1 , 3.LED2 , 20.LED3 ,<br>22.LED4 , 23.LED5 , 25.LED6 ,<br>42.LED7 , 44.LED8 | 4.CP1 , 5.CP2       | 6.FAIL1 , 7.FAIL2   |

|-----------------------------------------------------------------------------------|---------------------|---------------------|

| LED1~8 100k                                                                       | OVP 100 3k          | 50<br>7V            |

| 9.CPUDI ,12.CPUCLK , 13.CPUCS                                                     | 10.CPUDO            | 15.VREG             |

| CPUVDD CPUVDD                                                                     | CPUVDD CPUVDD CPUDO | VREG 150k 765k 252k |

# ●In/Output Equivalent Circuit 2

| In/Output Equivalent Circuit 2   |                                             |                  |  |

|----------------------------------|---------------------------------------------|------------------|--|

| 16.VREF                          | 17.ISET                                     | 18.VSET          |  |

| VREG CL7V VREF                   | CL7V<br>ISET 500                            | CL7V<br>VSET 500 |  |

| 19.TEST                          | 26.TOUT1 , 35.CT_SYNC_OUT , 36.BCT_SYNC_OUT | 27.BRT , 28. RT  |  |

| TEST 30k                         | VREG VREG                                   | CL7V             |  |

| 29.CS                            | 30.OVP, 34.UVLO                             | 31.SWOUT         |  |

| CL7V  CS  100  5P  5k            | OVP 1k 5k                                   | VREG VREG SWOUT  |  |

| 33.LOADSW                        | 37.CT_SYNC_IN , 38.BCT_SYNC_IN              | 39.COMP          |  |

| LOADSW                           | VREG VREG                                   | COMP VREG        |  |

| 40.TOUT2                         | 41.EN                                       | CL7V             |  |

| DataSheet4U.com  Tout2  2k  100k | 172k 10k                                    | VCC CL7V         |  |

#### Usage Notes

#### 1.) Absolute Maximum Ratings

Although the quality of this product has been tightly controlled, deterioration or even destruction may occur if the absolute maximum ratings, such as for applied pressure and operational temperature range, are exceeded. Furthermore, we are unable to assume short or open mode destruction conditions. If special modes, which exceed the absolute maximum ratings, are expected, physical safely precautions such as fuses should be considered.

#### 2.) Reverse Connection of Power Supply Connector

The IC can destruct from reverse connection of the power supply connector. Precautions, such as inserting a diode between the external power supply and IC power terminal, should be taken as protection against reverse connection destruction.

#### 3.) Power Supply Line

Because there is a return of current regenerated by back EMF of the external coil, the capacity value should be determined after confirming that there are no problems with characteristics such as capacity loss at low temperatures with electrolysis condensers, for example by placing a condenser between the power supply and GND as a route for the regenerated current.

#### 4.) GND Potential

The potential of the GND pin should be at the minimum potential during all operation status

#### 5.) Heat Design

Heat design should consider power dissipation (Pd) during actual use and margins should be set with plenty of room.

#### 6.) Short-circuiting Between Terminals and Incorrect Mounting

When attaching to the printed substrate, pay special attention to the direction and proper placement of the IC. If the IC is attached incorrectly, it may be destroyed.

Destruction can also occur when there is a short, which can be caused by foreign objects entering between outputs or an output and the power GND.

#### 7.) Operation in Strong Magnetic Fields

Exercise caution when operating in strong magnet fields, as errors can occur.

#### 8.) ASO

When using this IC, it should be configured so that the output Tr should not exceed absolute maximum ratings and ASO. With CMOS ICs and ICs that have multiple power sources, there is a chance of rush current flowing momentarily, so exercise caution with power supply coupling capacity, power supply and width of GND pattern wiring and its layout.

#### 9.) Heat Interruption Circuit

This IC has a built-in Temperature Protection Circuit (TSD circuit). The temperature protection circuit (TSD circuit) is only to cut off the IC from thermal runaway, and has not been designed to protect or guarantee the IC. Therefore, the user should not plan to activate this circuit with continued operation in mind.

#### 10.) Inspection of Set Substrates

If a condenser is connected to a pin with low impedance when inspecting the set substrate, stress may be placed on the IC, so there should be a discharge after each process. Furthermore, when connecting a jig for the inspection process, the power must first be turned OFF before connection and inspection, and turned OFF again before removal.

# 11.) IC Terminal Input

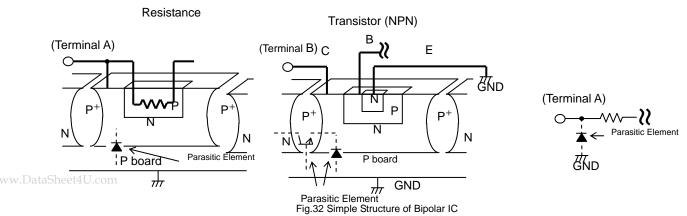

This IC is a monolithic IC, and between each element there is a P+ isolation and P substrate for element separation.

There is a P-N junction formed between this P-layer and each element's N-layer, which makes up various parasitic elements.

For example, when resistance and transistor are connected with a terminal as in figure 15:

OWhen GND>(terminal A) at the resistance, or GND>(terminal B) at the transistor (NPN), the P-N junction operates as a parasitic diode. OAlso, when GND>(terminal B) at the transistor, a parasitic NPN transistor operates by the N-layer of other elements close to the aforementioned parasitic diode.

With the IC's configuration, the production of parasitic elements by the relationships of the electrical potentials is inevitable. The operation of the parasitic elements can also interfere with the circuit operation, leading to malfunction and even destruction. Therefore, uses that cause the parasitic elements to operate, such as applying voltage to the input terminal that is lower than the GND (P-substrate), should be avoided.

#### 12.) Earth Wiring Pattern

Where there are both a small signal GND and a large current GND, it is recommended that large current GND pattern and small signal GND pattern are separated, and that there is an earth at the set's control point so that the pattern wiring's resistance and voltage change from the large current doesn't change the small signal GND's voltage. Ensure that the GND wiring patterns for external parts do not fluctuate.

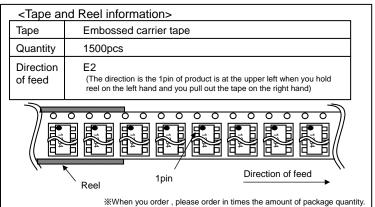

Selecting a Model Name When Ordering

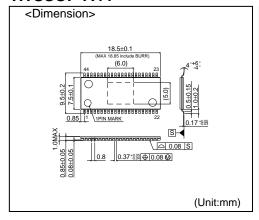

# HTSSOP-A44

### Notes

No copying or reproduction of this document, in part or in whole, is permitted without the consent of ROHM Co.,Ltd.

The content specified herein is subject to change for improvement without notice.

The content specified herein is for the purpose of introducing ROHM's products (hereinafter "Products"). If you wish to use any such Product, please be sure to refer to the specifications, which can be obtained from ROHM upon request.

Examples of application circuits, circuit constants and any other information contained herein illustrate the standard usage and operations of the Products. The peripheral conditions must be taken into account when designing circuits for mass production.

Great care was taken in ensuring the accuracy of the information specified in this document. However, should you incur any damage arising from any inaccuracy or misprint of such information, ROHM shall bear no responsibility for such damage.

The technical information specified herein is intended only to show the typical functions of and examples of application circuits for the Products. ROHM does not grant you, explicitly or implicitly, any license to use or exercise intellectual property or other rights held by ROHM and other parties. ROHM shall bear no responsibility whatsoever for any dispute arising from the use of such technical information.

The Products specified in this document are intended to be used with general-use electronic equipment or devices (such as audio visual equipment, office-automation equipment, communication devices, electronic appliances and amusement devices).

The Products specified in this document are not designed to be radiation tolerant.

While ROHM always makes efforts to enhance the quality and reliability of its Products, a Product may fail or malfunction for a variety of reasons.

Please be sure to implement in your equipment using the Products safety measures to guard against the possibility of physical injury, fire or any other damage caused in the event of the failure of any Product, such as derating, redundancy, fire control and fail-safe designs. ROHM shall bear no responsibility whatsoever for your use of any Product outside of the prescribed scope or not in accordance with the instruction manual.

The Products are not designed or manufactured to be used with any equipment, device or system which requires an extremely high level of reliability the failure or malfunction of which may result in a direct threat to human life or create a risk of human injury (such as a medical instrument, transportation equipment, aerospace machinery, nuclear-reactor controller, fuel-controller or other safety device). ROHM shall bear no responsibility in any way for use of any of the Products for the above special purposes. If a Product is intended to be used for any such special purpose, please contact a ROHM sales representative before purchasing.

If you intend to export or ship overseas any Product or technology specified herein that may be controlled under the Foreign Exchange and the Foreign Trade Law, you will be required to obtain a license or permit under the Law.

Thank you for your accessing to ROHM product informations.

More detail product informations and catalogs are available, please contact us.

# **ROHM Customer Support System**

http://www.rohm.com/contact/