## **Power Amplifier Bias and Control IC**

#### **Features**

- 2x 4 analog outputs with up to 50mA sourcing and 20mA sinking capability

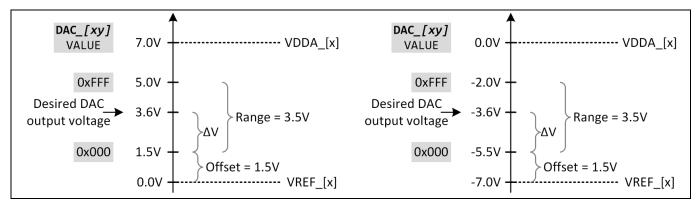

- 12 Bit DACs with programmable ranges:

- 0...3.5V and 0...7V

- bipolar range support: from -7...0V up to 0...7V

- o Programmable offset for range adaption

- o Internal voltage reference

- o Configurable tracking mode

- Optional temperature compensation of analog outputs via Look-Up Table (LUT)

- o Configurable gate bias compensation

- 2x 2 bias switches for time-division-duplex

(TDD) support with configurable clamp voltage:

- Fixed to VREF

- Neighbouring DAC (tracking opt.)

- Tracking clamping DAC

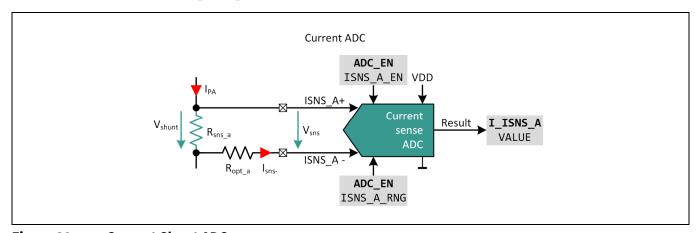

- 2x Current Shunt ADC

- 12 Bit SD ADC with internal reference

- Programmable Full-Scales: 15mV, 30mV, 60mV, 120mV, 240mV

- Offset compensated

- Floating input stage up to 60V common mode

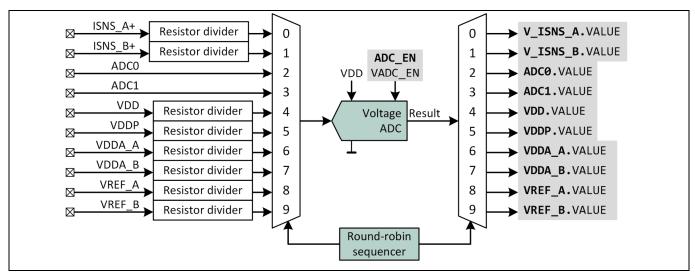

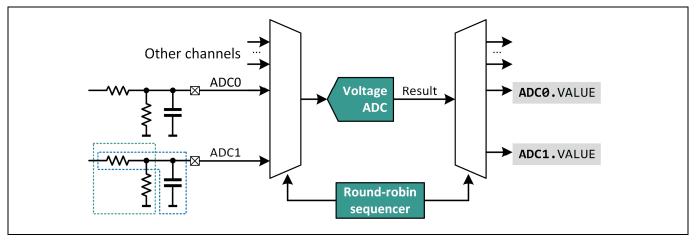

- Voltage ADC:

- o 11 Bit SAR ADC with internal reference

- Available Inputs:

- 2x 60V Full-Scale

- 2x 3V Full-Scale

- Supply pins

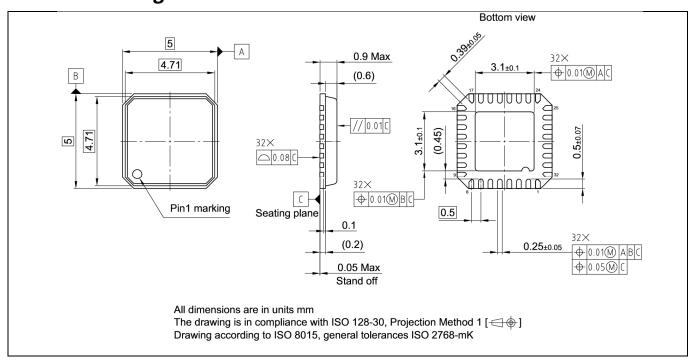

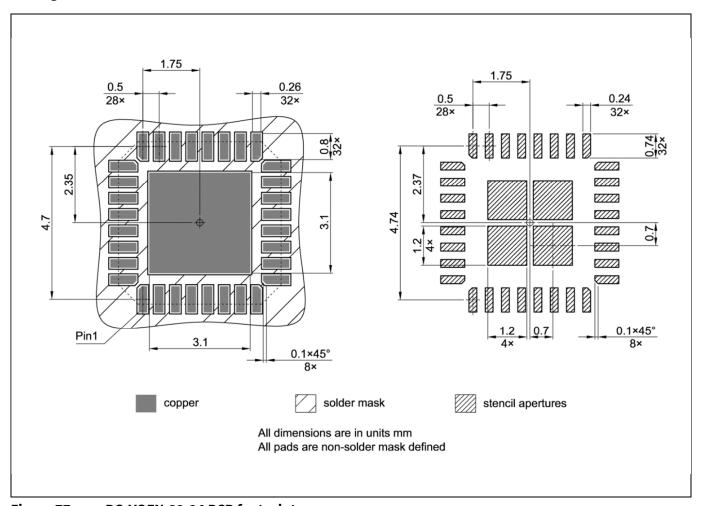

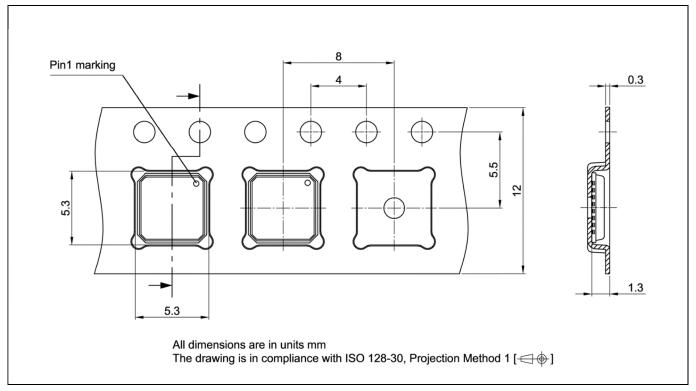

PG-VQFN-32 5x5mm<sup>2</sup>

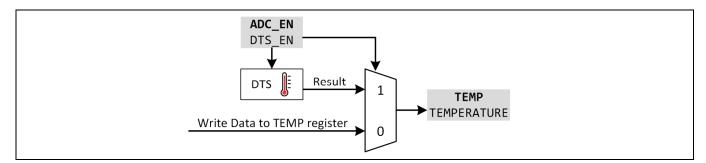

- Die Temperature Sensor

- o 9 bit resolution

- Measurement Range: -40°C to 160°C

- o 2.5°C accuracy

- Can be used for temperature compensation

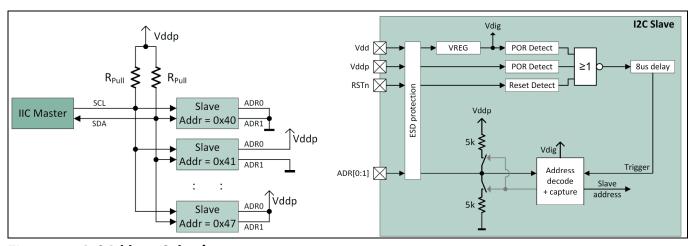

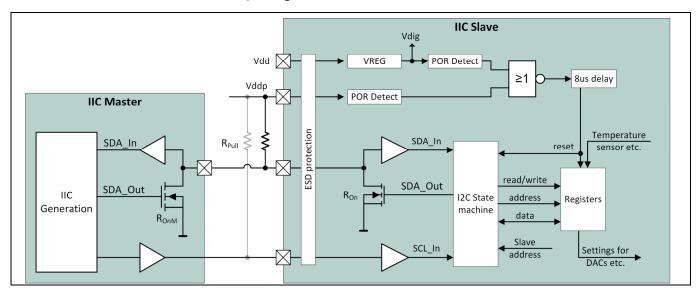

- I3C Serial Interface with I2C support

- SDR (12.5MBit/s) and HDR-DDR (25MBit/s) transmission modes supported

- Device ID selection via 3-state inputs

- Temperature Range (junction): -40°C to 150°C

# **Potential applications**

Cellular Base Stations: Bias & control circuit for power amplifiers

#### **Product validation**

Qualified for industrial applications according to the relevant tests of JEDEC47/20/22.

## **Description**

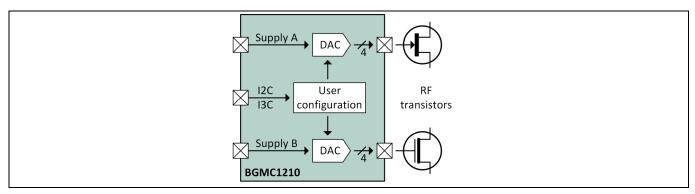

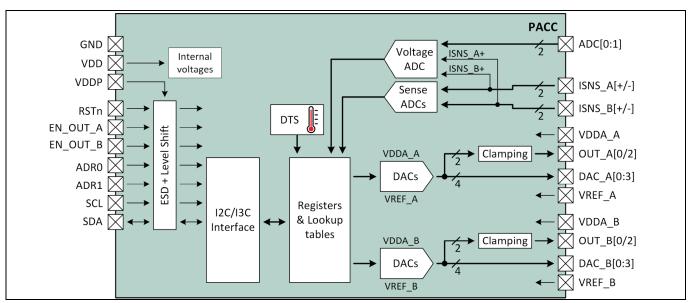

The BGMC1210 is a bias and control IC for Power Amplifiers (PA) that operate with negative Gate-Source voltages (e.g. GaN) and/or positive Gate-Source voltages (e.g. LDMOS). The BGMC1210 supports up to 2 PAs

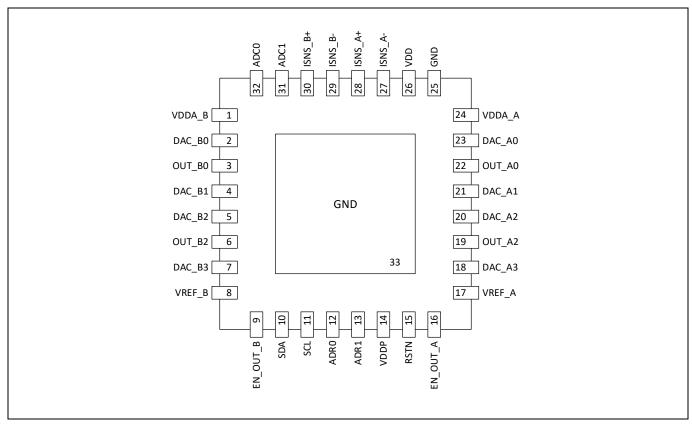

#### **Pin Configuration**

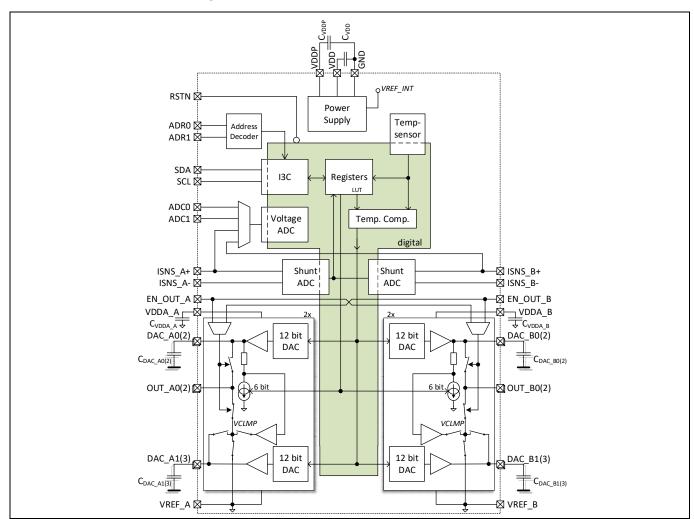

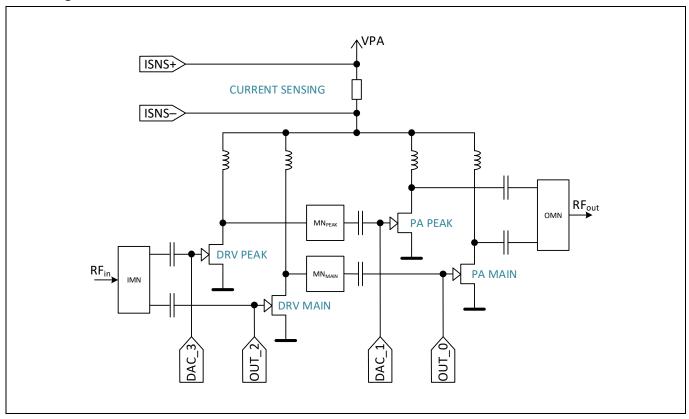

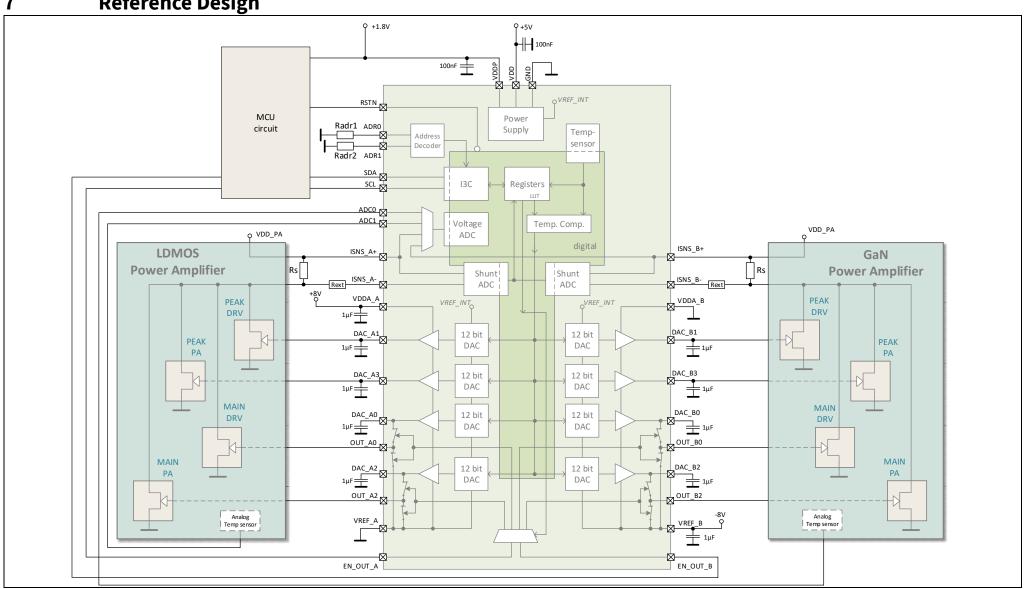

with 4 DAC outputs per each side of the IC. DACs have a resolution of 12 Bit each, supplied by an internal reference voltage and buffered by an amplifier providing up to 50mA driving current. Block diagram of the BGMC1210 is shown in Figure 1 and simplified typical PA application circuit is shown in Figure 2. The ranges and output voltages can be programmed via an I3C interface, which is backward compatible with I<sup>2</sup>C. The DACs are separated into two groups A and B, which can support independent output voltage ranges. Supported output voltage ranges are 0...7 V and 0...3.5 V, which can be offset into negative voltage domain depending on the selected DAC supply voltage for corresponding group at pins VREF\_A/VREF\_B and VDDA\_A/VDDA\_B. Thus, four DACs can support positive voltage range of 0...+7V or 0...+3.5V, whereas the other group of four DACs can support negative voltage range of -7...0V or -3.5...0V (or any range in between defined by lower DAC supply voltage at pins VREF\_A/VREF\_B, such as e.g. -6...+1). On top of that there is an OFFSET parameter, which allows to shift the voltage within the supply range.

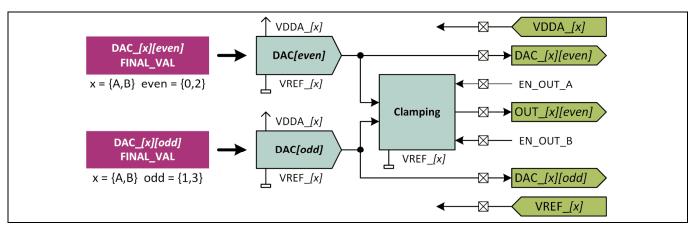

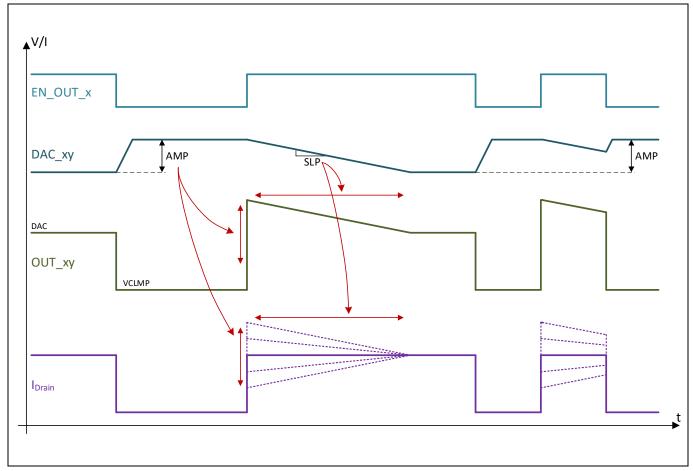

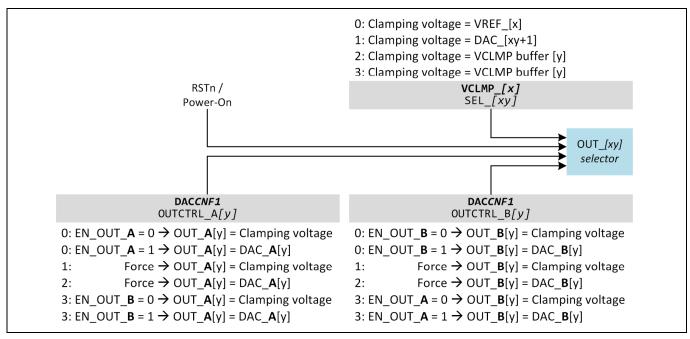

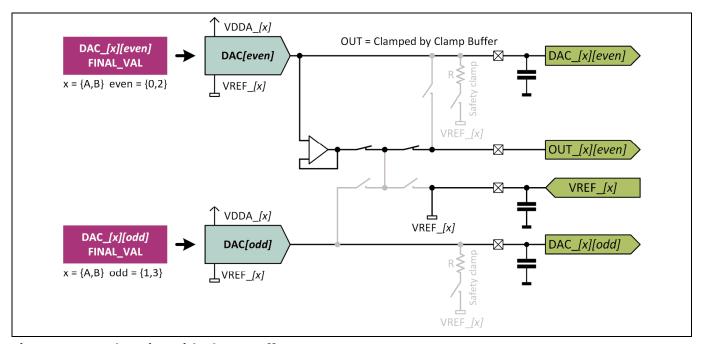

Biasing switches for Time-Division-Duplex (TDD) support are present on 2 outputs per side (OUT\_xy), directly controlled via dedicated pins  $EN_OUT_x$  (x = [A, B]; y = [0, 2]). The grouping of switched outputs by  $EN_OUT_x$  inputs can be defined. Clamping voltages for switched outputs can be set to a fixed VREF\_x potential,  $DAC_x1/DAC_x3$  output or a dedicated 6-bit clamping DAC voltage.

The output values of the DAC can be configured to compensate the power amplifier temperature drift via a Look-Up Table (LUT) and an integrated temperature sensor.

Figure 1 Functional Block Diagram

## **Pin Configuration**

Figure 2 Typical Power Amplifier application circuit

## **Power Amplifier Bias and Control IC**

## **Table of contents**

# **Table of contents**

| Featı                   | ures                                          | 1  |

|-------------------------|-----------------------------------------------|----|

| Pote                    | ential applications                           | 1  |

| Prod                    | luct validation                               | 1  |

| Desc                    | ription                                       | 1  |

| Table                   | e of contents                                 | 4  |

| 1                       | Pin Configuration                             |    |

| -<br>2                  | Absolute Maximum Ratings                      |    |

| 3                       | Specifications                                |    |

| <b>3</b> .1             | Operational Ratings                           |    |

| 3.2                     | ESD Ratings                                   |    |

| 3.2<br>3.3              | External components                           |    |

| 3.4                     | Thermal information                           |    |

| 3. <del>4</del><br>3.5  | Electrical characteristics                    |    |

| 3.5.1                   |                                               |    |

| 3.5.2                   |                                               |    |

| 3.5.2                   | 117                                           |    |

| 3.5.4                   | •                                             |    |

| 3.5.5                   |                                               |    |

| 3.5.6                   |                                               |    |

| 3.5.7                   | <b>3</b> .                                    |    |

| 3.5.8                   | ·                                             |    |

| 3.6                     | ESD Concept                                   |    |

| 4<br>4                  | Functional Description                        |    |

| <b>4.</b><br>4.1        | Overview                                      |    |

| 4.2                     | Functional Block Diagram                      |    |

| 4.3                     | Startup and Shutdown Procedure                |    |

| 4.3.1                   |                                               |    |

| 4.3.2                   | •                                             |    |

| 4.3.3                   |                                               |    |

| 4.3.4                   |                                               |    |

| 4.4                     | Operation Modes                               |    |

| 4.4.1                   | •                                             |    |

| 4.4.2                   |                                               |    |

| 4.5                     | DAC Output Voltage Configuration              |    |

| 4.5.1                   | 1 6 6                                         |    |

| 4.5.2                   |                                               |    |

| 4.6                     | DAC and OUT Voltages in Active Mode           |    |

| 4.6.1                   | •                                             |    |

| 4.6.2                   |                                               |    |

| 4.6.3                   |                                               |    |

| 4.6.4                   |                                               |    |

| 4.6.5                   | ·                                             |    |

|                         | ·                                             |    |

| 4.6.6                   | ) DAC value Step #4: Stope                    |    |

|                         | ·                                             |    |

| 4.6.6<br>4.6.7<br>4.6.8 | DAC Value Step #5: Clamp Compensation + Limit | 34 |

## **Power Amplifier Bias and Control IC**

## Table of contents

| 4.7.1  | Clamping Using VREF                         | 37 |

|--------|---------------------------------------------|----|

| 4.7.2  | Clamping Using Neighboring Odd DAC          | 37 |

| 4.7.3  | Clamping Using Clamp Buffer                 | 38 |

| 4.8    | Voltage ADC                                 | 39 |

| 4.9    | Current Shunt ADC                           | 40 |

| 4.10   | DTS: Die Temperature Sensor                 | 42 |

| 5      | Application and Implementation              | 43 |

| 5.1    | DAC Basic Settings Overview                 | 43 |

| 5.2    | DAC Value, Offset and Range                 | 44 |

| 5.3    | DAC Source/Sink Current Setting             | 45 |

| 5.4    | DAC Enable                                  | 45 |

| 6      | I2C/I3C Serial Digital Interface            | 46 |

| 6.1    | I2C Address Selection                       | 46 |

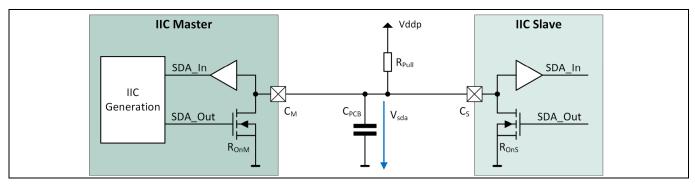

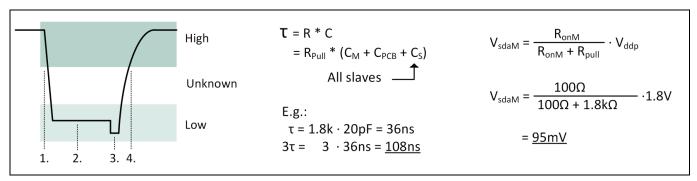

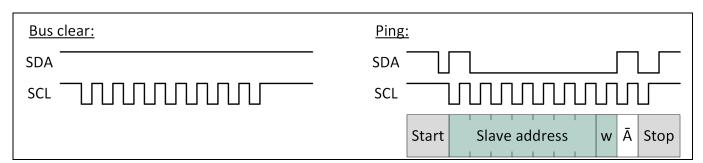

| 6.2    | I2C Design Considerations                   | 47 |

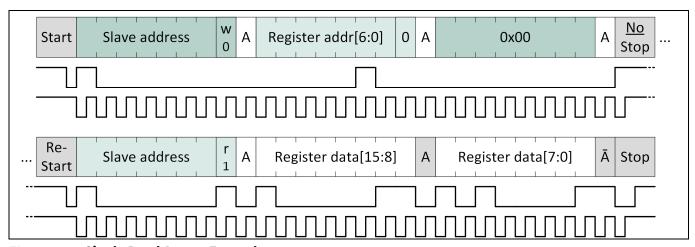

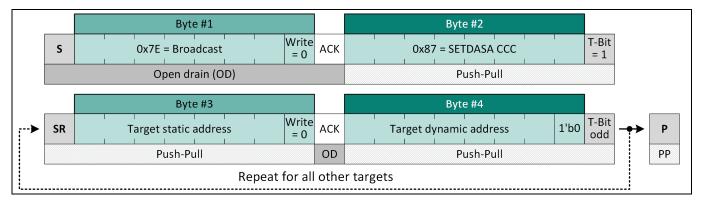

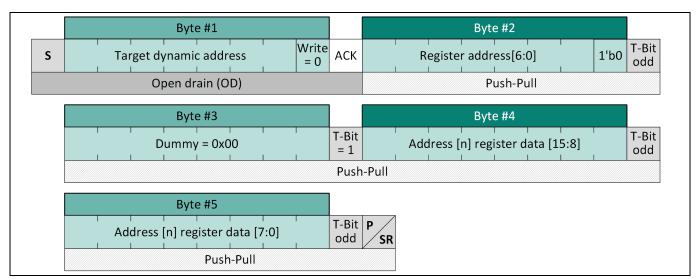

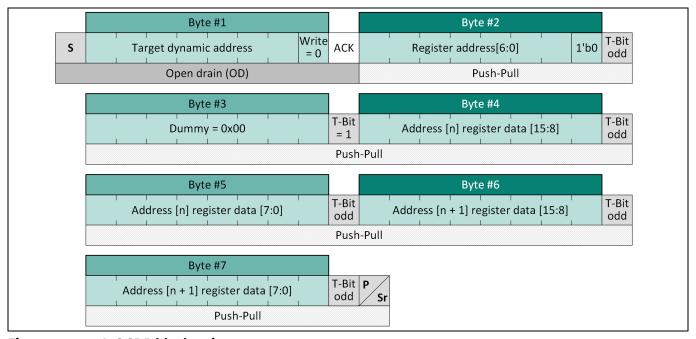

| 6.3    | I2C Communication                           | 49 |

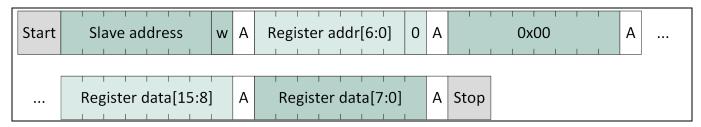

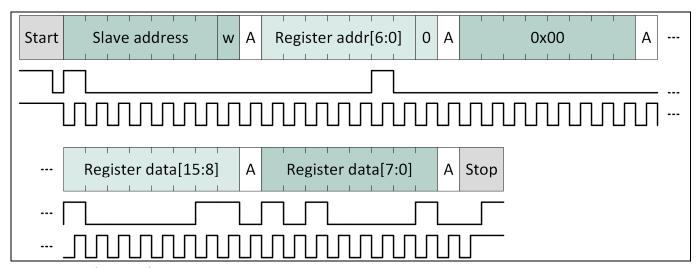

| 6.3.1  | I2C Dummy access                            | 49 |

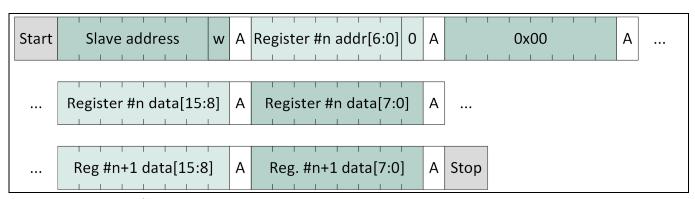

| 6.3.2  | I2C Write access                            | 50 |

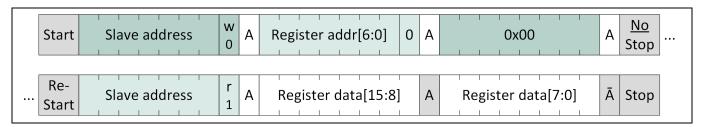

| 6.3.3  | I2C Read access                             | 51 |

| 6.4    | I3C Communication                           | 52 |

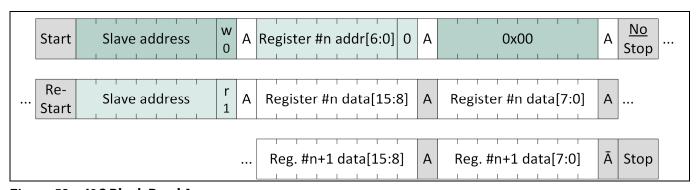

| 6.4.1  | I3C Target Information                      | 52 |

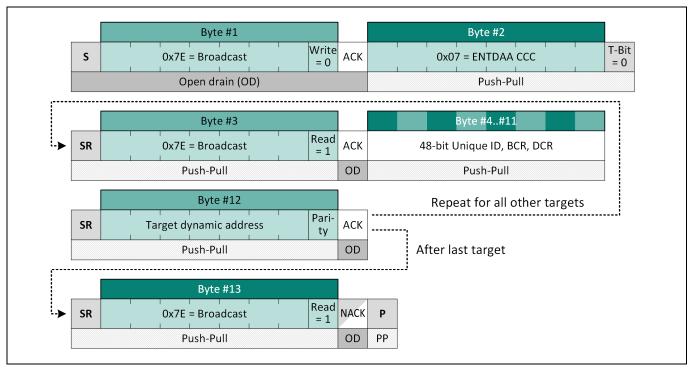

| 6.4.2  | I3C Dynamic Address assertion using ENTDAA  | 53 |

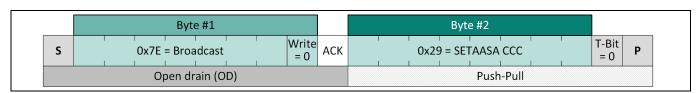

| 6.4.3  | I3C Dynamic Address assertion using SETDASA | 54 |

| 6.4.4  | I3C Dynamic Address assertion using SETAASA | 54 |

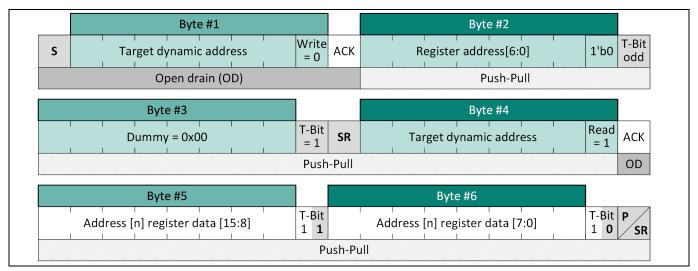

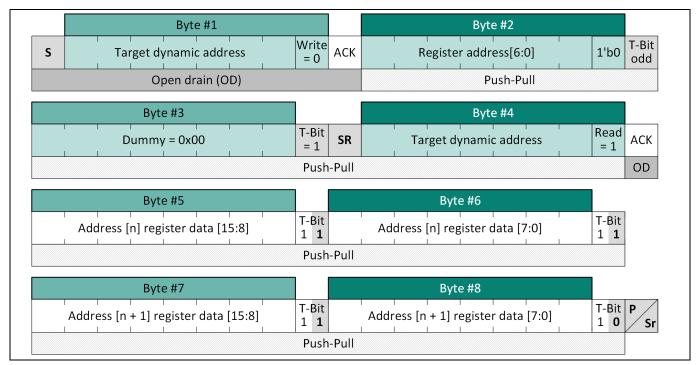

| 6.4.5  | I3C SDR read access                         | 55 |

| 6.4.6  | I3C SDR write access                        | 57 |

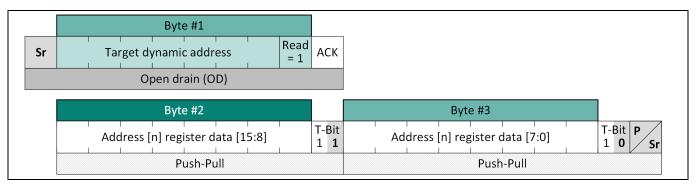

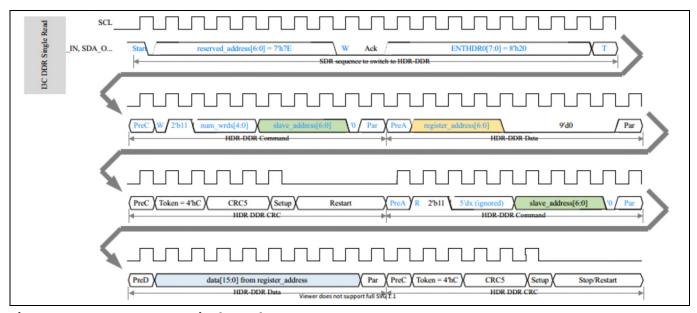

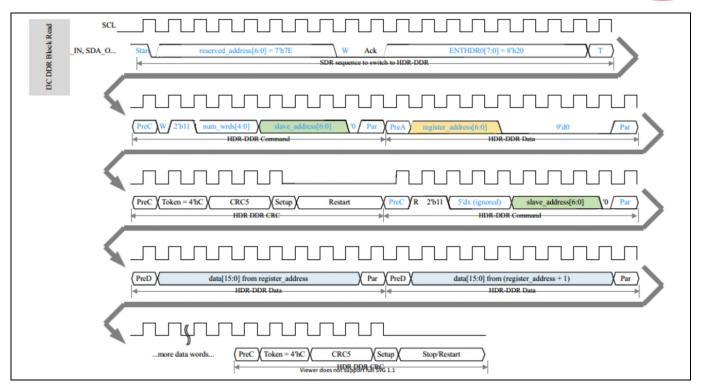

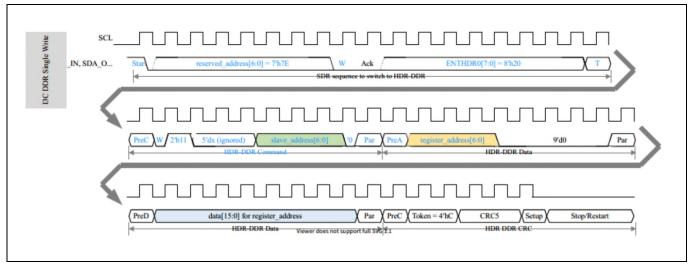

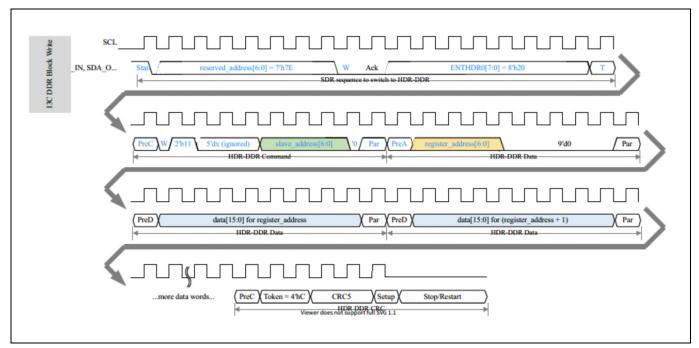

| 6.4.7  | 13C HDR DDR                                 | 58 |

| 6.4.8  | I3C HDR DDR read access                     | 58 |

| 6.4.9  | I3C HDR DDR write access                    | 60 |

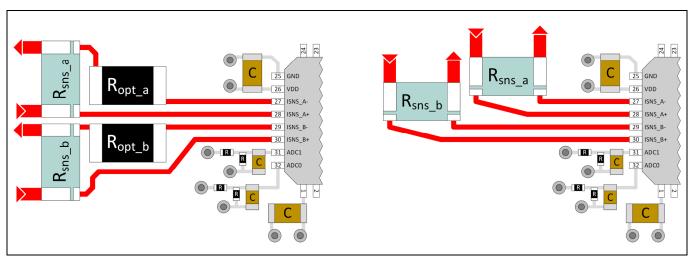

| 7      | Reference Design                            | 61 |

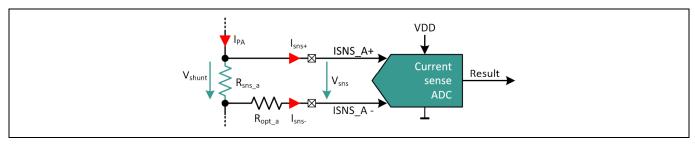

| 7.1    | Current Sense ADC                           | 62 |

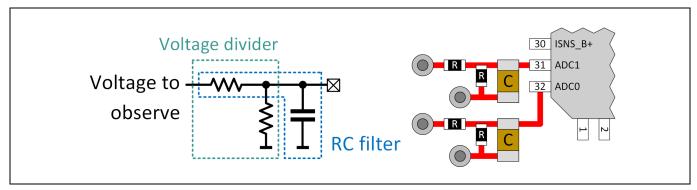

| 7.2    | Voltage ADC                                 | 63 |

| 7.3    | Digital Pins                                | 63 |

| 7.3.1  | RSTN Pin                                    | 63 |

| 7.3.2  | Address Pins ADR0/1                         | 64 |

| 7.3.3  | SCL/SDA Pins                                | 64 |

| 7.3.4  | EN_OUT_A/B Pins                             | 64 |

| 8      | Register Map                                | 65 |

| 8.1    | Register summary                            | 65 |

| 8.2    | Register details                            | 67 |

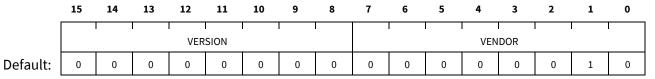

| 8.2.1  | VENDOR register                             | 67 |

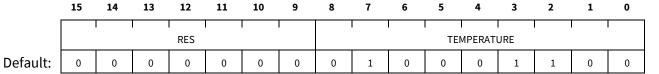

| 8.2.2  | TEMP register                               | 67 |

| 8.2.3  | V_ISNS_A register                           | 67 |

| 8.2.4  | V_ISNS_B register                           | 68 |

| 8.2.5  | ADC0 register                               | 68 |

| 8.2.6  | ADC1 register                               | 68 |

| 8.2.7  | VDD register                                | 69 |

| 8.2.8  | VDDP register                               | 69 |

| 8.2.9  | VDDA_A register                             | 69 |

| 8.2.10 | 0 VDDA_B register                           | 70 |

## **Power Amplifier Bias and Control IC**

## **Table of contents**

| 8.2.11   | Vref_A register       | 70 |

|----------|-----------------------|----|

| 8.2.12   | Vref_B register       | 70 |

| 8.2.13   | I_ISNS_A register     | 71 |

| 8.2.14   | I_ISNS_B register     | 71 |

| 8.2.15   | DAC feedback register | 71 |

| 8.2.16   | ADC enable register   | 72 |

| 8.2.17   | DACCNF1 register      | 73 |

| 8.2.18   | DACCNF2 register      | 73 |

| 8.2.19   | VCLMP_A register      | 74 |

| 8.2.20   | VCLMP_B register      | 74 |

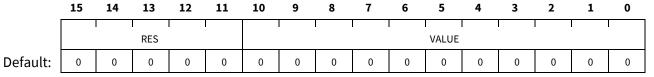

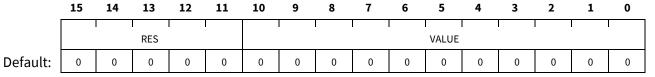

| 8.2.21   | DAC_A0 register       | 75 |

| 8.2.22   | DAC_A1 register       | 75 |

| 8.2.23   | DAC_A2 register       | 76 |

| 8.2.24   | DAC_A3 register       | 76 |

| 8.2.25   | DAC_B0 register       | 77 |

| 8.2.26   | DAC_B1 register       | 77 |

| 8.2.27   | DAC_B2 register       | 78 |

| 8.2.28   | DAC_B3 register       | 78 |

| 8.2.29   | TCLUT_A0_L register   | 79 |

| 8.2.30   | TCLUT_A0_H register   | 79 |

| 8.2.31   | TCLUT_A1_L register   | 80 |

| 8.2.32   | TCLUT_A1_H register   | 80 |

| 8.2.33   | TCLUT_A2_L register   | 80 |

| 8.2.34   | TCLUT_A2_H register   | 81 |

| 8.2.35   | TCLUT_A3_L register   | 81 |

| 8.2.36   | TCLUT_A3_H register   | 81 |

| 8.2.37   | TCLUT_B0_L register   | 82 |

| 8.2.38   | TCLUT_B0_H register   | 82 |

| 8.2.39   | TCLUT_B1_L register   | 83 |

| 8.2.40   | TCLUT_B1_H register   | 83 |

| 8.2.41   | TCLUT_B2_L register   | 83 |

| 8.2.42   | TCLUT_B2_H register   | 84 |

| 8.2.43   | TCLUT_B3_L register   | 84 |

| 8.2.44   | TCLUT_B3_H register   | 84 |

| 8.2.45   | CCOMP_A0 register     | 85 |

| 8.2.46   | CCOMP_A2 register     | 85 |

| 8.2.47   | CCOMP_B0 register     | 86 |

| 8.2.48   | CCOMP_B2 register     | 86 |

| 9 Pa     | ackage Information    | 87 |

| Davision | n history             | 90 |

**Pin Configuration**

# **1** Pin Configuration

Figure 3 Pin number assignment of BGMC1210

Table 1 Pin definition and function

| Pin# | Symbol   | Function | Description                                                                                                                                                                                                         |

|------|----------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | VDDA_B   | SUP      | Upper DAC supply voltage; depending on selected DAC output range, connects either to positive supply (positive gate voltages) or GND (negative gate voltages); side B                                               |

| 2    | DAC_B0   | DAC OUT  | DAC out; side B                                                                                                                                                                                                     |

| 3    | OUT_B0   | OUT      | Switched bias output; connects to DAC_B0 or VCLMP potential based on the level at configured EN_OUT_x, ( $x = [A, B]$ ); VCLMP can be defined by VREF_B, DAC_B1 or CLMP DAC based on register configuration; side B |

| 4    | DAC_B1   | DAC OUT  | DAC out; no switching; side B                                                                                                                                                                                       |

| 5    | DAC_B2   | DAC OUT  | DAC out; side B                                                                                                                                                                                                     |

| 6    | OUT_B2   | OUT      | Switched bias output; connects to DAC_B2 or VCLMP potential based on the level at configured EN_OUT_x, ( $x = [A, B]$ ); VCLMP can be defined by VREF_B, DAC_B3 or CLMP DAC based on register configuration; side B |

| 7    | DAC_B3   | DAC OUT  | DAC out; no switching; side B                                                                                                                                                                                       |

| 8    | VREF_B   | SUP      | Lower DAC supply / reference voltage; depending on selected DAC output range, connects either to GND (positive gate voltages) or negative supply (negative gate voltages); side B                                   |

| 9    | EN_OUT_B | IN       | Switch the configured OUT_xy outputs between DAC_xy and corresponding VCLMP potential ( $x = [A, B]$ ; $y = [0, 2]$ ); side B                                                                                       |

| 10   | SDA      | IN/OUT   | I3C/I <sup>2</sup> C data                                                                                                                                                                                           |

| 11   | SCL      | IN       | I3C/I <sup>2</sup> C clock                                                                                                                                                                                          |

## **Power Amplifier Bias and Control IC**

## **Pin Configuration**

| 12 | ADR0     | IN      | I3C/I <sup>2</sup> C Device ID, bit 0                                                                                                                                                                               |

|----|----------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13 | ADR1     | IN      | I3C/I <sup>2</sup> C Device ID, bit 1                                                                                                                                                                               |

| 14 | VDDP     | SUP     | Digital I/O pins supply rail                                                                                                                                                                                        |

| 15 | RSTN     | IN      | Asynchronous reset                                                                                                                                                                                                  |

| 16 | EN_OUT_A | IN      | Switch the configured OUT_xy outputs between DAC_xy and corresponding VCLMP potential ( $x = [A, B]$ ; $y = [0, 2]$ ); side A                                                                                       |

| 17 | VREF_A   | SUP     | Lower DAC supply / reference voltage; depending on selected DAC output range, connects either to GND (positive gate voltages) or negative supply (negative gate voltages); side A                                   |

| 18 | DAC_A3   | DAC OUT | DAC out; no switching; side A                                                                                                                                                                                       |

| 19 | OUT_A2   | OUT     | Switched bias output; connects to DAC_A2 or VCLMP potential based on the level at configured EN_OUT_x, ( $x = [A, B]$ ); VCLMP can be defined by VREF_A, DAC_A3 or CLMP DAC based on register configuration; side A |

| 20 | DAC_A2   | DAC OUT | DAC out; side A                                                                                                                                                                                                     |

| 21 | DAC_A1   | DAC OUT | DAC out; no switching; side A                                                                                                                                                                                       |

| 22 | OUT_A0   | OUT     | Switched bias output; connects to DAC_A0 or VCLMP potential based on the level at configured EN_OUT_x, (x = [A, B]); VCLMP can be defined by VREF_A, DAC_A1 or CLMP DAC based on register configuration; side A     |

| 23 | DAC_A0   | DAC OUT | DAC out; side A                                                                                                                                                                                                     |

| 24 | VDDA_A   | SUP     | Upper DAC supply voltage; depending on selected DAC output range, connects either to positive supply (positive gate voltages) or GND (negative gate voltages); side A                                               |

| 25 | GND      | SUP     | Ground connection                                                                                                                                                                                                   |

| 26 | VDD      | SUP     | Main supply voltage                                                                                                                                                                                                 |

| 27 | ISNS_A-  | ADC IN  | Differential current sensing ADC negative input; side A                                                                                                                                                             |

| 28 | ISNS_A+  | ADC IN  | Differential current sensing ADC positive input / Voltage ADC input; side A                                                                                                                                         |

| 29 | ISNS_B-  | ADC IN  | Differential current sensing ADC negative input; side B                                                                                                                                                             |

| 30 | ISNS_B+  | ADC IN  | Differential current sensing ADC positive input / Voltage ADC input; side B                                                                                                                                         |

| 31 | ADC1     | ADC IN  | Voltage ADC input 1                                                                                                                                                                                                 |

| 32 | ADC0     | ADC IN  | Voltage ADC input 0                                                                                                                                                                                                 |

| 33 | GND      | SUP     | Ground connection                                                                                                                                                                                                   |

## **Absolute Maximum Ratings**

# 2 Absolute Maximum Ratings

Table 2 Absolute Maximum Ratings 1,2

| Parameter                                             | Symbol /          | Values     |  |            |    | Note /     |

|-------------------------------------------------------|-------------------|------------|--|------------|----|------------|

|                                                       | Function          | Min. Typ.  |  | Max.       |    | Conditions |

| Main supply                                           | VDD               | -0.3       |  | 5.5        | V  |            |

| Pad supply                                            | VDDP              | -0.3       |  | 3.6        | V  |            |

| Positive DAC supply <sup>3</sup>                      | VDDA_x            | -0.3       |  | 8.0        | V  |            |

| Negative DAC supply/reference <sup>3</sup>            | VREF_x            | -8.0       |  | 0.3        | V  |            |

| DAC supply <sup>3</sup>                               | VDDA_x – VREF_x   | -0.3       |  | 8.0        | V  |            |

| Digital I/Os                                          | IN/OUT            | -0.3       |  | VDDP+0.3   | V  |            |

| DAC outputs <sup>3</sup>                              | DAC_xy            | VREF_x-0.3 |  | VDDA_x+0.3 | V  |            |

| Switched outputs <sup>3</sup>                         | OUT_xy            | VREF_x-0.3 |  | VDDA_x+0.3 | V  |            |

| Voltage ADC inputs                                    | ADC0/1            | -0.3       |  | 3.3        | V  |            |

| Current sense inputs <sup>3</sup>                     | ISNS_x+/-         | -0.3       |  | 60         | V  |            |

| Differential current sense input voltage <sup>3</sup> | ISNS_x+ - ISNS_x- | -1         |  | 1          | V  |            |

| Junction temperature                                  | T <sub>J</sub>    | -40        |  | 150        | °C |            |

| Storage temperature                                   | T <sub>STG</sub>  | -65        |  | 150        | °C |            |

<sup>&</sup>lt;sup>1</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability

<sup>&</sup>lt;sup>2</sup> All voltages are with respect to GND=0V unless otherwise noted. Currents are positive into and negative out of the specified terminal.

$<sup>^{3}</sup>$  x = [A, B]; y = [0, 1, 2, 3].

# **3** Specifications

# 3.1 Operational Ratings

Table 3 Operational Ratings<sup>2</sup>

| Parameter                                  | Symbol                 |      | Values | Unit | Note / |            |

|--------------------------------------------|------------------------|------|--------|------|--------|------------|

|                                            |                        | Min. | Тур.   | Max. |        | Conditions |

| Main supply                                | VDD                    | 3.1  | 3.3    | 5.5  | V      |            |

| Pad supply                                 | VDDP                   | 1.65 | 1.80   | 3.6  | V      |            |

| Positive DAC supply <sup>1</sup>           | VDDA_x                 | 0    |        | 8    | V      |            |

| Negative DAC supply/reference <sup>1</sup> | VREF_x                 | -8   |        | 0    | V      |            |

| DAC supply <sup>1</sup>                    | VDDA_x – VREF_x        | 3.1  |        | 8.0  | V      |            |

| ISNS inputs                                | ISNS_x+/-              | 0    |        | 60   | V      |            |

| ISNS input current                         | I <sub>ISNS_x+/-</sub> | -120 |        | 120  | mA     |            |

| Ramp rate supply, ISNS inputs              | $V_{ramp}$             |      |        | 10   | V/us   |            |

| Junction temperature                       | T <sub>J</sub>         | -40  |        | 150  | °C     |            |

$<sup>^{1}</sup> x = [A, B].$

## 3.2 ESD Ratings

Table 4 ESD Ratings<sup>1</sup>

| Parameter                                                                                                 | Symbol           |      | Value | Unit | Note / |            |

|-----------------------------------------------------------------------------------------------------------|------------------|------|-------|------|--------|------------|

|                                                                                                           |                  | Min. | Тур.  | Max. |        | Conditions |

| ESD robustness on all pins,<br>Human Body Model (HBM)<br>sensitivity as per<br>ANSI/ESDA/JEDEC JS-001     | V <sub>HBM</sub> | -2   |       | +2   | kV     |            |

| ESD robustness on all pins,<br>Charged Device Model (CDM)<br>sensitivity as per<br>ANSI/ESDA/JEDEC JS-002 | V <sub>CDM</sub> | -0.5 |       | +0.5 | kV     |            |

<sup>&</sup>lt;sup>1</sup> All voltages are with respect to GND=0V unless otherwise noted.

## 3.3 External components

**Table 5** External components

| Parameter                                     | Symbol              | Values               |      |                   | Unit | Note / Conditions                   |

|-----------------------------------------------|---------------------|----------------------|------|-------------------|------|-------------------------------------|

|                                               |                     | Min.                 | Тур. | Max.              |      |                                     |

| DAC load capacitance <sup>1</sup>             | C <sub>DAC_xy</sub> | 30 <sup>2</sup> /100 | 1000 | 1200 <sup>3</sup> | nF   |                                     |

| VDD buffer capacitor                          | C <sub>VDD</sub>    |                      | 100  |                   | nF   |                                     |

| VDDP buffer capacitor                         | C <sub>VDDP</sub>   |                      | 100  |                   | nF   |                                     |

| VDDA_x-VREF_x buffer capacitance <sup>1</sup> | C <sub>VDDA_x</sub> |                      | 1000 |                   | nF   | Connected between VDDA_x and VREF_x |

<sup>&</sup>lt;sup>2</sup> All voltages are with respect to GND=0V unless otherwise noted.

| Parameter                                                | Symbol              | Values |      |      | Unit | Note / Conditions                                                                                    |  |

|----------------------------------------------------------|---------------------|--------|------|------|------|------------------------------------------------------------------------------------------------------|--|

|                                                          |                     | Min.   | Тур. | Max. |      |                                                                                                      |  |

| OUT load capacitance for VCLMP buffer usage <sup>1</sup> |                     |        |      | 5    | nF   | Maximum load capacitance<br>for VCLMP buffer;<br>VCLMP_x.SET_xy = 10 <sub>b</sub> or 11 <sub>b</sub> |  |

| VADC input buffer capacitance                            | C <sub>ADC0/1</sub> |        | 10   |      | nF   | Noise filter                                                                                         |  |

$<sup>^{1}</sup>$  x = [A, B]; y = [0, 1, 2, 3].

## 3.4 Thermal information

Table 6 Thermal resistance

| Parameter                                           | Symbol |      | Values |      | Unit | Note /<br>Conditions |

|-----------------------------------------------------|--------|------|--------|------|------|----------------------|

|                                                     |        | Min. | Тур.   | Max. |      |                      |

| Thermal resistance between junction and bottom pad  | Rth_B  |      | 2.64   |      | K/W  |                      |

| Thermal resistance between junction and package top | Rth_T  |      | 35.4   |      | K/W  |                      |

## 3.5 Electrical characteristics

## 3.5.1 Gate biasing

Table 7 Electrical characteristics of gate biasing 2,3

| Parameter                      | Symbol                | Values |      |      | Unit | Note / Conditions                                                                                 |

|--------------------------------|-----------------------|--------|------|------|------|---------------------------------------------------------------------------------------------------|

|                                |                       | Min.   | Тур. | Max. |      |                                                                                                   |

| GATE BIASING DAC               | ·                     |        |      |      |      |                                                                                                   |

| DAC resolution                 | RES <sub>DAC</sub>    |        | 12   |      | bits |                                                                                                   |

| DAC full-scale range "low"     | FSR <sub>low</sub>    |        | 3.5  |      | V    | Referred to VREF_x, RNG='0'                                                                       |

| DAC full-scale range "high"    | FSR <sub>high</sub>   |        | 7    |      | V    | Referred to VREF_x, RNG='1'                                                                       |

| DAC gain error                 | Eg <sub>DAC</sub>     | -3     |      | +3   | %FSR |                                                                                                   |

| DAC differential non-linearity | DNL <sub>DAC</sub>    | -1.0   |      | 1.5  | LSB  | Monotonic                                                                                         |

| DAC temperature stability      | dV <sub>DAC</sub> /dT |        |      | 0.3  | mV/K |                                                                                                   |

| DAC source current             | I <sub>src</sub>      | 10     |      |      | mA   | Current flowing out of pins,<br>DAC_xy < VDDA_x - 0.2V <sup>1</sup>                               |

| DAC source current "high"      | I <sub>src,hi</sub>   | 50     |      |      | mA   | Current flowing out of pins,<br>high current mode enabled,<br>DAC_xy < VDDA_x - 1.0V <sup>1</sup> |

| DAC sink current               | I <sub>snk</sub>      | 8      |      |      | mA   | Current flowing into pins,<br>DAC_xy > VREF_x + 0.7V 1                                            |

| DAC sink current "high"        | I <sub>snk,hi</sub>   | 20     |      |      | mA   | Current flowing into pins,<br>high current mode enabled,<br>DAC_xy > VREF_x + 1.0V <sup>1</sup>   |

| DAC source current limitation  | I <sub>src,lim</sub>  |        | 20   |      | mA   | Current flowing out of pins,<br>DAC_xy < VDDA_x - 0.2V <sup>1</sup>                               |

<sup>&</sup>lt;sup>2</sup> Lower capacitance value is only valid if the load (DACCNF2.LD\_xy) is configured to "low capacitance".

$<sup>^3</sup>$  Maximum capacitance value can be exceeded (up to 15  $\mu$ F), but a sequential turn-on or a slow DACCNF1.SLP setting of the DACs is recommended in this case to avoid overheating.

# **Power Amplifier Bias and Control IC**

## **Specifications**

| Parameter                                              | Symbol                                     |      | Value | s    | Unit                                  | Note / Conditions                                                                                 |

|--------------------------------------------------------|--------------------------------------------|------|-------|------|---------------------------------------|---------------------------------------------------------------------------------------------------|

|                                                        |                                            | Min. | Тур.  | Max. |                                       |                                                                                                   |

| DAC source current limitation, "high"                  | I <sub>src,lim,hi</sub>                    |      | 70    |      | mA                                    | Current flowing out of pins,<br>high current mode enabled,<br>DAC_xy < VDDA_x - 1.0V <sup>1</sup> |

| DAC sink current limitation                            | I <sub>snk,lim</sub>                       |      | 13    |      | mA                                    | Current flowing into pins,<br>DAC_xy > VREF_x + 0.7V 1                                            |

| DAC sink current limitation, "high"                    | I <sub>snk,lim,hi</sub>                    |      | 30    |      | mA                                    | Current flowing into pins,<br>high current mode enabled,<br>DAC_xy > VREF_x + 1.0V <sup>1</sup>   |

| DAC static load regulation                             | $dV_{DAC}/dI_{DAC}$                        | 0.0  | 0.7   | 1.9  | mV/<br>mA                             | $VREF_x + 1V < V_{DAC}$ $V_{DAC} < VDDA_x - 1V^1$                                                 |

| BIAS SWITCHES                                          |                                            |      |       |      |                                       |                                                                                                   |

| OUT transmission resistance                            | R <sub>trans</sub>                         |      | 3.5   | 5    | Ω                                     | OUT_xy is connected to DAC_xy, DAC_xy > VREF_x + 1.5V, IDC = 10mA 1                               |

| OUT transmission resistance variation over Temperature | dR <sub>trans</sub> /dT                    |      |       | 12   | mΩ/<br>K                              | OUT_xy is connected to DAC_xy, DAC_xy > VREF_x + 1.5V, IDC = 10mA 1                               |

| OUT clamping resistance                                | R <sub>clamp</sub>                         |      |       | 15   | Ω                                     | OUT_xy is connected to VREF_x, I <sub>DC</sub> = 10mA <sup>1</sup>                                |

| OUT transient peak current                             | I <sub>OUT,peak</sub>                      | -200 |       | 200  | mA                                    | for pulses shorter than 100 ns                                                                    |

| CLAMP DAC (DAC enabled)                                |                                            |      |       |      |                                       |                                                                                                   |

| CLAMP DAC resolution                                   | RES <sub>CLMP</sub>                        |      | 6     |      | bit                                   |                                                                                                   |

| CLAMP DAC full scale range                             | FSR <sub>CLMP</sub>                        |      | 1.42  |      | V                                     | referred to DAC_x0(2) <sup>1</sup>                                                                |

| CLAMP DAC LSB size                                     | LSB <sub>CLMP</sub>                        |      | 22.5  |      | mV                                    |                                                                                                   |

| CLAMP DAC gain error                                   | Eg <sub>CLMP</sub>                         | -5   |       | 5    | %FSR                                  | $I_{OUT_xy} = 0 \text{mA}^{1}$                                                                    |

| CLAMP DAC sink current                                 | I <sub>CLMPsnk</sub>                       |      |       | 30   | mA                                    | OUT_xy > VREF_x + 1.5V 1                                                                          |

| CLAMP DAC current limitation                           | I <sub>CLMPsnk,lim</sub>                   |      | 50    |      | mA                                    |                                                                                                   |

| CLAMP DAC static load regulation                       | dV <sub>CLMP</sub> /<br>dI <sub>CLMP</sub> |      |       | 15   | mV/<br>mA                             | EN_OUT_x = 0,<br>I <sub>OUT,snk</sub> =020mA,<br>OUT_xy > VREF_x + 1.5V <sup>1</sup>              |

| CLAMP DAC disabled/unsupplied                          |                                            | _    |       | _    |                                       |                                                                                                   |

| CLMP DAC sink current                                  | I <sub>CLMPsnk_dis</sub>                   | 12   | 25    |      | mA                                    | OUT_xy > VREF_x + 2V 1                                                                            |

| ·                                                      | ·                                          |      |       | ·    | · · · · · · · · · · · · · · · · · · · | · · · · · · · · · · · · · · · · · · ·                                                             |

$<sup>^{1}</sup>$   $\overline{x = [A, B]; y = [0, 1, 2, 3]}$ .

$<sup>^{\</sup>rm 2}$  All voltages are with respect to GND=0V unless otherwise noted.

$<sup>^3</sup>$  The minimum and maximum limits are valid over the full operational range and are ensured by characterization and statistical correlation. Typical values are tested at ambient temperature  $T_A = 25$  °C.

## 3.5.2 Supply monitoring

Table 8 Electrical characteristics of supply monitoring <sup>2,3</sup>

| Parameter                                  | Symbol                        |      | Values |      | Unit | Note / Conditions |  |  |

|--------------------------------------------|-------------------------------|------|--------|------|------|-------------------|--|--|

|                                            |                               | Min. | Тур.   | Max. |      |                   |  |  |

| VDD UVLO release                           | UVLO <sub>VDD,rel</sub>       | 2.6  | 2.8    | 3    | V    |                   |  |  |

| VDD UVLO lock                              | UVLO <sub>VDD,lck</sub>       | 2.5  | 2.7    | 2.9  | V    |                   |  |  |

| VDD UVLO hysteresis                        | UVLO <sub>VDD,hys</sub>       |      | 100    |      | mV   |                   |  |  |

| VDDA_x-VREF_x UVLO<br>release <sup>1</sup> | UVLO <sub>VDDA-VREF,rel</sub> | 2.6  | 2.8    | 3    | V    |                   |  |  |

| VDDA_x-VREF_x UVLO lock1                   | UVLO <sub>VDDA-VREF,lck</sub> | 2.5  | 2.7    | 2.9  | V    |                   |  |  |

| VDDA_x-VREF_x UVLO<br>hysteresis¹          | UVLO <sub>VDDA-VREF,hys</sub> |      | 100    |      | mV   |                   |  |  |

| VDDP UVLO release                          | UVLO <sub>VDDP,rel</sub>      | 1.50 | 1.55   | 1.60 | V    |                   |  |  |

| VDDP UVLO lock                             | UVLO <sub>VDDP,lck</sub>      | 1.45 | 1.50   | 1.55 | V    |                   |  |  |

| VDDP UVLO hysteresis                       | UVLO <sub>VDDP,hys</sub>      | 30   | 50     | 70   | mV   |                   |  |  |

$<sup>^{1}</sup>$  x = [A, B]; y = [0, 1, 2, 3].

## 3.5.3 Temperature sensor

Table 9 Electrical characteristics of temperature sensor <sup>1</sup>

| Parameter             | Symbol             |      | Values |      | Unit | Note / Conditions |

|-----------------------|--------------------|------|--------|------|------|-------------------|

|                       |                    | Min. | Тур.   | Max. |      |                   |

| DTS resolution        | RES <sub>DTS</sub> |      | 9      |      | bits |                   |

| DTS measurement range | RNG <sub>DTS</sub> | -40  |        | 160  | °C   |                   |

| DTS absolute error    | E <sub>DTS</sub>   | -2.5 |        | 2.5  | °C   |                   |

<sup>&</sup>lt;sup>1</sup> The minimum and maximum limits are valid over the full operational range and are ensured by characterization and statistical correlation. Typical values are tested at ambient temperature T<sub>A</sub> = 25 °C.

## 3.5.4 Voltage ADC

Table 10 Electrical characteristics of VADC <sup>2,3</sup>

| Parameter                           | Symbol                   |      | Values |      | Unit  | Note / Conditions                              |

|-------------------------------------|--------------------------|------|--------|------|-------|------------------------------------------------|

|                                     |                          | Min. | Тур.   | Max. | 1     |                                                |

| VADC resolution                     | RES <sub>VADC</sub>      |      | 11     |      | bit   |                                                |

| VADC full-scale range<br>ADC0/1     | FSR <sub>VADC,ADC</sub>  |      | 3.07   |      | V     |                                                |

| VADC full-scale range<br>ISNS_x+1   | FSR <sub>VADC,ISNS</sub> |      | 61.46  |      | V     | ISNS voltages must not exceed ISNS_x+/- = 60 V |

| VADC differential non-<br>linearity | DNL <sub>VADC</sub>      | -1   |        | 2    | LSB11 |                                                |

| VADC gain error ADC0/1              | Eg <sub>VADC,ADC</sub>   | 0    |        | 1.5  | %     |                                                |

<sup>&</sup>lt;sup>2</sup> All voltages are with respect to GND=0V unless otherwise noted.

<sup>&</sup>lt;sup>3</sup> The minimum and maximum limits are valid over the full operational range and are ensured by characterization and statistical correlation. Typical values are tested at ambient temperature T<sub>A</sub> = 25 °C.

## **Power Amplifier Bias and Control IC**

## **Specifications**

| Parameter                | Symbol                  |      | Values |      | Unit  | Note / Conditions |

|--------------------------|-------------------------|------|--------|------|-------|-------------------|

|                          |                         | Min. | Тур.   | Max. |       |                   |

| VADC gain error ISNS_x+1 | Eg <sub>VADC,ISNS</sub> | 0    |        | 2.0  | %     |                   |

| VADC offset error        | Eo <sub>VADC</sub>      | -3   |        | 3    | LSB11 |                   |

$<sup>^{1}</sup>$  x = [A, B]; y = [0, 1, 2, 3].

## 3.5.5 Current shunt ADC

Table 11 Electrical characteristics of CSA <sup>2,3</sup>

| Parameter                 | Symbol                  |      | Values |      | Unit | Note / Conditions                                                                     |

|---------------------------|-------------------------|------|--------|------|------|---------------------------------------------------------------------------------------|

|                           |                         | Min. | Тур.   | Max. |      |                                                                                       |

| CSA resolution            | RES <sub>CSA</sub>      |      | 12     |      | bit  |                                                                                       |

| CSA input range 0         | RNG <sub>CSA,rng0</sub> |      | 15     |      | mV   | ADCEN.ISNS_x_RNG=000 <sub>b</sub> <sup>1</sup>                                        |

| CSA LSB size range 0      | LSB <sub>CSA,rng0</sub> |      | 9.4    |      | μV   | ADCEN.ISNS_x_RNG=000 <sub>b</sub> <sup>1</sup>                                        |

| CSA input range 1         | RNG <sub>CSA,rng1</sub> |      | 30     |      | mV   | ADCEN.ISNS_x_RNG=001 <sub>b</sub> <sup>1</sup>                                        |

| CSA LSB size range 1      | LSB <sub>CSA,rng1</sub> |      | 18.8   |      | μV   | ADCEN.ISNS_x_RNG=001 <sub>b</sub> <sup>1</sup>                                        |

| CSA input range 2         | RNG <sub>CSA,rng2</sub> |      | 60     |      | mV   | ADCEN.ISNS_x_RNG=010 <sub>b</sub> <sup>1</sup>                                        |

| CSA LSB size range 2      | LSB <sub>CSA,rng2</sub> |      | 37.6   |      | μV   | ADCEN.ISNS_x_RNG=010 <sub>b</sub> <sup>1</sup>                                        |

| CSA input range 3         | RNG <sub>CSA,rng3</sub> |      | 120    |      | mV   | ADCEN.ISNS_x_RNG=011 <sub>b</sub> <sup>1</sup>                                        |

| CSA LSB size range 3      | LSB <sub>CSA,rng3</sub> |      | 75.2   |      | μV   | ADCEN.ISNS_x_RNG=011 <sub>b</sub> <sup>1</sup>                                        |

| CSA input range 4         | RNG <sub>CSA,rng4</sub> |      | 240    |      | mV   | ADCEN.ISNS_x_RNG≥100 <sub>b</sub> <sup>1</sup>                                        |

| CSA LSB size range 4      | LSB <sub>CSA,rng4</sub> |      | 150.4  |      | μV   | ADCEN.ISNS_x_RNG≥100 <sub>b</sub> <sup>1</sup>                                        |

| CSA sample rate           | SR <sub>CSA</sub>       |      | 20     |      | kS/s |                                                                                       |

| CSA offset error side A   | Eo <sub>CSA_A</sub>     | -250 |        | 100  | uV   |                                                                                       |

| CSA offset error side B   | Eo <sub>CSA_B</sub>     | -100 |        | 250  | uV   |                                                                                       |

| CSA gain error            | Eg <sub>CSA</sub>       | -1.5 |        | 1.5  | %FSR |                                                                                       |

| SNDR input ranges 0 and 1 | SNDR <sub>0/1</sub>     | 50   |        |      | dB   | ADCEN.ISNS_x_RNG=000 <sub>b</sub> /<br>ADCEN.ISNS_x_RNG=001 <sub>b</sub> <sup>1</sup> |

| SNDR input ranges 2 and 3 | SNDR <sub>2/3</sub>     | 56   |        |      | dB   | ADCEN.ISNS_x_RNG=010 <sub>b</sub> /<br>ADCEN.ISNS_x_RNG=011 <sub>b</sub> <sup>1</sup> |

| SNDR input range 4        | SNDR <sub>4</sub>       | 62   |        |      | dB   | ADCEN.ISNS_x_RNG=100 <sub>b</sub> <sup>1</sup>                                        |

$<sup>^{1}</sup>$  x = [A, B]; y = [0, 1, 2, 3].

<sup>&</sup>lt;sup>2</sup> All voltages are with respect to GND=0V unless otherwise noted.

<sup>&</sup>lt;sup>3</sup> The minimum and maximum limits are valid over the full operational range and are ensured by characterization and statistical correlation. Typical values are tested at ambient temperature T<sub>A</sub> = 25 °C.

<sup>&</sup>lt;sup>2</sup> All voltages are with respect to GND=0V unless otherwise noted.

<sup>&</sup>lt;sup>3</sup> The minimum and maximum limits are valid over the full operational range and are ensured by characterization and statistical correlation. Typical values are tested at ambient temperature T<sub>A</sub> = 25 °C.

## 3.5.6 Timing parameters

Table 12 Timing parameters <sup>2</sup>

| Parameter                      | Symbol                  |      | Values | 5    | Unit | Note / Conditions                                                                                            |

|--------------------------------|-------------------------|------|--------|------|------|--------------------------------------------------------------------------------------------------------------|

|                                |                         | Min. | Тур.   | Max. |      |                                                                                                              |

| Reset pulse width              | t <sub>reset</sub>      | 80   |        |      | ns   |                                                                                                              |

| Rampup time                    | t <sub>rampup</sub>     |      |        | 180  | μs   | RSTN is tied to VDDP, VDD and VDDP are abov UVLO threshold. Time until interface is ready to accept commands |

| Startup time                   | t <sub>start</sub>      |      |        | 10   | μs   | RSTN transision from 0 to 1 until interface is ready to accept commands                                      |

| BIAS SWITCHES                  |                         |      |        |      |      |                                                                                                              |

| OUT propagation delay clamping | t <sub>clamp</sub>      |      |        | 300  | ns   | C <sub>OUT</sub> =0nF, time measure<br>from OUT_EN_x change<br>until 10% of final value <sup>1</sup>         |

| OUT propagation delay enable   | t <sub>prop,en</sub>    |      |        | 300  | ns   | C <sub>OUT</sub> =0nF, time measure<br>from OUT_EN_x change<br>until 10% of final value <sup>1</sup>         |

| ADC                            | •                       |      |        | -    | 1    |                                                                                                              |

| VADC startup time              | t <sub>VADC,start</sub> | 35   | 47     | 59   | μs   | from VADC_EN=1 until<br>first result (I_ISNS_A) is<br>available                                              |

| VADC round robin time          | $t_{VADC,round}$        | 17   | 23     | 29   | μs   | Full conversion cycle of all 10 channels                                                                     |

| CSA                            |                         |      |        |      |      |                                                                                                              |

| CSA startup time               | t <sub>CSA,start</sub>  | 43   | 57     | 71   | μs   |                                                                                                              |

| CSA conversion time            | t <sub>CSA,conv</sub>   | 38.4 | 51.2   | 64.0 | μs   |                                                                                                              |

| DTS                            |                         |      |        |      |      |                                                                                                              |

| DTS startup Time               | t <sub>DTS,start</sub>  | 3.15 | 4.2    | 5.25 | ms   |                                                                                                              |

| DTS conversion Time            | t <sub>DTS,conv</sub>   | 3    | 4      | 5    | ms   |                                                                                                              |

$<sup>^{1}\</sup>overline{x = [A, B]}; y = [0, 1, 2, 3].$

$<sup>^2</sup>$  The minimum and maximum limits are valid over the full operational range and are ensured by characterization and statistical correlation. Typical values are tested at ambient temperature  $T_A = 25 \, ^{\circ}C$ .

## 3.5.7 Current consumption

Table 13 Current consumption <sup>1</sup>

| Parameter                                  | Symbol                   |      | Values |      | Unit | Note / Conditions                                                                                            |

|--------------------------------------------|--------------------------|------|--------|------|------|--------------------------------------------------------------------------------------------------------------|

|                                            |                          | Min. | Тур.   | Max. |      |                                                                                                              |

| VDD current consumption, in RESET          | I <sub>VDD,reset</sub>   |      | 200    |      | μΑ   | RSTN pin = '0'                                                                                               |

| VDD current consumption, in ACTIVE         | I <sub>VDD,active</sub>  |      | 4      | 7    | mA   | RSTN pin = '1', VADC and<br>CSA enabled, all DACs<br>enabled, no DC loads at<br>DAC outputs                  |

| VDDA / VREF current consumption, in RESET  | I <sub>VDDA,reset</sub>  |      | 300    |      | μΑ   | RSTN pin = '0';<br>per one side                                                                              |

| VDDA / VREF current consumption, in ACTIVE | I <sub>VDDA,active</sub> |      | 4.2    |      | mA   | RSTN pin = '1', VADC and<br>CSA enabled, all DACs<br>enabled, no DC loads at<br>DAC outputs;<br>per one side |

| VDDP current consumption                   | I <sub>VDDP</sub>        |      | 1      |      | mA   | Depending on communication traffic                                                                           |

<sup>&</sup>lt;sup>1</sup> The minimum and maximum limits are valid over the full operational range and are ensured by characterization and statistical correlation. Typical values are tested at ambient temperature T<sub>A</sub> = 25 °C.

# 3.5.8 Digital Interface

Table 14 Electrical Characteristics Digital Logic 1,2

| Parameter                    | Symbol                |            | Values |          | Unit | Note / Conditions              |

|------------------------------|-----------------------|------------|--------|----------|------|--------------------------------|

|                              |                       | Min.       | Тур.   | Max.     |      |                                |

| High-level input voltage     | V <sub>IH</sub>       |            |        | 0.7·VDDP | V    |                                |

| Low-level input voltage      | V <sub>IL</sub>       | 0.3·VDDP   |        |          | V    |                                |

| High-level output voltage    | V <sub>OH</sub>       | VDDP - 0.1 |        |          | V    | VDDP = 1.65 V3.6 V<br>I = 1 mA |

| Low-level output voltage     | V <sub>OL</sub>       |            |        | 0.1      | V    | VDDP = 1.65 V3.6 V<br>I = 1 mA |

| xternal ADR0/1 pull resistor | ADR <sub>PULL</sub>   | 0          |        | 100      | Ohm  |                                |

| Reset pulse duration         | RST <sub>active</sub> | 80         |        |          | ns   |                                |

<sup>&</sup>lt;sup>1</sup> The minimum and maximum limits are valid over the full operational range and are ensured by characterization and statistical correlation. Typical values are tested at ambient temperature T<sub>A</sub> = 25 °C.

<sup>&</sup>lt;sup>2</sup> All voltages are with respect to GND=0V unless otherwise noted.

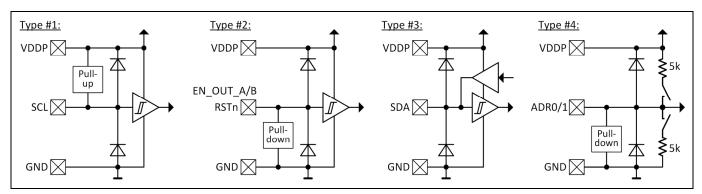

## 3.6 ESD Concept

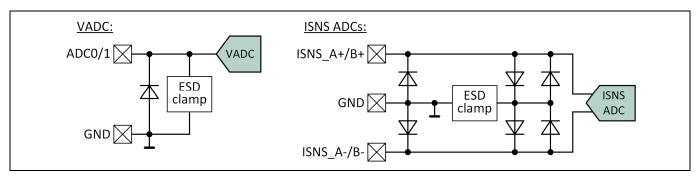

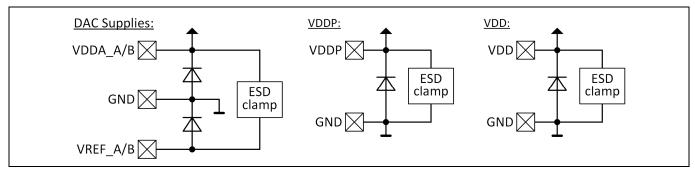

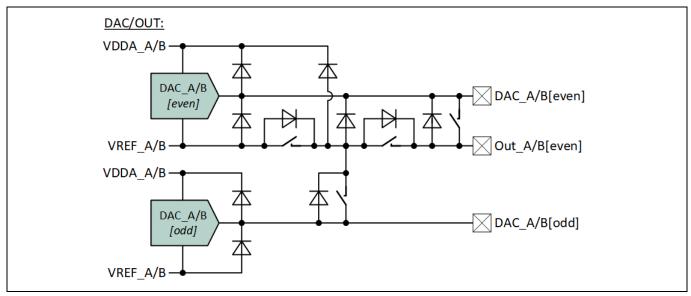

The following figures show a simplified view of the main ESD protection building blocks:

Figure 4 ESD protection for digital pins

Figure 5 ESD protection for ADC pins

Figure 6 ESD protection for supply pins

## **Power Amplifier Bias and Control IC**

## **Specifications**

Figure 7 ESD protection for DAC pins

## 4 Functional Description

#### 4.1 Overview

The BGMC1210 is an eight-channel analog monitoring and control IC with integrated switch control on four output channels, capable of voltage, current and temperature monitoring. The device supports dual polarity on two of its DAC groups A and B, each including four DACs. Two of the DACs in each group are equipped with switches to enable fast toggling between the DAC output and configured clamping voltage. Positive or negative polarity on a corresponding DAC group is defined by the voltages at its supply inputs. The device registers are configured through an I2C/I3C interface.

The main application of BGMC1210 is a bias voltage generation for RF transistor Power Amplifiers as a below simplified block diagram shows.

Figure 8 Simplified Device Block Diagram

## 4.2 Functional Block Diagram

The main building blocks of BGMC1210 are shown in the figure below. It also lists all the device pins.

Figure 9 Detailed Device Block Diagram

## 4.3 Startup and Shutdown Procedure

## **4.3.1** Startup Procedure

The following startup procedure is recommended:

- 1. RSTN is connected to VDDP via pull-up resistor

- 2. Turn-on VREF\_A, VREF\_B, VDD, VDDP, VDDA\_A, VDDA\_B

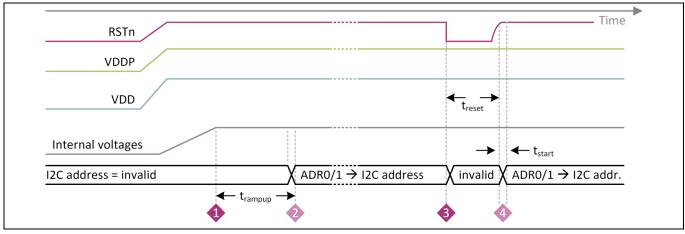

- 3. Once VDDP and VDD are powered up wait  $t_{rampup}$  = 180 us to allow the I2C/I3C interface to unlock

- 4. Program registers:

- programmed registers will have immediate effect on analog periphery

- ADCs can be fetched (if enabled)

- 5. PA transistor gate voltages at OUT\_A0(2), OUT\_B0(2), DAC\_A1(3), DAC\_B1(3) can be enabled

- 6. PA transistors Vdd supply can be enabled

Power supplies can be ramped-up in any sequence. To make the digital interface available VDD and VDDP need to cross their undervoltage release threshold  $UVLO_{VDD,rel}$  and  $UVLO_{VDDP,rel}$ . This is necessary as the device-internal logic is supplied by internal voltages derived from VDD (see Figure 10 time point #1) and the device pins are supplied by VDDP:

Figure 10 Power-Up and reset Timing

After the rampup time  $t_{rampup}$  the internal voltages are stable and the address pins ADR0/1 determine the I2C address (see time point #2). Digital communication (e.g. I2C accesses or I3C dynamic address assertion) can now take place. The address remains stable until the next VDD/VDDP power-down or reset via RSTN. Note that the voltages VDDA\_A, VDDA\_B, VREF\_A and VREF\_B will have no effect on the availability of the digital interface.

Once  $t_{rampup}$  elapsed and the internal voltages are available the temperature sensor (DTS), the voltage ADC (ADC) as well as the current sense ADC (CSA) can be used. To do so they need to be enabled and their startup time needs to elapse ( $t_{VADC,start} / t_{CSA,start} / t_{DTS,start}$ ).

A hardware reset via RSTN (see time point #3) will block the digital interface. Once deasserted communication can take place again after time  $t_{\text{start}}$  elapsed (see time point #4). For further details on the software reset please refer to section 4.3.3.

In cases where the RSTN is driven directly from a microcontroller/FPGA without being pulled to VDDP the rampup time  $t_{rampup}$  must elapse before using the I2C/I3C interface.

In general it is good practice to assert a hardware reset via RSTN after each power cycle.

#### **Functional Description**

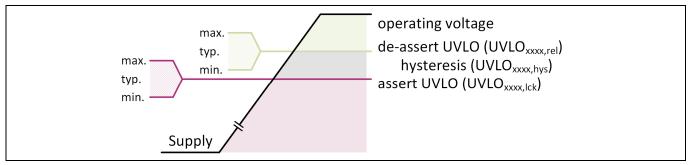

## 4.3.2 Voltage Monitoring

All voltages provided externally to the device are monitored. Once a voltage falls below its undervoltage limit  $(UVLO_{lck})$  it needs to rise beyond its undervoltage release limit  $(UVLO_{rel})$ . The voltage difference between the two is the hysteresis:

Figure 11 Voltage Monitoring

#### 4.3.3 Software Reset

In case software needs to execute a reset by asserting RSTN low (see Figure 10 time point #3) the digital interface will be blocked during that time. The RSTN pin needs to be logic low for minimum time of 80ns (RST<sub>active</sub>). After reset is released it takes maximum  $t_{start}$  to make the digital interface accessible again (see Figure 10 time point #4).

Note:

Reset events shorter than 50ns can cause undeterministic device behavior. In case such events are unavoidable (e.g. during power-on phase) a defined reset pulse is required.

#### 4.3.4 Shutdown Procedure

The following shutdown procedure is recommended:

- 1. Set gate voltages at DAC\_A1(3), DAC\_B1(3) to pinchoff or lower

- 2. Set transistor gate voltages at OUT\_A0(2), OUT\_B0(2) to clamping or lower

- 3. Disable PA transistor supply

- 4. Set RSTN low (RSTN=0)

- 5. Turn-off VREF\_A, VREF\_B, VDD, VDDP, VDDA\_A, VDDA\_B (no specific sequence required)

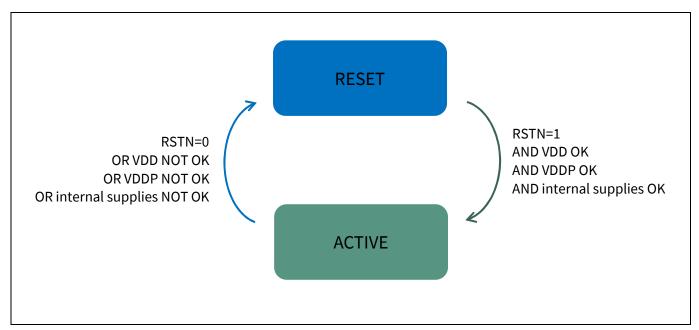

## 4.4 Operation Modes

#### 4.4.1 Mode: RESET

At power-up, when RSTN input is low or in the event of VDD/VDDP supply getting out of range, the BGMC1210 state machine is placed in a RESET state:

- All registers are reset to their initial values (asynchronous)

- Analog infrastructure for DACs is powered up to ensure safe output voltages and fast startup

- DAC\_xy outputs are set to VREF\_x by default register settings and are pulled down to VREF\_x with internal safety clamp

- OUT\_xy outputs are switched to VREF\_x (clamped)

- All ADCs are disabled

- No digital communication to the device is possible

#### 4.4.2 Mode: ACTIVE

After RSTN becomes logic high and if main supplies (VDD, VDDP and internal supplies) are ready and within range, the BGMC1210 state machine finds itself in an ACTIVE state:

- Digital interface available

- All registers are transparent towards the analog part: a changed register content will have immediate effect on the output

- The ADCs are operating (if enabled) and results can be fetched from registers

Figure 12 BGMC1210 state diagram

## 4.5 DAC Output Voltage Configuration

#### 4.5.1 Overview

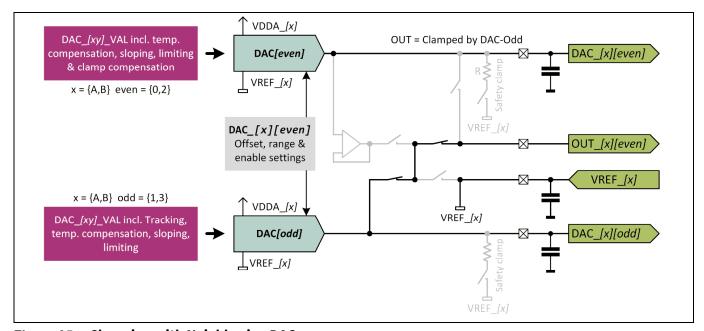

The analog control channels are built around eight DAC cores, each consisting of an R-2R DAC and an output voltage buffer. BGMC1210 offers two independent groups of outputs: A and B. Each group consists of four DACs with a separate supply domain per group.

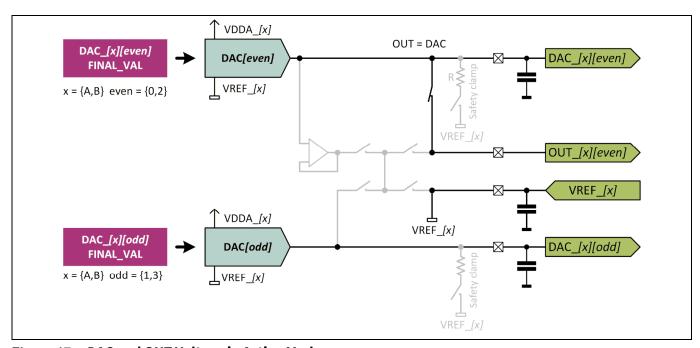

Two of the DACs per group, the ones with even channel number (DAC\_A0, DAC\_A2, DAC\_B0, DAC\_B2), are connected via switched circuits to additional outputs: OUT\_A0, OUT\_A2, OUT\_B0, OUT\_B2. This enables clamping of the output voltage, which means that the voltage at these pins can be toggled between two levels to support PA operation in a time-division duplexing (TDD) radios. One voltage level, defined by the DAC with even channel number, is used to bring RF transistors into their active/conductive region. The other voltage level (clamping voltage) is used to bring the RF transistors into their pinch-off region. Two pins, EN\_OUT\_A and EN\_OUT\_B, allow toggling between two voltages at switched outputs of corresponding DAC group. A simplified block diagram is given in the following figure.

Figure 13 DAC Simplified Block Diagram

Figure 14 DACs And Their Registers

#### **Power Amplifier Bias and Control IC**

#### **Functional Description**

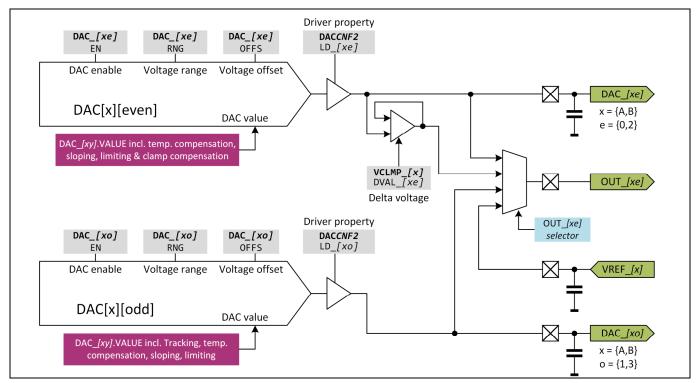

The generated voltages depend on various register settings. Figure 14 shows the entry point for each register setting.

Every DAC has a 12-bit resolution, internal reference voltage and can be adjusted in range and offset. Supply range per DAC group is defined by reference potential VREF\_x and supply input VDDA\_x: VDDA\_x - VREF\_x. Supply voltage can be selected down to -8V and up to +8V, so that enhancement type LDMOS transistors as well as depletion type GaN transistors are supported.

To reduce traffic on the digital control interface it is possible to enable temperature compensation via a look-up table and/or enable tracking of the DAC used for peak device to the DAC used for main device. Additional features include DAC clamping compensation, a dedicated internal clamping buffer and a possibility to use neighboring DAC as a clamping potential.

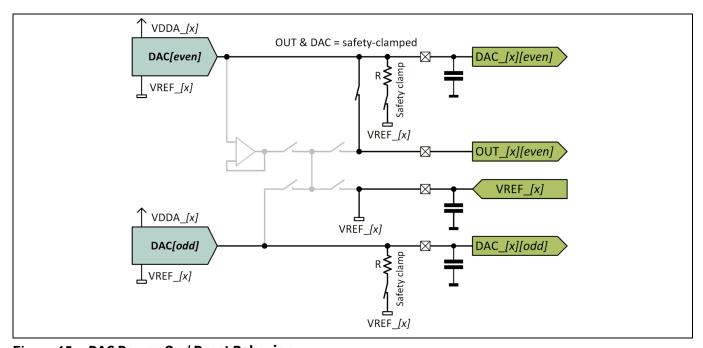

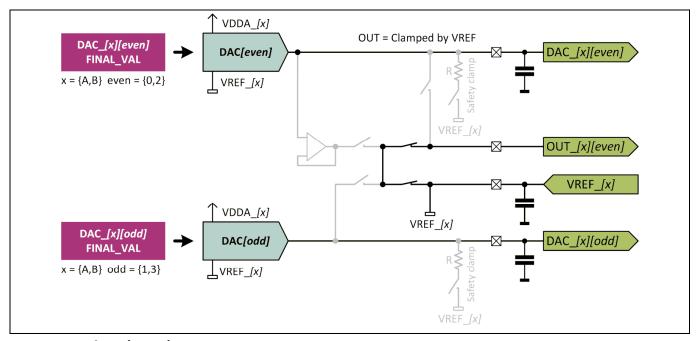

## 4.5.2 DAC and OUT Voltages in Reset Mode

An external reset (RSTN logic low) and a power-on reset (VDD/VDDP) will cause all register settings to revert to their reset values. This also disables the DAC cores. In this state the BGMC1210 pulls DAC\_[x][even], DAC\_[x][odd] and OUT\_[x][even] outputs to VREF\_[x] levels by means of dedicated safety clamps to protect the gates of RF transistors from electrical damage. The following figure gives a simplified overview about the electrical behavior in reset mode:

Figure 15 DAC Power-On / Reset Behavior

Please note that the OUT\_[x][even] outputs will be clamped to VREF\_[x] through a transistor which will cause a clamping voltage slightly higher than at the DAC\_[x][even] or DAC\_[x][odd] outputs.

## 4.6 DAC and OUT Voltages in Active Mode

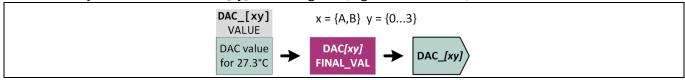

In the simplest case (with compensations, slope control and limitation disabled) a DAC output voltage is determined by the value in the DAC\_[xy].VALUE register (e.g. DAC\_A3.VALUE):

Figure 16 DAC Output Voltage Simple View

In Active Mode the DAC voltages are forwarded to the corresponding DAC and OUT pins according to the following simplified circuit diagram:

Figure 17 DAC and OUT Voltage in Active Mode

## 4.6.1 DAC Value Calculation Flow

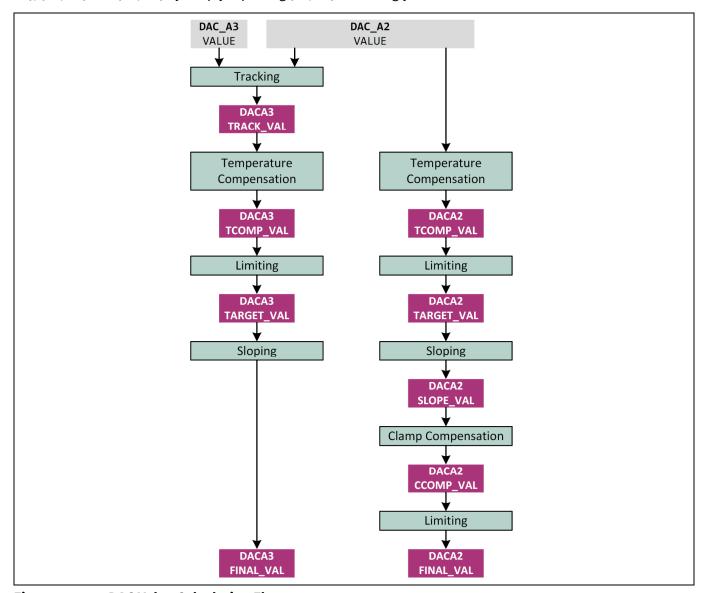

To allow higher flexibility DAC output voltages depend on various register settings. These settings will be processed in several steps resulting in a final DAC value which will then be converted into a voltage. Note that even and odd DACs behave slightly different since their purpose is different.

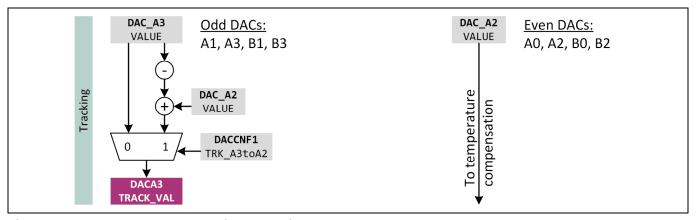

The following figure lists individual steps of this processing flow. For the sake of readability DAC A3 and DAC A2 are shown as an odd and even DAC, respectively. The figure is also valid for other odd/even DAC pairs like {A1, A0}, {B1, B0} and {B3, B2} by simply replacing {A3, A2} accordingly:

Figure 18 DAC Value Calculation Flow

- <u>Tracking (step #1)</u>: An odd DAC channel can be set to track its neighboring even DAC channel (e.g. DAC\_A3 tracks DAC\_A2). In this case an offset between the channels needs to be defined.

- <u>Temperature compensation (step #2)</u>: A device receiving a DAC voltage usually shows a performance drifting with temperature. To mitigate such effects a temperature compensation mechanism is provided.

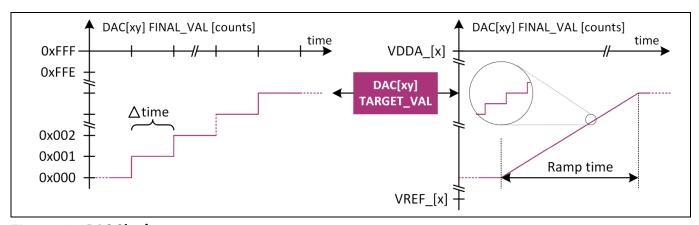

- <u>Sloping (step #3)</u>: To avoid excessive (peak) currents when charging capacitors connected to the DACs an output voltage step can be slowed down by turning the step into a ramp. This is done by the sloping feature.

#### **Functional Description**

- <u>Limiting (step #4 and #6):</u> To prevent a DAC voltage from rolling over when exceeding the maximum or minimum DAC value a limit is used. Under normal operating / configuration conditions the limits will never be reached.

- <u>Clamp Compensation (step #5):</u> Some RF transistors fed by the DACs show trapping effects causing them to underperform at the bias point set by the DAC. This happens when the transistor returns from the clamped (pinch-off) state to the conducting state. This effect usually disappears after a short time (microseconds). In such situations time-limited over-biasing may be required. This is provided by the clamp compensation mechanism for all even DACs.

The final calculated value is then fed to the DAC which will then generate the corresponding output voltage. During software implementation phase it can come in handy to check the calculated DAC value. This can be done by using the DAC\_FB register.

All these steps are described in more details later during this chapter.

#### 4.6.2 Initial DAC Value Calculation

To calculate DAC\_[xy].VALUE for a desired DAC output voltage the following parameters must be known:

- DAC supply voltages VDDA\_[x] and VREF\_[x]

- Desired output voltage for DAC channel [xy] relative to VREF\_[x]

- DAC range

- DAC offset

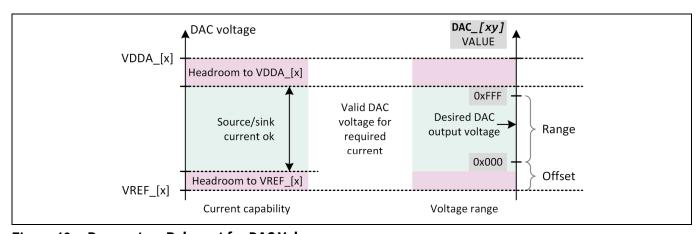

The figure below shows how those parameters define the DAC output voltage:

Figure 19 Parameters Relevant for DAC Value

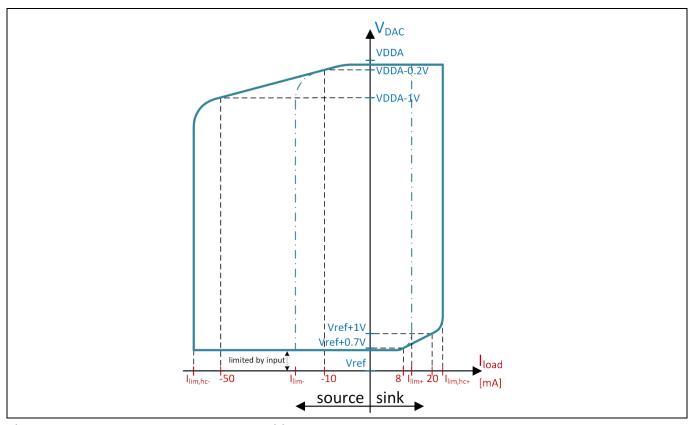

The DAC output voltage should have a certain headroom to VDDA\_[x] and VREF\_[x] to allow normal operation of DAC buffers, ensure specified DAC accuracy and sink and source current capabilities. For details on the required voltage headrooms see the specifications for I<sub>src, hi</sub> as well as I<sub>snk</sub> and I<sub>snk, hi</sub> in Table 7.

#### **Functional Description**

The following figure illustrates DAC buffer driving capabilities with respect to the buffer output voltage V<sub>DAC</sub>:

Figure 20 DAC Output Voltage Capability

To set a fixed voltage offset in relation to VREF\_[x] a corresponding setting can be defined for each individual channel by DAC\_[xy]. OFFS. Preferrably the offset is selected such that the desired DAC voltage range resides within the boundaries of VDDA\_[x] / VREF\_[x] with respecting corresponding voltage headrooms. Available offsets are 0V (OFFS = 0), 0.5V (OFFS = 1), 1.5V (OFFS = 2) and 3.0V (OFFS = 3).

To maximize DAC granularity the 3.5V voltage range is used (DAC\_[xy].RNG = 1). Otherwise the range will be 7V (DAC\_[xy].RNG = 1).

As the final step the DAC value DAC\_[xy].VALUE can be calculated as the voltage difference relative to the offset voltage set by DAC\_[xy].OFFS ( $=\Delta V$ ). The following equation can be used to calculate the DAC value (refer to an example in section 5.2 for more details):

DAC\_[xy].VALUE =

$$\frac{4095}{\text{Range}} \cdot \Delta V$$

$\Delta V = DAC_Voltage - Offset - VREF_[x]$

Figure 21 DAC Value Equation

## 4.6.3 DAC Value Step #1: Tracking

An odd DAC channel can be set to track its neighboring even DAC channel (e.g. DAC\_A3 tracks DAC\_A2). This is typically done when an odd DAC is used as a clamping voltage for the neighboring even DAC. Often clamping voltage can/should have a fixed voltage offset to bias point voltage. In this case an offset between the two channels is defined as shown on Figure 22.

If an odd DAC is configured to track an even DAC, the range and offset settings will be taken from the even DAC registers. This is needed for linear tracking and proper limitation.

# infineon

#### **Functional Description**

Figure 22 DAC Value Calculation: Tracking

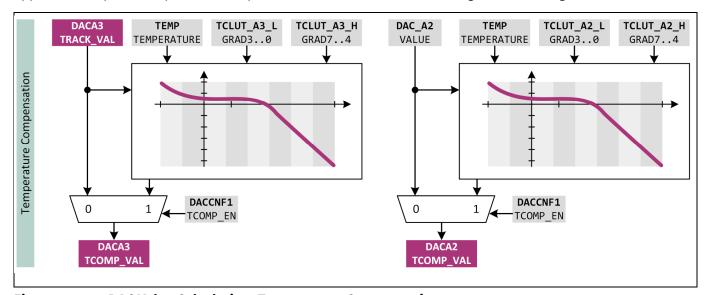

## 4.6.4 DAC Value Step #2: Temperature Compensation

The BGMC1210 provides built-in thermal compensation as a convenient solution to minimize temperature drifts of both internal DACs (minor drift) and RF transistors (major drift) connected to them. In case user application requires temperature compensation it is advised to read through the following sections.

Figure 23 DAC Value Calculation: Temperature Compensation

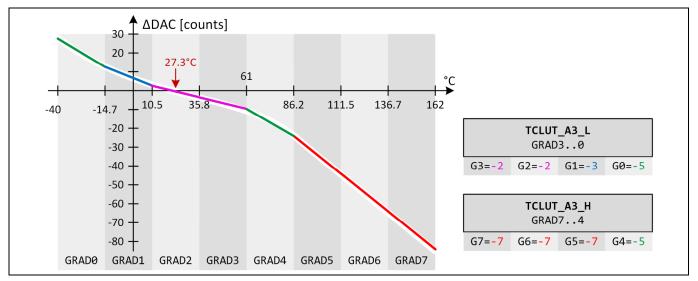

Compensation is implemented with a Look-Up Table (LUT), in which eight temperature coefficients (gradients) for each individual DAC can be configured (e.g. TCLUT\_A3\_L and TCLUT\_A3\_H). Depending on the temperature measured by the Die Temperature Sensor (DTS), a delta to the reference DAC value of 27.3°C is calculated and provided to the DAC via DAC\_[xy]\_VAL (if temperature compensation is enabled via DACCNF1.TCOMP\_EN).

In total nine equidistant interpolation points at fixed temperatures are needed to calculate the eight gradients (see Figure 24). The gradients need to be defined in such a way that the piecewise interpolated values approximate the Delta DAC curve (see Figure 25) best.

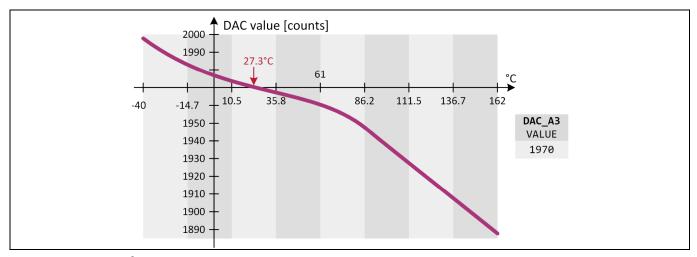

The following example is a real-world example where the DACs are used in a GaN-based power amplifier. It describes the process how to find the best gradients. The starting point is always a measurement over temperature to determine the DAC values required to achieve the desired DAC (here DAC\_A3) output voltage. Figure 24 shows an example of such measurement.

#### **Functional Description**

Figure 24 DAC Value Over Temperature

In this example a DAC value of 1970 is required to achieve the desired output voltage at the reference temperature of 27.3°C measured by the DTS. This value is used for the DAC\_A3.VALUE register. It will also be the reference point for the gradient fitting.

The temperature points shown on the X-axis match the temperatures at which one gradient starts/ends. Gradient #0 starts at -40°C while gradient #1 starts at -14.7°C and so on. Therefore it makes sense to measure the DAC value at least for these temperatures. For a better fitting more measurements are advised. Figure 24 shows such a graph measured using multiple points.

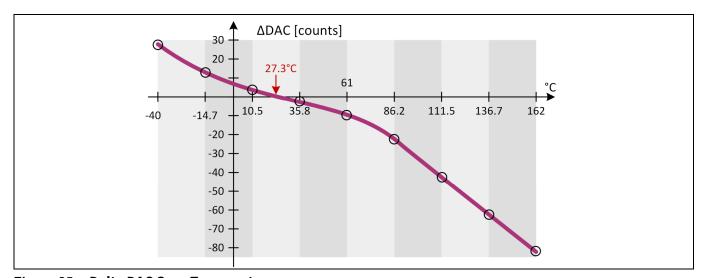

The graph in Figure 25 can then be plotted relative to the DAC value at 27.3°C:

Figure 25 Delta DAC Over Temperature

The delta values can now be used to calculate the gradients such that they best-fit the previously shown curve. Each gradient is valid for a temperature range of 24.5K. This odd number is calculated like this: (32 counts in the TEMP.TEMPERATURE register) \* (0.7648K per count).

Gradient #0 for example is used only for temperatures between -40°C ... -15.5°C. Gradient #1 starts at -14.7°C (-15.5°C + 0.7648K) and ends at +9.7°C (10.5°C – 0.7648K) and so on.

#### **Functional Description**

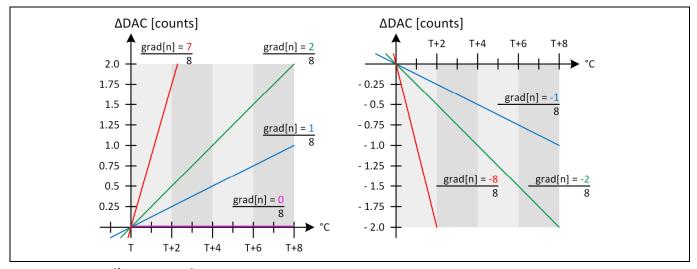

A gradient describes the delta between two DAC values measured at two temperatures 8 Kelvin apart from each other. The gradients reach from -8...+7 in steps of 1 and are programmed using the two's complement (Figure 26).

|                                                         | Decimal | Binary | Hex | Decimal | Binary | Hex |

|---------------------------------------------------------|---------|--------|-----|---------|--------|-----|

|                                                         | 7       | 0111   | 7   | -1      | 1111   | F   |

|                                                         | 6       | 0110   | 6   | -2      | 1110   | Е   |

| DAC deviation [counts]                                  | 5       | 0101   | 5   | -3      | 1101   | D   |

| $grad[n] = \frac{DAC deviation [counts]}{per 8 Kelvin}$ | 4       | 0100   | 4   | -4      | 1100   | С   |

| per e ne.viii                                           | 3       | 0011   | 3   | -5      | 1011   | В   |

|                                                         | 2       | 0010   | 2   | -6      | 1010   | Α   |

|                                                         | 1       | 0001   | 1   | -7      | 1001   | 9   |

|                                                         | 0       | 0000   | 0   | -8      | 1000   | 8   |

Figure 26 Gradient Two's Complement

For example if the DAC value for -40°C is 2000 counts and for -15.5°C it is 1985 counts the DAC-Delta is 15 counts. Since the temperature delta is 24.5K the gradient is calculated as:

$(1985 \text{ counts} - 2000 \text{ counts}) / [-15.5^{\circ}\text{C} - (-40.0^{\circ}\text{C})] = -15 \text{ counts} / 24.5\text{K} = -4.9 \text{ counts} / 8\text{K}$

The nearest suitable gradient is -5 which stands for -5 counts / 8K. This procedure is repeated for each gradient. Some gradient examples are shown in the following figure.

Figure 27 Gradient Examples

An example for a gradient fitted curve can be found in Figure 28. The curve from Figure 25 is shown as a white envelope.

Figure 28 Gradient Example

Please note that the gradients in the registers TCLUT\_A3\_H and TCLUT\_A3\_L are shown with MSB on the left (gradient #0) and LSB on the right (gradient #7) while in Figure 28 they appear the other way around.

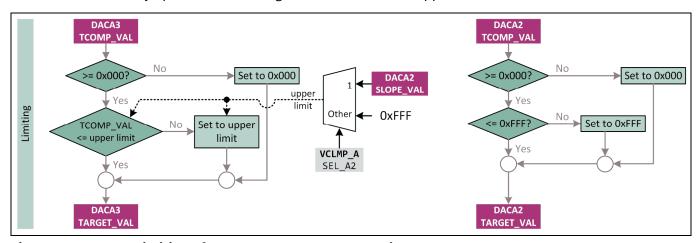

## 4.6.5 DAC Value Step #3: Limit

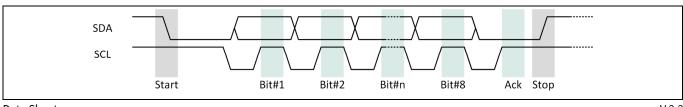

The DAC values coming from the temperature compensation (DAC[xy] TCOMP\_VAL) are limited to 0xFFF at the upper end and 0x000 at the lower end. Temperature compensation may leed to values outside this range and therefore limits need to be applied. For the majority of usecases it is unlikely that the limits will ever be reached as the DACs are usually operated with enough headroom from the upper and lower limit.