# BK2535

## Datasheet

## FLIP51 MCU+RF

Building 41, Capital of Tech Leaders, 1387 Zhangdong Road, Zhangjiang High-Tech Park, Pudong New District, Shanghai, China Tel: (86)21 51086811 Fax: (86)21 60871089

This document contains information that may be proprietary to, and/or secrets of, Beken Corporation. The contents of this document should not be disclosed outside the companies without specific written permission.

Disclaimer: Descriptions of specific implementations are for illustrative purpose only, actual hardware implementation may differ.

## **Revision History**

| Version | Date         | Author(s)              | Description                                       |

|---------|--------------|------------------------|---------------------------------------------------|

| 0.1     | Jan. 20,2015 | Lizhen                 | Initial flash version                             |

| 0.2     | Feb. 15,2014 | Lizhen                 | Update USB RF etc.                                |

| 0.3     | Apr. 15,2014 | Lizhen                 | Update package and mode select, add FLASH control |

| 0.4     | Jun. 15,2014 | Lizhen Update LBD part |                                                   |

| 0.5     | Aug. 18,2015 | Lizhen                 | Update the format                                 |

| 0.6     | Nov. 19,2015 | Ronghui                | Updated the feature part                          |

| 0.7     | 4.12.2016    | Guodong                | Updatad PWM address                               |

|         |              |                        |                                                   |

|         |              |                        |                                                   |

### Table of Contents

| 1. | Introduction                               | .9 |

|----|--------------------------------------------|----|

| 2. | Feature                                    | .9 |

| 3. | Block Diagram1                             | 10 |

| 4. | PIN information1                           | 11 |

| 4  | .1. BK2535_QFN321                          | 11 |

| 4  | .2. BK2535 QFN561                          | 13 |

| 5. | MCU Description                            | 16 |

| 5  | .1. FLIP51 Micro-Controller                |    |

|    | 5.1.1. Introduction1                       | 16 |

|    | 5.1.2. MCU diagram                         | 17 |

| 5  | 5.1.2. MCU diagram                         | 18 |

|    | 5.2.1. Overview                            | 18 |

|    | 5.2.2. Program Memory (CODE space)1        |    |

|    | 5.2.3. External Data Memory (XDATA space)1 | 19 |

|    | 5.2.4. Internal Data Memory (IDATA space)  | 19 |

| 5  | .3. Power management                       |    |

|    | 5.3.1. Power Control Register              | 28 |

|    | 5.3.2. Work State                          | 29 |

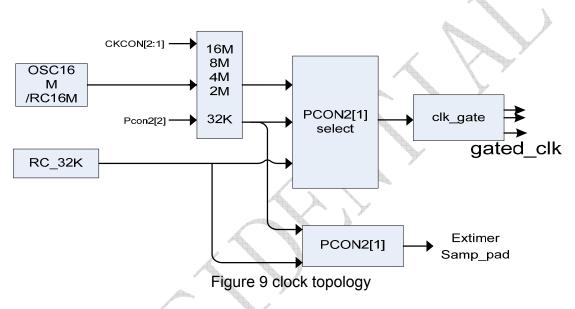

| 5  | .4. Clock system                           | 31 |

|    | 5.4.1. System clock topology               | 31 |

|    | 5.4.2. Peripherals clock management        |    |

| 5  | .5. Reset system                           |    |

|    | .6. Interrupt system                       | 34 |

|    | 5.6.1. Introduction                        |    |

|    | 5.6.2. Interrupt enable                    | 38 |

|    | 5.6.3. Interrupt priority                  |    |

|    | 5.6.4. Interrupt blocking conditions       |    |

| 6. | Peripheral module                          |    |

| 6  | .1. OVERVIEW                               |    |

|    | .2. UART                                   |    |

|    | 6.2.1. Serial port overview                |    |

|    | 6.2.2. Operation mode                      |    |

|    | 6.2.3. Programming the Baud Rate           |    |

|    | 6.2.4. Serial port registers               |    |

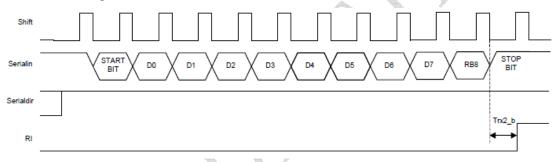

| 6  | .3. ADC                                    |    |

| -  | 6.3.1. introduction                        |    |

|    | 6.3.2. Register explain                    |    |

|    | 6.3.3. Sample rate:                        |    |

|    | 6.3.4. ADC usage                           |    |

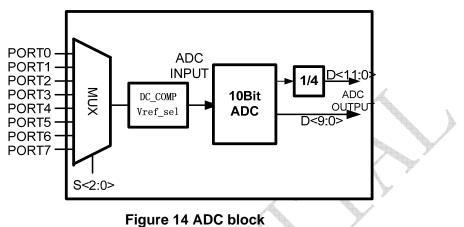

| 6  | .4. PWM                                    |    |

| 0  | 6.4.1. OVERVIEW                            |    |

|    | 6.4.2. FUNCTIONAL DESCRIPTION              |    |

|    |                                            |    |

|    | 6.4.3. Frequency of PWM                                                        |     |

|----|--------------------------------------------------------------------------------|-----|

|    | 6.5. I2C                                                                       |     |

|    | 6.5.1. I2C master                                                              | .53 |

|    | 6.5.2. I2C slave                                                               | .69 |

|    | 6.6. RNG                                                                       | .77 |

|    | 6.7. LBD                                                                       | .78 |

|    | 6.7.1. LBD threshold                                                           | .78 |

|    | 6.8. FLASH control                                                             |     |

|    | 6.9. WDT                                                                       | .81 |

|    | 6.10. Ext Timer                                                                | .82 |

|    | 6.11. Encryption Decryption Unit (AES)                                         |     |

| 7. |                                                                                |     |

| 8. | USB                                                                            |     |

|    | 8.1. Clock                                                                     | .90 |

|    | 8.2. USB Register Access                                                       | .90 |

|    | 8.3. ENDPOINT Configuration                                                    | .90 |

|    | 8.4. Interrupt                                                                 | .93 |

|    | 8.5. FIFO                                                                      |     |

|    | 8.5.1. FIFO SFR register                                                       | .96 |

|    | 8.5.1. FIFO SFR register                                                       | .98 |

|    | 8.5.3. FIFO Operation                                                          | 98  |

|    | 8.6. Device Address                                                            |     |

|    | <ul><li>8.7. Frame number register</li><li>8.8. USB power management</li></ul> | .99 |

|    | 8.8. USB power management                                                      | .99 |

|    | 8.9. USB debug mode register                                                   |     |

|    | 8.10. USB RESET                                                                |     |

|    | 8.11. Endpoint Buffer                                                          | 100 |

| 9. |                                                                                | 102 |

| 1( | D. BK2535 RF transceiver                                                       | 103 |

|    | 10.1. General Description                                                      |     |

|    | 10.2. Abbreviations                                                            |     |

|    | 10.3. State Control                                                            |     |

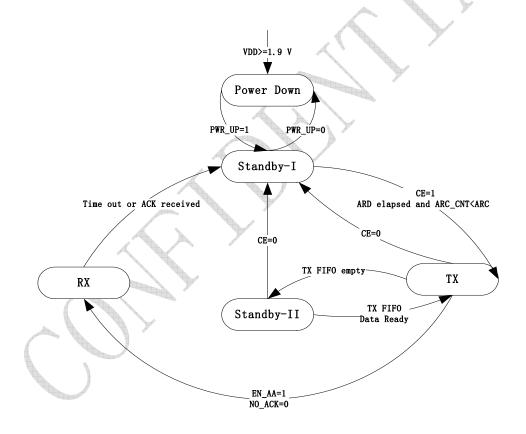

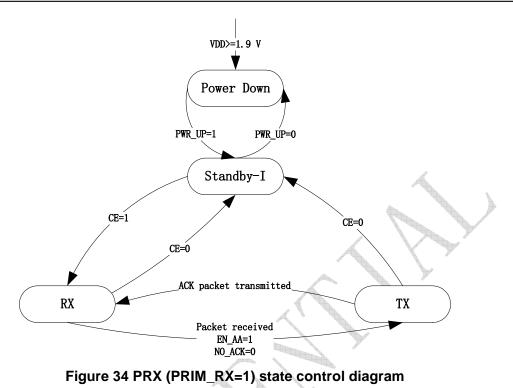

|    | 10.3.1. State Control Diagram                                                  |     |

|    |                                                                                | 107 |

|    | 10.3.3. Standby-I Mode                                                         |     |

|    | 10.3.4. Standby-II Mode                                                        |     |

|    | 10.3.5. TX Mode                                                                |     |

|    | 10.3.6. RX Mode                                                                |     |

|    | 10.4. Packet Processing                                                        |     |

|    | 10.4.1. Packet Format                                                          |     |

|    | 10.4.2. Packet Handling                                                        |     |

|    | 10.5. Data and Control Interface                                               |     |

|    | 10.5.1. TX/RX FIFO                                                             |     |

|    | 10.5.2. Interrupt                                                              |     |

|    | 10.6. RF Command                                                               |     |

|    | 10.7. Register Map                                                             | 117 |

| 10.7.1. Digital Register          | 117 |

|-----------------------------------|-----|

| 10.7.2. Analog Register           |     |

| 10.7.3. TX power control setting  |     |

| 10.7.4. PLL setting time          |     |

| 11. Electrical specifications     |     |

| 11.1. RF part                     |     |

| 11.2. MCU part                    |     |

| 12. Typical Application Schematic |     |

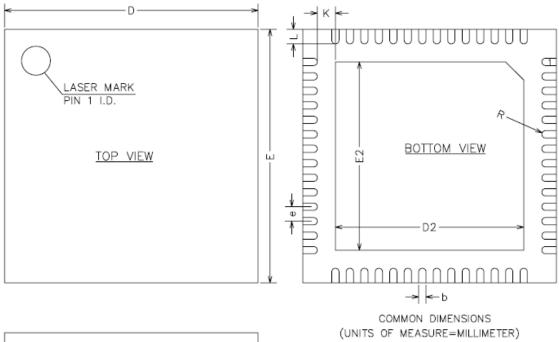

| 13. Package Information           |     |

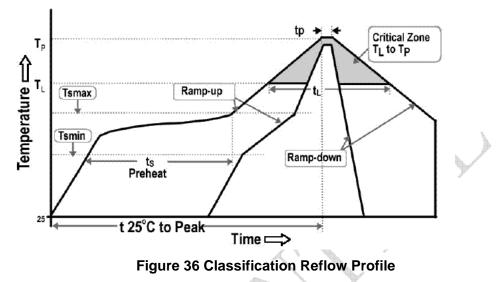

| 14. Solder Reflow Profile         |     |

| 15. Contact Information           |     |

## List of Figures

| FIGURE 1 BK2535 BLOCK DIAGRAM                               | 10    |

|-------------------------------------------------------------|-------|

| FIGURE 2 BK2535_M                                           | 11    |

| FIGURE 3 BK2535_K                                           | 13    |

| FIGURE 4 FLIP51 ARCHITECTURE                                | 17    |

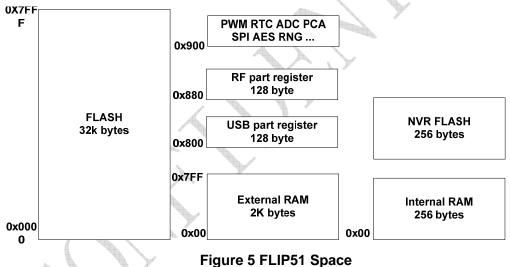

| FIGURE 5 FLIP51 SPACE                                       | 18    |

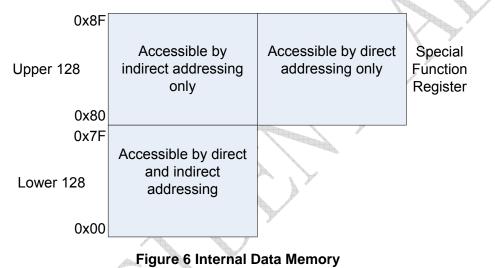

| FIGURE 6 INTERNAL DATA MEMORY                               | 20    |

| FIGURE 7 INTERNAL RAM LOWER 128 BYTES                       | 21    |

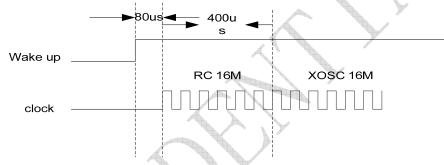

| FIGURE 8 WAKE UP PROCESS                                    | 31    |

| FIGURE 9 CLOCK TOPOLOGY                                     |       |

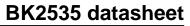

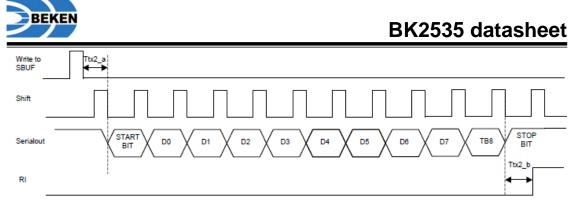

| FIGURE 10 SERIAL TRANSMIT MODE 1                            | 44    |

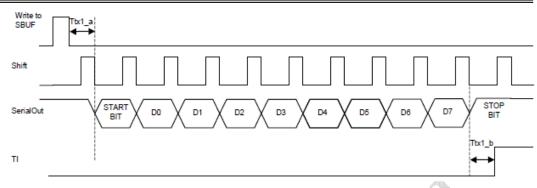

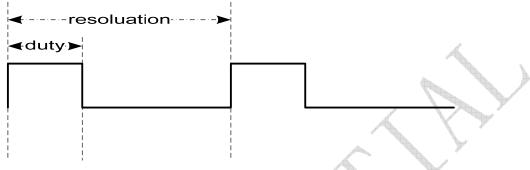

| FIGURE 11 SERIAL RECEIVE MODE 1                             |       |

| FIGURE 12 SERIAL TRANSMIT MODE 2                            |       |

| FIGURE 13 SERIAL RECEIVE MODE 2                             | 45    |

| FIGURE 14 ADC BLOCK                                         |       |

| FIGURE 15 PWM PARAMETER                                     |       |

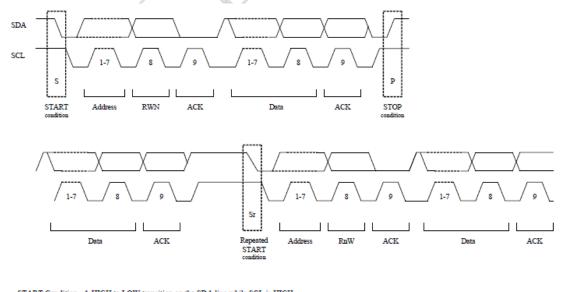

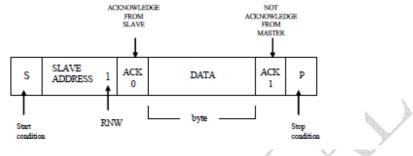

| FIGURE 16 COMPLETE DATA TRANSFER                            | 58    |

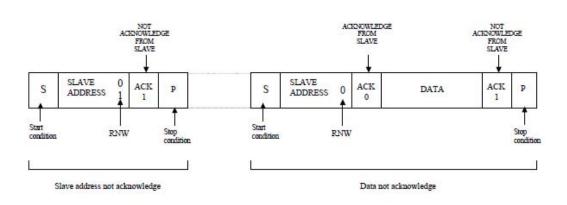

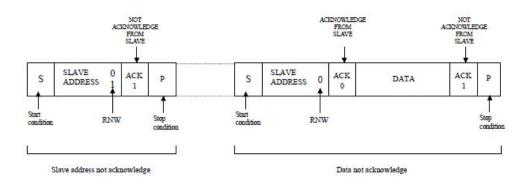

| FIGURE 17 "NOT ACKNOWLEDGE" BY SLAVE                        | 60    |

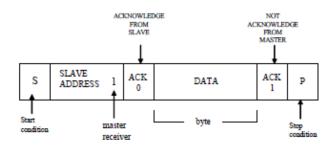

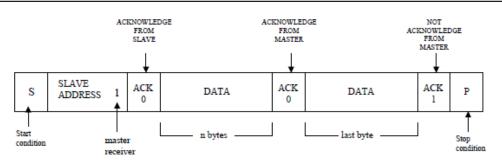

| FIGURE 18 "NOT ACKNOWLEDGE" BY MASTER (END OF TRANSMISSION) |       |

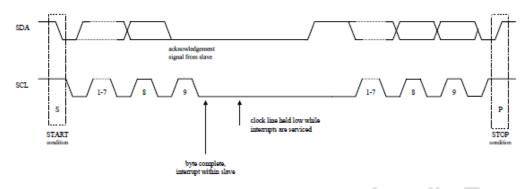

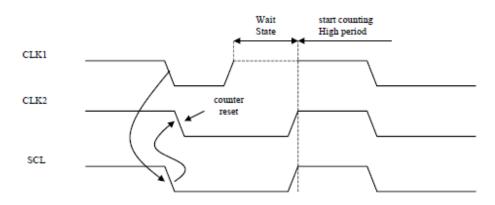

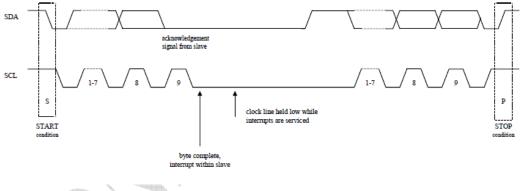

| FIGURE 19 CLOCK SYNCHRONIZATION1                            |       |

| FIGURE 20 CLOCK SYNCHRONIZATION2                            |       |

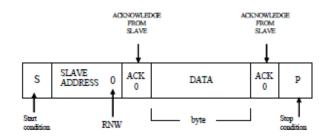

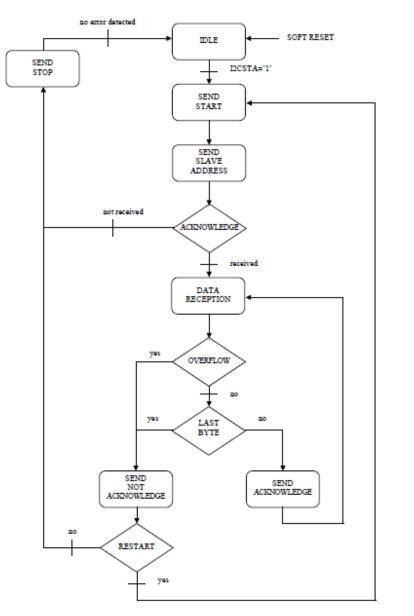

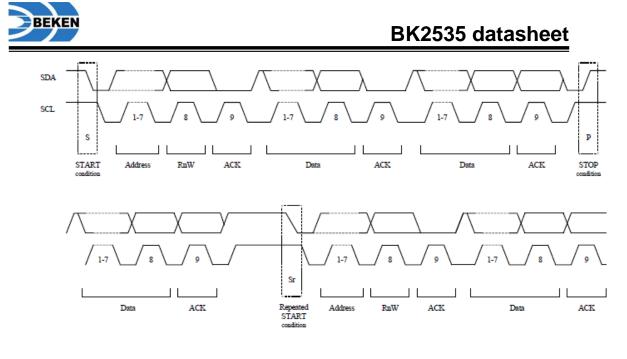

| FIGURE 21 TYPICAL TRANSMISSION                              |       |

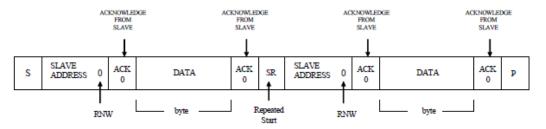

| FIGURE 22 REPEATED START OR STOP CONDITION AFTER LAST BYTE  |       |

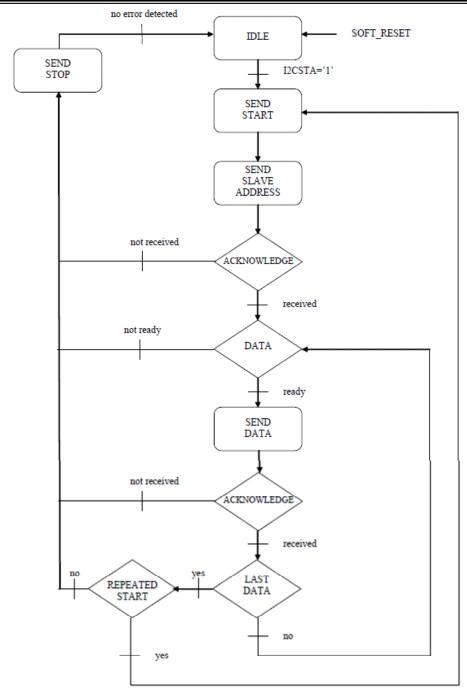

| FIGURE 23 TRANSMISSION FSM                                  | 65    |

| FIGURE 24 TYPICAL RECEPTION                                 |       |

| FIGURE 25 REPEATED START OR STOP CONDITION AFTER LAST BYTE  | 67    |

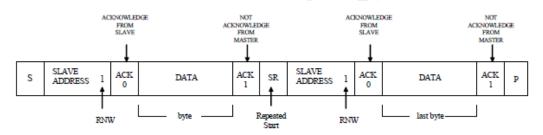

| FIGURE 26 RECEPTION FSM                                     |       |

| FIGURE 27 COMPLETE DATA TRANSFER 7-BIT ADDRESSING           |       |

| FIGURE 28 "NOT ACKNOWLEDGE" BY SLAVE DEVICE                 | 75    |

| FIGURE 29 "NOT ACKNOWLEDGE" BY MASTER DEVICE                |       |

| FIGURE 30 CLOCK SYNCHRONIZATION                             |       |

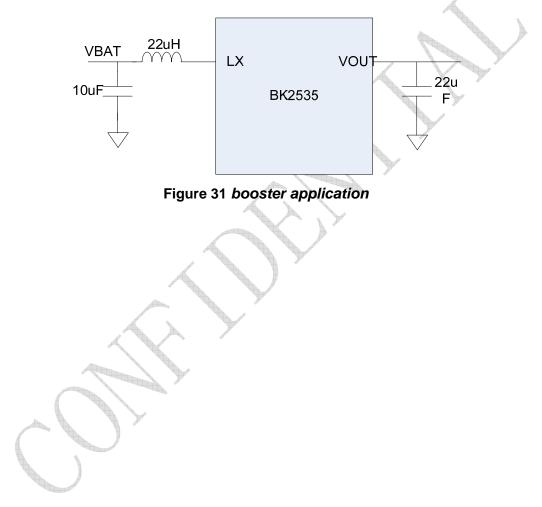

| FIGURE 31 BOOSTER APPLICATION                               | 89    |

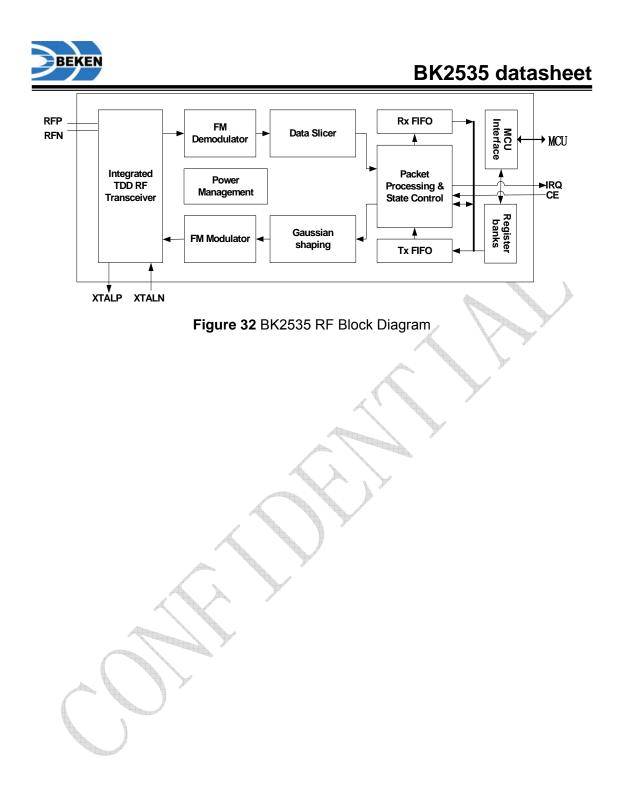

| FIGURE 32 BK2535 RF BLOCK DIAGRAM                           | . 104 |

| FIGURE 33 PTX (PRIM_RX=0) STATE CONTROL DIAGRAM             | . 106 |

| FIGURE 34 PRX (PRIM_RX=1) STATE CONTROL DIAGRAM             | . 107 |

| FIGURE 35 PACKET FORMAT                                     | . 109 |

| FIGURE 36 CLASSIFICATION REFLOW PROFILE                     | . 132 |

|                                                             |       |

## List of tables

| TABLE 1 QFN32 PIN DEFINITION                                      |           |

|-------------------------------------------------------------------|-----------|

| TABLE 2 QFN56 PIN DEFINITION                                      |           |

| TABLE 3 SPECIAL FUNCTION REGISTERS MEMORY MAP                     |           |

| TABLE 4 CORE SFRS                                                 |           |

| TABLE 5 ADDITIONAL INTERRUPT SFRS                                 |           |

| TABLE 6 I/O PORTS SFRS                                            |           |

| TABLE 7 SERIAL PORT SFRS                                          |           |

| TABLE 8 <i>TIMERS SFRS</i><br>TABLE 9 <i>BIRD SFRS</i>            |           |

| TABLE 9 BIRD SFRS                                                 |           |

| TABLE 10 POWER MANAGEMENT REGISTER                                |           |

| TABLE 11 POWER MANAGEMENT REGISTER                                | 50<br>27  |

| TABLE 12 CLOCK ENABLE REGISTER                                    | 22<br>22  |

| TABLE 13 CLK_EN_CFG REGISTER                                      | 22<br>25  |

| TABLE 14 INTERROPT SOURCES                                        |           |

| TABLE 15 HIMER/COUNTER CONTROL REGISTER (TCON LOW)                | 20<br>27  |

| TABLE 10 MMI REGISTERS                                            |           |

| TABLE 17 ADDITIONAL INTERRUPT REGISTERS                           |           |

| TABLE 18 ADDITIONAL INTERROFT LAG REGISTER (AII )                 |           |

| TABLE 19 INTERROPT ENABLE REGISTER (IE)                           | 29        |

| TABLE 20 ADDITIONAL INTERROPT ENABLE REGISTER (AIE)               | <u>70</u> |

| TABLE 22 INTERRUPT PRIORITY WITHIN A SAME PRIORITY LEVEL (0 OR 1) |           |

| TABLE 22 INTERRUPT PRIORITY WITHIN A SAME PRIORITY LEVEL (U OR 1) |           |

| TABLE 23 INTERROPT PRIORITY REGISTER (IP)                         |           |

| TABLE 24 ADDITIONAL INTERROPT PRIORITT REGISTER (AIP)             |           |

| TABLE 25 SERIAL PORT REGISTERS                                    |           |

| TABLE 20 SERIAL PORT CONTROL REGISTER (SCON)                      |           |

| TABLE 27 ADC REGISTER0                                            | 49        |

|                                                                   | 49        |

| TABLE 29 ADC REGISTER2                                            | 49<br>10  |

| TABLE 30 ADC REGISTERS                                            | 49        |

| TABLE 31 ADC ANALOG REGISTER                                      |           |

| TABLE 32 ADC ANALOG REGISTER ADDRESS                              |           |

| TABLE 34 PWM REGISTER SUMMARIZE                                   |           |

| TABLE 35 I2CM REGISTER                                            |           |

| TABLE 35 IZCM REGISTER (MCON)                                     |           |

| TABLE 30 IZCM RECEIVE REGISTER (MRCON)                            |           |

| TABLE 38 I2CM TRANSMIT BUFFER (MTXBUF)                            |           |

| TABLE 39 I2CM MPRESC REGISTER                                     |           |

| TABLE 40 I2CM STATUS REGISTER 0 (MSTAT0)                          |           |

| TABLE 40 IZCM STATUS REGISTER 0 (MSTATU)                          |           |

| TABLE 42 I2CM INTERRUPT ENABLE REGISTER 0 (MIENO)                 |           |

| TABLE 43 I2CM INTERRUPT ENABLE REGISTER 1 (MIENO)                 |           |

| TABLE 44 I2CM CALL ADDRESS REGISTER (MCADDR)                      |           |

| TABLE 45 RESERVED ADDRESSES FOR I2CANSACTIONS                     |           |

| TABLE 45 RESERVED ADDRESSES FOR RECENSACTIONS                     |           |

| TABLE 40 IZC SLAVE REGISTER                                       |           |

| TABLE 49 DATA REGISTER                                            |           |

| TABLE 49 SSTATO REGISTER                                          |           |

| TABLE 50 SSTATU REGISTER                                          |           |

|                                                                   |           |

| TABLE 51 SIENO REGISTER                                           | /3        |

| TABLE 52 SIEN1 REGISTER                          |      |

|--------------------------------------------------|------|

| TABLE 53 SSADDR REGISTER                         |      |

| TABLE 54 RESERVED ADDRESSES FOR I2C TRANSACTIONS | . 75 |

| TABLE 55 RNG REGISTER                            |      |

| TABLE 56 LBD THRESHOLD REGISTER                  | 78   |

| TABLE 57 FLASH CONTROL REGISTER1                 | . 79 |

| TABLE 58 FLASH CONTROL REGISTER2                 | 79   |

| TABLE 59 WATCH DOG REGISTER                      |      |

| TABLE 60 THE PRESCALER OF WATCH DOG CLOCK        |      |

| TABLE 61 RTC REGISTER                            |      |

| TABLE 62 AES CONTROL REGISTER                    |      |

| TABLE 63 KEY REGISTER                            |      |

| TABLE 64 AES INT REGISTER                        |      |

| TABLE 65 MDU SFR                                 |      |

| TABLE 66 MDU REGISTER (READ)                     | 85   |

| TABLE 67 MDU REGISTER(WRITE)                     | 86   |

| TABLE 68 MDU OPERATION TABLE                     |      |

| TABLE 69 OPERATION DATA                          |      |

| TABLE 70 OPERATE RESULT                          |      |

| TABLE 71 MDU OPERATIONS EXECUTION TIMES          |      |

| TABLE 72 USB MSB ENDPOINT ADDRESS                |      |

| TABLE 73 CONFIGURE REGISTER 1 OF ENDPOINT 0      |      |

| TABLE 74 ENDPOINT N CONFIGURE REGISTER           |      |

| TABLE 75 ENDPOINT NCONFIGURE REGISTER 0          | 93   |

| TABLE 76 USBINTO INTERRUPT REGISTER              | 93   |

| TABLE 77 EP_STATUS REGISTER                      | 94   |

| TABLE 78 EP_STATUS REGISTER                      |      |

| TABLE 79 USBINT1 INTERRUPT REGISTER              |      |

| TABLE 80 USB_ENO INTERRUPT ENABLE REGISTER       | 95   |

| TABLE 81 USB_EN1INTERRUPT ENABLE REGISTER        |      |

| TABLE 82 FIFO EP_RDY REGISTER                    |      |

| TABLE 83 FIFO LOWER 8 BITS COUNTER REGISTER      |      |

| TABLE 84 FIFO UPPER 2 BITS COUNTER REGISTER      |      |

| TABLE 85 FIFO EP_HALT REGISTER                   |      |

| TABLE 86 DEVICE ADDRESS REGISTER                 |      |

| TABLE 87 FRAM_NO_0 LOWER 8 BITS REGISTER         |      |

| TABLE 88 FRAM_NO_0 UPPER 3 BITS REGISTER         |      |

| TABLE 89 USB POWER CONTROL REGISTER              |      |

| TABLE 90 USB DEBUG REGISTER                      |      |

| TABLE 91 USB RESET REGISTER                      |      |

| TABLE 92 WORK MODE SELECTION                     |      |

| TABLE 93 RF COMMAND                              |      |

| TABLE 94 DIGITAL REGISTER                        |      |

| TABLE 95 TX POWER SETTING                        |      |

| TABLE 96 PLL SETTING TIME                        |      |

| TABLE 97 SOLDER REFLOW PROFILE                   | 132  |

### 1. Introduction

The BK2535 is a RF SOC chip, which combine a 2.4 GHz radio, a fast 8051 compatible CPU named FILE51, essential peripherals, and on-air compatibility with the other product series from BEKEN. The BK2535 is a perfect fit for HID applications, RF tags and remote controlled products.

### 2. Feature

- 1.8 V to 3.6 V power supply

- FLIP51 MCU compatible with 8051

- A 4-stage pipeline architecture that enables to execute most of the instructions in a single clock cycle.

- 32k bytes FLASH for program

- 256 Bytes IRAM and 2k Bytes SRAM

- Embedded three Timer/Counter

- Support UART I2C SPI interface

- Support AES encryption

- A pseudo random number generator embedded

- Total 40 GPIO available

- The dedicated 2 PWM available and 6 PCA can be used as PWM

- The embedded BIRD (Built-In Real-time Debugger) system for online debug

- 8 channel ADC embedded

- Booster embedded

- Integrated 2.4G RF transceiver

- low power consumption, embedded with 32k RC oscillator

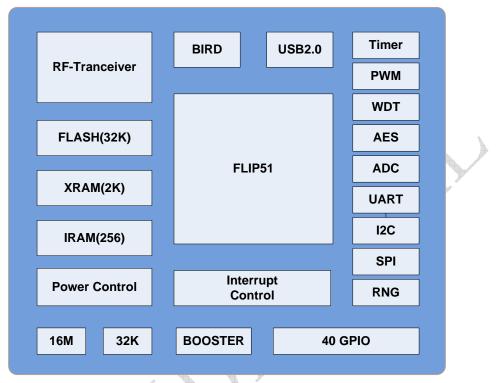

### 3. Block Diagram

### Figure 1 BK2535 Block Diagram

4. **PIN** information

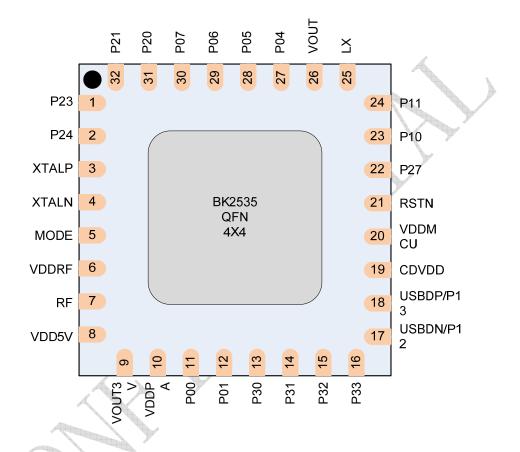

### 4.1. BK2535\_QFN32

### Figure 2 BK2535\_M

| NO. | Name   | Pin Function  | Description                                    |

|-----|--------|---------------|------------------------------------------------|

| 1   | P2.3   | Digital I/O   | General I/O, or clock for SMBUS (I2C)          |

| 2   | P2.4   | Digital I/O   | General I/O, or data I/O for SMBUS (I2C)       |

| 3   | XTALP  | Analog output | Oscillator output                              |

| 4   | XTALN  | Analog input  | Oscillator input                               |

| 5   | MODE   | Digital input | Mode selection                                 |

| 6   | VDDRF  | Power supply  | Power supply for RF part module                |

| 7   | RF     | RF port       | ANTENNA port                                   |

| 8   | VDD5V  | 5V Power      | 5V supply from USB, used for inner 5V LDO      |

| 9   | VOUT3V | Analog output | 3v power output, connected with decoupling CAP |

| 10  | VDDPA  | Power supply  | Power supply for PA part                       |

| 11 | P0.0       | Digital I/O         | General I/O, or input for timer0                           |

|----|------------|---------------------|------------------------------------------------------------|

| 12 | P0.1       | Digital I/O         | General I/O, or input for timer1                           |

| 13 | P3.0       | I/O or analog input | General I/O, or input of ADC0                              |

| 14 | P3.1       | I/O or analog input | General I/O, or input of ADC1                              |

| 15 | P3.2       | I/O or analog input | General I/O, or input of ADC2                              |

| 16 | P3.3       | I/O or analog input | General I/O, or input of ADC3                              |

| 17 | USB_DN/P12 | Digital I/O         | USB input N, or General I/O                                |

| 18 | USB_DP/P13 | Digital I/O         | USB input P, or General I/O                                |

| 19 | CDVDD      | Analog output       | 1.5V power output, connected with decoupling CAP           |

| 20 | VDDMCU     | Power supply        | Power supply for MCU part                                  |

| 21 | RSTN       | Digital input       | Reset for chip, active low                                 |

| 22 | P2.7       | Digital I/O         | General I/O, or PWM1                                       |

| 23 | P1.0       | Digital I/O         | General I/O, or input for external interrupt 0, active low |

| 24 | P1.1       | Digital I/O         | General I/O, or input for external interrupt 1, active low |

| 25 | LX         | Analog input        | Switch, connect to BAT through a inductance                |

| 26 | VOUT       | Analog output       | The output of booster                                      |

| 27 | P0.4       | Digital I/O         | General I/O, or MOSI for SPI                               |

| 28 | P0.5       | Digital I/O         | General I/O, or MISO for SPI                               |

| 29 | P0.6       | Digital I/O         | General I/O, or SCK for SPI                                |

| 30 | P0.7       | Digital I/O         | General I/O, or chip select for SPI                        |

| 31 | P2.0       | Digital I/O         | General I/O, or input for UART0                            |

| 32 | P2.1       | Digital I/O         | General I/O, or output for UART0                           |

Table 1 QFN32 PIN Definition

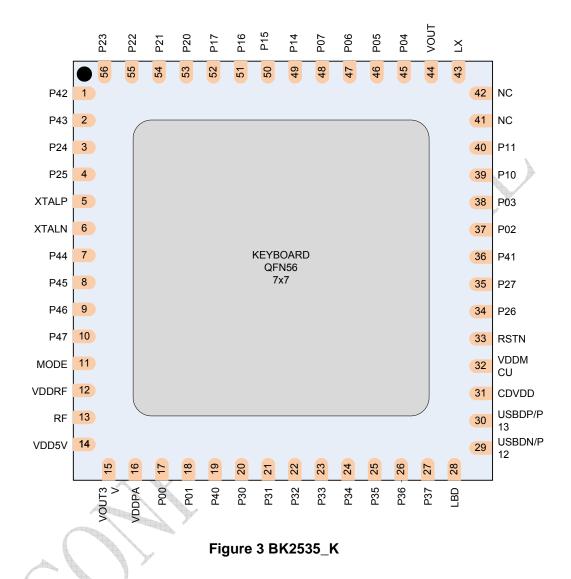

#### 4.2. BK2535\_QFN56

| PIN | Name  | Pin Function  | Description                              |

|-----|-------|---------------|------------------------------------------|

| 1   | P4.2  | Digital I/O   | General I/O, or PCA port                 |

| 2   | P4.3  | Digital I/O   | General I/O, or PCA port                 |

| 3   | P2.4  | Digital I/O   | General I/O, or data I/O for SMBUS (I2C) |

| 4   | P2.5  | Digital I/O   | General I/O                              |

| 5   | XTALP | Analog output | Oscillator output                        |

| 6   | XTALN | Analog input  | Oscillator input                         |

| 7   | P44   | Digital I/O   | General I/O, or PCA port                 |

| 8   | P45   | Digital I/O   | General I/O, or PCA port                 |

| 9   | P46   | Digital I/O   | General I/O,                             |

| 10  | P47   | Digital I/O   | General I/O,                             |

| 11       | MODE         | Digital input              | Mode selection                                               |

|----------|--------------|----------------------------|--------------------------------------------------------------|

| 12       | VDDRF        | Power supply               | Power supply for RF part module                              |

| 13       | RF           | RF port                    | ANTENNA port                                                 |

| 14       | VDD5V        | 5V Power                   | 5V supply from USB, used for inner 5V                        |

|          |              |                            | LDO                                                          |

| 15       | VOUT3V       | Analog output              | 3v power output, connected with                              |

| -        |              | 5                          | decoupling CAP                                               |

| 16       | VDDPA        | Power supply               | Power supply for PA part                                     |

| 17       | P0.0         | Digital I/O                | General I/O, or input for timer0                             |

| 18       | P0.1         | Digital I/O                | General I/O, or input for timer1                             |

| 19       | P4.0         | Digital I/O                | General I/O, or PCA port                                     |

| 20       | P3.0         | I/O or analog input        | General I/O, or input of ADC0                                |

| 21       | P3.1         | I/O or analog input        | General I/O, or input of ADC1                                |

| 22       | P3.2         | I/O or analog input        | General I/O, or input of ADC2                                |

| 23       | P3.3         | I/O or analog input        | General I/O, or input of ADC3                                |

| 24       | P3.4         | I/O or analog input        | General I/O, or input of ADC4                                |

| 25       | P3.5         | I/O or analog input        | General I/O, or input of ADC5                                |

| 26       | P3.6         | I/O or analog input        | General I/O, or input of ADC6                                |

| 27       | P3.7         | Digital I/O or analog      | General I/O, or input of ADC7                                |

|          |              | input                      |                                                              |

| 28       | LBD          | Analog input               | Low power detect pin                                         |

| 29       | USB_DN/P12   | Digital I/O                | USB input N, or General I/O                                  |

| 30       | USB_DP/P13   | Digital I/O                | USB input P, or General I/O                                  |

| 31       | CDVDD        | Analog output              | 1.5V power output, connected with                            |

|          |              |                            | decoupling CAP                                               |

| 32       | VDDMCU       | Power supply               | Power supply for MCU part                                    |

| 33       | RSTN         | Digital input              | Reset for chip, active low                                   |

| 34<br>35 | P2.6         | Digital I/O                | General I/O, or PWM0                                         |

|          | P2.7<br>P4.1 | Digital I/O<br>Digital I/O | General I/O, or PWM1                                         |

| 36<br>37 | P0.2         | Digital I/O                | General I/O, or PCA port<br>General I/O, or input for timer2 |

| 38       | P0.2         | Digital I/O                | General I/O, or acquire/reload trigger                       |

| 30       | FU.3         | Digital I/O                | signal for timer2                                            |

| 39       | P1.0         | Digital I/O                | General I/O, or input for external                           |

|          |              | Signatino                  | interrupt 0, active low                                      |

| 40       | P1.1         | Digital I/O                | General I/O, or input for external                           |

|          |              |                            | interrupt 1, active low                                      |

| 41       | NC           |                            | • •                                                          |

| 42       | NC           |                            |                                                              |

| 43       | LX           | Analog input               | Switch, connect to BAT through a                             |

|          |              |                            | inductance                                                   |

| 44       | VOUT         | Analog output              | The output of booster                                        |

| 45       | P0.4         | Digital I/O                | General I/O, or MOSI for SPI                                 |

| 46       | P0.5         | Digital I/O                | General I/O, or MISO for SPI                                 |

| 47       | P0.6         | Digital I/O                | General I/O, or SCK for SPI                                  |

| 48       | P0.7         | Digital I/O                | General I/O, or chip select for SPI                          |

| 49       | P1.4         | Digital I/O                | General I/O                                                  |

| 50       | P1.5         | Digital I/O                | General I/O                                                  |

| 51       | P1.6         | Digital I/O                | General I/O                                                  |

| 52       | P1.7         | Digital I/O                | General I/O                                                  |

| 53       | P2.0         | Digital I/O                | General I/O, or input for UART0                              |

| 54 | P2.1 | Digital I/O | General I/O, or output for UART0      |

|----|------|-------------|---------------------------------------|

| 55 | P2.2 | Digital I/O | General I/O,                          |

| 56 | P2.3 | Digital I/O | General I/O, or clock for SMBUS (I2C) |

Table 2 QFN56 PIN definition

### 5. MCU Description

### 5.1. FLIP51 Micro-Controller

#### 5.1.1. Introduction

The FLIP8051 is an improved option of the 80c51 microcontroller. It is 100% binary code upward compatible with the legacy 80c51.

Its pipeline architecture provides an increase of processing speed an average nine times, when running at the same clock frequency as a standard 80c51 real component.

- Full binary code compatibility with the legacy 80C51/52

- 2 Data Pointers for faster memory copies and indexing.

- Hardware-controlled Wait State solution for asynchronous peripherals

- Static synchronous design with no internal tri-state busses

- Power-saving modes provide solutions for low-power applications

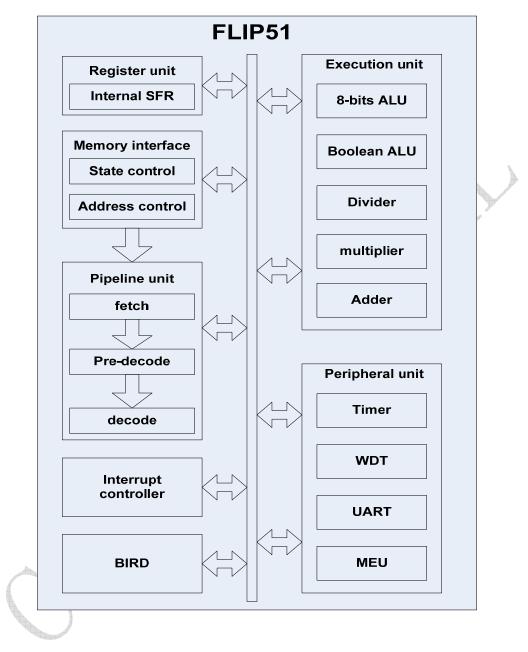

#### 5.1.2. MCU diagram

### Figure 4 FIIP51 architecture

### 5.2. FLIP8051 address space

#### 5.2.1. Overview

The memory organization of the Flip8051 is similar to that of standard 80C51. There are three separate memory spaces: CODE space (program memory), the XDATA space (external data memory) and the IDATA space (internal data memory).

These memory spaces shared the same address space but are accessed with different instruction types.

There are organized as follow for BK2535:

CODE space: up to 32K Bytes of addressing range

XDATA space: up to 2K Bytes of addressing range

IDATA space: up to 256 Bytes.

### 5.2.2. Program Memory (CODE space)

The Flip8051 has a 64K Bytes code space (32K for BK2535). Program memory is normally assumed to be read only and can be accessed only by MOVC instruction (or of course by the instruction fetch).

Two addressing modes are available for MOVC instructions:

16-bit data pointer (@A+DPTR).

The MOVC instructions use these indirect modes to access the current 64 K page of the code memory.

16-bit program counter (@A+PC).

The MOVC instruction uses this indirect mode to access the 64 K page of the code memory.

### 5.2.3. External Data Memory (XDATA space)

The **External Data memory** shares address bus with program memory. This data space can be up to 64K Bytes (2K for BK2535).

The external data memory can be accessed only by the standard MOVX instructions (plus some new instructions of the WHIRL instruction set)

Two addressing modes are available for MOVX instructions:

Byte register (@Ri, i = 0, 1).

Registers R0 and R1 indirectly address external data memory locations 00h-FFh. When MOVX instructions use this indirect mode, the MSB of the 16-bit address is filled with the content of MPAGE SFR (0A1h). Then, it allows MOVX @Ri instruction to access to 64K Bytes of external data memory. Usually, in 80C51 application, the Port 2 is used to this address extension. In order to keep software compatibility with existing 80C51 program, the register MPAGE is also updated by any value written at P2 register.

16-bit data pointer (@DPTR).

The MOVX instructions use these indirect modes to access the page of the external data RAM pointed by the extended data pointer (DPX).

### 5.2.4. Internal Data Memory (IDATA space)

The **Internal data memory** is composed by 256 bytes of internal RAM and by a number of SFRs.

The main difference between these IDATA and XDATA spaces is the kind of instructions that enable to access to these memories. Most of the "data transfer" instructions are dedicated to access internal data memory (IDATA) since there are only four instructions (MOVX) dedicated to access external data memory.

Moreover, only indirect addressing mode is available for XDATA whilst IDATA can be addressed by register, direct, register-indirect or immediate addressing mode. This provides a higher flexibility to access data. In addition, the Flip8051 memory interface with IDATA space is optimized and then access time to this space is faster than the access time of XDATA for both read/write operations.

#### 5.2.4.1. Internal Data memory organization

The internal data memory is divided into 3 spaces, which are referred to as the **Lower 128**, **Upper 128** and **SFR space**. Either direct or indirect addressing may be used to access the **lower 128** bytes of internal data memory. The **upper 128** bytes of internal data memory are accessible by indirect addressing only while direct addressing to region above 0x7F will access **SFR space**.

In the Flip8051, the SFRs are implemented internally to the model using Flip-Flops.

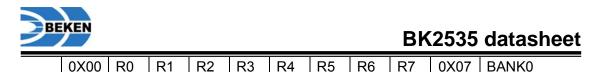

5.2.4.2. Internal ram: lower 128 byes

| 0X78         0X7F           0X70         0X77           0X68         0X6F           0X60         0X67           0X58         0X5F           0X50         0X5F           0X48         0X4F           0X40         0X47 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0X68         0X6F           0X60         0X67           0X58         0X5F           0X50         0X5F           0X48         0X4F                                                                                     |

| 0X60         0X67           0X58         General Purpose Memory         0X57           0X48         0X4F                                                                                                              |

| 0X58<br>0X500X5F<br>0X570X480X4F                                                                                                                                                                                      |

| 0X50General Purpose Memory0X570X480X4F                                                                                                                                                                                |

| 0X50<br>0X48<br>0X4F                                                                                                                                                                                                  |

|                                                                                                                                                                                                                       |

| 0X40 0X47                                                                                                                                                                                                             |

|                                                                                                                                                                                                                       |

| 0X38 0X3F                                                                                                                                                                                                             |

| 0X30 0X37                                                                                                                                                                                                             |

| 0X28 Bit Addressable Memory 0X2F                                                                                                                                                                                      |

| 0X20 Bit Addressable Methory 0X27                                                                                                                                                                                     |

| 0X18 R0 R1 R2 R3 R4 R5 R6 R7 0X1F BAN                                                                                                                                                                                 |

| 0X10 R0 R1 R2 R3 R4 R5 R6 R7 0X17 BAN                                                                                                                                                                                 |

| 0X08 R0 R1 R2 R3 R4 R5 R6 R7 0X0F BAN                                                                                                                                                                                 |

| Figure 7   | Internal | Ram    | Lower | 128 | <b>B</b> vtes |

|------------|----------|--------|-------|-----|---------------|

| i igui c i | memai    | i (ann | LOWCI | 120 | Dyics         |

The lower 128 bytes of Internal Data Memory is organized in three distinct areas:

0x00-0x1F: The Register Banks are at the lowest 32 bytes of the internal data memory. Only one Register Bank is used at a time when an instruction uses R0 to R7. 2 bits in Processor Status Word (PSW), called RS1 and RS0, control the selection of the Register Bank. Bank 0 is selected upon reset. Indirect addressing mode used R0 and R1 as index registers

0x20-0x2F: This memory space contains a general-purpose memory, which is bit addressable as well as byte addressable. The bit address ranged from 0 to 0x7F. When bit addressing is used in an instruction, the bit access in this region will occur. In this memory range, when bit addressing is used, bit address 0x00 is the bit 0 of address 0x20 while bit 7 of the byte 0x20 has bit address 0x07. Bit address 0x7F is the bit 7 of address 0x2F. A bit access is different than a byte access by the type of instruction used.

0x30-0x7F: A general-purpose byte-addressable memory is located above address 0x30. It can be accessed both by direct or indirect addressing mode.

#### 5.2.4.3. Internal Ram: Upper 128 Bytes

The usage of the addresses between 0x80 and 0xFF is up to the user. This memory can be used for any purpose providing that indirect addressing mode is used when accessing this memory space, otherwise the Special Function Register memory will be accessed.

### 5.2.4.4. The Stack and the stack pointer

The stack refers to an area of internal RAM that is used in conjunction with certain instructions (PUSH, POP) to store and retrieve data quickly. The Stack pointer register (SP, 0x81) is used to hold an internal RAM address that is called the "top of the stack". The data held in the SP register is the address in internal RAM where the last byte of data was stored by a stack operation. The reset value of Stack pointer register is 0X07 and which can be changed to any internal RAM address by the programmer. Usually, the stack is located high in the RAM to avoid conflict with the work register, bit and byte area in internal RAM.

#### 5.2.4.5. Special Function Registers

The direct-access data memory locations from 0x80 to 0xFF constitute the special function registers (SFRs). All the special function registers of the original 80C51 are present in the Flip8051. SFRs with addresses ending in 0x0 or 0x8 (e.g. P0, TCON, P1, SCON, IE, etc.) are bit-addressable as well as byte-addressable. All other SFRs are byte-addressable only.

The special function registers (SFRs) reside in their associated peripherals or in the core. The following tables shows the SFR address space with the SFR mnemonics and reset values. Unoccupied locations in the SFR space are unimplemented, i.e. no register exists. If an instruction attempts to write to an unimplemented SFR location, the instruction executes, but nothing is actually written. If an unimplemented SFR location is read, it returns an unspecified value.

| SFR<br>Name   | bit7   | bit6     | bit5    | bit4     | bit3       | bit2   | bit1           | bit0   | addr |

|---------------|--------|----------|---------|----------|------------|--------|----------------|--------|------|

|               |        |          |         |          |            |        |                |        | 0x80 |

| SP            | -      | -        | -       | -        | -          | -      | -              | -      | 0x81 |

| DPL           | -      | -        | -       | -        | -          | -      | -              | -      | 0x82 |

| DPH           | -      | -        | -       | -        | -          | -      | -              | -      | 0x83 |

| CKCON         | CKDIV1 | CKDIV0   | smod0   | x        | х          | x      | x              | x      | 0x84 |

| CLK_EN<br>CFG | adc_en | timer_en | uart_en | pwm_en   | spi_en     | i2c_en | aes_mud_<br>en | wdt_en | 0x85 |

| PCON2         | SMOD   | EUSB     | CMD_RST | Latch_en | deep_sleep | OSC32k | RC32k          | IDLE   | 0x86 |

|               |        |          |         |          |            |        |                |        | 0x87 |

| TCON          | TF1    | TR1      | TF0     | TR0      | IE1        | IT1    | IE0            | IT0    | 0x88 |

| TMOD          | GATE   | C/T      | M1      | MO       | GATE       | C/T    | M1             | MO     | 0x89 |

| TL0           | -      | -        | -       | -        | -          | -      | -              | -      | 0x8A |

| TL1           | -      | -        | -       | -        | -          | -      | -              | -      | 0x8B |

| TH0           | -      | -        | -       | -        | -          | -      | -              | -      | 0x8C |

| TH1           | -      | -        | -       | -        | -          | -      | -              | -      | 0x8D |

| CCMCON        | -      | -        | -       | -        | -          | -      | -              | -      | 0x8E |

| CCMVAL        | -      | -        | -       | -        | -          | -      | -              | -      | 0x8F |

| P1            | -      | -        | -       | -        | -          | -      | -              | -      | 0x90 |

|               |        |          |         |          |            |        |                |        | 0x91 |

| DPSEL         | x      | x        | x       | x        | x          | x      | x              | DPSEL0 | 0x92 |

| P1IN_EN       | -      | -        | -       | -        | -          | -      | -              | -      | 0x93 |

| P2IN_EN       | -      | -        | -       | -        | -          | -      | -              | -      | 0x94 |

| P3IN_EN       | -      | -        | -       | -        | -          | -      | -              | -      | 0x95 |

|               |        |          |         |          |            |        |                |        | 0x96 |

| MMS           | -      | -        | -       | -        | -          | -      | -              | -      | 0x97 |

| SCON0         | SM0    | SM1      | SM2     | REN      | TB8        | RB8    | ТІ             | RI     | 0x98 |

| SBUF0         | -      | -        | -       | -        | -          | -      | -              | -      | 0x99 |

|               |        |          |         |          |            |        |                | 1      | 0x9A |

| PAGE_A        | x      | x        | x       | x        | x          | x      | х              | х      | 0x9B |

| (NA)           |            |   |     |       |     |     |     |      |                     |

|----------------|------------|---|-----|-------|-----|-----|-----|------|---------------------|

| PAGE_B<br>(NA) | x          | x | x   | x     | x   | x   | x   | x    | 0x9C                |

| PAGE_C<br>(NA) | x          | x | x   | x     | x   | x   | x   | x    | 0x9D                |

| P1OUT_N        | -          | - | -   | -     | -   | -   | -   | -    | 0x9E                |

| P2OUT_N        | -          | - | -   | -     | -   | -   | -   | -    | 0x9F                |

| P2             | -          | - | -   | -     | -   | -   | -   | -    | 0xA0                |

| MPAGE          | -          | - | -   | -     | -   | -   | -   | -    | 0xA1                |

|                |            |   |     |       |     |     |     |      | 0xA2                |

|                |            |   |     |       |     |     |     |      | 0xA3                |

|                |            |   |     |       |     |     |     |      | 0xA4                |

| P3OUT_N        | -          | - | -   | -     | -   | -   | -   | -    | 0xA5                |

| WDT            | x          | x | x   | state | x   | ps2 | ps1 | ps0  | 0xA6                |

|                | <b>F</b> A |   | FTO | 50    | 574 | EV4 | ET0 | EV(0 | 0xA7                |

| IE             | EA         | x | ET2 | ES    | ET1 | EX1 | ET0 | EX0  | 0xA8                |

| P1_PU          | -          | - | -   | -     | -   | -   | -   | -    | 0xA9<br><b>0xAA</b> |

| P2_PU          | -          | - | -   | -     | -   | -   | -   | -    | 0xAB                |

| P3_PU          | -          | - | -   | -     | -   | -   | -   | -    | 0xAC                |

| F3_FU          | -          |   |     | -     | -   | -   |     | -    | 0xAC<br>0xAD        |

|                |            |   |     |       |     |     |     |      | 0xAD<br>0xAE        |

| P1_PD          | -          | - | -   | -     | -   | -   | -   | -    | 0xAF                |

| P3             | -          | - | -   | -     | -   | -   | -   | -    | 0xB0                |

|                |            |   |     |       |     |     |     |      | 0xB1                |

|                |            |   |     |       |     |     |     |      | 0xB2                |

|                |            |   |     |       |     |     |     |      | 0xB3                |

| P2_PD          | -          |   | -   | -     | -   | -   | -   | -    | 0xB4                |

| P3_PD          | -          | - | -   | -     | -   | -   | -   | -    | 0xB5                |

|                |            |   |     |       |     |     |     |      | 0xB6                |

|                |            |   |     |       |     |     |     |      | 0xB7                |

| IP             | -          | - | -   | -     | -   | -   | -   | -    | 0xB8                |

|                |            |   |     |       |     |     |     |      | 0XB9                |

|                |            |   |     |       |     |     |     |      | 0xBA                |

|                |            |   |     |       |     |     |     |      | 0xBB                |

|                |            |   |     |       |     |     |     |      | 0xBC                |

|                |            |   |     |       |     |     |     |      | 0xBD                |

|                |            |   |     |       |     |     |     |      | 0xBE                |

|                |            |   |     |       |     |     |     |      | 0xBF                |

| AIF            | -          | - | -   | -     | -   | -   | -   | -    | 0xC0                |

|                       |     |          |          |          |          |              |          |              | 0xC1 |

|-----------------------|-----|----------|----------|----------|----------|--------------|----------|--------------|------|

|                       |     |          |          |          |          |              |          |              | 0xC2 |

|                       |     |          |          |          |          |              |          |              | 0xC3 |

|                       |     |          |          |          |          |              |          |              | 0xC4 |

|                       |     |          |          |          |          |              |          |              | 0xC5 |

|                       |     |          |          |          |          |              |          |              | 0xC6 |

|                       |     |          |          |          |          |              |          |              | 0xC7 |

| T2CON                 | TF2 | EXF2     | RCLK     | TCLK     | EXEN2    | TR2          | CT2      | CPRL2        | 0xC8 |

| NMI                   | x   | x        | x        | x        | x        | x            | nmi_en   | nmi_flag     | 0xC9 |

| RCAP2L                | -   | -        | -        | -        | -        | -            | -        | -            | 0xCA |

| RCAP2H                | -   | -        | -        | -        | -        | -            | -        | -            | 0xCB |

| TL2                   | -   | -        | -        | -        | -        | -            | -        | -            | 0xCC |

| TH2                   | -   | -        | -        | -        | -        | -            | -        | -            | 0xCD |

|                       |     |          |          |          |          |              |          |              | 0xCE |

|                       |     |          |          |          |          |              |          |              | 0xCF |

| PSW                   | -   | -        | -        | -        | -        | -            | -        | -            | 0xD0 |

|                       |     |          |          |          |          |              |          |              | 0xD1 |

| I2CM                  | x   | x        | ETBE     | x        | ETBF     | ERBE         | x        | ERBF         | 0xD2 |

| DATA_IE               |     |          |          |          |          |              |          |              | 0xD3 |

|                       |     |          |          |          |          |              |          |              |      |

| I2CM<br>CALLADD<br>R0 | RWN | CADDR[6] | CADDR[5] | CADDR[4] | CADDR[3] | CADDR[<br>2] | CADDR[1] | CADDR[<br>0] | 0xD4 |

|                       |     |          |          | 1        |          |              |          |              | 0xD5 |

|                       |     |          |          |          |          |              |          |              | 0xD6 |

| -                     |     |          |          |          |          |              |          |              | 0xD7 |

|                       |     |          |          |          |          |              |          |              | 0xD8 |

| P1_OPDR               | -   | _        | -        | -        | -        | -            | -        | -            | 0xD9 |

| P2_OPDR               | -   | -        | -        | -        | -        | -            | -        | -            | 0xDa |

| P3_OPDR               | -   | -        | -        | -        | -        | -            | -        | -            | 0xDb |

|                       |     |          |          |          |          |              |          |              | 0xDc |

|                       |     |          |          |          |          |              |          |              | 0xDd |

|                       |     |          |          |          |          |              |          |              | 0xDe |

| -                     |     |          |          |          |          |              |          |              | 0xDf |

| ACC                   | -   | -        | -        | -        | -        | -            | -        | -            | 0xE0 |

| I2CM<br>CTRL          | x   | х        | WAIT     | x        | STOP     | SRST         | STA      | BUSY         | 0xE1 |

| I2CM                  | -   | -        | -        | -        | -        | -            | -        | -            | 0xE2 |

| RXDATA                | -   | -        | -        | -        | -        | -            | -        | -            | 0xE3 |

| I2CM<br>TXDATA        | -   | -        | -        | -        | -        | -            |          |              |      |

| I2CM<br>PRESC         | -   | -        | -        | -        | -        | -            | -        | -            | 0xE4 |

| I2CM<br>TXRX_ST |   | x | x        | DNA      | SANA     | UNF          | OVF               | NEND             | 0XE5         |

|-----------------|---|---|----------|----------|----------|--------------|-------------------|------------------|--------------|

| S               |   |   |          |          |          |              |                   |                  |              |

| I2CM<br>DATA_ST | x | x | TBE      | x        | TBF      | RBE          | x                 | RBF              | 0XE6         |

| S<br>I2CM       |   |   |          |          | FOANIA   | FUNE         | EOVF              |                  | 0            |

| TXRX_IE         | x | х | x        | EDNA     | ESANA    | EUNF         |                   | ENEND            | 0xE7         |

| AIE             | - | - | -        | -        | -        | -            | -                 | -                | 0xE8         |

| PALT0           | x | x | T2_EX_EN | T2_IN_EN | T1_IN_EN | T0_IN_E<br>N | EX1_IN_E<br>N     | EX0_IN_<br>EN    | 0xE9         |

| EXSLEEP         | x | x | x        | x        | x        | x            | further_sle<br>ep | supper_s<br>leep | 0xEA         |

|                 |   |   |          |          |          |              |                   |                  | 0xEB         |

| P1_WUEN         | - | - | -        | -        | -        | -            | -                 | -                | 0xEC         |

| P2_WUEN         | - | - | -        | -        | -        | -            | -                 | -                | 0xED         |

| P3_WUEN         | - | - | -        | -        | -        | -            | -                 | -                | 0xEE         |

|                 |   |   |          |          |          |              |                   |                  | 0xEF         |

| В               |   |   |          |          |          |              |                   |                  | 0xF0         |

|                 |   |   |          |          |          |              |                   |                  | 0xF1         |

|                 |   |   |          |          |          |              |                   |                  | 0xF2         |

|                 |   |   |          |          |          |              |                   |                  | 0xF3         |

|                 |   |   |          |          |          |              |                   |                  | 0xF4<br>0xF5 |

|                 |   |   |          |          |          |              |                   |                  | 0xF6         |

|                 |   |   |          |          |          |              |                   |                  |              |

| PALT1           |   |   | PCA_IO   | PWM_IO   |          | UART0_I<br>O | SPI_IO            | 12C_10           | 0xF7         |

| AIP             | - | - | -        | -        | -        | -            | -                 | -                | 0xF8         |

|                 |   |   |          |          |          |              |                   |                  | 0xF9         |

| P1_WUM<br>OD    | - | - | -        | -        | -        | -            | -                 | -                | 0xFA         |

| P2_WUM<br>OD    | - | - | -        | -        | -        | -            | -                 | -                | 0xFB         |

| P3_WUM<br>OD    | - | - | -        | -        | -        | -            | -                 | -                | 0xFC         |

|                 |   |   |          |          |          |              |                   |                  | 0xFD         |

|                 |   |   |          |          |          |              |                   |                  | 0xFE         |

|                 |   |   |          |          |          |              |                   |                  | 0xFF         |

|                 |   | 1 | 1        | 1        | l        | 1            | 1                 | 1                |              |

### Table 3 Special Function Registers Memory Map

### 5.2.4.6. SFR table for MCU part

| Register | Address | Description            | Reset value |

|----------|---------|------------------------|-------------|

| ACC      | 0xE0    | Accumulator            | 00h         |

| В        | 0xF0    | B Register             | 00h         |

| DPH      | 0x83    | Data Pointer high byte | 00h         |

| DPL      | 0x82    | Data Pointer low byte  | 00h         |

Y

| DPSEL | 0x92 | Data Pointer selection     | 00h |

|-------|------|----------------------------|-----|

| IE    | 0xA8 | Interrupt Enable Control   | 00h |

| IP    | 0xB8 | Interrupt Priority Control | 00h |

| MPAGE | 0xA1 | Memory page register       | 00h |

| PCON2 | 0x86 | Power Control              | 00h |

| PSW   | 0xD0 | Program Status Word        | 00h |

| SP    | 0x81 | Stack Pointer              | 07h |

### Table 4 Core SFRs

| Register | Address | Description                   | Reset value |

|----------|---------|-------------------------------|-------------|

| AIE      | 0xE8    | Additional interrupt enable   | 00h         |

| AIF      | 0xC0    | Additional interrupt flag     | 00h         |

| AIP      | 0xF8    | Additional interrupt priority | 00h         |

### Table 5 Additional interrupt SFRs

|          | 1       |                            | -         |

|----------|---------|----------------------------|-----------|

| Register | Address | Description                | RST value |

| P0       | 0x80    | Port0 value                | 0xFF      |

| P0IN_EN_ | 0x91    | Port input enable, active  | 0xFF      |

|          |         | high                       |           |

| P0OUT_N_ | 0x9A    | Port output enable, active | 0xFF      |

|          |         | low                        |           |

| P0_PU    | 0xA9    | Port pull-up selection     | 0xFF      |

| P0_PD    | 0xAE    | Port pull-down selection   | 0x00      |

| P0_OPDR  | 0xD8    | Open drain selection       | 0x00      |

| P0_WUEN  | 0xEB    | Port wake up enable        | 0x00      |

| P0_WKMOD | 0xF9    | Port wake up mode          | 0x00      |

| A        |         | selection                  |           |

| P1       | 0x80    | Port0 value                | 0xFF      |

| P1IN_EN_ | 0x93    | Port input enable, active  | 0xFF      |

|          |         | high                       |           |

| P1OUT_N_ | 0x9E    | Port output enable, active | 0xFF      |

|          |         | low                        |           |

| P1_PU    | 0xAA    | Port pull-up selection     | 0xFF      |

| P1_PD    | 0xAF    | Port pull-down selection   | 0x00      |

| P1_OPDR  | 0xD9    | Open drain selection       | 0x00      |

| P1_WUEN  | 0xEC    | Port wake up enable        | 0x00      |

| P1_WKMOD | 0xFA    | Port wake up mode          | 0x00      |

|          |         | selection                  |           |

| P2       | 0xA0    | Port0 value                | 0xFF      |

| P2IN_EN_ | 0x94    | Port input enable, active  | 0xFF      |

|          |         | high                       |           |

| P2OUT_N_ | 0x9F    | Port output enable, active | 0xFF      |

|          |         | low                        |           |

| P2_PU    | 0xAB | Port pull-up selection            | 0xFF   |

|----------|------|-----------------------------------|--------|

| P2_PD    | 0XB4 | Port pull-down selection          | 0x00   |

| P2_OPDR  | 0xDA | Open drain selection              | 0x00   |

| P2_WUEN  | 0xED | Port wake up enable               | 0x00   |

| P2_WKMOD | 0xFB | Port wake up mode selection       | 0x00   |

| P3       | 0xB0 | Port0 value                       | 0xFF   |

| P3IN_EN_ | 0x95 | Port input enable, active<br>high | 0xFF   |

| P3OUT_N_ | 0Xa5 | Port output enable, active low    | 0xFF   |

| P3_PU    | 0xAC | Port pull-up selection            | 0xFF   |

| P3_PD    | 0xB5 | Port pull-down selection          | 0x00   |

| P3_OPDR  | 0xDB | Open drain selection              | 🚩 0x00 |

| P3_WUEN  | 0xEE | Port wake up enable               | 0x00   |

| P3_WKMOD | 0xFC | Port wake up mode selection       | 0x00   |

| P4       | 0xB7 | Port0 value                       | 0xFF   |

| P4IN_EN_ | 0x96 | Port input enable, active high    | 0xFF   |

| P4OUT_N_ | 0xa7 | Port output enable, active low    | 0xFF   |

| P4_PU    | 0xAD | Port pull-up selection            | 0xFF   |

| P4_PD    | 0xB6 | Port pull-down selection          | 0x00   |

| P4_OPDR  | 0xDC | Open drain selection              | 0x00   |

| P4_WUEN  | 0xEF | Port wake up enable               | 0x00   |

| P4_WKMOD | 0xFD | Port wake up mode selection       | 0x00   |

### Table 6 I/O ports SFRs

NOTE: some ports are not available in BK2535; please refer to the package information.

| Register | Address | Description    | Reset value |

|----------|---------|----------------|-------------|

| SBUF     | 0x99    | Serial Buffer  | 00h         |

| SCON     | 0x98    | Serial Control | 00h         |

### Table 7 Serial Port SFRs

| Register | Address | Description                   | RST value |

|----------|---------|-------------------------------|-----------|

| T2CON    | 0xC8    | Timer/Counter 2 control       | 00h       |

| TCON     | 0x88    | Timer/Counter 0 and 1 control | 00h       |

| TH0      | 0x8C    | Timer/Counter 0 high byte     | 00h       |

| TH1      | 0x8D    | Timer/Counter 1 high byte     | 00h       |

| TH2      | 0xCD    | Timer/Counter 2 high byte     | 00h       |

| TL0    | 0x8A | Timer/Counter 0 low byte           | 00h |

|--------|------|------------------------------------|-----|

| TL1    | 0x8B | Timer/Counter 1 low byte           | 00h |

| TL2    | 0xCC | Timer/Counter 2 low byte           | 00h |

| TMOD   | 0x89 | Timer/Counter 0 and 1 mode control | 00h |

| RCAP2H | 0xCB | Timer 2 Reload/Capture high byte   | 00h |

| RCAP2L | 0xCA | Timer 2 Reload/Capture low byte    | 00h |

| WDTRST | 0xA6 | WDT enable register                | 00h |

#### Table 8 Timers SFRs

| Register | Address | Description                    | RST value |

|----------|---------|--------------------------------|-----------|

| CCMCON   | 0x8E    | BIRD Communication Control     | 00h       |

| CCMVAL   | 0x8F    | BIRD Communication Value       | 00h       |

| MMS      | 0x97    | Reserved for emulation purpose | 07h       |

#### Table 9 BIRD SFRs

#### 5.3. Power management

For applications where power consumption is critical, the BK2535 provides all kinds of power saving modes.

#### 5.3.1. Power Control Register

|           |        |      |       | and the second s |        |           | 1      |      |

|-----------|--------|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------|--------|------|

| PCON2     | 7      | 6    | 5     | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3      | 2         | 1      | 0    |

| 1 0 0 112 |        | v    | U V   | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        | -         | •      | •    |

| 0x87      | SMOD   | EUSB | CMD R | Latch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Deep s | OSC32     | RC32k  | IDLE |

| 0,01      | 510100 | LOJD |       | Laten_                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Deep_3 | 05052     | NCJZK_ | IDLL |