# BL0942 datasheet

# BL0942 Calibration-

BL0942

Free Metering

Chip Data

Sheet

#### Table of contents

| 1 | Product | Brief 4                                            |

|---|---------|----------------------------------------------------|

|   | 1.1     | Function Introduction                              |

|   | 1.2     | Main Features                                      |

|   | 1.3     | System Block Diagram5                              |

|   | 1.4     | Package and Pin Description6                       |

|   | 1.5     | Register List                                      |

|   | 1.6     | Special Register Description9                      |

|   | 1.7     | Performance indicators11                           |

|   | 1.7.    | 1 Electrical parameter performance11               |

|   | 1.7.    | 2 Limit range                                      |

| 2 | Functio | nal description                                    |

|   | 2.1     | Current and voltage transient waveform measurement |

|   | 2.2     | Active power                                       |

|   | 2.3     | Active power anti-submarine motion14               |

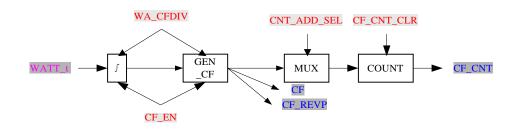

|   | 2.4     | Energy Metering                                    |

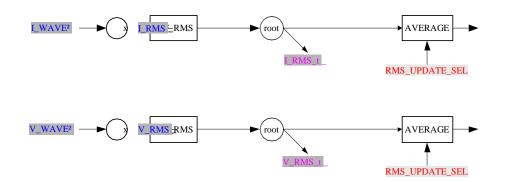

|   | 2.5     | RMS value of current and voltage 16                |

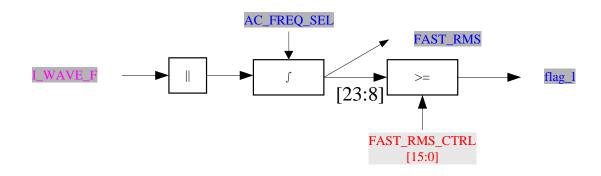

|   | 2.6     | Overcurrent Detection                              |

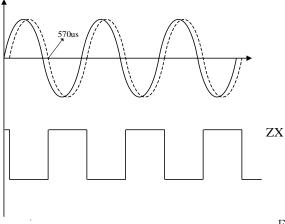

|   | 2.7     | Zero-crossing detection                            |

|   | 2.8     | Line voltage frequency detection                   |

| 3 | Communi | cation interface                                   |

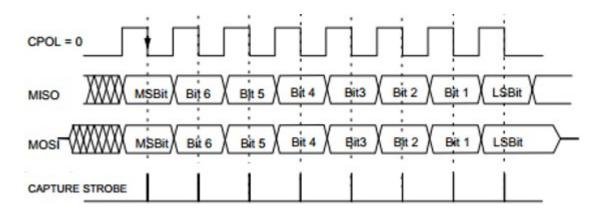

|   | 3.1     | SPI                                                |

|   | 3.1.    | 1 Working mode                                     |

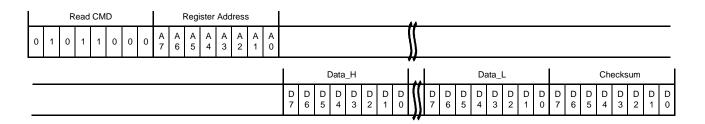

|   | 3.1.    | 2 frame structure                                  |

**BL0942**

# **BL0942** 内置时钟免校准计量芯片

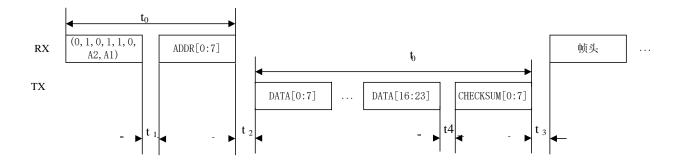

|     | 3.1.3                       | Write Operation Timing23                  |  |  |  |  |

|-----|-----------------------------|-------------------------------------------|--|--|--|--|

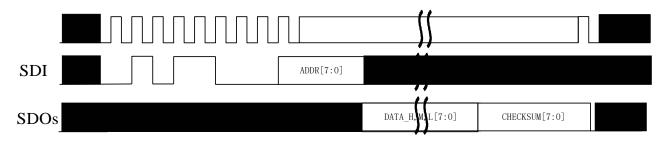

|     | 3.1.4                       | Read Operation Timing24                   |  |  |  |  |

|     | 3.1.5                       | SPI Interface Fault Tolerance Mechanism24 |  |  |  |  |

| 3.2 | UA                          | RT25                                      |  |  |  |  |

|     | 3.2.1                       | Baud Rate Configuration 25                |  |  |  |  |

|     | 3.2.2                       | 25 per byte format                        |  |  |  |  |

|     | 3.2.3                       | Write Timing                              |  |  |  |  |

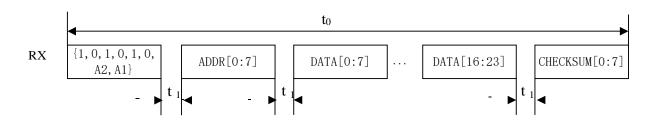

|     | 3.2.4                       | Read Timing                               |  |  |  |  |

|     | 3.2.5                       | Timing Description                        |  |  |  |  |

|     | 3.2.6                       | Packet Send Mode                          |  |  |  |  |

|     | 3.2.7                       | UART Interface Protection Mechanism29     |  |  |  |  |

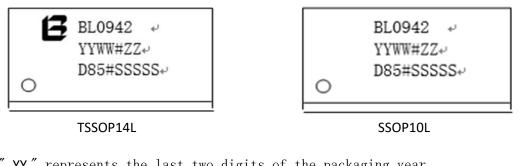

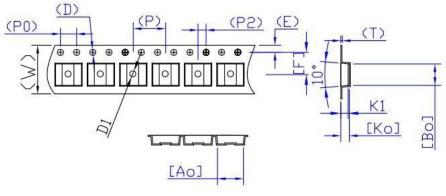

| 0rd | ler Info                    | rmation                                   |  |  |  |  |

| Scr | Screen printing information |                                           |  |  |  |  |

| pac | kages .                     |                                           |  |  |  |  |

4

5

6

# 1 Product description

#### 1.1 Function introduction

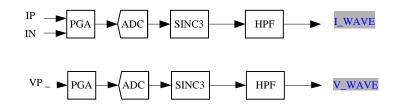

**BL0942** is a calibration-free energy metering chip with a built-in clock, suitable for single-phase multi-function energy meters, smart sockets, smart home appliances and other applications, with high cost performance.

BL0942

**BL0942** integrates 2- way high-precision Sigma-Delta ADC , analog circuit modules such as reference voltage, power management, and digital signal processing circuits for processing electrical parameters such as active power, current and voltage RMS.

**BL0942** can measure parameters such as current, voltage RMS, active power, active energy, etc., and can output fast current RMS (for overcurrent protection), as well as waveform output and other functions, and output data through UART/SPI interface, which can fully meet the requirements of intelligent The needs of fields such as sockets, smart home appliances, single-phase multi-function electric energy meters, and big data collection of electricity consumption information.

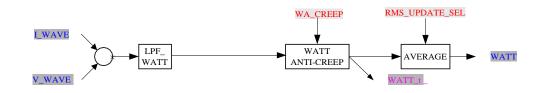

**BL0942** has a patented anti-creep design, combined with a reasonable external hardware design, it can ensure that the noise power is not included in the energy pulse when there is no current.

#### 1.2 main feature

- Two independent Sigma-Delta ADCs, one current and one voltage.

- RMS current range ( 10mA~30A ) @1mohm

- Active energy (1w~6600w) @1mohm@220V

- Can output current, voltage RMS, fast current RMS, active power

- The batch factory gain error is less than 1%, and the external components can be exempted from calibration if they meet certain conditions

- The current channel has an overcurrent monitoring function, and the monitoring threshold and response time can be set

- Voltage / current zero-crossing signal output

- Built-in waveform register, which can output waveform data for load type analysis

- SPI ( the fastest rate supports 900KHz) /UART ( 4800-38400bps) communication method ( TSSOP14L Package supports up to 4 slice cascading

- Power down monitoring, below 2.7V, the chip enters the reset state

- Built-in **1.218V** reference voltage source

- Built-in oscillation circuit, the clock is about 4MHz

- Chip single working power supply 3.3V, low power consumption 10mW (typical value)

BL0942

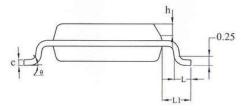

• SSOP10L/TSSOP14L encapsulation

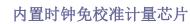

### 1.3 System Block Diagram

*BL0942*

Figure 1

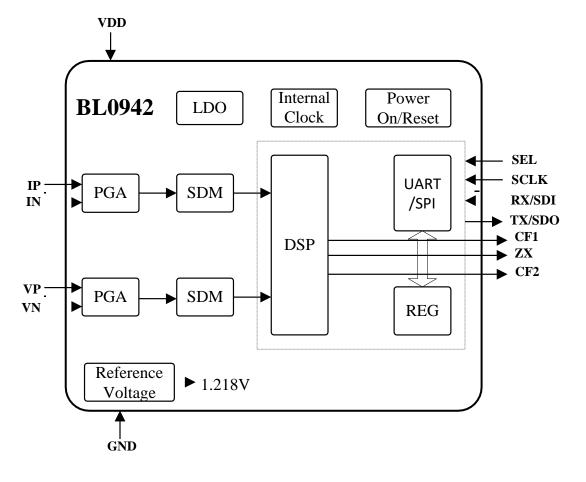

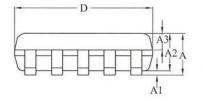

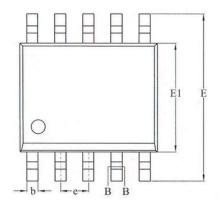

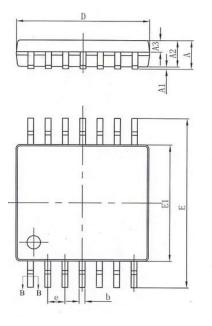

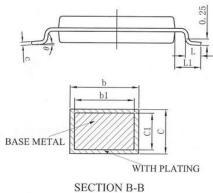

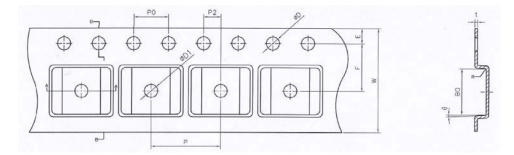

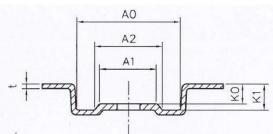

# 1.4 Package and Pin Description

*BL0942*

Figure 2

Pin Description ( SSOP10L)

| pin | symbol   | illu                                                             |  |  |  |  |  |  |  |

|-----|----------|------------------------------------------------------------------|--|--|--|--|--|--|--|

| No  |          | stra                                                             |  |  |  |  |  |  |  |

|     |          | te                                                               |  |  |  |  |  |  |  |

| 1   | VDD      | Power supply ( +3.3V)                                            |  |  |  |  |  |  |  |

| 2,3 | IP,IN    | Current channel analog input, the maximum differential           |  |  |  |  |  |  |  |

|     |          | voltage of the pins is ±42mV (30mV rms)                          |  |  |  |  |  |  |  |

| 4   | VP       | Voltage signal input terminal, maximum differential              |  |  |  |  |  |  |  |

|     |          | voltage ±100mV (70mV rms)                                        |  |  |  |  |  |  |  |

| 5   | GND      | chip ground                                                      |  |  |  |  |  |  |  |

| 6   | CF1      | Power status output, which can be configured by the              |  |  |  |  |  |  |  |

|     |          | <b>OT_FUNX</b> register to output a variety of power information |  |  |  |  |  |  |  |

| 7   | SEL      | UART/SPICommunication mode selection (0: UART 1:                 |  |  |  |  |  |  |  |

|     |          | SPI), internal pull-down resistor,                               |  |  |  |  |  |  |  |

|     |          | Floating is $0$ level ( UART), and the pin is directly connected |  |  |  |  |  |  |  |

|     |          | to VDD to be high level ( SPI)                                   |  |  |  |  |  |  |  |

| 8   | SCLK_BPS | SPI mode clock input, selectable baud rate in UART mode          |  |  |  |  |  |  |  |

| 9   | RX/SDI   | UART/SPI multiplexing pin, UART RX/SPI DIN, external pull-       |  |  |  |  |  |  |  |

|     |          | up is required in UART mode                                      |  |  |  |  |  |  |  |

|     |          | resistance                                                       |  |  |  |  |  |  |  |

| 10  | TX/SDO   | UART/SPI multiplexed pin, UART TX/SPI DOUT, needs to be          |  |  |  |  |  |  |  |

|     |          | connected externally in UART mode                                |  |  |  |  |  |  |  |

|     |          | pull resistor                                                    |  |  |  |  |  |  |  |

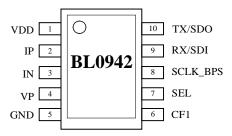

#### Pin Description ( TSSOP14L)

| in     | a semb a 1 | illu                                                                       |  |  |  |  |  |  |  |

|--------|------------|----------------------------------------------------------------------------|--|--|--|--|--|--|--|

| pin    | symbol     |                                                                            |  |  |  |  |  |  |  |

| number |            | stra<br>te                                                                 |  |  |  |  |  |  |  |

|        |            |                                                                            |  |  |  |  |  |  |  |

| 1      | VDD        | Power supply ( +3.3V)                                                      |  |  |  |  |  |  |  |

| 2,3    | IP,IN      | Current channel analog input, the maximum differential voltage             |  |  |  |  |  |  |  |

|        |            | of the pins at the default gain of $16 \text{ is } \pm 42 \text{mV}$ (30mV |  |  |  |  |  |  |  |

|        |            | rms) ;                                                                     |  |  |  |  |  |  |  |

| 4      | VP         | Voltage signal input terminal, maximum differential voltage                |  |  |  |  |  |  |  |

|        |            | ±100mV (70mV rms)                                                          |  |  |  |  |  |  |  |

| 5      | GND        | chip ground                                                                |  |  |  |  |  |  |  |

| 6      | A1         | UART mode, it is used as the low address of the chip select                |  |  |  |  |  |  |  |

|        |            | function. Internal default dropdown.                                       |  |  |  |  |  |  |  |

| 7      | A2_NCS     | UART mode, it is used as the high address of the chip select               |  |  |  |  |  |  |  |

|        |            | function. In SPI mode, as CS chip select control,                          |  |  |  |  |  |  |  |

|        |            | Active low. Internal default dropdown.                                     |  |  |  |  |  |  |  |

| 8      | CF2        | Power status output, which can be configured by the OT_FUNX                |  |  |  |  |  |  |  |

|        |            | register to output a variety of power information                          |  |  |  |  |  |  |  |

| 9      | ZX         | The zero-crossing monitoring output pin can be configured by               |  |  |  |  |  |  |  |

|        |            | the <b>OT_FUNX</b> register to output a variety of electric energy         |  |  |  |  |  |  |  |

|        |            | information                                                                |  |  |  |  |  |  |  |

| 10     | CF1        | Power status output, which can be configured by the $OT_{FUNX}$            |  |  |  |  |  |  |  |

|        |            | register to output a variety of power information                          |  |  |  |  |  |  |  |

| 11     | SEL        | UART/SPI Communication mode selection (0: UART 1: SPI),                    |  |  |  |  |  |  |  |

|        |            | there is a pull-down resistor inside , and it is                           |  |  |  |  |  |  |  |

|        |            | It is Olevel ( UART), and the pin is directly connected to                 |  |  |  |  |  |  |  |

|        |            | VDD, which is high level (SPI)                                             |  |  |  |  |  |  |  |

| 12     | SCLK_BPS   | SPI mode clock input, selectable baud rate in UART mode                    |  |  |  |  |  |  |  |

| 13     | RX/SDI     | UART/SPI multiplexing pin, UART RX/SPI DIN, external pull-up               |  |  |  |  |  |  |  |

|        |            | resistor is required in UART mode                                          |  |  |  |  |  |  |  |

| SHAN |        | ■ <b>BL0942</b> 内置时钟免校准计量芯片                                   |

|------|--------|---------------------------------------------------------------|

| 14   | TX/SDO | UART/SPI multiplexing pin, UART TX/SPI DOUT, external pull-up |

|      |        | resistor is required in UART mode                             |

# 1.5 register list

| essnal<br>read /<br>read /<br>writenal<br>writeclan<br>t<br>bit0x01L_WAVERW200x00000Current waveform register, signed0x02V_WAVERW200x000000Current RMS register, signed0x03L_RMSRW200x000000Current RMS register, unsigned0x04V_RMSRWtwo0x000000Current RMS register, unsigned0x05L_FAST_RMSRWtwo0x000000Current Fast RMS Register,<br>unsigned0x06WATTRWtwo0x000000Current Fast RMS Register,<br>unsigned0x06WATTRWtwo0x000000Active power register, signed0x07CF_CNTRWtwo0x000000Active power register, signed0x08FREQRW160x4E20LINE VOLTAGE FREQUEXCY REGISTER0x09STATUSRW100x000status register0x14WA_CREEPR/WR80x00Current RMS Small Signal<br>Correction Register0x14UA_CREEPR/WR30x1Current Fast RMS Refresh Period<br>Register0x16L_FAST_RMS<br>CYCR/WR60x24Output Configuration Register0x14WA_CREEPR/WR60x24Output Configuration Register0x14WA_CREEPR/WR100x87Current Fast RMS Refresh Period<br>Register0x15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1.1. |             | exter   | inter  | effi     |               | 1                                       |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------|---------|--------|----------|---------------|-----------------------------------------|--|--|--|--|--|

| readreadreadreadreadreadreadreadreadwritewritebit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | addr | name        | nal     | nal    | cien     | Defaults      | describe                                |  |  |  |  |  |

| Electric parameter<br>register (read only)           Ox01         I_WAVE         R         W         20         0x00000         Current waveform register, signed           0x02         V_WAVE         R         W         20         0x00000         Current RMS register, unsigned           0x03         I_RMS         R         W         twen         0x000000         Current RMS register, unsigned           0x04         V_RMS         R         W         twen         0x000000         Voltage rms register, unsigned           0x05         I_FAST_RMS         R         W         twen         0x000000         Current Fast RMS Register,<br>Unsigned           0x06         WATT         R         W         twen         0x000000         Active power register, signed           0x06         WATT         R         W         twen         0x000000         Active power register, signed           0x07         CF_CNT         R         W         twen         0x000000         Active energy pulse count           ty         four         I         0x00000         Active energy pulse count         register, unsigned           0x08         FREQ         R         W         16         0x4E20         LINE VOLTAGE FREQUENCY REGISTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 635  |             |         | read / | t        |               |                                         |  |  |  |  |  |

| register (read only)0x01I_WAVERW200x00000Current waveform register, signed0x02V_WAVERW200x00000Voltage waveform register, signed0x03I_RMSRWtwen<br>four0x000000Current RMS register, unsigned0x04V_RMSRWtwen<br>four0x000000Voltage rms register, unsigned0x04V_RMSRWtwen<br>four0x000000Current Fast RMS Register,<br>Unsigned0x05I_FAST_RMSRWtwen<br>four0x000000Active power register, signed<br>ty0x06WATTRWtwen<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |             | write   | write  |          |               |                                         |  |  |  |  |  |

| Ox01     I_WAVE     R     W     20     0x00000     Current waveform register, signed       Ox02     V_WAVE     R     W     20     0x000000     Voltage waveform register, signed       Ox03     I_RMS     R     W     twen     0x000000     Current RMS register, unsigned       Ox04     V_RMS     R     W     twen     0x000000     Current RMS register, unsigned       0x04     V_RMS     R     W     twen     0x000000     Current Fast RMS Register, unsigned       0x05     I_FAST_RMS     R     W     twen     0x000000     Current Fast RMS Register, unsigned       0x06     WATT     R     W     twen     0x000000     Active power register, signed       0x07     CF_CNT     R     W     twen     0x000000     Active energy pulse count register, unsigned       0x08     FREQ     R     W     twen     0x00000     Active energy pulse count register       0x09     STATUS     R     W     10     0x000     Status register       0x12     I_RMSOS     R/W     R     8     0x00     Current RMS Small Signal Correction Register       0x14     WA_CREEP     R/W     R     8     0x08     Active power anti-passage register       0x12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |             |         |        |          |               |                                         |  |  |  |  |  |

| DX02     V_WAVE     R     W     20     0x00000     Voltage waveform register, signed       Dx03     I_RMS     R     W     twen     0x000000     Current RMS register, unsigned       Dx04     V_RMS     R     W     twen     0x000000     Voltage rms register, unsigned       0x04     V_RMS     R     W     twen     0x000000     Voltage rms register, unsigned       0x05     I_FAST_RMS     R     W     twen     0x000000     Current Fast RMS Register, Unsigned       0x06     WATT     R     W     twen     0x000000     Active power register, signed       0x07     CF_CNT     R     W     twen     0x000000     Active power register, unsigned       0x08     FREQ     R     W     16     0x4E20     LINE VOLTAGE FREQUENCY REGISTER       0x09     STATUS     R     W     10     0x00     status register       0x12     I_RMSOS     R/W     R     8     0x08     Active power anti-passage register       0x14     WA_CREEP     R/W     R     8     0x08     Active power anti-passage register       0x14     UA_CREEP     R/W     R     16     0xFFF     Current Fast RMS Refresh Period Register       0x14     WA_CREEP     <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0.01 |             |         |        |          |               |                                         |  |  |  |  |  |

| Dx03     I_RMS     R     W     twen<br>ty<br>four     0x00000     Current RMS register, unsigned       0x04     V_RMS     R     W     twen<br>ty<br>four     0x000000     Voltage rms register, unsigned       0x05     I_FAST_RMS     R     W     twen<br>ty     0x000000     Current Fast RMS Register,<br>Unsigned       0x06     WATT     R     W     twen<br>ty     0x000000     Active power register, signed       0x07     CF_CNT     R     W     twen<br>ty     0x000000     Active energy pulse count<br>register, unsigned       0x08     FREQ     R     W     16     0x4E20     LINE VOLTAGE FREQUENCY REGISTER       0x09     STATUS     R     W     10     0x000     status register       0x12     I_RMSOS     R/W     R     8     0x08     Active power anti-passage register       0x14     WA_CREEP     R/W     R     8     0x08     Active power anti-passage register       0x14     UA_CREEP     R/W     R     8     0x08     Active power anti-passage register       0x15     I_FAST_RMS_<br>TH     R/W     R     16     0xFFFF     Current Fast RMS Refresh Period<br>Register       0x14     WA_CREEP     R/W     R     2     0x3     Line Voltage Frequency Refresh<br>Period Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |             |         |        |          |               |                                         |  |  |  |  |  |

| Image: Constraint of the second sec                 |      | —           |         |        |          |               |                                         |  |  |  |  |  |

| NoteNoteNoteNoteNote0x04V_RMSRWtwen<br>ty<br>four0x000000Voltage rms register, unsigned<br>ty<br>four0x05I_FAST_RMSRWtwen<br>ty<br>four0x000000Current Fast RMS Register,<br>Unsigned0x06WATTRWtwen<br>four0x000000Active power register, signed<br>ty<br>four0x06WATTRWtwen<br>ty<br>four0x000000Active power register, signed<br>register, unsigned0x07CF_CNTRWtwen<br>ty<br>four0x000000Active energy pulse count<br>register, unsigned0x08FREQRW160x4E20LINE VOLTAGE FREQUENCY REGISTER0x09STATUSRW100x000status register0x12I_RMSOSR/WR80x00Current RMS Small Signal<br>Correction Register0x14WA_CREEPR/WR80x0BActive power anti-pasage register0x14I_FAST_RMS_<br>THR/WR160x4FFFCurrent Fast RMS Refresh Period<br>Register0x16I_FAST_RMS_<br>CVCR/WR30x1Current Fast RMS Refresh Period<br>Register0x17FREQ_CYCR/WR60x24Output Configuration Register0x18OT_FUNXR/WR100x87User Mode Select Register0x19MODER/WR100x87User Mode Select Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0x03 | I_RMS       | R       | W      |          | 0x000000      | Current RMS register, unsigned          |  |  |  |  |  |

| Ox04     V_RMS     R     W     twen<br>ty<br>four     0x000000<br>0x000000     Voltage rms register, unsigned       0x05     I_FAST_RMS     R     W     twen<br>four     0x000000     Current Fast RMS Register,<br>Unsigned       0x06     WATT     R     W     twen<br>four     0x000000     Active power register, signed       0x07     CF_CNT     R     W     twen<br>four     0x000000     Active energy pulse count<br>register, unsigned       0x08     FREQ     R     W     16     0x4220     LINE VOLTAGE FREQUENCY REGISTER       0x09     STATUS     R     W     10     0x000     status register       0x12     I_RMSOS     R/W     R     8     0x00     Current RMS Small Signal<br>Correction Register       0x14     WA_CREEP     R/W     R     8     0x08     Active power anti-passage register       0x15     I_FAST_RMS_<br>TH     R/W     R     16     0xFFFF     Current Fast RMS Refresh Period<br>Register       0x16     I_FAST_RMS_<br>CYC     R/W     R     2     0x3     Line Voltage Frequency Refresh<br>Period Register       0x17     FREQ_CYC     R/W     R     6     0x24     Output Configuration Register       0x18     OT_FUNX     R/W     R     10     0x87     User Mode Select Re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |             |         |        | -        |               |                                         |  |  |  |  |  |

| DecisionLength of the fourty<br>fourOx000000<br>Ox000000Current Fast RMS Register,<br>Unsigned0x06WATTRWtwen<br>four0x000000<br>fourActive power register, signed<br>ty<br>four0x07CF_CNTRWtwen<br>four0x000000<br>fourActive energy pulse count<br>register, unsigned<br>four0x07CF_CNTRWtwen<br>four0x000000<br>fourActive energy pulse count<br>register, unsigned<br>four0x08FREQRW160x4E20LINE VOLTAGE FREQUENCY REGISTER<br>User operation<br>rregister0x09STATUSRW100x000Status register0x12I_RMSOSR/WR80x0BActive power anti-passage register<br>urrite)0x14WA_CREEPR/WR80x0BActive power anti-passage register0x16I_FAST_RMS_<br>CYCR/WR160xFFFFCurrent Fast RMS Refresh Period<br>Register0x17FREQ_CYCR/WR20x3Line Voltage Frequency Refresh<br>Period Register0x18OT_FUNXR/WR100x87User Mode Select Register0x14GAIN_CRR/WR100x87User Mode Select Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0×04 |             | D       | \٨/    |          | 0×000000      | Voltago rms registor unsigned           |  |  |  |  |  |

| Image: FAST_RMSRWfourCurrent Fast RMS Register,<br>Unsigned0x06WATTRWtwen<br>tw0x00000<br>twActive power register, signed0x06WATTRWtwen<br>tw0x000000<br>tyActive power register, signed0x07CF_CNTRWtwen<br>tw0x00000<br>tyActive energy pulse count<br>register, unsigned0x08FREQRW160x4E20LINE V0LTAGE FREQUENCY REGISTER0x09STATUSRW100x000Status register0x12I_RMSOSR/WR80x00Current RMS Small Signal<br>Correction Register0x14WA_CREEPR/WR80x00Current Fast RMS Threshold<br>Register0x16I_FAST_RMS_<br>CYCR/WR160xFFFFCurrent Fast RMS Threshold<br>Register0x17FREQ_CYCR/WR20x3Line Voltage Frequency Refresh<br>Period Register0x18OT_FUNXR/WR60x42Output Configuration Register0x18OT_FUNXR/WR100x87User Mode Select Register0x18GAIN_CRR/WR100x87User Mode Select Register0x18GAIN_CRR/WR100x87User Mode Select Register0x18GAIN_CRR/WR100x87User Mode Select Register0x14GAIN_CRR/WR100x87User Mode Select Register<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0x04 | v_RIVI3     | n       | vv     |          | 0,000000      | voltage ims register, unsigned          |  |  |  |  |  |

| Image: Constraint of the second sec                 |      |             |         |        | -        |               |                                         |  |  |  |  |  |

| Image: series of the series                  | 0x05 | I_FAST_RMS  | R       | W      | twen     | 0x000000      | Current Fast RMS Register,              |  |  |  |  |  |

| 0x06WATTRWtwen<br>ty<br>four0x000000Active power register, signed0x07CF_CNTRWtwen<br>ty<br>four0x000000Active energy pulse count<br>register, unsigned0x08FREQRW160x4E20LINE VOLTAGE FREQUENCY REGISTER<br>operation<br>register0x09STATUSRW100x000Status register0x12I_RMSOSR/WR80x00Current RMS Small Signal<br>Correction Register0x14WA_CREEPR/WR80x0BActive power anti-passage register0x15I_FAST_RMS_<br>THR/WR160xFFFFCurrent Fast RMS Threshold<br>Register0x16I_FAST_RMS_<br>CYCR/WR20x3Line Voltage Frequency Refresh<br>Period Register0x17FREQ_CYCR/WR60x24Output Configuration Register0x18OT_FUNXR/WR100x87User Mode Select Register0x14GAIN_CRR/WR100x87User Mode Select Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |             |         |        | ty       |               | Unsigned                                |  |  |  |  |  |

| Image: Constraint of the second sec                 |      |             |         |        | four     |               |                                         |  |  |  |  |  |

| Image: Note of the image: Note of t                 | 0x06 | WATT        | R       | W      |          | 0x000000      | Active power register, signed           |  |  |  |  |  |

| 0x07CF_CNTRWtwen<br>ty<br>four0x000000Active energy pulse count<br>register, unsigned0x08FREQRW160x4E20LINE VOLTAGE FREQUENCY REGISTER0x09STATUSRW100x000status register0x012I_RMSOSR/WR80x00Current RMS Small Signal<br>Correction Register0x14WA_CREEPR/WR80x00Current FASS Small Signal<br>Correction Register0x15I_FAST_RMS_<br>THR/WR160xFFFFCurrent Fast RMS Threshold<br>Register0x16I_FAST_RMS_<br>CYCR/WR30x1Current Fast RMS Refresh Period<br>Register0x17FREQ_CYCR/WR20x3Line Voltage Frequency Refresh<br>Period Register0x18OT_FUNXR/WR100x87User Mode Select Register0x14GAIN_CRR/WR20x2Current Channel Gain Control<br>Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |             |         |        | -        |               |                                         |  |  |  |  |  |

| NoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNoteNo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0.07 |             | D       | 14/    |          | 0.000000      |                                         |  |  |  |  |  |

| Image: constraint of the state of the sta                 | 0x07 | CF_CN1      | к       | vv     |          | 0x000000      |                                         |  |  |  |  |  |

| 0x08FREQRW160x4E20LINE VOLTAGE FREQUENCY REGISTER0x09STATUSRW100x000status registerUser operation<br>register (read and<br>write)0x12I_RMSOSR/WR80x00Current RMS Small Signal<br>Correction Register0x14WA_CREEPR/WR80x0BActive power anti-passage register0x14WA_CREEPR/WR160xFFFFCurrent Fast RMS Threshold<br>Register0x16I_FAST_RMS_<br>CYCR/WR160x11Current Fast RMS Refresh Period<br>Register0x17FREQ_CYCR/WR20x3Line Voltage Frequency Refresh<br>Period Register0x18OT_FUNXR/WR100x87User Mode Select Register0x19MODER/WR20x2Current Channel Gain Control<br>Register0x1AGAIN_CRR/WR20x2Current Channel Gain Control<br>Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |             |         |        | -        |               | register, unsigneu                      |  |  |  |  |  |

| User operation register (read and write)         0x12       I_RMSOS       R/W       R       8       0x00       Current RMS Small Signal Correction Register         0x14       WA_CREEP       R/W       R       8       0x0B       Active power anti-passage register         0x14       WA_CREEP       R/W       R       8       0x0B       Active power anti-passage register         0x14       TH       R/W       R       16       0xFFFF       Current Fast RMS Threshold Register         0x16       I_FAST_RMS_<br>TH       R/W       R       3       0x1       Current Fast RMS Refresh Period Register         0x17       FREQ_CYC       R/W       R       2       0x3       Line Voltage Frequency Refresh Period Register         0x18       OT_FUNX       R/W       R       6       0x24       Output Configuration Register         0x19       MODE       R/W       R       10       0x87       User Mode Select Register         0x14       GAIN_CR       R/W       R       2       0x2       Current Channel Gain Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0x08 | FREQ        | R       | W      |          | 0x4E20        | LINE VOLTAGE FREQUENCY REGISTER         |  |  |  |  |  |

| register (read and write)         0x12       I_RMSOS       R/W       R       8       0x00       Current RMS Small Signal Correction Register         0x14       WA_CREEP       R/W       R       8       0x08       Active power anti-passage register         0x15       I_FAST_RMS_TH       R/W       R       16       0xFFFF       Current Fast RMS Threshold Register         0x16       I_FAST_RMS_CYC       R/W       R       3       0x1       Current Fast RMS Refresh Period Register         0x17       FREQ_CYC       R/W       R       2       0x3       Line Voltage Frequency Refresh Period Register         0x18       OT_FUNX       R/W       R       6       0x24       Output Configuration Register         0x19       MODE       R/W       R       10       0x87       User Mode Select Register         0x14       GAIN_CR       R/W       R       2       0x24       Output Configuration Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0x09 | STATUS      | R       | W      | 10       | 0x000         | status register                         |  |  |  |  |  |

| write)0x12I_RMSOSR/WR80x00Current RMS Small Signal<br>Correction Register0x14WA_CREEPR/WR80x0BActive power anti-passage register0x15I_FAST_RMS_<br>THR/WR160xFFFFCurrent Fast RMS Threshold<br>Register0x16I_FAST_RMS_<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |             |         |        | User     | operation     |                                         |  |  |  |  |  |

| 0x12I_RMSOSR/WRR80x00Current RMS Small Signal<br>Correction Register0x14WA_CREEPR/WR80x0BActive power anti-passage register0x15I_FAST_RMS_<br>THR/WR160xFFFFCurrent Fast RMS Threshold<br>Register0x16I_FAST_RMS_<br>CYCR/WR30x1Current Fast RMS Refresh Period<br>Register0x17FREQ_CYCR/WR20x3Line Voltage Frequency Refresh<br>Period Register0x18OT_FUNXR/WR60x24Output Configuration Register0x19MODER/WR20x2Current Channel Gain Control<br>Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |             |         |        | regist   | er (read a    | nd                                      |  |  |  |  |  |

| Image: Construction of the image: Construction RegisterConstruction Register0x14WA_CREEPR/WR80x0BActive power anti-passage register0x15I_FAST_RMS_<br>THR/WR160xFFFFCurrent Fast RMS Threshold<br>Register0x16I_FAST_RMS_<br>CYCR/WR30x1Current Fast RMS Refresh Period<br>Register0x17FREQ_CYCR/WR20x3Line Voltage Frequency Refresh<br>Period Register0x18OT_FUNXR/WR60x24Output Configuration Register0x19MODER/WR100x87User Mode Select Register0x1AGAIN_CRR/WR20x2Current Channel Gain Control<br>Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |             |         |        | 1        |               |                                         |  |  |  |  |  |

| Ox14WA_CREEPR/WR8Ox0BActive power anti-passage registerOx15I_FAST_RMS_<br>THR/WR16OxFFFFCurrent Fast RMS Threshold<br>RegisterOx16I_FAST_RMS_<br>CYCR/WR3Ox1Current Fast RMS Refresh Period<br>Register0x17FREQ_CYCR/WR2Ox3Line Voltage Frequency Refresh<br>Period Register0x18OT_FUNXR/WR6Ox24Output Configuration Register0x19MODER/WR100x87User Mode Select Register0x1AGAIN_CRR/WR2Ox2Current Channel Gain Control<br>Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0x12 | I_RMSOS     | R/W     | R      | 8        | 0x00          | _                                       |  |  |  |  |  |

| 0x15I_FAST_RMS_<br>THR/WR160xFFFFCurrent Fast RMS Threshold<br>Register0x16I_FAST_RMS_<br>CYCR/WR30x1Current Fast RMS Refresh Period<br>Register0x17FREQ_CYCR/WR20x3Line Voltage Frequency Refresh<br>Period Register0x18OT_FUNXR/WR60x24Output Configuration Register0x19MODER/WR100x87User Mode Select Register0x1AGAIN_CRR/WR20x2Current Channel Gain Control<br>Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0.11 |             | 5 / 1 / |        |          | 0.05          |                                         |  |  |  |  |  |

| Ox15THR/WR16OxFFFFCurrent Fast RMS Threshold<br>RegisterOx16I_FAST_RMS_<br>CYCR/WR3Ox1Current Fast RMS Refresh Period<br>RegisterOx17FREQ_CYCR/WR2Ox3Line Voltage Frequency Refresh<br>Period RegisterOx18OT_FUNXR/WR6Ox24Output Configuration RegisterOx19MODER/WR10Ox87User Mode Select RegisterOx1AGAIN_CRR/WR2Ox2Current Channel Gain Control<br>Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0x14 |             | R/W     | R      | 8        | OxOB          | Active power anti-passage register      |  |  |  |  |  |

| Ox16I_FAST_RMS_<br>CYCR/WR3Ox1Current Fast RMS Refresh Period<br>Register0x17FREQ_CYCR/WR20x3Line Voltage Frequency Refresh<br>Period Register0x18OT_FUNXR/WR60x24Output Configuration Register0x19MODER/WR100x87User Mode Select Register0x1AGAIN_CRR/WR20x2Current Channel Gain Control<br>Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0x15 |             | R/W     | R      | 16       | <b>OxFFFF</b> | Current Fast RMS Threshold              |  |  |  |  |  |

| Ox16CYCR/WR3Ox1Current Fast RMS Refresh Period<br>Register0x17FREQ_CYCR/WR2Ox3Line Voltage Frequency Refresh<br>Period Register0x18OT_FUNXR/WR6Ox24Output Configuration Register0x19MODER/WR100x87User Mode Select Register0x1AGAIN_CRR/WR20x2Current Channel Gain Control<br>Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      | IH          |         |        |          |               | Register                                |  |  |  |  |  |

| CYC       CYC       Register         0x17       FREQ_CYC       R/W       R       2       0x3       Line Voltage Frequency Refresh<br>Period Register         0x18       OT_FUNX       R/W       R       6       0x24       Output Configuration Register         0x19       MODE       R/W       R       10       0x87       User Mode Select Register         0x1A       GAIN_CR       R/W       R       2       0x2       Current Channel Gain Control<br>Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0.10 | I_FAST_RMS_ |         | P      | 2        | 01            | Comment Fract DMC D C 1 D 1 1           |  |  |  |  |  |

| Ox17FREQ_CYCR/WR2Ox3Line Voltage Frequency Refresh<br>Period RegisterOx18OT_FUNXR/WR6Ox24Output Configuration RegisterOx19MODER/WR10Ox87User Mode Select RegisterOx1AGAIN_CRR/WR2Ox2Current Channel Gain Control<br>Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0x16 | CYC         | R/W     | К      | 3        | 0x1           |                                         |  |  |  |  |  |

| Ox18     OT_FUNX     R/W     R     6     Ox24     Output Configuration Register       0x19     MODE     R/W     R     10     0x87     User Mode Select Register       0x1A     GAIN_CR     R/W     R     2     0x2     Current Channel Gain Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0,17 |             | D /\.   | D      | 2        | 0.2           |                                         |  |  |  |  |  |

| Ox18OT_FUNXR/WR6Ox24Output Configuration RegisterOx19MODER/WR100x87User Mode Select RegisterOx1AGAIN_CRR/WR20x2Current Channel Gain Control<br>Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | UX17 | ΓΚΕΨ_ΟΊΟ    | K/ VV   | К      | 2        | UX3           |                                         |  |  |  |  |  |