Ver 1.1

# In-System Programmable Configuration PROMs

# Datasheet

Part Number: BQ18V04

| Page of Revise Control | Page | of Re | evise | Control |

|------------------------|------|-------|-------|---------|

|------------------------|------|-------|-------|---------|

| Version<br>No. | Publish<br>Time | Revised<br>Chapter | Revise Introduction | Note |

|----------------|-----------------|--------------------|---------------------|------|

| 1.0            | 2017.6          |                    | Initial release.    |      |

| 1.1            | 2018.3          |                    | Update format       |      |

|                |                 |                    |                     |      |

|                |                 |                    |                     |      |

|                |                 |                    |                     |      |

|                |                 |                    |                     |      |

|                |                 |                    |                     |      |

|                |                 |                    |                     |      |

|                |                 |                    |                     |      |

# **TABLE OF CONTENTS**

| 1. | Features                               |

|----|----------------------------------------|

| 2. | Description1                           |

| 3. | Structure                              |

| 4. | Pinout and Pin Description             |

| 5. | Product Description                    |

|    | 5.1 Connecting BQ18V04                 |

|    | 5.2 Operation Timing                   |

|    | 5.3 Initiating FPGA Configuration      |

|    | 5.4 Configuration Modes                |

|    | 5.5 Cascading Configuration            |

|    | 5.6 Reset Activation                   |

|    | 5.7 Standby Mode                       |

|    | 5.8 In-System Programming              |

|    | 5.9 JTAG Protocol Compatibility7       |

| 6. | Electrical Parameters                  |

|    | 6.1 Operating Conditions               |

|    | 6.2 Recommended Operating Conditions10 |

| 7. | Package Description                    |

## 1. Features

• In-system programmable 3.3V 4-megabit FLASH-based PROMs

- Applicable for configuration of The BMTI of Aerospace and Xilinx Inc

FPGAs

- Data retention time: 20 years

- Endurance of 2,000 program/erase cycles over full military temperature

range

- Reliability

- Temperature range :  $-55^{\circ}$  ~  $+125^{\circ}$

- Antistatic ability(human boby model) : 2000V

- Class B of GJB597A and GJB548A-96

- IEEE Std 1149.1 boundary-scan (JTAG) support

- JTAG command initiation of standard FPGA configuration

- Multiple configuration modes

- Serial Slow/Fast configuration (up to 33 MHz)

- 5V tolerant I/O pins accept 3.3V signals

- Design support using the Xilinx Alliance<sup>™</sup> and Foundation<sup>™</sup> series

software packages

- Available in CLCC44 and CQFP44 packages

- Compatibility of BQ18V04

- Complete substitute for Xilinx XC18V04 of PC44 package

- Complete substitute for Xilinx XQ18V04 of VQ44 package

- Available for substitution of pin-to-pin, no modification for the whole design including PCB

# 2. Description

BQ18V04 is a PROM product compatible with Xilinx XQ18V04. Initial devices in this 3.3V family are a 4-megabit in-system programmable FLASH-based PROM that provides an repeatedly erased, non-volatile method for storing large FPGA configuration bitstreams in militray equipment on the ground or in space.

When the FPGA is in Master Serial mode, it generates a configuration clock that drives the PROM. A short valid time after  $\overline{CE}$  and  $OE/\overline{Reset}$ , data is available on the PROM DATA (D0) pin that is connected to the FPGA DIN pin. At every rising CCLK, PROM sends 1-bit data in turn. When the FPGA is in Slave Serial mode, the PROM and the FPGA are clocked by an external clock. Parallel configuration mode is similar to serial configuration mode, and Data output terminal is D0-D7.

Multiple devices can be concatenated by using the  $\overline{CEO}$  output to drive the  $\overline{CE}$  input of the following device. The clock inputs and the DATA outputs of all PROMs

in this chain are interconnected. BQ18V04 can be cascaded with Xilinx configuration PROM including XQ18V04 and XQ17V16, etc.

# 3. Structure

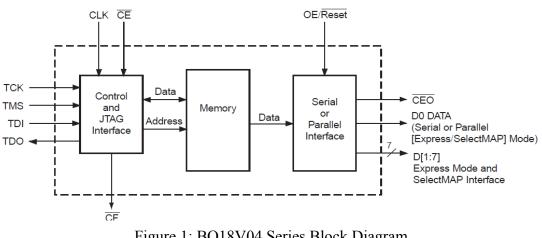

The structure of BQ18V04 includes three main logic block. See Figure 1.

- JTAG interface ∻

- Serial and parallel interface  $\diamond$

- FLASH memory  $\diamond$

## Figure 1: BQ18V04 Series Block Diagram

# 4. Pinout and Pin Description

|          | 1        | able 1. Pin Names and Descriptions                                                                                                                                                                      |

|----------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name | Function | Pin Decription                                                                                                                                                                                          |

| D0~D7    | DATA OUT | D0-D7 are the output pins to provide parallel data for configuring a FPGA. In serial mode, D1-D7 can be not connected and is in a high-impedance state by default.                                      |

| CLK      | DATA IN  | Each rising edge on the CLK input increments the internal address counter if both $\overline{CE}$ is Low and $OE/\overline{Reset}$ is High.                                                             |

|          | DATA IN  | When Low, this input holds the address counter reset and                                                                                                                                                |

| OE/RESET | DATA OUT | the DATA output is in a high-impedance state. This is a                                                                                                                                                 |

| OE/RESET | OUTPUT   | bidirectional open-drain pin that is held Low while the                                                                                                                                                 |

|          | ENABLE   | PROM is reset. Polarity is NOT programmable.                                                                                                                                                            |

| CE       | DATA IN  | When $\overline{CE}$ is High, this pin puts the device into standby mode and resets the address counter. The DATA output pin is in a high-impedance state, and the device is in low power standby mode. |

| CF       | DATA OUT | Allows JTAG CONFIG instruction to initiate FPGA                                                                                                                                                         |

| Table 1: P | Pin Names and | Descriptions |

|------------|---------------|--------------|

|------------|---------------|--------------|

| -      |                     |                                                                                                                                                                                                                                                                      |

|--------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | OUTPUT<br>ENABLE    | configuration without powering down FPGA. This is an open-drain output that is pulsed Low by the JTAG CONFIG command.                                                                                                                                                |

|        | DATA OUT            | Chip Enable Output ( $\overline{CEO}$ ) is connected to the $\overline{CE}$ input of the next PROM in the chain. This output is Low when                                                                                                                             |

| CEO    | OUTPUT<br>ENABLE    | $\overline{CE}$ is Low and OE/RESET input is High, AND the internal address counter has been incremented beyond its Terminal Count (TC) value. When OE/RESET goes Low, $\overline{CEO}$ stays High until the PROM is brought out of reset by bringing OE/RESET High. |

| GND    |                     | Ground connection                                                                                                                                                                                                                                                    |

| TMS    | MODE<br>SELECT      | The state of TMS on the rising edge of TCK determines<br>the state transitions at the Test Access Port (TAP)<br>controller. TMS has an internal 50K ohm resistive pull-up<br>on it to provide a logic "1" to the device if the pin is not<br>driven.                 |

| ТСК    | CLOCK               | This pin is the JTAG test clock. It sequences the TAP controller and all the JTAG test and programming electronics.                                                                                                                                                  |

| TDI    | DATA IN             | This pin is the serial input to all JTAG instruction and data registers. TDI has an internal 50K ohm resistive pull-up on it to provide a logic "1" to the system if the pin is not driven.                                                                          |

| TDO    | DATA OUT            | This pin is the serial output for all JTAG instruction and data registers. TDO has an internal 50K ohm resistive pull-up on it to provide a logic "1" to the system if the pin is not driven.                                                                        |

| Vccint | INTERNAL<br>VOLTAGE | Positive 3.3V supply voltage for internal logic and input buffers.                                                                                                                                                                                                   |

| Vcco   | I/O<br>VOLTAGE      | Positive 3.3V supply voltage connected to the output voltage drivers.                                                                                                                                                                                                |

# 5. Product Description

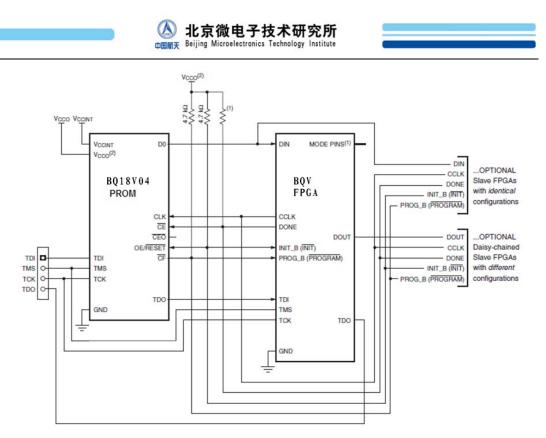

# 5.1 Connecting BQ18V04

The outputs of BQ18V04 drive the inputs of inputs. Connectiong the FPGAdevice and the PROM in master serial mode, see Figure 2. In master serial mode, CCLK drives the CLK of PROM. Other signals are as following.

Figure 2: Master Serial Mode

- The DATA output(s) of the PROM(s) drives the DIN input of the lead FPGA device.

- The Master FPGA CCLK output drives the CLK input(s) of the PROM(s) in Master Serial mode.

- The CEO output of a PROM drives the CE input of the next PROM in a daisy chain.

- The OE/Reset pins of all PROMs are connected to the INIT of all FPGA devices. This connection assures that the PROM address counter is reset before the start of any configuration.

- The BQ18V04 CE input can be driven from the DONE pin. The CE input of the first (or only) PROM can be driven by the DONE output of all target FPGA devices, provided that DONE is not permanently grounded.CE can also be permanently tied Low, but this keeps the DATA output active and causes an unnecessary power.

- In serial mode, the BQ18V04 D1-D7 can keep non-connected and are in a high-impendance state.

- Parallel mode is similar to slave serial mode. The DATA is clocked out of the PROM one byte per CCLK instead of one bit per CCLK cycle.

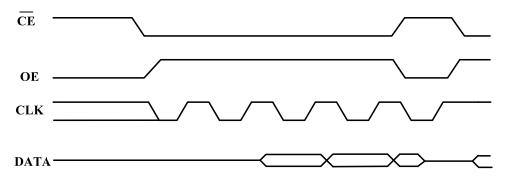

#### **5.2 Operation Timing**

After the BQ18V04  $\overline{CE}$  and OE/Reset are valid for a short time, the data of PROM are transferred to the Din terminal of FPGA through the D0 terminal. Figure 3 shows the operation timing.

Figure 3: PROM operation timing

#### **5.3 Initiating FPGA Configuration**

The BQ18V04 devices incorporate a pin named  $\overline{CF}$  that is controllable through the JTAG CONFIG instruction. Executing the CONFIG instruction through JTAG pulses the  $\overline{CF}$  low, which resets the FPGA and initiates configuration. The  $\overline{CF}$  pin must be connected to the PROGRAM pin on the FPGA(s). The Xilinx iMPACT software can issue the CONFIG command.

#### **5.4 Configuration Modes**

The BQ18V04 accommodates serial and parallel methods of configuration. The configuration modes are selectable through a user control register in the BQ18V04 device. This control register is accessible through JTAG, and is set using the "Parallel mode" setting on the Xilinx iMPACT software. Serial output is the default programming mode.

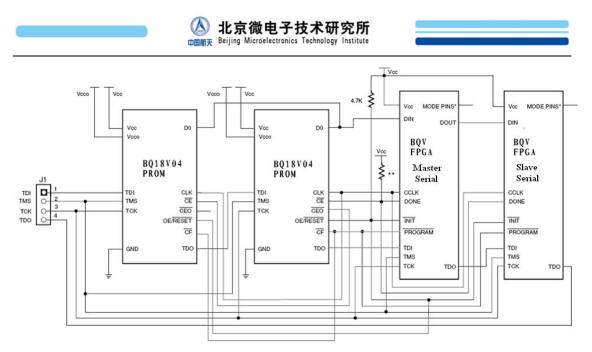

#### **5.5 Cascading Configuration**

For multiple FPGAs configured as a serial daisy-chain, or a single FPGA requiring larger configuration memories in a serial or SelectMAP configuration mode, cascaded PROMs provide additional memory. Figure 4 shows a daisy configuration mode.

Figure 4: a daisy configuration mode

Multiple BQ18V04 devices can be concatenated by using the  $\overline{CEO}$  output to drive the  $\overline{CE}$  input of the downstream device. The clock inputs and the data outputs of all BQ18V04 devices in the chain are interconnected. After the last bit from the first PROM is read, the next clock signal to the PROM asserts its  $\overline{CEO}$  output Low and drives its DATA line to a high-impedance state. The second PROM recognizes the Low level on its  $\overline{CE}$  input and enables its DATA output.

#### **5.6 Reset Activation**

On power up,  $OE/\overline{Reset}$  is held low until the BQ18V04 is active (1.6 ms) and able to supply data after receiving a CCLK pulse from the FPGA.  $OE/\overline{Reset}$  is connected to an external resistor to pull  $OE/\overline{Reset}$  HIGH releasing the FPGA  $\overline{INIT}$  and allowing configuration to begin.  $OE/\overline{Reset}$  is held low until the BQ18V04 voltage reaches the operating voltage range. If the power drops below 2.0V, the PROM will reset.  $OE/\overline{Reset}$  polarity is NOT programmable.

#### Note:

After BQ18V04 power on is compeleted, if OE/Reset is externally pull down, then the OE/Reset low pulse time will not be less than 1.6mS.

#### 5.7 Standby Mode

The PROM enters a low-power standby mode whenever  $\overline{CE}$  is asserted High. The output remains in a high-impedance state regardless of the state of the OE/Reset input. JTAG pins TMS, TDI and TDO can be in a high-impedance state or High. See table 2.

| Control Ir | nputs | s Outputs                                                                        |                  |             |                   |

|------------|-------|----------------------------------------------------------------------------------|------------------|-------------|-------------------|

| OE/RESET   | CE    | Internal Address                                                                 | DATA             | CEO         | I <sub>CC</sub>   |

| High       | Low   | If address $\leq TC^{(1)}$ : increment<br>If address > $TC^{(1)}$ : don't change | Active<br>High-Z | High<br>Low | Active<br>Reduced |

| Low        | Low   | Held reset                                                                       | High-Z           | High        | Active            |

| High       | High  | Held reset                                                                       | High-Z           | High        | Standby           |

| Low        | High  | Held reset                                                                       | High-Z           | High        | Standby           |

#### Table 2: Truth Table for Control inputs and outputs

Notes:

1. TC = Terminal Count = highest address value. TC + 1 = address 0.

#### 5.8 In-System Programming

In-System Programmable PROMs can be programmed individually, or two or more can be daisy-chained together and programmed in-system via the standard 4-pin JTAG protocol. In-system programming can use the following software kits.

1) Xilinx development system (iMPACT software and a download cable)

- 2) A third-party JTAG development system

- 3) A JTAG-compatible board tester

- 4) A simple microprocessor interface that emulates the JTAG instruction sequence

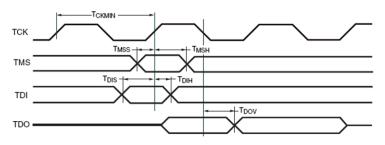

BQ18V04 can be programmed by the Xilinx HW-130, MultiPRO and third-party programmers. The ISP programming algorithm requires issuance of a reset that will cause OE/Reset to go low. Figure 5 shows the BQV18V04 TAP (Test Access Port) timing.

Figure 5: Test Access Port timing

#### 5.9 JTAG Protocol Compatibility

The BQ18V04 family is fully compliant with the IEEE Std. 1149.1 Boundary-Scan, also known as JTAG. A Test Access Port (TAP) and registers are provided to support all required boundary scan instructions, as well as many of the optional instructions specified by IEEE Std. 1149.1. In addition, the JTAG interface is used to implement in-system programming (ISP) to facilitate configuration, erasure, and verification operations on the BQ18V04 device.

The boundary-scan register is a 8-bit register. It supports many instructions, including BYPAS, SAMPLE/PRELOAD, EXTEST, CLAMP, HIGHZ, IDCODE, USERCODE and CONFIG. Table 4 lists the instruction code and function of these

instructions.

| l able 4                     | : Boundary Scan Ins     | tructions                          |

|------------------------------|-------------------------|------------------------------------|

| <b>Boundary-Scan Command</b> | <b>Binary Code(7:0)</b> | Description                        |

| <b>Required Instructions</b> |                         |                                    |

| BYPASS                       | 11111111                | Enables BYPASS                     |

| SAMPLE/PRELOAD               | 00000001                | Enables boundary-scan              |

|                              |                         | SAMPLE/PRELOAD                     |

|                              |                         | operation                          |

| EXTEST                       | 00000000                | Enables boundary-scan              |

|                              |                         | EXTEST operation                   |

| <b>Optional Instructions</b> |                         |                                    |

| CLAMP                        | 11111010                | Enables boundary-scan              |

|                              |                         | CLAMP operation                    |

| HIGHZ                        | 11111100                | All outputs in                     |

|                              |                         | high-impedance state               |

|                              |                         | simultaneously                     |

| IDCODE                       | 11111110                | Enables shifting out               |

|                              |                         | 32-bit IDCODE                      |

| USERCODE                     | 11111101                | Enables shifting out               |

|                              |                         | 32-bit USERCODE                    |

| BQ18V04 Specific Instructi   | ons                     |                                    |

| CONFIG                       | 11101110                | Initiates FPGA configuration       |

|                              |                         | by pulsing $\overline{CF}$ pin low |

| The IDCODE of PO18V          | 0.4  is  05026002 b     | The USEPCODE register              |

The IDCODE of BQ18V04 is 05026093h. The USERCODE register is user-programmable, which shows the programmed content of the device. If the device is blank or was not loaded during programming, the USERCODE register will contain FFFFFFFh.

# 6. Electrical Parameters

| Parameter                       | Symbol          | Conditions (Unless special conditions, $3.0V \le Vccint \le 3.6V$ ,         | Limit |     | Luita |

|---------------------------------|-----------------|-----------------------------------------------------------------------------|-------|-----|-------|

| Parameter                       | Symbol          | 3.0V $\leq$ Vcco $\leq$ 3.6V,<br>-55°C $\leq$ T <sub>A</sub> $\leq$ 125°C ) | Min   | Max | Units |

| High-level<br>output<br>voltage | V <sub>OH</sub> | $I_{OH}$ =-4mA, $V_{CCINT}$ =3.0V, $V_{CCO}$ =3.0V                          | 2.4   |     | V     |

| Low-level<br>output<br>voltage  | V <sub>OL</sub> | $I_{OL}=4mA$ , $V_{CCINT}=3.0V$ , $V_{CCO}=3.0V$                            |       | 0.4 | V     |

| T / 1 · 1          |                              |                                                           |      |     |        |

|--------------------|------------------------------|-----------------------------------------------------------|------|-----|--------|

| Input high         |                              |                                                           |      |     |        |

| voltage<br>leakage | I <sub>IH</sub>              | $V_{CCINT}=3.6V$ , $V_{CCO}=3.6$ , $V_{IN}=3.6V$          | —    | 10  | μΑ     |

| current            |                              |                                                           |      |     |        |

| Input low          |                              |                                                           |      |     |        |

| voltage            |                              |                                                           |      |     |        |

| leakage            | $ \mathbf{I}_{\mathrm{IL}} $ | $V_{CCINT}=3.6V$ , $V_{CCO}=3.6$ , $V_{IN}=0V$            | —    | 10  | μA     |

| current            |                              |                                                           |      |     |        |

| JTAG input         |                              |                                                           |      |     |        |

| pins leakage       | IIL <sub>JTAG</sub>          | $V_{CCINT}=3.6V, V_{CCO}=3.6V, V_{IN}=3.6V$               | -100 |     | μA     |

| current            | 1110                         |                                                           |      |     | •      |

| Output             |                              |                                                           |      |     |        |

| High-Z             | т                            | V = 2 G V = 2 G V = 2 G V                                 | 10   | 10  |        |

| leakage            | I <sub>OZH</sub>             | $V_{CCINT}=3.6V, V_{CCO}=3.6V, V_{IN}=3.6V$               | -10  | 10  | μA     |

| current            |                              |                                                           |      |     |        |

| High-level         | V                            | V = -2.2 V = V = -2.2 V                                   | 2.0  |     | V      |

| input voltage      | V <sub>IH</sub>              | $V_{\text{CCINT}}=3.3V$ , $V_{\text{CCO}}=3.3V$           | 2.0  |     | v      |

| Low-level          | $V_{IL}$                     | $V_{CCINT}=3.3V, V_{CCO}=3.3V$                            |      | 0.8 | V      |

| input voltage      | • IL                         | · CCINI 5.5 •, • CCO 5.5 •                                |      | 0.0 | •      |

| Supply             |                              |                                                           |      |     |        |

| current,           | I <sub>CCSTA</sub>           | $V_{CCINT}=3.6V, V_{CCO}=3.6V$                            |      | 20  | mA     |

| standby            | ICCSIA                       |                                                           |      | 20  | IIII I |

| mode               |                              |                                                           |      |     |        |

| Supply             | -                            |                                                           |      | -   |        |

| current,           | I <sub>CCDYN</sub>           | $V_{CCINT}=3.6V$ , $V_{CCO}=3.6V$ , f=25MHz               | —    | 50  | mA     |

| active mode        |                              |                                                           |      |     |        |

| Input and          |                              |                                                           |      | 1.5 | Б      |

| output             | $C_{in}$ / out               | f=1.0MHz, $T_A=25$ °C                                     |      | 15  | pF     |

| capacitance        |                              |                                                           |      |     |        |

| Function test      |                              | V <sub>CCINT</sub> =3.3V, V <sub>CCO</sub> =3.3V, f=40MHz |      | —   | —      |

| TDO valid          | т                            |                                                           |      | 25  |        |

| delay              | $T_{\text{DOV}}$             | $V_{CCINT}$ =3.0V, $V_{CCO}$ =3.0V (See Figure            | _    | 25  | ns     |

| CLK to data        | Tara                         | 1A, 1B)                                                   |      | 25  | ng     |

| D0-D7 delay        | T <sub>CAC</sub>             |                                                           |      | 23  | ns     |

# **6.1 Operating Conditions**

| Absolute Maximum Ratings:                     |                       |

|-----------------------------------------------|-----------------------|

| Internal supply voltage( $V_{\text{CCINT}}$ ) | -0.5V~+4.0V           |

| IO supply voltage( $V_{\rm CCO}$ )            | -0.5V~+4.0V           |

| DC input voltage( $V_{IN}$ ) internal thresh  | nold0.5V~+5.5V        |

| Voltage applied to High-Z output( $V_{\rm T}$ | s) $-0.5V \sim +5.5V$ |

| Lead soldering temperature of CLCC44 ( $T_h$ ) 10s         |  |          | )°C |

|------------------------------------------------------------|--|----------|-----|

| Lead soldering temperature of CQFP44 ( $T_h$ ) 10s         |  |          | )°C |

| Thermal resistance, junction to case ( $\theta_{\rm JC}$ ) |  | 1°C      | /W  |

| Junction temperature $(T_J)$                               |  |          | )°C |

| Storage temperature(T <sub>STG</sub> )                     |  | 65℃~+150 | )°C |

| Data retention time $(T_{DR})$                             |  | 20 ye    | ars |

| Max erase/program cycles $(T_{PE})$                        |  |          | 0   |

## **6.2 Recommended Operating Conditions**

| Recommended operating conditions:            |                          |

|----------------------------------------------|--------------------------|

| Internal voltage supply $(V_{\text{CCINT}})$ |                          |

| Supply voltage for I/O for 3.3V open         | ration ( $V_{\rm CCO}$ ) |

| High-level input voltage $(V_{\rm IH})$      |                          |

| Low-level input voltage $(V_{\rm IL})$       | 0V~0.8V                  |

| Operating temperature (TC)                   | 55°C∼+125°C              |

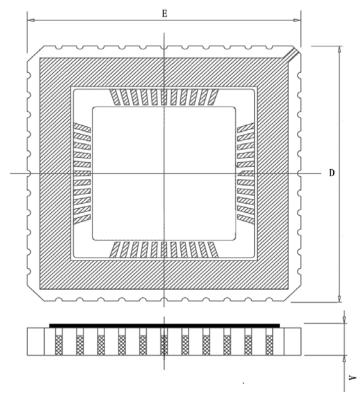

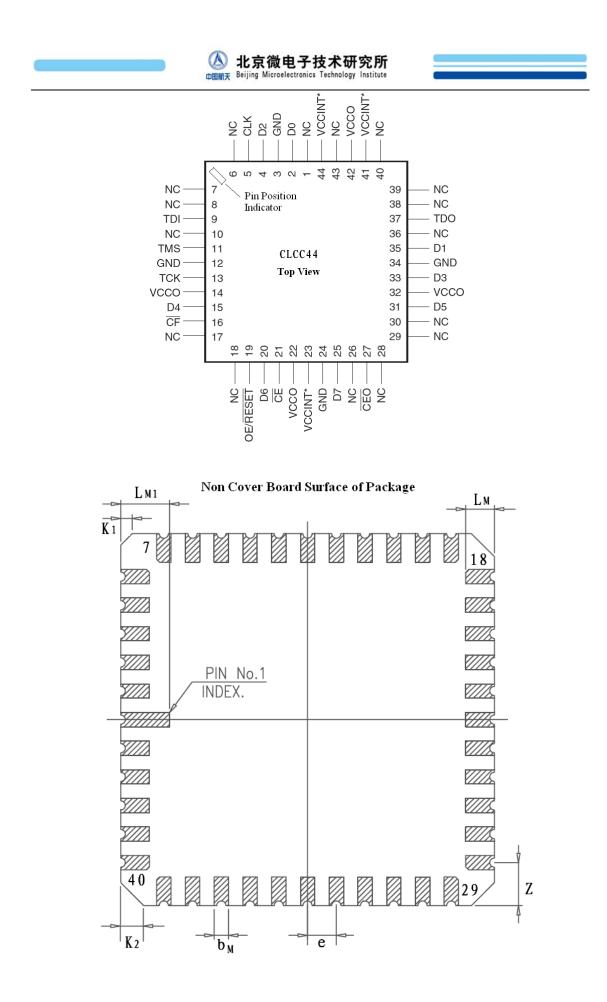

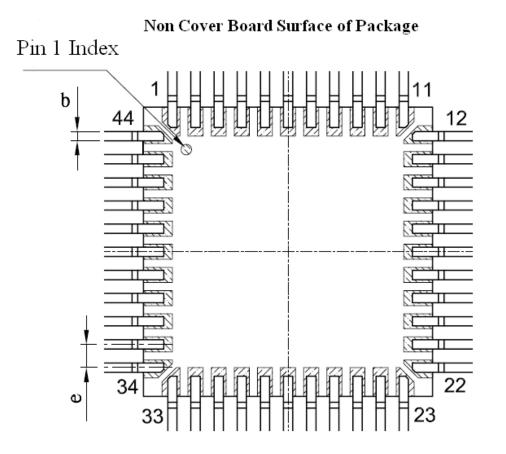

# 7. Package Description

BQ18V04 packaged with CCLC44 is named BQ18V04CL. BQ18V04 packaged with CQFP44 is named BQ18V04CQ. The dimension and pin arrangement of BQ18V04 CCLC44 package:

|                 |        |      | emits: min |

|-----------------|--------|------|------------|

| SYMBOL          | INCHES |      |            |

|                 | MIN    | NOM  | MAX        |

| А               | 1.63   |      | 3.05       |

| b <sub>M</sub>  | 0.56   |      | 0.71       |

| e               |        | 1.27 |            |

| $\mathbf{K}_1$  |        |      | 0.63       |

| K <sub>2</sub>  | 0.77   |      |            |

| L <sub>M</sub>  | 1.14   |      | 1.40       |

| L <sub>M1</sub> | 1.95   |      | 2.36       |

| D               | 16.25  |      | 16.76      |

| Е               | 16.25  |      | 16.76      |

| Z               |        | 1.91 |            |

Units: mm

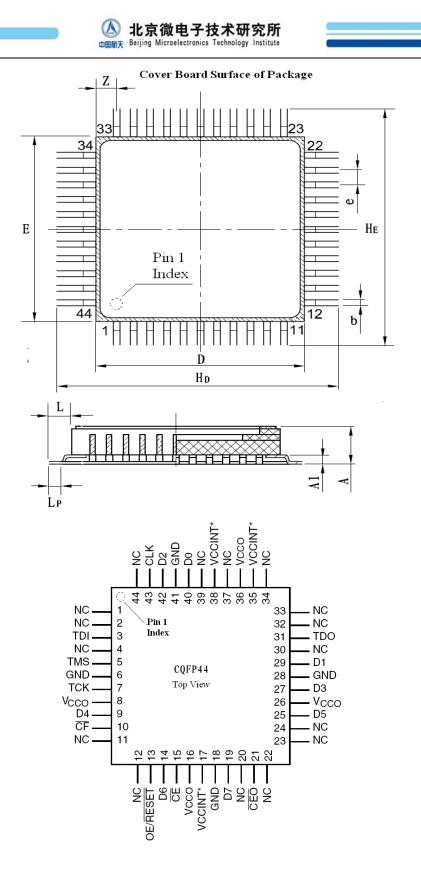

The dimension and pin arrangement of BQ18V04 CQFP44 package:

Units: mm

| SYMBOL | MIN   | NOM  | MAX   |

|--------|-------|------|-------|

| А      | 1.90  | _    | 2.90  |

| A1     | 0.35  | —    | _     |

| b      |       | 0.32 | _     |

| с      | 0.11  |      | 0.2   |

| e      |       | 0.80 |       |

| D/E    | 9.70  |      | 10.30 |

| HD/HE  | 12.00 |      | 13.50 |

| L      | 1.30  | _    | 1.80  |

| Lp     | 0.80  |      | 1.20  |

| Z      |       |      | 1.27  |

#### Service and Support:

Address: No.2 Siyingmen N. Road. Donggaodi. Fengtai District.Beijing.China.

Department: Department of international cooperation

telephone: 010-67968115-7178

Fax: 010-68757706

Zip code: 100076