# **Gas Gauge IC for High Discharge Rates**

#### **Features**

- ➤ Conservative and repeatable measurement of available charge in rechargeable batteries

- ➤ Designed for portable equipment such as power tools with high discharge rates

- ➤ Designed for battery pack integration

- 120µA typical standby current (self-discharge estimation mode)

- Small size enables implementations in as little as ½ square inch of PCB

- Direct drive of LEDs for capacity display

- ➤ Self-discharge compensation using internal temperature sensor

- Simple single-wire serial communications port for subassembly testing

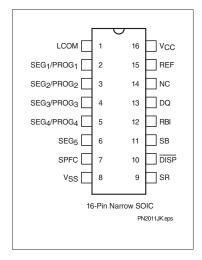

- ➤ 16-pin narrow SOIC

#### **General Description**

The bq2011K Gas Gauge IC is intended for battery-pack installation to maintain an accurate record of a battery's available charge. The IC monitors a voltage drop across a sense resistor connected in series between the negative battery terminal and ground to determine charge and discharge activity of the battery. The bq2011K is designed for systems such as power tools with very high discharge rates.

Battery self-discharge is estimated based on an internal timer and temperature sensor. Compensations for battery temperature and rate of charge or discharge are applied to the charge, discharge, and selfdischarge calculations to provide available charge information across a wide range of operating conditions. Initial battery capacity is set using the PROG<sub>1-4</sub> and SPFC pins. Actual battery capacity is automatically "learned" in the course of a discharge cycle from full to empty and may be displayed depending on the display mode.

Nominal available charge may be directly indicated using a five-segment LED display. These segments are used to graphically indicate nominal available charge.

The bq2011K supports a simple single-line bidirectional serial link to an external processor (common ground). The bq2011K outputs battery information in response to external commands over the serial link. To support subassembly testing, the outputs may also be controlled by command. The external processor may also overwrite some of the bq2011K gas gauge data registers.

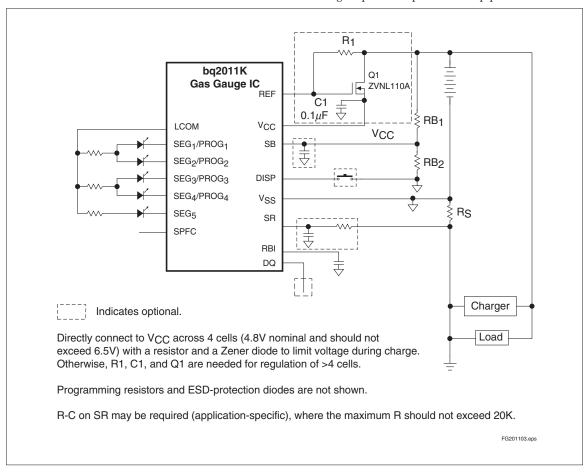

The bq2011K may operate directly from four cells. With the REF output and an external transistor, a simple, inexpensive regulator can be built to provide  $V_{\rm CC}$  from a greater number of cells.

Internal registers include available charge, temperature, capacity, battery ID, and battery status.

### **Pin Connections**

#### **Pin Names**

| LCOM                   | LED common output                     | REF                        | Voltage reference output           |

|------------------------|---------------------------------------|----------------------------|------------------------------------|

| SEG <sub>1</sub> /PROG | LED segment 1/ Program 1 input        | NC                         | No connect                         |

| SEG <sub>2</sub> /PROG | 2 LED segment 2 / Program 2 input     | DQ                         | Serial communications input/output |

| SEC /DDOC              | 1                                     | RBI                        | Register backup input              |

| SEG3/FROG              | 3 LED segment 3/ Program<br>3 input   | SB                         | Battery sense input                |

| SEG <sub>4</sub> /PROG | 4 LED segment 4/ Program<br>4 input   | $\overline{\mathrm{DISP}}$ | Display control input              |

| SEG <sub>5</sub>       | 1                                     | SR                         | Sense resistor input               |

| 5                      | LED segment 5                         | $V_{CC}$                   | 3.0-6.5V                           |

| SPFC                   | Programmed full count selection input | $V_{SS}$                   | Negative battery terminal          |

10/97 B

#### **Pin Descriptions**

#### LCOM LED common

Open-drain output switches  $V_{\rm CC}$  to source current for the LEDs. The switch is off during initialization to allow reading of PROG<sub>1-4</sub> pull-up or pull-down program resistors. LCOM is high impedance when the display is off.

# $\begin{array}{ll} SEG_1- & LED \ display \ segment \ outputs \\ SEG_5 & \end{array}$

Each output may activate an LED to sink the current sourced from LCOM, the battery, or  $V_{\rm CC}.\ \,$

# $PROG_1$ - Programmed full count selection inputs $PROG_4$ (dual function with $SEG_1 \cdot SEG_4$ )

These three-level input pins define the programmed full count (PFC) in conjunction with SPFC pin, define the display mode and enable or disable self-discharge.

#### SPFC Programmed full count selection input

This three-level input pin along with  $PROG_{1-3}$  define the programmed full count (PFC) thresholds described in Table 1. The state of the SPFC pin is only read immediately after a reset condition.

#### SR Sense resistor input

The voltage drop  $(V_{SR})$  across the sense resistor  $R_{\rm S}$  is monitored and integrated over time to interpret charge and discharge activity. The SR input is tied to the low side of the sense resistor and battery pack ground (see Figure 1).  $V_{SR} > V_{SS}$  indicates discharge, and  $V_{SR} < V_{SS}$  indicates charge. The effective voltage drop,  $V_{SRO}$ , as seen by the bq2011K is  $V_{SR} + V_{OS}$  (see Table 4).

#### NC No connect

#### DISP Display control input

$\overline{DISP}$  floating allows the LED display to be active during certain charge and discharge conditions. Transitioning  $\overline{DISP}$  low activates the display for  $4\pm0.5$  seconds.

#### SB Secondary battery input

This input monitors the single-cell voltage potential through a high-impedance resistive divider network for the end-of-discharge voltage (EDV) threshold and maximum cell voltage (MCV).

#### RBI Register backup input

This input is used to provide backup potential to the bq2011K registers during periods when  $V_{\rm CC} < 3V_{\rm \cdot}$  A storage capacitor should be connected to RBI.

#### DQ Serial I/O pin

This is an open-drain bidirectional pin.

#### REF Voltage reference output for regulator

REF provides a voltage reference output for an optional micro-regulator.

#### V<sub>CC</sub> Supply voltage input

#### V<sub>SS</sub> Ground

### **Functional Description**

#### **General Operation**

The bq2011K determines battery capacity by monitoring the amount of charge input to or removed from a rechargeable battery. The bq2011K measures discharge and charge currents, estimates self-discharge, monitors the battery for low-battery voltage thresholds, and compensates for temperature and charge/discharge rates. The charge measurement is made by monitoring the voltage across a small-value series sense resistor between the battery's negative terminal and ground. The available battery charge is determined by monitoring this voltage over time and correcting the measurement for the environmental and operating conditions.

Figure 1 shows a typical battery pack application of the bq2011K using the LED display with absolute mode as a charge-state indicator. The absolute display mode uses the programmed full count (PFC) as the full reference, forcing each segment of the display to represent a fixed amount of charge. A push-button display feature is available for momentarily enabling the LED display.

The bq2011K monitors the charge and discharge currents as a voltage across a sense resistor (see Rs in Figure 1). A filter between the negative battery terminal and the SR pin may be required if the rate of change of the battery current is too great.

#### **Register Backup**

The bq2011K RBI input pin is intended to be used with a storage capacitor to provide backup potential to the in-

Figure 1. Application Diagram: LED Display, Absolute Mode

ternal bq2011K registers when  $V_{\rm CC}$  momentarily drops below 3.0V.  $V_{\rm CC}$  is output on RBI when  $V_{\rm CC}$  is above 3.0V.

After  $V_{\rm CC}$  rises above 3.0V, the bq2011K checks the internal registers for data loss or corruption. If data has changed, then the NAC register is cleared, and the LMD register is loaded with the initial PFC.

#### **Voltage Thresholds**

In conjunction with monitoring  $V_{SR}$  for charge/discharge currents, the bq2011K monitors the single-cell battery potential through the SB pin. The single-cell voltage potential is determined through a resistor-divider network per the following equation:

$$\frac{RB_1}{RB_2} \ = \ N-1$$

where N is the number of cells,  $RB_1$  is connected to the positive battery terminal, and  $RB_2$  is connected to the negative battery terminal. The single-cell battery voltage is monitored for the end-of-discharge voltage (EDV) and for maximum cell voltage (MCV). The EDV threshold level is used to determine when the battery has reached an "empty" state, and the MCV threshold is used for fault detection during charging. The MCV threshold for the bq2011K is fixed at:

$$V_{\rm MCV} = 2.00 V$$

The EDV threshold varies as a function of discharge current as follows:

| V <sub>SRO</sub> (mV) | V <sub>EDV</sub> (V) |

|-----------------------|----------------------|

| $0 < V_{SRO} \le 10$  | 1.160                |

| $10 < V_{SRO} \le 20$ | 1.124                |

| $20 < V_{SRO} \le 40$ | 1.060                |

| $40 < V_{SRO} \le 60$ | 0.960                |

| $V_{\rm spo} > 60$    | 0 (OVLD)             |

#### Reset

Reset can be accomplished with a command over the serial port as described on page 13.

#### **Temperature**

The bq2011K internally determines the temperature in  $10^{\circ}\text{C}$  steps centered from -35°C to +85°C. The temperature steps are used to adapt charge and discharge rate compensations, self-discharge counting, and available charge display translation. The temperature range is available over the serial port in  $10^{\circ}\text{C}$  increments as shown below:

| TMPGG (hex) | Temperature Range                                |

|-------------|--------------------------------------------------|

| 0x          | < -30°C                                          |

| 1x          | -30°C to -20°C                                   |

| 2x          | -20°C to -10°C                                   |

| 3x          | -10°C to 0°C                                     |

| 4x          | 0°C to 10°C                                      |

| 5x          | $10^{\circ}\mathrm{C}$ to $20^{\circ}\mathrm{C}$ |

| 6x          | 20°C to 30°C                                     |

| 7x          | $30^{\circ}\mathrm{C}$ to $40^{\circ}\mathrm{C}$ |

| 8x          | 40°C to 50°C                                     |

| 9x          | 50°C to 60°C                                     |

| Ax          | 60°C to 70°C                                     |

| Bx          | 70°C to 80°C                                     |

| Cx          | > 80°C                                           |

#### **Layout Considerations**

The bq2011K measures the voltage differential between the SR and  $V_{\rm SS}$  pins.  $V_{\rm OS}$  (the offset voltage at the SR pin) is greatly affected by PC board layout. For optimal results, the PC board layout should follow the strict rule of a single-point ground return. Sharing high-current ground with small signal ground causes undesirable noise on the small signal nodes. Additionally:

- The capacitors (SB and  $V_{\rm CC}$ ) should be placed as close as possible to the SB and  $V_{\rm CC}$  pins, respectively, and their paths to  $V_{\rm SS}$  should be as short as possible. A high-quality ceramic capacitor of 0.1 $\mu$ f is recommended for  $V_{\rm CC}$ .

- $\blacksquare$  The sense resistor  $(R_S)$  should be as close as possible to the bq2011K.

- The R-C on the SR pin should be located as close as possible to the SR pin. The maximum R should not exceed 20K.

#### **Gas Gauge Operation**

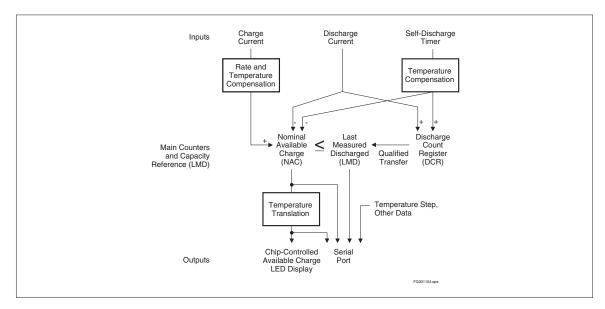

The operational overview diagram in Figure 2 illustrates the operation of the bq2011K. The bq2011K accumulates a measure of charge and discharge currents, as well as an estimation of self-discharge. Charge currents are temperature and rate compensated, whereas self-discharge is only temperature compensated.

The main counter, Nominal Available Charge (NAC), represents the available battery capacity at any given time. Battery charging increments the NAC register, while battery discharging and self-discharge decrement

the NAC register and increment the DCR (Discharge Count Register).

The Discharge Count Register (DCR) is used to update the Last Measured Discharge (LMD) register only if a complete battery discharge from full to empty occurs without any partial battery charges. Therefore, the bq2011K adapts its capacity determination based on the actual conditions of discharge.

The battery's initial capacity is equal to the Programmed Full Count (PFC) shown in Table 1. Until LMD is updated, NAC counts up to but not beyond this threshold during subsequent charges. This approach allows the gas gauge to be charger-independent and compatible with any type of charge regime.

#### Last Measured Discharge (LMD) or learned battery capacity:

LMD is the last measured discharge capacity of the battery. On initialization (application of  $V_{\rm CC}$  or battery replacement), LMD = PFC. During subsequent discharges, the LMD is updated with the latest measured capacity in the Discharge Count Register (DCR) representing a discharge from full to below EDV. A qualified discharge is necessary for a capacity transfer from the DCR to the LMD register. The LMD also serves as the 100% reference threshold used by the relative display mode.

#### 2. Programmed Full Count (PFC) or initial battery capacity:

The initial LMD and gas gauge rate values are programmed by using PFC. The PFC also provides the 100% reference for the absolute display mode. The bq2011K is configured for a given application by selecting a PFC value from Table 1. The correct PFC may be determined by multiplying the rated battery capacity in mAh by the sense resistor value:

Battery capacity (mAh) \* sense resistor ( $\Omega$ ) =

Selecting a PFC slightly less than the rated capacity for absolute mode provides capacity above the full reference for much of the battery's life.

#### Example: Selecting a PFC Value

Given:

Sense resistor =  $0.002\Omega$ Number of cells = 6Capacity = 1800mAh, NiCd cells Current range = 1A to 80A Absolute display mode Self-discharge =  $\%_0$ Voltage drop across sense resistor = 2mV to 160mV

Figure 2. Operational Overview

Therefore:

$1800\text{mAh}*0.002\Omega=3.6\text{mVh}$

Select:

$PFC = 35840 \ counts \ or \ 3.39mVh$   $SPFC = Z \ (float)$   $PROG1, PROG2 = H \ or \ Z$  PROG3 = L  $PROG4 = H \ or \ Z$

The initial full battery capacity is 3.39mVh (1695mAh) until the bq2011K "learns" a new capacity with a qualified discharge from full to EDV.

#### 3. Nominal Available Charge (NAC):

NAC counts up during charge to a maximum value of LMD and down during discharge and self discharge to 0. NAC is reset to 0 on initialization and on the first valid charge following discharge to EDV. To prevent overstatement of charge during periods of overcharge, NAC stops incrementing when NAC = LMD.

Note: NAC is set to the value in LMD when  $PROG_4$  is pulled low during a reset.

Table 1. bq2011K Programmed Full Count mVh Selections

| Programmed Full Count (PFC) | mVh  | Scale       | Display<br>Mode | SPFC | PROG₁  | PROG <sub>2</sub> | PROG₃  |

|-----------------------------|------|-------------|-----------------|------|--------|-------------------|--------|

| 40192                       | 3.81 | 1/10560     |                 | Н    | H or Z | H or Z            | H or Z |

| 32256                       | 3.05 | 1/<br>10560 |                 | Z    | H or Z | H or Z            | H or Z |

| 28928                       | 2.74 | 1/<br>10560 |                 | L    | H or Z | H or Z            | H or Z |

| 25856                       | 2.45 | 1/10560     | Absolute        | Н    | L      | H or Z            | H or Z |

| 35840                       | 3.39 | 1/10560     |                 | Z    | L      | H or Z            | H or Z |

| 23296                       | 2.21 | 1/10560     |                 | L    | L      | H or Z            | H or Z |

**Table 2. Programmed Self-Discharge**

| PROG <sub>4</sub> | NAC Reset Value | Self-Discharge |  |  |

|-------------------|-----------------|----------------|--|--|

| H or Z            | NAC = 0         | Enabled        |  |  |

| L                 | NAC = PFC       | Disabled       |  |  |

#### 4. Discharge Count Register (DCR):

The DCR counts up during discharge independent of NAC and could continue increasing after NAC has decremented to 0. Prior to NAC = 0 (empty battery), both discharge and self-discharge increment the DCR. After NAC = 0, only discharge increments the DCR. The DCR resets to 0 when NAC = LMD. The DCR does not roll over but stops counting when it reaches FFFFh.

The DCR value becomes the new LMD value on the first charge after a valid discharge to  $V_{\rm EDV}$  if:

No valid charge initiations (charges greater than 256 NAC counts; or 0.006-0.01C) occurred during the period between NAC = LMD and EDV detected.

The self-discharge count is not more than 4096 counts (8% to 18% of PFC, specific percentage threshold determined by PFC).

The temperature is  $\geq 0^{\circ}$ C when the EDV level is reached during discharge.

The valid discharge flag (VDQ) indicates whether the present discharge is valid for LMD update.

#### **Charge Counting**

Charge activity is detected based on a negative voltage on the  $V_{SR}$  input. If charge activity is detected, the bq2011K increments NAC at a rate proportional to  $V_{SRO} \, (V_{SR} \, + \, V_{OS})$  and, if enabled, activates an LED display if  $V_{SRO} < \text{-}2\text{mV}$ . Charge actions increment the NAC after compensation for charge rate and temperature.

The bq2011K determines a valid charge activity sustained at a continuous rate equivalent to  $V_{SRO}<$  -400 $\mu V.$  A valid charge equates to a sustained charge activity greater than 256 NAC counts. Once a valid charge is detected, charge counting continues until  $V_{SRO}$  rises above -400 $\mu V.$

#### **Discharge Counting**

All discharge counts where  $V_{SRO} > 500 \mu V$  cause the NAC register to decrement and the DCR to increment. Exceeding the fast discharge threshold (FDQ) if the rate is equivalent to  $V_{SRO} > 2mV$  activates the display, if enabled. The display remains active for 10 seconds after  $V_{SRO}$  falls below 2mV.

#### **Self-Discharge Estimation**

The bq2011K continuously decrements NAC and increments DCR for self-discharge based on time and temperature. The self-discharge count rate is programmed to be a nominal  $y_{80}$  \* NAC rate per day or disabled per Table 2. This is the rate for a battery temperature between 20–30°C. The NAC register cannot not be decremented below 0.

#### **Count Compensations**

The bq2011K determines fast charge when the NAC updates at a rate of ≥2 counts/sec. Charge activity is compensated for temperature and rate before updating the NAC and/or DCR. Self-discharge estimation is compensated for temperature before updating the NAC or DCR.

#### **Charge Compensation**

Two charge efficiency factors are used for trickle charge and fast charge. Fast charge is defined as a rate of charge resulting in  $\geq 2$  NAC counts/sec ( $\geq 0.15C$  to 0.32C depending on PFC selections; see Table 1). The compensation defaults to the fast charge factor until the actual charge rate is determined.

Temperature adapts the charge rate compensation factors over three ranges between nominal, warm, and hot temperatures. The compensation factors are shown below.

| Charge<br>Temperature | Trickle Charge<br>Compensation | Fast Charge<br>Compensation |  |  |

|-----------------------|--------------------------------|-----------------------------|--|--|

| <30°C                 | 0.80                           | 0.95                        |  |  |

| 30-50°C               | 0.75                           | 0.90                        |  |  |

| > 50°C                | 0.70                           | 0.85                        |  |  |

#### **Discharge Compensation**

Corrections for the rate of discharge are made by adjusting EDV thresholds. The compensation factor used during discharge is set to 1.00 for all rates and temperatures. The recoverable charge at colder temperatures is adjusted for display purposes only. See page 13.

#### **Self-Discharge Compensation**

The self-discharge compensation is programmed for a nominal rate of  $\frac{1}{2}$ <sub>0</sub> \* NAC per day or disabled. This is the rate for a battery within the 20–30°C temperature range (TMPGG = 6x). This rate varies across 8 ranges from <10°C to >70°C, doubling with each higher temperature step (10°C). See Table 3.

**Table 3. Self-Discharge Compensation**

| Temperature<br>Range | Self-Discharge Compensation<br>Typical Rate/Day |

|----------------------|-------------------------------------------------|

| < 10°C               | $^{\mathrm{NAC}}\!\!/_{320}$                    |

| 10–20°C              | $^{ m NAC}\!\!/_{ m 160}$                       |

| 20–30°C              | $NAC_{80}$                                      |

| 30–40°C              | $NAC_{40}$                                      |

| 40–50°C              | $^{ m NAC}\!\!/_{ m 20}$                        |

| 50–60°C              | NAC/10                                          |

| 60–70°C              | $_{ m NAC}_{ m 5}$                              |

| > 70°C               | NAC/2.5                                         |

#### **Error Summary**

The LMD is susceptible to error on initialization or if no updates occur. On initialization, the LMD value includes the error between the programmed full capacity and the actual capacity. This error is present until a valid discharge occurs and LMD is updated (see the DCR description in the "Layout Considerations" section). The other cause of LMD error is battery wear-out. As the battery ages, the measured capacity must be adjusted to account for changes in actual battery capacity.

#### **Current-Sensing Error**

Table 4 illustrates the current-sensing error as a function of  $V_{SR}$ . A digital filter eliminates charge and discharge counts to the NAC register when  $V_{SRO}$  ( $V_{SR}$  +  $V_{OS}$ ) is between -400 $\mu$ V and 500 $\mu$ V.

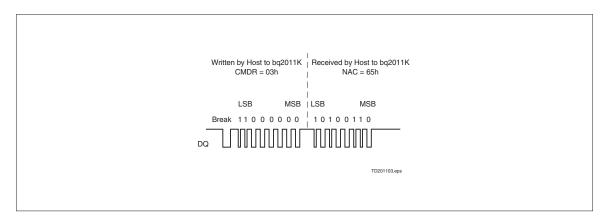

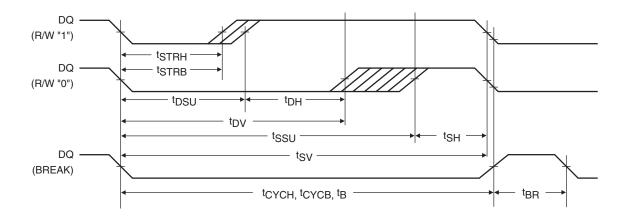

#### Communicating With the bq2011K

The bq2011K includes a simple single-pin (DQ plus return) serial data interface. A host processor uses the interface to access various bq2011K registers. Battery characteristics may be easily monitored by adding a single contact to the battery pack. The open-drain DQ pin on the bq2011K should be pulled up by the host system, or may be left floating if the serial interface is not used.

The interface uses a command-based protocol, where the host processor sends a command byte to the bq2011K. The command directs the bq2011K to either store the next eight bits of data received to a register specified by the command byte or output the eight bits of data specified by the command byte.

The communication protocol is asynchronous return-toone. Command and data bytes consist of a stream of eight bits that have a maximum transmission rate of 333 bits/sec. The least-significant bit of a command or data byte is transmitted first. The protocol is simple enough that it can be implemented by most host processors using either polled or interrupt processing. Data input from the bq2011K may be sampled using the pulse-width capture timers available on some microcontrollers.

Communication is normally initiated by the host processor sending a BREAK command to the bq2011K. A BREAK is detected when the DQ pin is driven to a logic-low state for a time,  $t_B$  or greater. The DQ pin should then be returned to its normal ready-high logic state for a time,  $t_{BR}$ . The bq2011K is now ready to receive a command from the host processor.

The return-to-one data bit frame consists of three distinct sections. The first section is used to start the transmission by either the host or the bq2011K taking the DQ pin to a

Table 4. bq2011K Current-Sensing Errors

| Symbol | Parameter                              | Typical | Maximum | Units | Notes                                                                     |

|--------|----------------------------------------|---------|---------|-------|---------------------------------------------------------------------------|

| INL    | Integrated non-linearity error         | ± 2     | ± 4     | %     | Add 0.1% per °C above or below 25°C and 1% per volt above or below 4.25V. |

| INR    | Integrated non-<br>repeatability error | ± 1     | ± 2     | %     | Measurement repeatability given similar operating conditions.             |

logic-low state for a period,  $t_{\rm STRH,B}$ . The next section is the actual data transmission, where the data should be valid by a period,  $t_{\rm DSU}$ , after the negative edge used to start communication. The data should be held for a period,  $t_{\rm DV}$ , to allow the host or bq2011K to sample the data bit.

The final section is used to stop the transmission by returning the DQ pin to a logic-high state by at least a period, tssu, after the negative edge used to start communication. The final logic-high state should be held until a period, tsv, to allow time to ensure that the bit transmission was stopped properly. The timings for data and break communication are given in the serial communication timing specification and illustration sections.

Communication with the bq2011K is always performed with the least-significant bit being transmitted first. Figure 3 shows an example of a communication sequence to read the bq2011K NAC register.

#### bq2011K Registers

The bq2011K command and status registers are listed in Table 5 and described below.

#### **Command Register (CMDR)**

The write-only CMDR register is accessed when eight valid command bits have been received by the bq2011K. The CMDR register contains two fields:

- W/R bit

- Command address

The  $W/\overline{R}$  bit of the command register is used to select whether the received command is for a read or a write function.

The W/R values are:

|     | CMDR Bits |   |   |   |   |   |   |  |  |  |

|-----|-----------|---|---|---|---|---|---|--|--|--|

| 7   | 6         | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

| W/R | -         | - | - | - | - | - | - |  |  |  |

Where  $W/\overline{R}$  is:

- 0 The bq2011K outputs the requested register contents specified by the address portion of CMDR.

- 1 The following eight bits should be written to the register specified by the address portion of CMDR.

The lower seven-bit field of CMDR contains the address portion of the register to be accessed. Attempts to write to invalid addresses are ignored.

| CMDR Bits |     |     |     |     |     |     |              |  |  |  |

|-----------|-----|-----|-----|-----|-----|-----|--------------|--|--|--|

| 7         | 6   | 5   | 4   | 3   | 2   | 1   | 0            |  |  |  |

| -         | AD6 | AD5 | AD4 | AD3 | AD2 | AD1 | AD0<br>(LSB) |  |  |  |

#### **Primary Status Flags Register (FLGS1)**

The read-only FLGS1 register (address=01h) contains the primary bq2011K flags.

Figure 3. Typical Communication With the bq2011K

Table 5. bq2011K Command and Status Registers

|        | Dowleton                                             | Las           | Read/ |        |        |        | Contro | l Field |        |        |        |

|--------|------------------------------------------------------|---------------|-------|--------|--------|--------|--------|---------|--------|--------|--------|

| Symbol | Register<br>Name                                     | Loc.<br>(hex) | Write | 7(MSB) | 6      | 5      | 4      | 3       | 2      | 1      | 0(LSB) |

| CMDR   | Command<br>register                                  | 00h           | Write | W/R    | AD6    | AD5    | AD4    | AD3     | AD2    | AD1    | AD0    |

| FLGS1  | Primary<br>status flags<br>register                  | 01h           | Read  | CHGS   | BRP    | MCV    | n/u    | VDQ     | n/u    | EDV    | n/u    |

| TMPGG  | Temperature<br>and gas gauge<br>register             | 02h           | Read  | TMP3   | TMP2   | TMP1   | TMP0   | GG3     | GG2    | GG1    | GG0    |

| NACH   | Nominal<br>available<br>charge high<br>byte register | 03h           | R/W   | NACH7  | NACH6  | NACH5  | NACH4  | NACH3   | NACH2  | NACH1  | NACH0  |

| NACL   | Nominal<br>available<br>charge low<br>byte register  | 17h           | Read  | NACL7  | NACL6  | NACL5  | NACL4  | NACL3   | NACL2  | NACL1  | NACL0  |

| BATID  | Battery<br>identification<br>register                | 04h           | R/W   | BATID7 | BATID6 | BATID5 | BATID4 | BATID3  | BATID2 | BATID1 | BATID0 |

| LMD    | Last meas-<br>ured dis-<br>charge regis-<br>ter      | 05h           | R/W   | LMD7   | LMD6   | LMD5   | LMD4   | LMD3    | LMD2   | LMD1   | LMD0   |

| FLGS2  | Secondary<br>status flags<br>register                | 06h           | Read  | CR     | DR2    | DR1    | DR0    | n/u     | n/u    | n/u    | OVLD   |

| OCTL   | Output control register                              | 0ah           | Write | 1      | OC5    | OC4    | OC3    | OC2     | OC1    | n/u    | OCE    |

| RST    | Reset register                                       | 39h           | Write | RST    | 0      | 0      | 0      | 0       | 0      | 0      | 0      |

**Note:** n/u = not used

The *charge status* flag (CHGS) is asserted when a valid charge rate is detected. Charge rate is deemed valid when  $V_{SRO} < -400 \mu V$ . A  $V_{SRO}$  of greater than- $400 \mu V$  or discharge activity clears CHGS.

The CHGS values are:

| FLGS1 Bits |   |   |   |   |   |   |   |  |  |

|------------|---|---|---|---|---|---|---|--|--|

| 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

| CHGS       | - | - | - | - | - | - | - |  |  |

Where CHGS is:

- 0 Either discharge activity detected or  $V_{SRO} > -400 \mu V$

- 1  $V_{SRO} < -400 \mu V$

The *battery replaced* flag (BRP) is asserted whenever the potential on the SB pin (relative to  $V_{SS}$ ),  $V_{SB}$ , rises above 0.1V and determines the internal registers have been corrupted. The BRP flag is also set when the bq2011K is reset (see the RST register description). BRP is cleared if either the bq2011K is charged until NAC = LMD or discharged until EDV is reached. BRP = 1 signifies that the device has been reset.

The BRP values are:

|                 | FLGS1 Bits |   |   |   |   |   |   |  |  |  |

|-----------------|------------|---|---|---|---|---|---|--|--|--|

| 7 6 5 4 3 2 1 0 |            |   |   |   |   |   |   |  |  |  |

| -               | BRP        | - | - | - | - | - | - |  |  |  |

Where BRP is:

- $\begin{array}{ll} 0 & \ \, \text{bq2011K is charged until NAC} = LMD \ \text{or} \\ \text{discharged until the EDV flag is asserted} \end{array}$

- 1 Initial or full  $V_{CC}$  reset, or a serial port initiated reset has occurred

The *maximum cell voltage* flag (MCV) is asserted whenever the potential on the SB pin (relative to  $V_{\rm SS}$ ) is above 2.0V. The MCV flag is asserted until the condition causing MCV is removed.

The MCV values are:

| FLGS1 Bits      |   |     |   |   |   |   |   |  |

|-----------------|---|-----|---|---|---|---|---|--|

| 7 6 5 4 3 2 1 0 |   |     |   |   |   |   |   |  |

| -               | - | MCV | - | - | - | - | - |  |

Where MCV is:

- $0 V_{SB} < 2.0V$

- $1 \qquad V_{SB} > 2.0 V$

The *valid discharge* flag (VDQ) is asserted when the bq2011K is discharged from NAC=LMD. The flag re-

mains set until either LMD is updated or one of three actions that can clear VDQ occurs:

- The self-discharge count register (SDCR) has exceeded the maximum acceptable value (4096 counts) for an LMD update.

- A valid charge action equal to 256 NAC counts with  $V_{SRO}$  < -400 $\mu$ V.

- The EDV flag was set at a temperature below 0°C

The VDQ values are:

| FLGS1 Bits      |   |   |   |     |   |   |   |  |  |

|-----------------|---|---|---|-----|---|---|---|--|--|

| 7 6 5 4 3 2 1 0 |   |   |   |     |   |   |   |  |  |

| -               | - | - | - | VDQ | - | - | - |  |  |

Where VDQ is:

- 0 SDCR  $\geq$  4096, subsequent valid charge action detected, or EDV is asserted with the temperature less than 0°C

- 1 On first discharge after NAC = LMD

The *end-of-discharge warning* flag (EDV) warns the user that the battery is empty. SEG1 blinks at a 4Hz rate. EDV detection is disabled if OVLD = 1. The EDV flag is latched until a valid charge has been detected.

The EDV values are:

|                 | FLGS1 Bits |   |   |   |   |     |   |  |  |  |

|-----------------|------------|---|---|---|---|-----|---|--|--|--|

| 7 6 5 4 3 2 1 0 |            |   |   |   |   |     |   |  |  |  |

| -               | -          | - | - | - | - | EDV | - |  |  |  |

Where EDV is:

- 0 Valid charge action detected

- $1 V_{\rm SB} < V_{\rm EDV}$

#### Temperature and Gas Gauge Register (TMPGG)

The read-only TMPGG register (address=02h) contains two data fields. The first field contains the battery temperature. The second field contains the available charge from the battery.

| TMPGG Temperature Bits |      |      |      |   |   |   |  |  |  |

|------------------------|------|------|------|---|---|---|--|--|--|

| 7                      | 6    | 4    | 3    | 2 | 1 | 0 |  |  |  |

| TMP3                   | TMP2 | TMP1 | TMP0 | - | - | - |  |  |  |

The bq2011K contains an internal temperature sensor. The temperature is used to set charge efficiency factors as well as to adjust the self-discharge coefficient. The temperature register contents may be translated as shown in Table 6.

**Table 6. Temperature Register Contents**

| ТМР3 | TMP2 | TMP1 | TMP0 | Temperature                                            |

|------|------|------|------|--------------------------------------------------------|

| 0    | 0    | 0    | 0    | T < -30°C                                              |

| 0    | 0    | 0    | 1    | -30°C < T < -20°C                                      |

| 0    | 0    | 1    | 0    | -20°C < T < -10°C                                      |

| 0    | 0    | 1    | 1    | $-10^{\circ} \text{C} < \text{T} < 0^{\circ} \text{C}$ |

| 0    | 1    | 0    | 0    | $0^{\circ} \text{C} < \text{T} < 10^{\circ} \text{C}$  |

| 0    | 1    | 0    | 1    | 10°C < T < 20°C                                        |

| 0    | 1    | 1    | 0    | 20°C < T < 30°C                                        |

| 0    | 1    | 1    | 1    | 30°C < T < 40°C                                        |

| 1    | 0    | 0    | 0    | 40°C < T < 50°C                                        |

| 1    | 0    | 0    | 1    | 50°C < T < 60°C                                        |

| 1    | 0    | 1    | 0    | 60°C < T < 70°C                                        |

| 1    | 0    | 1    | 1    | 70°C < T < 80°C                                        |

| 1    | 1    | 0    | 0    | T > 80°C                                               |

The bq2011K calculates the available charge as a function of NAC, temperature, and a full reference, either LMD or PFC. The results of the calculation are available via the display port or the gas gauge field of the TMPGG register. The register is used to give available capacity in  $\frac{1}{16}$  increments from 0 to  $\frac{15}{16}$ .

| TMPGG Gas Gauge Bits |   |   |   |     |     |     |     |  |  |

|----------------------|---|---|---|-----|-----|-----|-----|--|--|

| 7 6 5 4 3 2 1 0      |   |   |   |     |     |     | 0   |  |  |

| -                    | - | - | - | GG3 | GG2 | GG1 | GG0 |  |  |

The gas gauge display and the gas gauge portion of the TMPGG register are adjusted for cold temperature dependencies. A piece-wise correction is performed as follows:

| Temperature                                          | Available Capacity Calculation         |

|------------------------------------------------------|----------------------------------------|

| > 0°C                                                | NAC / "Full Reference"                 |

| $-20^{\circ}\text{C} < \text{T} < 0^{\circ}\text{C}$ | $0.75*\mathrm{NAC}$ / "Full Reference" |

| <-20°C                                               | 0.5 * NAC / "Full Reference"           |

The adjustment between > 0 °C and -20 °C < T < 0 °C has a 4 °C hysteresis.

#### Nominal Available Charge Register (NAC)

The read/write NACH register (address=03h) and the read-only NACL register (address=17h) are the main gas gauging registers for the bq2011K. The NAC registers are incremented during charge actions and decremented during discharge and self-discharge actions. The correction factors for charge/discharge efficiency are applied automatically to NAC.

If  $SEG_4=0$  on reset, then NACH = PFC and NACL = 0. If  $SEG_4=Z$  or H, the NACH and NACL registers are cleared to zero. NACL stops counting when NACH reaches zero. When the bq2011K detects a valid charge, NACL resets to zero; writing to the NAC register affects the available charge counts and, therefore, affects the bq2011K gas gauge operation.

#### **Battery Identification Register (BATID)**

The read/write BATID register (address=04h) is available for use by the system to determine the type of battery pack. The BATID contents are retained as long as  $V_{\rm CC}$  is greater than 2V. The contents of BATID have no effect on the operation of the bq2011K. There is no default setting for this register.

#### Last Measured Discharge Register (LMD)

LMD is a read/write register (address=05h) that the bq2011K uses as a measured full reference. The bq2011K adjusts LMD based on the measured discharge capacity of the battery from full to empty. In this way the bq2011K updates the capacity of the battery. LMD is set to PFC during a bq2011K reset.

#### Secondary Status Flags Register (FLGS2)

The read-only FLGS2 register (address=06h) contains the secondary bq2011K flags.

The *charge rate* flag (CR) is used to denote the fast charge regime. Fast charge is assumed whenever a charge action is initiated. The CR flag remains asserted if the charge rate does not fall below 2 counts/sec.

The CR values are:

|                 | FLGS2 Bits          |   |   |   |   |   |   |   |  |  |

|-----------------|---------------------|---|---|---|---|---|---|---|--|--|

| 7 6 5 4 3 2 1 0 |                     |   |   |   |   |   |   |   |  |  |

|                 | $\operatorname{CR}$ | - | - | - | - | - | - | - |  |  |

Where CR is:

- 0 When charge rate falls below 2 counts/sec

- 1 When charge rate is above 2 counts/sec

The fast charge regime efficiency factors are used when CR = 1. When CR = 0, the trickle charge efficiency factors are used. The time to change CR varies due to the user-selectable count rates.

The *discharge rate* flags, DR2-0, are bits 6-4.

|                 | FLGS2 Bits |     |     |   |   |   |  |  |  |  |

|-----------------|------------|-----|-----|---|---|---|--|--|--|--|

| 7 6 5 4 3 2 1 0 |            |     |     |   |   |   |  |  |  |  |

| -               | DR2        | DR1 | DR0 | - | - | - |  |  |  |  |

They are used to determine the present discharge regime as follows:

| DR2 | DR1 | DR0 | V <sub>SRO</sub> (mV) |

|-----|-----|-----|-----------------------|

| 0   | 0   | 0   | $0 < V_{SRO} \le 10$  |

| 0   | 0   | 1   | $10 < V_{SRO} \le 20$ |

| 0   | 1   | 0   | $20 < V_{SRO} \le 40$ |

| 0   | 1   | 1   | $40 < V_{SRO} \le 60$ |

| 1   | 0   | 0   | $V_{SRO} > 60$        |

The overload flag (OVLD) is asserted when a discharge overload is detected,  $V_{SRO} > 60 mV$ . OVLD remains asserted as long as the condition is valid.

| FLGS2 Bits      |   |   |   |   |   |   |      |  |  |

|-----------------|---|---|---|---|---|---|------|--|--|

| 7 6 5 4 3 2 1 0 |   |   |   |   |   |   |      |  |  |

| -               | - | - | - | - | - | - | OVLD |  |  |

#### **Output Control Register (OCTL)**

The write-only OCTL register (address=0ah) provides the system with a means to check the display connections for the bq2011K. The segment drivers may be overwritten by data from OCTL when the least-significant bit of OCTL, OCE, is set. The data in bits  $OC_{5-1}$  of the OCTL register (see Table 5 for details) is output onto the segment pins,  $SEG_{5-1}$ , respectively if OCE=1. Whenever OCE is written to 1, the MSB of OCTL should be set to a 1. The OCE register location must be cleared to return the bq2011K to normal operation. OCE may be cleared by either writing the bit to a logic zero via the serial port or by resetting the bq2011K as explained below. Note: Whenever the OCTL register is written, the MSB of OCTL should be written to a logic one

#### **Reset Register (RST)**

The reset register (address=39h) provides the means to perform a software-controlled reset of the device. A full device reset may be accomplished by first writing LMD (address = 05h) to 00h and then writing the RST register contents from 00h to 80h. Setting any bit other than the most-significant bit of the RST register is not allowed, and results in improper operation of the bq2011K.

Resetting the bq2011K sets the following:

- LMD = PFC

- VDQ, OCE, and NAC = 0 (NAC = PFC when PROG<sub>4</sub> = L)

- BRP = 1

#### Display

The bq2011K can directly display capacity information using low-power LEDs. If LEDs are used, the segment pins should be tied to  $V_{\rm CC}$ , the battery, or the LCOM pin through resistors for programming the bq2011K.

The bq2011K displays the battery charge state in absolute mode. In absolute mode, each segment represents a fixed amount of charge, based on the initial PFC. In absolute mode, each segment represents 20% of the PFC. As the battery wears out over time, it is possible for the LMD to be below the initial PFC. In this case, all of the LEDs may not turn on, representing the reduction in the actual battery capacity.

The capacity display is also adjusted for the present battery temperature. The temperature adjustment reflects the available capacity at a given temperature but does not affect the NAC register. The temperature adjustments are detailed in the TMPGG register description.

When  $\overline{\rm DISP}$  is tied to  $V_{\rm CC}$ , the SEG<sub>1–5</sub> outputs are inactive. When  $\overline{\rm DISP}$  is left floating, the display becomes active during charge if the NAC registers are counting at a rate equivalent to  $V_{\rm SRO} <$  -2mV or fast discharge if the NAC registers are counting at a rate equivalent to  $V_{\rm SRO} >$  2mV. When  $\overline{\rm DISP}$  is left floating, the display also becomes active after the detection of a discharge signal with a minimum amplitude of  $V_{\rm SR} >$  20mV (10A for  $R_{\rm S} = 0.002\Omega)$  and a minimum pulse width of 25ms. When  $\overline{\rm DISP}$  is pulled low, the segment outputs become active for  $4s, \pm 0.5s.$

The segment outputs are modulated as two banks, with segments  $1,\,3,\,$  and 5 alternating with segments 2 and 4. The segment outputs are modulated at approximately  $320 \mathrm{Hz}$ , with each bank active for 30% of the period.

$SEG_1$  blinks at a 4Hz rate whenever  $V_{SB}$  has been detected to be below  $V_{EDV}$  to indicate a low-battery condition or NAC is less than 10% of PFC.

### Microregulator

The bq2011K can operate directly from 4 cells. To facilitate the power supply requirements of the bq2011K, an REF output is provided to regulate an external low-threshold n-FET. A micropower source for the bq2011K can be inexpensively built using the FET and an external resistor.

# **Absolute Maximum Ratings**

| Symbol             | Parameter                   | Minimum | Maximum | Unit | Notes                                                                                                                                         |

|--------------------|-----------------------------|---------|---------|------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| $V_{\rm CC}$       | Relative to V <sub>SS</sub> | -0.3    | 7.0     | V    |                                                                                                                                               |

| All other pins     | Relative to V <sub>SS</sub> | -0.3    | 7.0     | V    |                                                                                                                                               |

| $ m V_{SR}$        | Relative to $V_{\rm SS}$    | -0.3    | 7.0     | V    | Minimum $100\Omega$ series resistor should be used to protect SR in case of a shorted battery (see the bq2011K application note for details). |

| $T_{\mathrm{OPR}}$ | Operating temperature       | 0       | 70      | °C   | Commercial                                                                                                                                    |

| TOPK               | Operating temperature       |         |         |      |                                                                                                                                               |

Note:

Permanent device damage may occur if **Absolute Maximum Ratings** are exceeded. Functional operation should be limited to the Recommended DC Operating Conditions detailed in this data sheet. Exposure to conditions beyond the operational limits for extended periods of time may affect device reliability.

### DC Voltage Thresholds (TA = TOPR; V = 3.0 to 6.5V)

| Symbol             | Parameter                   | Minimum                 | Typical      | Maximum                 | Unit | Notes                             |

|--------------------|-----------------------------|-------------------------|--------------|-------------------------|------|-----------------------------------|

| $V_{\mathrm{EDV}}$ | End-of-discharge warning    | 0.96 * V <sub>EDV</sub> | $ m V_{EDV}$ | 1.04 * V <sub>EDV</sub> | V    | SB                                |

| $V_{\mathrm{SRQ}}$ | Valid charge                | -                       | -            | -400                    | μV   | V <sub>SR</sub> + V <sub>OS</sub> |

| $V_{ m SRD}$       | Valid discharge             | 500                     | -            | -                       | μV   | $V_{\rm SR}$ + $V_{\rm OS}$       |

| $V_{ m MCV}$       | Maximum single-cell voltage | 1.95                    | 2.0          | 2.05                    | V    | SB                                |

Note:

For proper operation of the threshold detection circuit,  $V_{\rm CC}$  must be at least 1.5V greater than the voltage being measured.

# DC Electrical Characteristics (TA = TOPR)

| Symbol               | Parameter                                           | Minimum               | Typical | Maximum        | Unit      | Notes                                                                                        |

|----------------------|-----------------------------------------------------|-----------------------|---------|----------------|-----------|----------------------------------------------------------------------------------------------|

| $V_{\rm CC}$         | Supply voltage                                      | 3.0                   | 4.25    | 6.5            | V         | $V_{CC}$ excursion from < 2.0V to $\geq$ 3.0V initializes the unit.                          |

| vos                  | Offset referred to $V_{\rm SR}$                     | -                     | ±50     | ±150           | μV        | $\overline{\mathrm{DISP}} = \mathrm{V_{CC}}$                                                 |

| <b>X</b> 7           | Reference at 25°C                                   | 5.7                   | 6.0     | 6.3            | V         | $I_{REF} = 5\mu A$                                                                           |

| $ m V_{REF}$         | Reference at -40°C to +85°C                         | 4.5                   | -       | 7.5            | V         | $I_{REF} = 5\mu A$                                                                           |

| $R_{REF}$            | Reference input impedance                           | 2.0                   | 5.0     | -              | $M\Omega$ | $V_{REF} = 3V$                                                                               |

|                      |                                                     | -                     | 90      | 135            | μΑ        | $V_{CC} = 3.0V$ , $DQ = 0$                                                                   |

| $I_{CC}$             | Normal operation                                    | -                     | 120     | 180            | μΑ        | $V_{CC} = 4.25V, DQ = 0$                                                                     |

|                      |                                                     | -                     | 170     | 250            | μΑ        | $V_{CC} = 6.5V, DQ = 0$                                                                      |

| $ m V_{SB}$          | Battery input                                       | 0                     | -       | $V_{\rm CC}$   | V         |                                                                                              |

| R <sub>SBmax</sub>   | SB input impedance                                  | 10                    | -       | -              | ΜΩ        | $0 < V_{SB} < V_{CC}$                                                                        |

| $I_{\mathrm{DISP}}$  | DISP input leakage                                  | -                     | -       | 5              | μА        | $V_{\rm DISP} = V_{\rm SS}$                                                                  |

| $I_{LCOM}$           | LCOM input leakage                                  | -0.2                  | -       | 0.2            | μA        | $\overline{\mathrm{DISP}} = \mathrm{V_{CC}}$                                                 |

| $I_{ m RBI}$         | RBI data-retention current                          | -                     | -       | 100            | nA        | $V_{RBI} > V_{CC} < 3V$                                                                      |

| $R_{DQ}$             | Internal pulldown                                   | 500                   | -       | -              | ΚΩ        |                                                                                              |

| $V_{\mathrm{SR}}$    | Sense resistor input                                | -0.3                  | -       | 2.0            | V         | V <sub>SR</sub> > V <sub>SS</sub> = discharge;<br>V <sub>SR</sub> < V <sub>SS</sub> = charge |

| $R_{SR}$             | SR input impedance                                  | 10                    | -       | -              | ΜΩ        | -200mV < V <sub>SR</sub> < V <sub>CC</sub>                                                   |

| $V_{\mathrm{IHPFC}}$ | PROG/SPFC logic input high                          | V <sub>CC</sub> - 0.2 | -       | -              | V         | SPFC, PROG <sub>1-4</sub>                                                                    |

| $V_{\rm ILPFC}$      | PROG/SPFC logic input low                           | -                     | -       | $V_{SS} + 0.2$ | V         | SPFC, PROG <sub>1-4</sub>                                                                    |

| V <sub>IZPFC</sub>   | PROG/SPFC logic input Z                             | float                 | -       | float          | V         | SPFC, PROG <sub>1-4</sub>                                                                    |

| I <sub>IHPFC</sub>   | PROG/SPFC input high current                        | -                     | 1.2     | -              | μA        | $V_{\rm PFC} = V_{\rm CC}/2$                                                                 |

| $I_{\rm ILPFC}$      | PROG/SPFC input low current                         | -                     | 1.2     | -              | μΑ        | $V_{\rm PFC} = V_{\rm CC}/2$                                                                 |

| $V_{\mathrm{OLSL}}$  | SEG <sub>X</sub> output low, low V <sub>CC</sub>    | -                     | 0.1     | -              | V         | $V_{CC}$ = 3V, $I_{OLS} \le 1.75$ mA<br>SEG <sub>1</sub> -SEG <sub>5</sub>                   |

| $V_{OLSH}$           | ${ m SEG}_{ m X}$ output low, high ${ m V}_{ m CC}$ | -                     | 0.4     | -              | V         | $\begin{aligned} V_{CC} &= 6.5 V, I_{OLS} \leq 11.0 mA \\ SEG_1 &= SEG_5 \end{aligned}$      |

| VOHML                | LCOM output high, low V <sub>CC</sub>               | V <sub>CC</sub> - 0.3 | -       | -              | V         | $V_{CC} = 3V, I_{OHLCOM} = -5.25mA$                                                          |

| $V_{\mathrm{OHMH}}$  | LCOM output high, high V <sub>CC</sub>              | V <sub>CC</sub> - 0.6 | -       | -              | V         | $V_{\rm CC}$ = 6.5V, $I_{\rm OHLCOM}$ = -33.0mA                                              |

| I <sub>OHLCOM</sub>  | LCOM source current                                 | -33                   | -       | -              | mA        | At $V_{OHLCOM} = V_{CC} - 0.6V$                                                              |

| Iols                 | SEG <sub>X</sub> sink current                       | 11.0                  | -       | -              | mA        | At $V_{OLSH} = 0.4V$ , $V_{CC} = 6.5V$                                                       |

| $I_{OL}$             | Open-drain sink current                             | 5.0                   | -       | -              | mA        | At $V_{OL} = V_{SS} + 0.3V$ , $DQ$                                                           |

| $V_{\mathrm{OL}}$    | Open-drain output low                               | -                     | -       | 0.5            | V         | $I_{OL} \le 5mA, DQ$                                                                         |

| $ m V_{IHDQ}$        | DQ input high                                       | 2.5                   | -       | -              | V         | DQ                                                                                           |

| $ m V_{ILDQ}$        | DQ input low                                        | -                     | -       | 0.8            | V         | DQ                                                                                           |

| RFLOAT               | Float state external impedance                      | -                     | 5       | -              | ΜΩ        | SPFC, PROG <sub>1-4</sub>                                                                    |

# **Serial Communication Timing Specification** (TA = TOPR)

| Symbol            | Parameter                   | Minimum | Typical | Maximum | Unit | Notes    |

|-------------------|-----------------------------|---------|---------|---------|------|----------|

| tcych             | Cycle time, host to bq2011K | 3       | -       | -       | ms   | See note |

| tcycb             | Cycle time, bq2011K to host | 3       | -       | 6       | ms   |          |

| $t_{ m STRH}$     | Start hold, host to bq2011K | 5       | -       | -       | ns   |          |

| $t_{\rm STRB}$    | Start hold, bq2011K to host | 500     | -       | -       | μs   |          |

| $ m t_{DSU}$      | Data setup                  | -       | -       | 750     | μs   |          |

| ${ m t_{DH}}$     | Data hold                   | 750     | -       | -       | μs   |          |

| ${ m t}_{ m DV}$  | Data valid                  | 1.50    | -       | -       | ms   |          |

| tssu              | Stop setup                  | -       | -       | 2.25    | ms   |          |

| $t_{\mathrm{SH}}$ | Stop hold                   | 700     | -       | -       | μs   |          |

| $t_{\rm SV}$      | Stop valid                  | 2.95    | -       | -       | ms   |          |

| $t_{\mathrm{B}}$  | Break                       | 3       | -       | -       | ms   |          |

| $t_{ m BR}$       | Break recovery              | 1       | -       |         | ms   |          |

Note: The open-drain DQ pin should be pulled to at least  $V_{\rm CC}$  by the host system for proper DQ operation. DQ may be left floating if the serial interface is not used.

# **Serial Communication Timing Illustration**

TD201002.eps

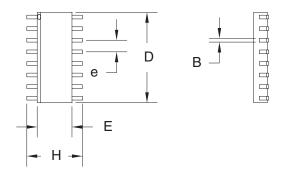

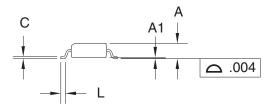

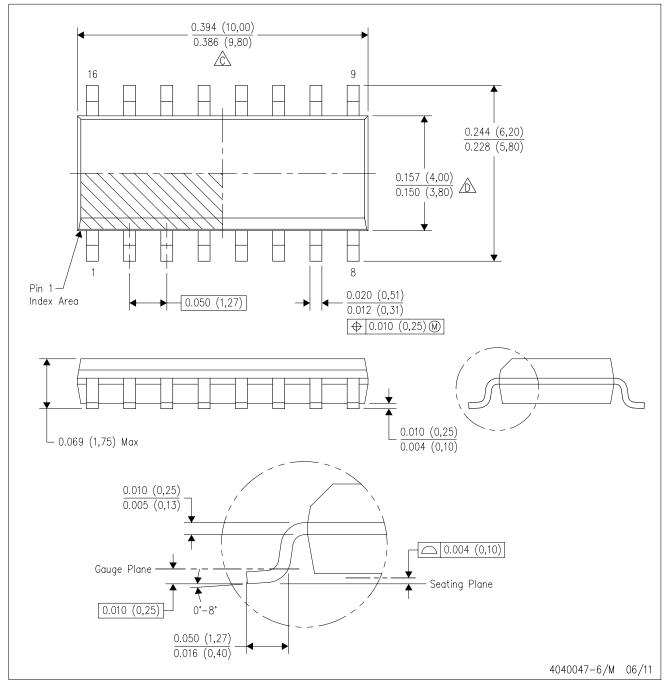

# 16-Pin SOIC Narrow (SN)

# 16-Pin SN (SOIC Narrow)

| Dimension | Minimum | Maximum |

|-----------|---------|---------|

| A         | 0.060   | 0.070   |

| A1        | 0.004   | 0.010   |

| В         | 0.013   | 0.020   |

| C         | 0.007   | 0.010   |

| D         | 0.385   | 0.400   |

| E         | 0.150   | 0.160   |

| e         | 0.045   | 0.055   |

| Н         | 0.225   | 0.245   |

| L         | 0.015   | 0.035   |

All dimensions are in inches.

# **Data Sheet Revision History**

| Change No. | Page No. | Description                                | Nature of Change |

|------------|----------|--------------------------------------------|------------------|

| 1          | 6        | Removed relative display mode from Table 1 | Correction       |

**Notes:** Change 1 = Oct. 1997 B changes from Oct. 1995.

# **Ordering Information**

ti.com 11-Oct-2005

#### **PACKAGING INFORMATION**

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins Package<br>Qty | Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|-----------------|--------------------|---------------------|-------------------------|------------------|------------------------------|

| BQ2011KSN-D121   | OBSOLETE              | SOIC            | D                  | 16                  | TBD                     | Call TI          | Call TI                      |

| BQ2011KSN-D121TR | OBSOLETE              | SOIC            | D                  | 16                  | TBD                     | Call TI          | Call TI                      |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

**NRND:** Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS) or Green (RoHS & no Sb/Br) - please check <a href="http://www.ti.com/productcontent">http://www.ti.com/productcontent</a> for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# D (R-PDS0-G16)

#### PLASTIC SMALL OUTLINE

NOTES:

- A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.006 (0,15) each side.

- Body width does not include interlead flash. Interlead flash shall not exceed 0.017 (0,43) each side.

- E. Reference JEDEC MS-012 variation AC.

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products                    |                        | Applications                  |                                   |

|-----------------------------|------------------------|-------------------------------|-----------------------------------|

| Audio                       | www.ti.com/audio       | Communications and Telecom    | www.ti.com/communications         |

| Amplifiers                  | amplifier.ti.com       | Computers and Peripherals     | www.ti.com/computers              |

| Data Converters             | dataconverter.ti.com   | Consumer Electronics          | www.ti.com/consumer-apps          |

| DLP® Products               | www.dlp.com            | Energy and Lighting           | www.ti.com/energy                 |

| DSP                         | dsp.ti.com             | Industrial                    | www.ti.com/industrial             |

| Clocks and Timers           | www.ti.com/clocks      | Medical                       | www.ti.com/medical                |

| Interface                   | interface.ti.com       | Security                      | www.ti.com/security               |

| Logic                       | logic.ti.com           | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Power Mgmt                  | power.ti.com           | Transportation and Automotive | www.ti.com/automotive             |

| Microcontrollers            | microcontroller.ti.com | Video and Imaging             | www.ti.com/video                  |

| RFID                        | www.ti-rfid.com        | Wireless                      | www.ti.com/wireless-apps          |

| RF/IF and ZigBee® Solutions | www.ti.com/lprf        |                               |                                   |

**TI E2E Community Home Page**

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2011, Texas Instruments Incorporated

e2e.ti.com