Ver 1.1

## **BQR2V** Series FPGA

# Datasheet

Part Number: BQR2V3000

## Page of Revise Control

| Version<br>No. | Publish<br>Time | Revised<br>Chapter | Revise Introduction | Note |

|----------------|-----------------|--------------------|---------------------|------|

| 1.0            | 2017.1          |                    | Initial release.    |      |

| 1.1            | 2018.3          |                    | Update format       |      |

|                |                 |                    |                     |      |

|                |                 |                    |                     |      |

|                |                 |                    |                     |      |

|                |                 |                    |                     |      |

|                |                 |                    |                     |      |

|                |                 |                    |                     |      |

|                |                 |                    |                     |      |

## **TABLE OF CONTENTS**

| 1. | Fec | atures5                                              |

|----|-----|------------------------------------------------------|

| 2. | Ger | neral Description                                    |

| 3. | Arc | hitecture7                                           |

| 3  | .1  | Overview                                             |

| 3  | .2  | Features                                             |

| 3  | .3  | Combinations and Maximum Number of Available I/Os51  |

| 4. | Cor | nfiguration51                                        |

| 4  | .1  | Configuration Modes                                  |

| 4  | .2  | Slave-Serial Mode                                    |

| 4  | .3  | Master-Serial Mode                                   |

| 4  | .4  | Slave SelectMAP Mode                                 |

| 4  | .5  | Master SelectMAP Mode                                |

| 4  | .6  | Boundary-Scan (JTAG, IEEE 1532) Mode                 |

| 4  | .7  | Configuration Sequence                               |

| 4  | .8  | Readback                                             |

| 4  | .9  | Bitstream Encryption                                 |

| 4  | .10 | Partial Reconfiguration                              |

| 5. | Ele | ctrical Characteristics                              |

| 5  | .1  | DC Characteristics                                   |

| 5  | .2  | Power-On Power Supply Requirements                   |

| 5  | .3  | General Power Supply Requirements                    |

| 5  | .4  | DC Input and Output Levels                           |

| 5  | 5.5 | LDT Differential Signal DC Specifications (LDT_25)60 |

| 5  | .6  | LVDS DC Specifications (LVDS_33 and LVDS_25)60       |

| 5   | .7   | Extended LVDS DC Specifications (LVDSEXT_33 and LVDSEXT_25) | 61 |

|-----|------|-------------------------------------------------------------|----|

| 5   | .8   | LVPECL DC Specifications                                    | 61 |

| 6.  | Pin  | Definitions                                                 | 62 |

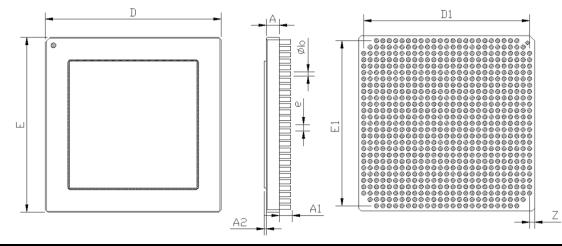

| 7.  | Pin  | out Information and Package                                 | 65 |

| Ap  | pend | ix I Electrical performance characteristics                 | 75 |

| Ap  | pend | ix II Application Notes                                     | 82 |

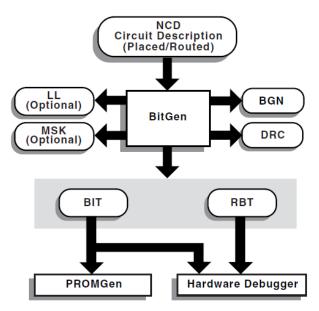

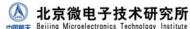

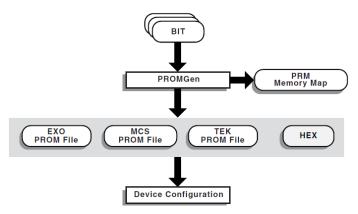

| Ap  | pend | ix III BitGen and PROMGen Switches and Options              | 83 |

| Ser | vice | and Support:                                                | 98 |

## \_\_\_\_\_

## 1. Features

- 0.13 µm 8-layer epitaxial process

- Certified to CAST C

- Guaranteed over the full military temperature range(-55°C to +125°C)

- Radiation hardened FPGAs for space and satellite Applications

- Guaranteed total ionizing dose to 100K Rad(si)

- Latch-up immune to LET = 75 MeV cm<sup>2</sup>/mg

- IP-Immersion Architecture

- ♦ Densities 3M system gates

- 300+ MHz internal clock

speed (Advance Data)

- ♦ 622+ Mb/s I/O(Advance Data)

- SelectRAMTM Memory Hierarchy

- 1.728Mb of dual-port RAM in 18 Kbit block SelectRAM resources

- 0.448 Mb of distributed

SelectRAM resources

- High-Performance Interfaces to External Memory

- ♦ SRAM interfaces

- SDR/DDR SRAM

- QDR SRAM

- ♦ CAM interfaces

- Arithmetic Functions

- ♦ Dedicated 18-bit×18-bit multiplier blocks

- ♦ Fast look-ahead carry logic chains

- Flexible Logic Resources

- ♦ Up to 28672 internal registers/latches with Clock Enable

- Up to 28672 look-up tables

(LUTs) or cascadable 16-bit

shift registers

- ♦ Wide multiplexers and wide-input function support

- Horizontal cascade chain and sum-of-products support

- ♦ Internal 3-state busing

- High-Performance Clock

Management Circuitry

- ♦ Up to 12 DCM (Digital Clock Manager) modules

- Precise clock de-skew

- Flexible frequency synthesis

- High-resolution phase shifting

- ♦ 16 global clock multiplexer buffers

- Active Interconnect Technology

- ♦ Fourth generation segmented routing structure

- ♦ Predictable, fast routing delay, independent of fanout

- SelectIO<sup>TM</sup>-Ultra Technology

- ♦ Up to 516 user I/Os

- 19 single-ended and six

differential standards

- Programmable sink current

(2 mA to 24 mA) per I/O

- Digitally Controlled

Impedance (DCI) I/O:

on-chip termination resistors

for single-ended I/O

standards

- ♦ Differential Signaling

- 622 Mb/s Low-Voltage Differential Signaling I/O (LVDS) with current mode drivers

- Bus LVDS I/O

- Lightning Data Transport (LDT) I/O with current driver buffers

- Low-Voltage Positive Emitter-Coupled Logic (LVPECL) I/O

- Built-in DDR input and output registers

- ♦ Proprietary

high-performance SelectLink

Technology

- High-bandwidth data path

- Double Data Rate (DDR) link

- Web-based HDL generation methodology

- Supported by Xilinx ISE Development Systems

**ē微电子技术研究**所

- SRAM-Based In-System Configuration

- ♦ Fast SelectMAP configuration

- ♦ IEEE 1532 support

- ♦ Partial reconfiguration

- ♦ Unlimited reprogrammability

- ♦ Readback capability

- 1.5V (V<sub>CCINT</sub>) Core Power Supply, Dedicated 3.3V V<sub>CCAUX</sub> Auxiliary and V<sub>CCO</sub> I/O Power Supplies IEEE 1149.1 Compatible Boundary-Scan Logic Support

## 2. General Description

The BQR2V3000 is developed for high performance, high-density, aerospace designs that are based on IP cores and customized modules. The device delivers complete solutions for telecommunication, networking, video, and DSP applications, including PCI, LVDS, and DDR interfaces.

The 0.13 µm CMOS 8-layer metal process and the BQR2V3000 architecture are optimized for high speed with low power consumption. Combining a wide variety of flexible features and a high densities of 1 million system gates, the BQR2V3000 enhances programmable logic design capabilities and is a powerful alternative to mask-programmed gates arrays and other one-time-programmable device. As shown

in 错误! 未找到引用源。, the BQR2V3000 comprises CLB, Multiplier Blocks, SelectRAM Blocks, DCMs and IOBs.

|           | Sautan          | CLB (1 C  | lices = Max 128 bits) | Multiplier          | SelectR              | AM Blocks |         |      |              |

|-----------|-----------------|-----------|-----------------------|---------------------|----------------------|-----------|---------|------|--------------|

| Device    | System<br>Gates | Array     | Slices                | Maximum Distributed | Multiplier<br>Blocks | 18 Kbit   | Max RAM | DCMs | Max I/O Pads |

|           |                 | Row xCol. | Shees                 | RAM Kbits           |                      | Blocks    | (Kbits) |      |              |

| BQR2V3000 | 3M              | 64 x 56   | 14,336                | 448                 | 96                   | 96        | 1,728   | 12   | 516          |

Table 1: BQR2V3000-CCGA717 Field-Programmable Gate Array

## **3.** Architecture

## 3.1 Overview

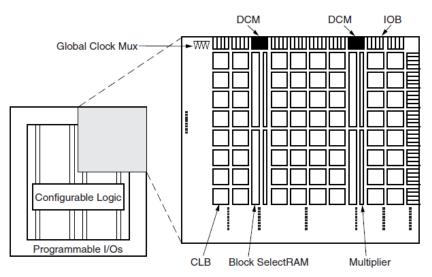

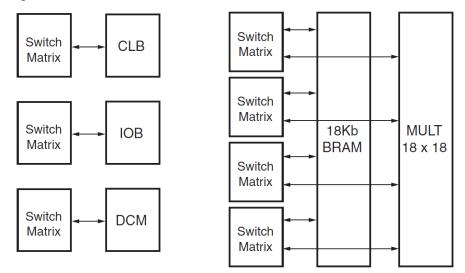

BQR2V3000 device are user-programmable gate arrays with various configurable elements. The BQR2V3000 architecture is optimized for high-density and high-performance logic designs. As shown in Figure 1, the programmable device is comprised of input/output blocks (IOBs) and internal configurable logic blocks (CLBs).

Programmable I/O blocks provide the interface between package pins and the internal configurable logic. Most popular and leading-edge I/O standards are supported by the programmable IOBs.

The internal configurable logic includes four major elements organized in a regular array:

- Configurable Logic Blocks (CLBs) provide functional elements for combinatorial and synchronous logic, including basic storage elements. BUFTs (3-state buffers) associated with each CLB element drive dedicated segmentable horizontal routing resources.

- Block SelectRAM memory modules provide large 18 Kbit storage elements of dual-port RAM.

- Multiplier blocks are 18-bit×18-bit dedicated multipliers.

- DCM (Digital Clock Manager) blocks provide self-calibrating, fully digital solutions for clock distribution delay compensation, clock multiplication and division, coarse- and fine-grained clock phase shifting.

A new generation of programmable routing resources called Active Interconnect Technology interconnects all of these elements. The general routing matrix (GRM) is an array of routing switches. Each programmable element is tied to a switch matrix,

allowing multiple connections to the general routing matrix. The overall programmable interconnection is hierarchical and designed to support high-speed designs.

All programmable elements, including the routing resources, are controlled by values stored in static memory cells. These values are loaded in the memory cells during configuration and can be reloaded to change the functions of the programmable elements.

Figure 1 BQR2V3000 Architecture Overview

### 3.2 Features

This section briefly describes BQR2V3000 features.

## 3.2.1 Input/Output Blocks (IOBs)

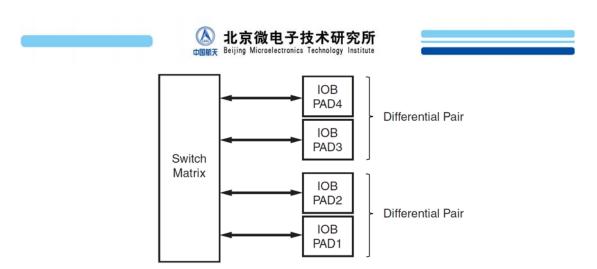

BQR2V3000 I/O blocks (IOBs) are provided in groups of two or four on the perimeter of each device. Each IOB can be used as an input and/or an output for single-ended I/Os. Two IOBs can be used as a differential pair. A differential pair is always connected to the same switch matrix, as shown in Figure 2.

Note: Differential I/Os must use the same clock.

IOB blocks are designed for high-performance I/Os, supporting 19 single-ended standards, as well as differential signaling with LVDS, LDT, Bus LVDS, and LVPECL.

Figure 2 BQR2V3000 Input/Output Tile

## **Supported I/O Standards**

BQR2V3000 IOB blocks feature SelectI/O-Ultra inputs and outputs that support a wide variety of I/O signaling standards. In addition to the internal supply voltage (VCCINT = 1.5V), output driver supply voltage (VCCO) is dependent on the I/O standard (see Table 1). An auxiliary supply voltage (VCCAUX = 3.3 V) is required, regardless of the I/O standard used.

| I/O Satndard | Output V <sub>CCO</sub> | Input V <sub>CCO</sub> | Input V <sub>REF</sub> | Board Termination<br>Voltage(V <sub>TT</sub> ) |

|--------------|-------------------------|------------------------|------------------------|------------------------------------------------|

| LVTTL        | 3.3                     | 3.3                    | N/A                    | N/A                                            |

| LVCMOS33     | 3.3                     | 3.3                    | N/A                    | N/A                                            |

| LVCMOS25     | 2.5                     | 2.5                    | N/A                    | N/A                                            |

| LVCMOS18     | 1.8                     | 1.8                    | N/A                    | N/A                                            |

| LVCMOS15     | 1.5                     | 1.5                    | N/A                    | N/A                                            |

| PCI33_3      | 3.3                     | 3.3                    | N/A                    | N/A                                            |

| PCI66_3      | 3.3                     | 3.3                    | N/A                    | N/A                                            |

| PCI-X        | 3.3                     | 3.3                    | N/A                    | N/A                                            |

| GTL          | Note 1                  | Note 1                 | 0.8                    | 1.2                                            |

| GTLP         | Note 1                  | Note 1                 | 1.0                    | 1.5                                            |

| HSTL_I       | 1.5                     | N/A                    | 0.75                   | 0.75                                           |

| HSTL_II      | 1.5                     | N/A                    | 0.75                   | 0.75                                           |

| HSTL_III     | 1.5                     | N/A                    | 0.9                    | 1.5                                            |

| HSTL_IV      | 1.5                     | N/A                    | 0.9                    | 1.5                                            |

| HSTL_I_18    | 1.8                     | N/A                    | 0.9                    | 0.9                                            |

Table 1 Supported Single-Ended I/O Standards

| I/O Satndard | Output V <sub>CCO</sub> | Input V <sub>CCO</sub> | Input V <sub>REF</sub> | Board Termination<br>Voltage(V <sub>TT</sub> ) |

|--------------|-------------------------|------------------------|------------------------|------------------------------------------------|

| HSTL_II_18   | 1.8                     | N/A                    | 0.9                    | 0.9                                            |

| HSTL_III_18  | 1.8                     | N/A                    | 1.1                    | 1.8                                            |

| HSTL_IV_18   | 1.8                     | N/A                    | 1.1                    | 1.8                                            |

| SSTL2_I      | 2.5                     | N/A                    | 1.25                   | 1.25                                           |

| SSTL2_II     | 2.5                     | N/A                    | 1.25                   | 1.25                                           |

| SSTL3_I      | 3.3                     | N/A                    | 1.5                    | 1.5                                            |

| SSTL3_II     | 3.3                     | N/A                    | 1.5                    | 1.5                                            |

| AGP-2X/AGP   | 3.3                     | N/A                    | 1.32                   | N/A                                            |

Notes:

$1.V_{CCO}$  of GTL or GTLP should not be lower than the termination voltage or the voltage seen at the I/O pad.

Table 2 Supported Differential Signal I/O Standards

| I/O Satndard | Output V <sub>CCO</sub> | Input V <sub>CCO</sub> | Input V <sub>REF</sub> | Output V <sub>OD</sub> |

|--------------|-------------------------|------------------------|------------------------|------------------------|

| LVPECL_33    | 3.3                     | N/A                    | N/A                    | 490mV to 1.22V         |

| LDT_25       | 2.5                     | N/A                    | N/A                    | 0.430-0.670            |

| LVDS_33      | 3.3                     | N/A                    | N/A                    | 0.250-0.400            |

| LVDS_25      | 2.5                     | N/A                    | N/A                    | 0.250-0.400            |

| LVDSEXT_33   | 3.3                     | N/A                    | N/A                    | 0.330-0.700            |

| LVDSEXT_25   | 2.5                     | N/A                    | N/A                    | 0.330-0.700            |

| BLVDS_25     | 2.5                     | N/A                    | N/A                    | 0.250-0.450            |

| ULVDS_25     | 2.5                     | N/A                    | N/A                    | 0.430-0.670            |

All of the user IOBs have fixed-clamp diodes to VCCO and to ground. These IOBs are not 5V tolerant.

## **Logic Resources**

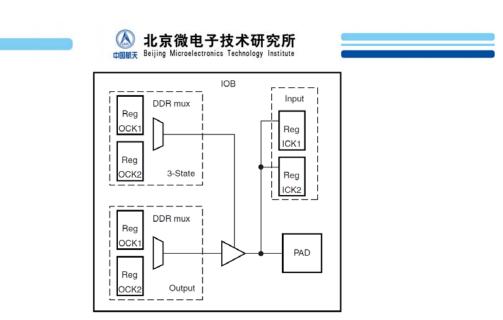

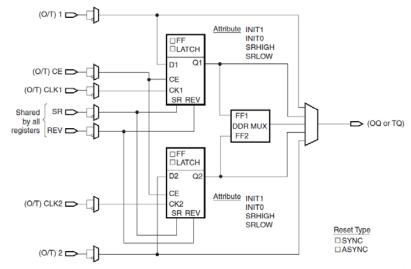

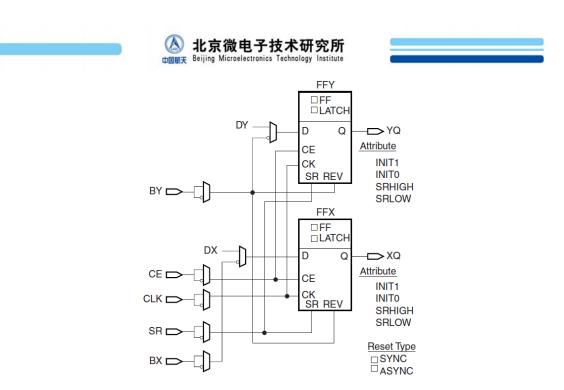

IOB blocks include six storage elements, as shown in Figure 3.Each storage element can be configured either as an edge-triggered D-type flip-flop or as a level-sensitive latch.On the input, output, and 3-state path, one or two DDR registers can be used.

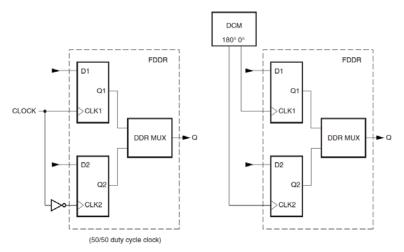

Double data rate is directly accomplished by the two registers on each path, clocked by the rising edges (or falling edges) from two different clock nets. The two clock signals are generated by the DCM and must be 180 degrees out of phase, as shown in Figure 4. There are two input, output, and 3-state data signals, each being alternately clocked out.

The DDR mechanism shown in Figure 4 can be used to mirror a copy of the clock on the output. This is useful for propagating a clock along the data that has an identical delay. It is also useful for multiple clock generation, where there is a unique clock driver for every clock load. BQR2V3000 can produce many copies of a clock with very little skew.

Each group of two registers has a clock enable signal (ICE for the input registers, OCE for the output registers, and TCE for the 3-state registers). The clock enable signals are active High by default. If left unconnected, the clock enable for that storage element defaults to the active state.

Each IOB block has common synchronous or asynchronous set and reset (SR and REV signals).SR forces the storage element into the state specified by the SRHIGH or SRLOW attribute. SRHIGH forces a logic"1". SRLOW forces a logic "0". When SR is used, a second input (REV) forces the storage element into the opposite state. The reset condition predominates over the set condition. The initial state after configuration or global initialization state is defined by a separate INIT0 and INIT1 attribute. By default, the SRLOW attribute forces INIT0, and the SRHIGH attribute forces INIT1.

For each storage element, the SRHIGH, SRLOW, INIT0, and INIT1 attributes are independent. Synchronous or asynchronous set/reset is consistent in an IOB block.All the control signals have independent polarities. Any inverter placed on a control input

is automatically absorbed.

Each register or latch (independent of all other registers or latches) (see Figure 5) can be configured as follows:

- No set or reset

- Synchronous set

- Synchronous reset

- Synchronous set and reset

- Asynchronous set (preset)

- Asynchronous reset (clear)

- Asynchronous set and reset (preset and clear)

The synchronous reset overrides a set, and an asynchronous clear overrides a preset.

Figure 4 Double Data Rate Registers

Figure 5 Register/Latch Configuration in an IOB Block

## **Input Path**

The BQR2V3000 IOB input path routes input signals directly to internal logic and/or through an optional input flip-flop or latch, or through the DDR input registers. An optional delay element at the D-input of the storage element eliminates pad-to-pad hold time. The delay is matched to the internal clock-distribution delay of the BQR2V3000 and when used, ensures that the pad-to-pad hold time is zero.Each input buffer can be configured to conform to any of the low-voltage signaling standards supported. In some of these standards the input buffer utilizes a user-supplied threshold voltage, VREF. The need to supply VREF imposes constraints on which standards can be used in the same bank.

## **Output Path**

The output path includes a 3-state output buffer that drives the output signal onto the pad. The output and/or the 3-state signal can be routed to the buffer directly from the internal logic or through an output/3-state flip-flop or latch, or through the DDR output/3-state registers.Each output driver can be individually programmed for a wide range of low-voltage signaling standards. In most signaling standards, the output High voltage depends on an externally supplied VCCO voltage. The need to supply VCCO imposes constraints on which standards can be used in the same bank.

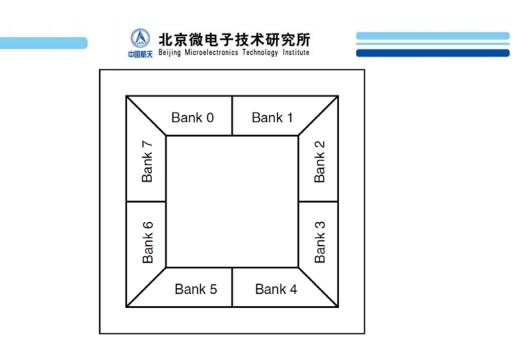

#### I/O Banking

Some of the I/O standards described above require VCCO and VREF voltages. These voltages are externally supplied and connected to device pins that serve groups of IOB blocks, called banks.Consequently, restrictions exist about which I/O standards can be combined within a given bank. Eight I/O banks result from dividing each edge of the FPGA into two banks, as shown in Figure 6. Each bank has multiple VCCO pins, all of which must be connected to the same voltage.This voltage is determined by the output standards in use.

Figure 6 BQR2V3000 I/O Banks: Top View for Wire-Bond Package

Some input standards require a user-supplied threshold voltage (VREF), and certain user-I/O pins are automatically configured as VREF inputs. Approximately one in six of the I/O pins in the bank assume this role.

VREF pins within a bank are interconnected internally, and consequently only one VREF voltage can be used within each bank. However, for correct operation, all VREF pins in the bank must be connected to the external reference voltage source.

#### **Rules for Combining I/O Standards in the Same Bank**

The following rules must be obeyed to combine different input, output, and bidirectional standards in the same bank:

## 1. Combining output standards only.

Output standards with the same output VCCO requirement can be combined in the same bank.

Compatible example:

SSTL2\_I and LVDS\_25\_DCI outputs

Incompatible example:

SSTL2\_I (output VCCO = 2.5V) and LVCMOS33 (output VCCO = 3.3V) outputs

## 2. Combining input standards only.

Input standards with the same input VCCO and input VREF requirements can be combined in the same bank.

Compatible example:

LVCMOS15 and HSTL\_IV inputs Incompatible example: LVCMOS15 (input VCCO = 1.5V) and LVCMOS18 (input VCCO = 1.8V) inputs Incompatible example: HSTL\_I\_DCI\_18 (VREF = 0.9V) and HSTL\_IV\_DCI\_18 (VREF = 1.1V) inputs

## 3. Combining input standards and output standards.

Input standards and output standards with the same input VCCO and output VCCO requirement can be combined in the same bank.

Compatible example:

LVDS\_25 output and HSTL\_I input

Incompatible example:

LVDS\_25 output (output VCCO = 2.5V) and

HSTL\_I\_DCI\_18 input (input VCCO = 1.8V)

## 4. Combining bidirectional standards with input or output standards.

When combining bidirectional I/O with other standards, make sure the bidirectional standard can meet rules 1 through 3 above.

## 5. Additional rules for combining DCI I/O standards.

a. No more than one Single Termination type (input or output) is allowed in the same bank.

Incompatible example:

HSTL\_IV\_DCI input and HSTL\_III\_DCI input

b. No more than one Split Termination type (input or output) is allowed in the same bank.

Incompatible example:

HSTL\_I\_DCI input and HSTL\_II\_DCI input

Table 3 summarizes all standards and voltage supplies.

Table 3 Summary of Voltage Supply Requirements to All Input and Output Standards

|  | I/O Standard | V <sub>CCO</sub> | V <sub>REF</sub> | <b>Termination</b> Type |  |

|--|--------------|------------------|------------------|-------------------------|--|

|--|--------------|------------------|------------------|-------------------------|--|

|                |        | <b>比京微电子技</b><br>ijing Microelectronics Te | 术研究所<br>chnology Institute |        |       |

|----------------|--------|--------------------------------------------|----------------------------|--------|-------|

|                | Output | Input                                      | Input                      | Output | Input |

| LVDS_33        |        |                                            | N/R <sup>(1)</sup>         | N/R    | N/R   |

| LVDSEXT_33     |        |                                            | N/R                        | N/R    | N/R   |

| LVPECL_33      |        |                                            | N/R                        | N/R    | N/R   |

| SSTL3_I        |        | N/R                                        | 1.5                        | N/R    | N/R   |

| SSTL3_II       |        |                                            | 1.5                        | N/R    | N/R   |

| AGP            |        |                                            | 1.32                       | N/R    | N/R   |

| LVTTL          |        |                                            | N/R                        | N/R    | N/R   |

| LVCMOS33       |        |                                            | N/R                        | N/R    | N/R   |

| LVDCI_33       | 3.3    |                                            | N/R                        | Series | N/R   |

| LVDCI_DV2_33   |        |                                            | N/R                        | Series | N/R   |

| PCI33_3        |        |                                            | N/R                        | N/R    | N/R   |

| PCI66_3        |        | 3.3                                        | N/R                        | N/R    | N/R   |

| PCIX           |        |                                            | N/R                        | N/R    | N/R   |

| LVDS_33_DCI    |        |                                            | N/R                        | N/R    | Split |

| LVDSEXT_33_DCI |        |                                            | N/R                        | N/R    | Split |

| SSTL3_I_DCI    |        |                                            | 1.5                        | N/R    | Split |

| SSTL3_II_DCI   |        |                                            | 1.5                        | Split  | Split |

| LVDS_25        |        |                                            | N/R                        | N/R    | N/R   |

| LVDSEXT_25     |        |                                            | N/R                        | N/R    | N/R   |

| LDT_25         |        |                                            | N/R                        | N/R    | N/R   |

| ULVDS_25       |        | N/R                                        | N/R                        | N/R    | N/R   |

| BLVDS_25       |        |                                            | N/R                        | N/R    | N/R   |

| SSTL2_I        |        |                                            | 1.25                       | N/R    | N/R   |

| SSTL2_II       | 2.5    |                                            | 1.25                       | N/R    | N/R   |

| LVCMOS25       | 2.5    |                                            | N/R                        | N/R    | N/R   |

| LVDCI_25       |        |                                            | N/R                        | Series | N/R   |

| LVDCI_DV2_25   |        |                                            | N/R                        | Series | N/R   |

| LVDS_25_DCI    |        | 2.5                                        | N/R                        | N/R    | Split |

| LVDSEXT_25_DCI |        |                                            | N/R                        | N/R    | Split |

| SSTL2_I_DCI    |        |                                            | 1.25                       | N/R    | Split |

| SSTL2_II_DCI   |        |                                            | 1.25                       | Split  | Split |

| HSTL_III_18    | 1.0    | <b>▶</b> ⊺/₽                               | 1.1                        | N/R    | N/R   |

| HSTL_IV_18     | 1.8    | N/R                                        | 1.1                        | N/R    | N/R   |

| 中国航天 Beijing Microelectronics T |        |               | chhorogy institute | 2       |           |

|---------------------------------|--------|---------------|--------------------|---------|-----------|

| I/O Standard                    | Vc     | co            | V <sub>REF</sub>   | Termina | tion Type |

| 1/O Standaru                    | Output | Input         | Input              | Output  | Input     |

| HSTL_I_18                       |        |               | 0.9                | N/R     | N/R       |

| HSTL_II_18                      |        |               | 0.9                | N/R     | N/R       |

| SSTL18_I                        |        |               | 0.9                | N/R     | N/R       |

| SSTL18_II                       |        |               | 0.9                | N/R     | N/R       |

| LVCMOS18                        |        |               | N/R                | N/R     | N/R       |

| LVDCI_18                        |        |               | N/R                | Series  | N/R       |

| LVDCI_DV2_18                    |        |               | N/R                | Series  | N/R       |

| HSTL_III_DCI_18                 |        |               | 1.1                | N/R     | Single    |

| HSTL_IV_DCI_18                  |        | 1.8           | 1.1                | Single  | Single    |

| HSTL_I_DCI_18                   |        |               | 0.9                | N/R     | Split     |

| HSTL_II_DCI_18                  |        |               | 0.9                | Split   | Split     |

| SSTL18_I_DCI                    |        |               | 0.9                | N/R     | Split     |

| SSTL18_II_DCI                   |        |               | 0.9                | Split   | Split     |

| HSTL_III                        |        |               | 0.9                | N/R     | N/R       |

| HSTL_IV                         |        | N/R           | 0.9                | N/R     | N/R       |

| HSTL_I                          |        | IN/K          | 0.75               | N/R     | N/R       |

| HSTL_II                         |        |               | 0.75               | N/R     | N/R       |

| LVCMOS15                        |        |               | N/R                | N/R     | N/R       |

| LVDCI_15                        | 1.5    |               | N/R                | Series  | N/R       |

| LVDCI_DV2_15                    | 1.5    |               | N/R                | Series  | N/R       |

| GTLP_DCI                        |        | 1.5           | 1                  | Single  | Single    |

| HSTL_III_DCI                    |        | 1.3           | 0.9                | N/R     | Single    |

| HSTL_IV_DCI                     |        |               | 0.9                | Single  | Single    |

| HSTL_I_DCI                      |        |               | 0.75               | N/R     | Split     |

| HSTL_II_DCI                     |        |               | 0.75               | Split   | Split     |

| GTL_DCI                         | 1.2    | 1.2           | 0.8                | Single  | Single    |

| GTLP                            | NI/D   | N/R           | 1                  | N/R     | N/R       |

| GTL                             | N/R    | 1 <b>N/ K</b> | 0.8                | N/R     | N/R       |

北京微电子技术研究所 Beijing Microelectronics Technology Institute

**Notes:** 1. N/R = no requirement.

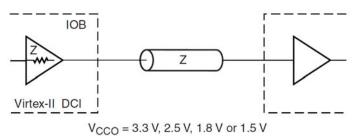

## **Digitally Controlled Impedance (DCI)**

Today's chip output signals with fast edge rates require termination to prevent

reflections and maintain signal integrity. High pin count packages (especially ball gridarrays) can not accommodate external termination resistors.

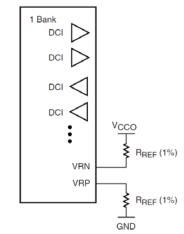

DCI provides controlled impedance drivers and on-chip termination for single-ended and differential I/Os. This eliminates the need for external resistors, and improves signal integrity. The DCI feature can be used on any IOB by selecting one of the DCI I/O standards. When applied to inputs, DCI provides input parallel termination. When applied to outputs, DCI provides controlled impedance drivers (series termination) or output parallel termination. DCI operates independently on each I/O bank. When a DCI I/O standard is used in a particular I/O bank, external reference resistors must be connected to two dual-function pins on the bank. These resistors, the voltage reference of the N transistor (VRN), and the voltage reference of the P transistor (VRP) are shown in Figure 7.

Figure 7 DCI in a BQR2V3000 Bank

When used with a terminated I/O standard, the value of resistors are specified by the standard (typically 50  $\Omega$ ). When used with a controlled impedance driver, the resistors set the output impedance of the driver within the specified range (25  $\Omega$  to 100  $\Omega$ ). For all series and parallel terminations listed in Table 4 and Table 5, the reference resistors must have the same value for any given bank. One percent resistors are recommended. The DCI system adjusts the I/O impedance to match the two external reference resistors or half of the reference resistors, and compensates for impedance changes due to voltage and/or temperature fluctuations. The adjustment is done by turning parallel transistors in the IOB on or off.

Table 4 SelectI/O-Ultra Controlled Impedance Buffers

| V <sub>CCO</sub> | DCI      | DCI Half Impedance |

|------------------|----------|--------------------|

| 3.3V             | LVDCI_33 | LVDCI_DV2_33       |

| 2.5V             | LVDCI_25 | LVDCI_DV2_25       |

| 1.8V | LVDCI_18 | LVDCI_DV2_18 |

|------|----------|--------------|

| 1.5V | LVDCI_15 | LVDCI_DV2_15 |

## **Controlled Impedance Drives(Series Termination)**

DCI can be used to provide a buffer with a controlled output impedance. It is desirable for this output impedance to match the transmission line impedance (Z). BQR2V3000 input buffers also support LVDCI and LVDCI\_DV2 I/O standards.

Figure 8 Internal Series Termination

### **Controlled Impedance Drives(Parallel Termination)**

DCI also provides on-chip termination for SSTL3, SSTL2,HSTL (Class I, II, III, or IV), and GTL/GTLP receivers or transmitters on bidirectional lines.

Table 5 lists the on-chip parallel terminations available in BQR2V3000. VCCO must be set according to Table 6.Note that there is a VCCO requirement for GTL\_DCI and GTLP\_DCI, due to the on-chip termination resistor.

| I/O Standard   | External<br>Termination | On-Chip Termination |

|----------------|-------------------------|---------------------|

| SSTL3 Class I  | SSTL3_I                 | SSTL3_I_DCI (1)     |

| SSTL3 Class II | SSTL3_II                | SSTL3_II_DCI (1)    |

| SSTL2 Class I  | SSTL2_I                 | SSTL2_I_DCI (1)     |

| SSTL2 Class II | SSTL2_II                | SSTL2_II_DCI (1)    |

| HSTL Class I   | HSTL_I                  | HSTL_I_DC           |

| HSTL Class II  | HSTL_II                 | HSTL_II_DC          |

| HSTL Class III | HSTL_III                | HSTL_III_DC         |

| HSTL Class IV  | HSTL_IV                 | HSTL_IV_DC          |

| GTL            | GTL                     | GTL_DC              |

| GTLP           | GTLP                    | GTLP_DC             |

Table 5 SelectI/O-Ultra Controlled Impedance Buffers

| I/O Standard                | Output VCCO | Input VCCO         | Input VREF | Termination<br>Type |

|-----------------------------|-------------|--------------------|------------|---------------------|

| LVDCI_33 <sup>(1)</sup>     | 3.3         | 3.3                | N/A        | Series              |

| LVDCI_DV2_33 <sup>(1)</sup> | 3.3         | 3.3                | N/A        | Series              |

| LVDCI_25 <sup>(1)</sup>     | 2.5         | 2.5                | N/A        | Series              |

| LVDCI_DV2_25 <sup>(1)</sup> | 2.5         | 2.5                | N/A        | Series              |

| LVDCI_18 <sup>(1)</sup>     | 1.8         | 1.8                | N/A        | Series              |

| LVDCI_DV2_18 <sup>(1)</sup> | 1.8         | 1.8                | N/A        | Series              |

| LVDCI_15 <sup>(1)</sup>     | 1.5         | 1.5                | N/A        | Series              |

| LVDCI_DV2_15 <sup>(1)</sup> | 1.5         | 1.5                | N/A        | Series              |

| GTL_DCI                     | 1.2         | 1.2                | 0.8        | Single              |

| GTLP_DCI                    | 1.5         | 1.5                | 1.0        | Single              |

| HSTL_I_DCI                  | 1.5         | 1.5 1.5 0.75 Split |            | Split               |

| HSTL_II_DCI                 | 1.5         | 1.5 0.75 Spl       |            | Split               |

| HSTL_III_DCI                | 1.5         | 1.5                | 0.9 Single |                     |

| HSTL_IV_DCI                 | 1.5         | 1.5                | 0.9        | Single              |

| HSTL_I_DCI                  | 1.8         | N/A                | 0.9        | Split               |

| HSTL_II_DCI                 | 1.8         | N/A                | 0.9        | Split               |

| HSTL_III_DCI                | 1.8         | N/A                | 1.1        | Single              |

| HSTL_IV_DCI                 | 1.8         | N/A                | 1.1        | Single              |

| SSTL2_I_DCI <sup>(2)</sup>  | 2.5         | 2.5                | 1.25       | Split               |

| SSTL2_II_DCI <sup>(2)</sup> | 2.5         | 2.5                | 1.25       | Split               |

| SSTL3_I_DCI <sup>(2)</sup>  | 3.3         | 3.3                | 1.5        | Split               |

| SSTL3_II_DCI <sup>(2)</sup> | 3.3         | 3.3                | 1.5        | Split               |

### Table 6 Supported DCI I/O Standards

Notes:

1. LVDCI\_XX and LVDCI\_DV2\_XX are LVCMOS controlled impedance buffers, matching the reference resistors or half of the reference resistors.

2. These are SSTL compatible.

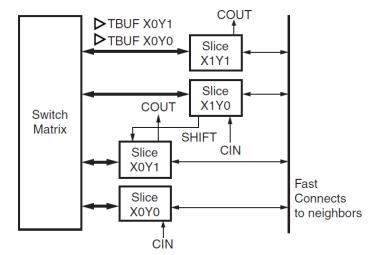

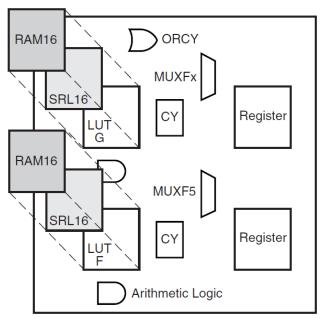

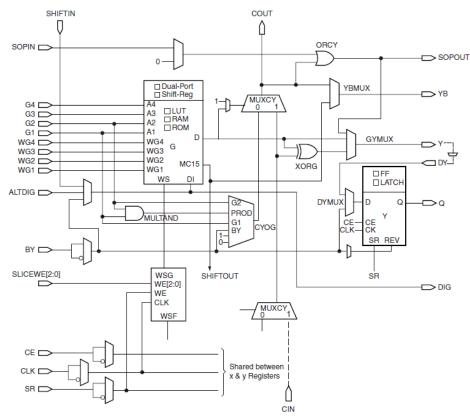

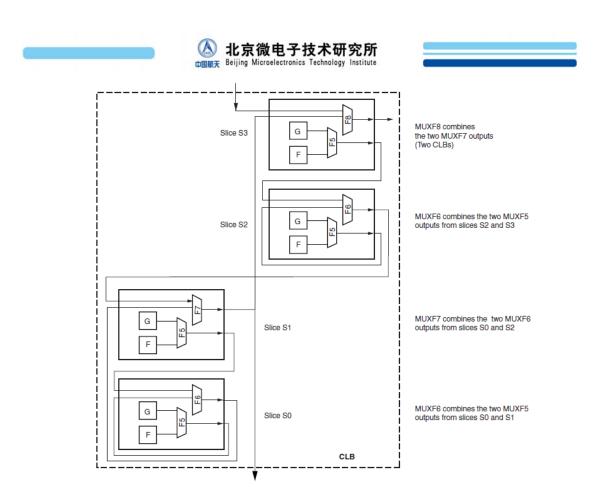

## 3.2.2 Configurable Logic Blocks (CLBs)

BQR2V3000 configurable logic blocks (CLB) are organized in an array and are used to build combinatorial and synchronous logic designs. Each CLB element is tied

to a switch matrix to access the general routing matrix, as shown Figure 9.A CLB element comprises four similar slices with fast local feedback within the CLB. The four slices are split into two columns of two slices with two independent carry logic chains and one common shift chain.

Figure 9 BQR2V3000 CLB Element

## **Slice Description**

Each slice includes two 4-input function generators, carry logic, arithmetic logic gates, wide function multiplexers and two storage elements. As shown in Figure 10, each 4-input function generator is programmable as a 4-input LUT, 16 bits of distributed SelectRAM memory, or a 16-bit variable-tap shift register element.

The output from the function generator in each slice drives both the slice output

and the D input of the storage element. Figure 11 shows a more detailed view of a single slice.

## Look-Up Table

BQR2V3000 function generators are implemented as 4-input look-up tables (LUTs). Four independent inputs are provided to each of the two function generators in a slice (F and G). These function generators are each capable of implementing any arbitrarily defined Boolean function of four inputs. The propagation delay is therefore independent of the function implemented. Signals from the function generators can exit the slice (X or Y output), can input the XOR dedicated gate (see arithmetic logic), or input the carry-logic multiplexer (see fast look-ahead carry logic), or feed the D input of the storage element, or go to the MUXF5 (not shown in Figure 11). In addition to the basic LUTs, the BQR2V3000 slice contains logic (MUXF5 and MUXFX multiplexers) that combines function generators to provide any function of five, six, seven, or eight inputs. The MUXFXs are either MUXF6,MUXF7, or MUXF8 according to the slice considered in the CLB. Selected functions up to nine inputs (MUXF6, MUXF7, or MUXF8 multiplexer to map any functions of six, seven, or eight inputs and selected wide logic functions.

## **Register/Latch**

The storage elements in a BQR2V3000 slice can be configured as either edge-triggered D-type flip-flops or level-sensitive latches. The D input can be directly driven by the X or Y output via the DX or DY input, or by the slice inputs bypassing the function generators via the BX or BY input. The clock enable signal (CE) is active High by default. If left unconnected, the clock enable for that storage element defaults to the active state. In addition to clock (CK) and clock enable (CE) signals, each slice has set and reset signals (SR and BY slice inputs). SR forces the storage element into the state specified by the attribute SRHIGH or SRLOW.SRHIGH forces a logic "1" when SR is asserted. SRLOW forces a logic "0". When SR is used, a second input (BY) forces the storage element into the opposite state. The reset conditionis predominant over the set condition (Figure 12).The initial state after configuration or global initial state is defined by a separate INIT0 and INIT1 attribute. By default, setting the SRLOW attribute sets INIT0, and setting the SRHIGH attribute sets INIT1.

For each slice, set and reset can be set to be synchronous or asynchronous. BQR2V3000 also have the ability to set INIT0 and INIT1 independent of SRHIGH and SRLOW.Control signals CLK,CE, and SR are common to both storage elements in one slice. All control signals have independent polarities. Any inverter placed on a control input is automatically absorbed.The set and reset functionality of a register or a latch can be configured as follows:

- No set or reset

- Synchronous set

- Synchronous reset

- Synchronous set and reset

- Asynchronous set (preset)

- Asynchronous reset (clear)

- Asynchronous set and reset (preset and clear)

The synchronous reset has precedence over a set, and an asynchronous clear has precedence over a preset.

Figure 11 BQR2V3000 Slice(Top Half)

Figure 12 Register/Latch Configuration in a Slice

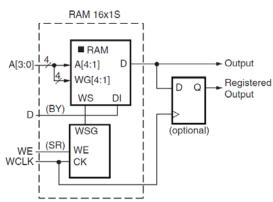

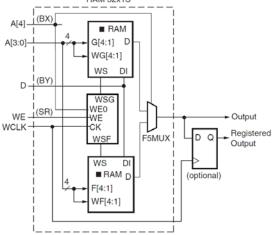

### **Distributed SelectRAM Memory**

Each function generator (LUT) can implement a 16 x 1-bit synchronous RAM resource called a distributed SelectRAM element. The SelectRAM elements are configurable within a CLB to implement the following:

- Single-Port 16 x 8 bit RAM

- Single-Port 32 x 4 bit RAM

- Single-Port 64 x 2 bit RAM

- Single-Port 128 x 1 bit RAM

- Dual-Port 16 x 4 bit RAM

- Dual-Port 32 x 2 bit RAM

- Dual-Port 64 x 1 bit RAM

Distributed SelectRAM memory modules are synchronous(write) resources. The combinatorial read access time is extremely fast, while the synchronous write simplifies high-speed designs. A synchronous read can be implemented with a storage element in the same slice. The distributed SelectRAM memory and the storage element share the same clock input. A Write Enable (WE) input is active High, and is driven by the SR input.Table 7 shows the number of LUTs (2 per slice) occupied by each distributed SelectRAM configuration.

Table 7 Distributed SelectRAM Configurations

#### T微电子技术研究所 Microelectronics Technology Institute

| RAM    | Number |

|--------|--------|

| 16 x1S | 1      |

| 16 x1D | 2      |

| 32x1S  | 2      |

| 32x1D  | 4      |

| 64x1S  | 4      |

| 64x1D  | 8      |

| 128x1S | 8      |

Notes:

1. S = single-port configuration, and D = dual-port configuration.

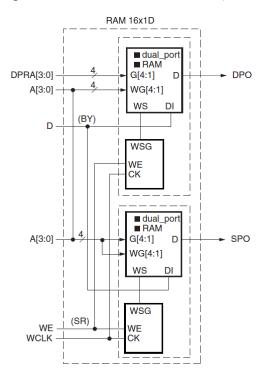

For single-port configurations, distributed SelectRAM memory has one address port for synchronous writes and asynchronous reads.For dual-port configurations, distributed SelectRAM memory has one port for synchronous writes and asynchronous reads and another port for asynchronous reads. The function generator (LUT) has separated read address inputs (A1, A2, A3, A4) and write address inputs (WG1/WF1, WG2/WF2, WG3/WF3, WG4/WF4).In single-port mode, read and write addresses share the same address bus. In dual-port mode, one function generator (R/W port) is connected with shared read and write addresses. The second function generator has the A inputs (read) connected to the second read-only port address and the W inputs (write) shared with the first read/write port address.Figure 13,Figure 14, and Figure 15 illustrate various example configurations

Figure 13 Distributed SelectRAM (RAM16x1S)

Figure 14 Single-Port Distributed SelectRAM(RAM32x1S)

Figure 15 Dual-Port Distributed SelectRAM(RAM16x1D)

Similar to the RAM configuration, each function generator(LUT) can implement a 16 x 1-bit ROM. Five configurations are available: ROM16x1, ROM32x1, ROM64x1,ROM128x1, and ROM256x1. The ROM elements are cascadable to implement wider or/and deeper ROM.ROM contents are loaded at configuration. Table 8 shows the number of LUTs occupied by each configuration.

| Table 8 ROM | Configuration |

|-------------|---------------|

|-------------|---------------|

| ROM   | Number of LUTs |

|-------|----------------|

| 16 x1 | 1              |

| 32x1   | 2        |

|--------|----------|

| 64x1   | 4        |

| 128x1  | 8(1CLB)  |

| 256 x1 | 16(2CLB) |

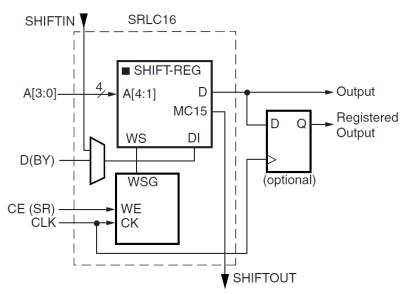

## **Shift Registers**

Each function generator can also be configured as a 16-bit shift register. The write operation is synchronous with a clock input (CLK) and an optional clock enable, as shown in Figure 16. A dynamic read access is performed through the 4-bit address bus, A[3:0]. The configurable 16-bit shift register cannot be set or reset. The read is asynchronous,however, the storage element or flip-flop is available to implement a synchronous read. The storage element should always be used with a constant address. For example, when building an 8-bit shift register and configuring the addresses to point to the seventh bit, the eighth bit can be the flip-flop. The overall system performance is improved by using the superior clock-to-out of the flip-flops.

Figure 16 Shift Register Configurations

An additional dedicated connection between shift registers allows connecting the last bit of one shift register to the first bit of the next, without using the ordinary LUT output .Longer shift registers can be built with dynamic access to any bit in the chain. The shift register chaining and the MUXF5, MUXF6, and MUXF7 multiplexers allow up to a 128-bit shift register with addressable access to be implemented in one CLB.

## **Multiplexers**

BQR2V3000 function generators and associated multiplexers can implement the following:

- 4:1 multiplexer in one slice

- 8:1 multiplexer in two slices

- 16:1 multiplexer in one CLB element (4 slices)

- 32:1 multiplexer in two CLB elements (8 slices)

Each slice has one MUXF5 multiplexer and one MUXFX multiplexer. The MUXFX multiplexer implements the MUXF6, MUXF7, or MUXF8, as shown in Figure 17.Each CLB element has two MUXF6 multiplexers, one MUXF7 multiplexer and one MUXF8 multiplexer. Any LUT can implement a 2:1 multiplexer.

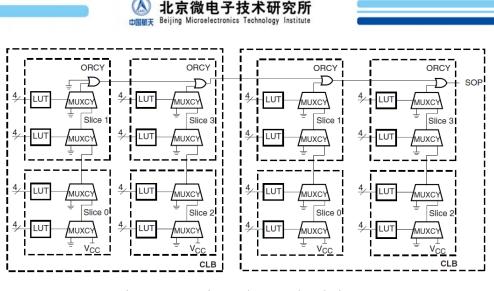

## Fast Lookahead Carry Logic

Dedicated carry logic provides fast arithmetic addition and subtraction. The BQR2V3000 CLB has two separate carry chains. The height of the carry chains is two bits per slice. The carry chain in the BQR2V3000 is running upward. The dedicated carry path and carry multiplexer (MUXCY) can also be used to cascade function generators for implementing wide logic functions.

## **Arithmetic Logic**

The arithmetic logic includes an XOR gate that allows a 2-bit full adder to be implemented within a slice. In addition, a dedicated AND (MULT\_AND) gate (shown in Figure 11)improves the efficiency of multiplier implementation.

Figure 17 MUXF5 and MUXFX multiplexers

## **Sum of Products**

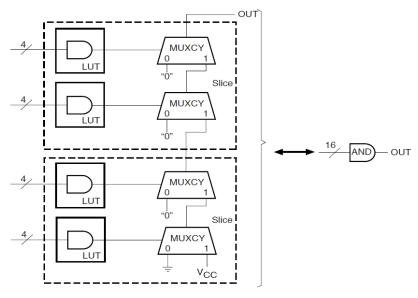

Each slice has a dedicated OR gate named ORCY,ORing together outputs from the slices carryout and the ORCY from an adjacent slice. The ORCY gate with the dedicated Sum of Products (SOP) chain are designed for implementing large, flexible SOP chains. One input of each ORCY is connected through the fast SOP chain to the output of the previous ORCY in the same slice row. The second input is connected to the output of the top MUXCY in the same slice, as shown in Figure 18.LUTs and MUXCYs can implement large AND gates or other combinatorial logic functions. Figure 19 illustrates LUT and MUXCY resources configured as a 16-input AND gate.

#### Figure 18 Horizontal Cascade Chain

Figure 19 Wide-Input AND Gate(16Inputs)

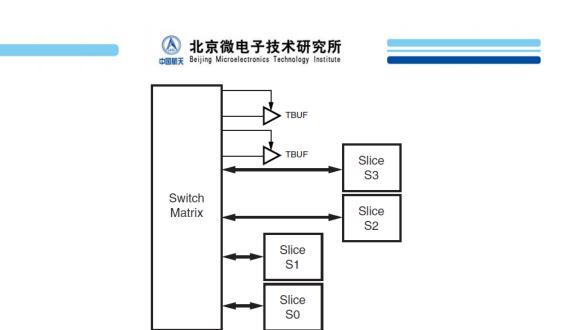

## **3-State Buffers**

Each CLB contains two 3-state drivers (TBUFs) that can drive on-chip buses. Each 3-state buffer has its own 3-state control pin and its own input pin.Each of the four slices have access to the two 3-state buffers through the switch matrix, as shown in Figure 20.TBUFs in neighboring CLBs can access slice outputs by direct connects. The outputs of the 3-state buffers drive horizontal routing resources used to implement 3-state buses.

Figure 20 BQR2V3000 3-State Buffers

Four horizontal routing resources per CLB are provided for on-chip 3-state buses. Each 3-state buffer has access alternately to two horizontal lines, which can be partitioned as shown in Figure 21. The switch matrices corresponding to SelectRAM memory and multiplier or I/O blocks are skipped.Table 9 shows the number of 3-state buffers available in BQR2V3000.

Table 9 BQR2V3000 3-StateBuffers

| Device    | 3-State Buffers per Row | Total Number of 3-State Buffers |

|-----------|-------------------------|---------------------------------|

| BQR2V3000 | 112                     | 7,168                           |

Figure 21 3-State Buffer Connection to Horizontal Lines

Table 10 summarizes the logic resources in one CLB. All of the CLBs are identical and each CLB or slice can be implemented in one of the configurations listed. Table 11 shows the available resources in all CLBs.

Table 10 Logic Resources in One CLB

| Slices | LUTs | Flip-Flops | MULT_ANDs | Arithmetic   | SOP    | Distributed | Shift     | TBUF |

|--------|------|------------|-----------|--------------|--------|-------------|-----------|------|

|        |      |            |           | &CarryChains | Chains | SelectRAM   | Registers |      |

| 4      | 8    | 8          | 8         | 2            | 2      | 128bits     | 128bits   | 2    |

Table 11 BQR2V3000 Logic Resource Available In All CLBs

| Device    | CLB<br>Array:<br>Row x<br>Column | Number<br>of Slices | Number of<br>LUTs | Max Distributed<br>SelectRAM or<br>Shift Register<br>(bits) | Number<br>of<br>Flip-Flops | Number of<br>Carry<br>Chains <sup>(1)</sup> | Number<br>of<br>SOP<br>Chains <sup>(1)</sup> |

|-----------|----------------------------------|---------------------|-------------------|-------------------------------------------------------------|----------------------------|---------------------------------------------|----------------------------------------------|

| BQR2V3000 | 64 x 56                          | 14,336              | 28,672            | 458,752                                                     | 28,672                     | 112                                         | 128                                          |

Notes:

1. The carry chains and SOP chains can be split or cascaded.

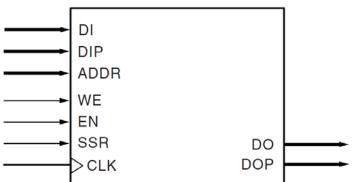

## 3.2.3 Block SelectRAM Memory

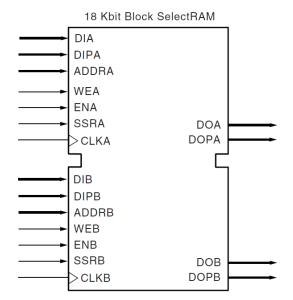

BQR2V3000 incorporate large amounts of 18 Kbit block SelectRAM. These complement the distributed SelectRAM resources that provide shallow RAM structures implemented in CLBs. Each BQR2V3000 block SelectRAM is an 18 Kbit true dual-port RAM with two independently clocked and independently controlled synchronous ports that access a common storage area. Both ports are functionally identical. CLK, EN, WE, and SSR polarities are defined through configuration.Each port has the following types of inputs: Clock and Clock Enable, Write Enable, Set/Reset, and Address, as well as separate Data/parity data inputs (for writes) and Data/parity data outputs (for reads). Operation is synchronous. The block SelectRAM behaves like a register. Control, address, and data inputs must (and need only) be valid during the set-up time window prior to a rising (or falling, a configuration option) clock edge. Data outputs change as a result of the same clock edge.

The BQR2V3000 block SelectRAM supports various configurations, including single- and dual-port RAM and various data/address aspect ratios. Supported memory configurations for single- and dual-port modes are shown in Table 12

| 16Kx1 bit | 2Kx9bits  |

|-----------|-----------|

| 8Kx2bits  | 1Kx18bits |

Table 12 Dual- and Single-Port Configurations

## **Single-Port Configuration**

As a single-port RAM, the block SelectRAM has access to the 18 Kbit memory locations in any of the 2K x 9-bit, 1K x 18-bit, or 512 x 36-bit configurations and to 16 Kbit memory locations in any of the 16K x 1-bit, 8K x 2-bit, or 4K x 4-bit configurations. The advantage of 9-bit, 18-bit, and 36-bit widths is the ability to store a parity bit for everyeight bits. Parity bits must be generated or checked externally in user logic. In such cases, the width is viewed as 8 + 1, 16 + 2, or 32 + 4. These extra parity bits are stored and behave exactly as the other bits, including the timing parameters. Video applications can use the 9-bit ratio of BQR2V3000 block SelectRAM memory to advantage.

Each block SelectRAM cell is a fully synchronous memory, as illustrated in Figure 22. Input data bus and output data bus widths are identical.

18 Kbit Block SelectRAM

Figure 22 18 Kbit Block SelectRAM Memory in Single-Port Mode

## **Dual-Port Configuration**

As a dual-port RAM, each port of block SelectRAM has access to a common 18 Kbit memory resource. These are fully synchronous ports with independent control signals for each port. The data widths of the two ports can be configured independently, providing built-in bus-width conversion. If both ports are configured in either 2K x 9-bit, 1K x 18-bit, or 512 x 36-bit configurations, the 18 Kbit block is accessible from Port A or B. If both ports are configured in either 16K x 1-bit, 8K x 2-bit, or 4K x 4-bit configurations, the 16 Kbit block is accessible from Port A or Port B. All other configurations result in one port having access to an 18 Kbit memory block and the other port having access to a 16 Kbit subset of the memory block equal

\_\_\_\_\_

to 16 Kbits. Each block SelectRAM cell is a fully synchronous memory, as illustrated in Figure 23. The two ports have independent inputs and outputs and are independently clocked.

Figure 23 18 Kbit Block SelectRAM in Dual-Port Mode

## **Port Aspect Ratios**

Table 13 shows the depth and the width aspect ratios for the 18 Kbit block SelectRAM. BQR2V3000 block SelectRAM also includes dedicated routing resources to provide an efficient interface with CLBs, block SelectRAM, and multipliers.

| Width | Depth  | Address Bus | Data Bus   | Parity Bus  |

|-------|--------|-------------|------------|-------------|

| 1     | 16,384 | ADDR[13:0]  | DATA[0]    | N/A         |

| 2     | 8,192  | ADDR[12:0]  | DATA[1:0]  | N/A         |

| 4     | 4,096  | ADDR[11:0]  | DATA[3:0]  | N/A         |

| 9     | 2,048  | ADDR[10:0]  | DATA[70]   | Parity[0]   |

| 18    | 1,024  | ADDR[9:0]   | DATA[15:0] | Parity[1:0] |

| 36    | 512    | ADDR[8:0]   | DATA[31:0] | Parity[3:0] |

Table 13 18Kbit Block SelectRAM Port Aspect Ratio

## **Read/Write Operations**

The BQR2V3000 block SelectRAM read operation is fully synchronous. An address is presented, and the read operation is enabled by control signals WEA and WEB in addition to ENA or ENB. Then, depending on clock polarity, a rising or

falling clock edge causes the stored data to be loaded into output registers. The write operation is also fully synchronous. Data and address are presented, and the write operation is enabled by control signals WEA or WEB in addition to ENA or ENB. Then, again depending on the clock input mode, a rising or falling clock edge causes the data to be loaded into the memory cell addressed. A write operation performs a simultaneous read operation. Three different options are available, selected by configuration:

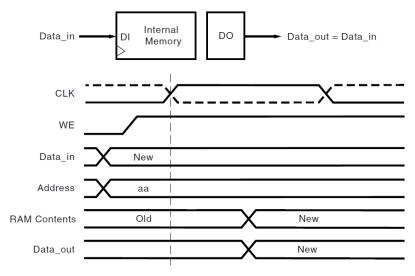

### 1. WRITE\_FIRST

The WRITE\_FIRST option is a transparent mode. The same clock edge that writes the data input (DI) into the memory also transfers DI into the output registers DO as shown in Figure 24.

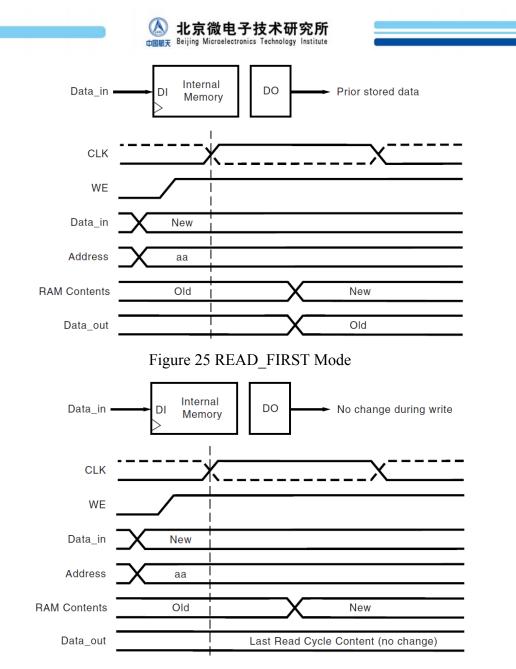

### 2. READ\_FIRST

The READ\_FIRST option is a read-before-write mode. The same clock edge that writes data input (DI) into the memory also transfers the prior content of the memory cell addressed into the data output registers DO, as shown in Figure 25

### 3. NO\_CHANGE

The NO\_CHANGE option maintains the content of the output registers, regardless of the write operation. The clock edge during the write mode has no effect on the content of the data output register DO. When the port is configured as NO\_CHANGE, only a read operation loads a new value in the output register DO, as shown in Figure 26.

Figure 24 WRITE\_FIRST Mode

Figure 26 NO\_CHANGE Mode

## **Control Pins and Attributes**

BQR2V3000 SelectRAM memory has two independent ports with the control signals described in Table 14. All control inputs including the clock have an optional inversion.

| Control Signal | Function                               |

|----------------|----------------------------------------|

| CLK            | Read and Write Clock                   |

| EN             | Enable affects Read, Write, Set, Reset |

| WE             | Write Enable                           |

Table 14 Control Functions

|                        | は国際天日の | と京微电子技术研究所                           |  |

|------------------------|--------|--------------------------------------|--|

| SSR Set DO register to |        | Set DO register to SRVAL (attribute) |  |

Initial memory content is determined by the INIT\_xx attributes. Separate attributes determine the output register value after device configuration (INIT) and SSR is asserted(SRVAL). Both attributes (INIT\_B and SRVAL) are available for each port when a block SelectRAM resource is configured as dual-port RAM.

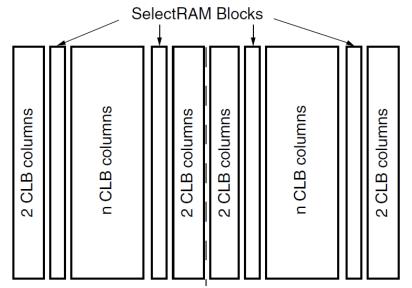

BQR2V3000 SelectRAM memory blocks are located in six columns. Column locations are shown in Table 15.

| Device    | Columna | SelectRAM Blocks |       |

|-----------|---------|------------------|-------|

| Device    | Columns | Per Column       | Total |

| BQR2V3000 | 6       | 16               | 96    |

Table 15 SelectRAM Memory Floor Plan

Table 16 shows the amount of block SelectRAM memory available for BQR2V3000. The 18 Kbit SelectRAM blocks are cascadable to implement deeper or wider single- or dual-port memory resources.

Table 16 BQR2V3000 SelectRAM Memory Available

| Dorrigo   | Total SelectRAM Memory |          |           |

|-----------|------------------------|----------|-----------|

| Device    | Blocks                 | in Kbits | in Bits   |

| BQR2V3000 | 96                     | 1,728    | 1,769,472 |

Figure 27 Block SelectRAM(4-column)

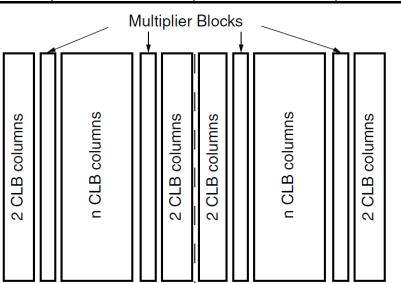

## 3.2.4 18-Bit×18-Bit Multipliers

A BQR2V3000 multiplier block is an 18-bit by 18-bit 2's complement signed

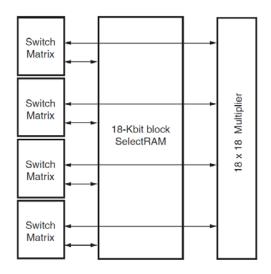

multiplier. BQR2V3000 incorporate many embedded multiplier blocks. These multipliers can be associated with an 18 Kbit block SelectRAM resource or can be used independently. They are optimized for high-speed operations and have a lower power consumption compared to an 18-bit×18-bit multiplier in slices. Each SelectRAM memory and multiplier block is tied to four switch matrices, as shown in Figure 28.

Figure 28 18-Bit×18-Bit Multipliers

The interconnect is designed to allow SelectRAM memory and multiplier blocks to be used at the same time, but some interconnect is shared between the SelectRAM and the multiplier. Thus, SelectRAM memory can be used only up to 18 bits wide when the multiplier is used, because the multiplier shares inputs with the upper data bits of the SelectRAM memory.

This sharing of the interconnect is optimized for an 18-bit-wide block SelectRAM resource feeding the multiplier. The use of SelectRAM memory and the multiplier with an accumulator in LUTs allows for implementation of a digital signal processor (DSP) multiplier-accumulator (MAC) function, which is commonly used in finite and infinite impulse response (FIR and IIR) digital filters.

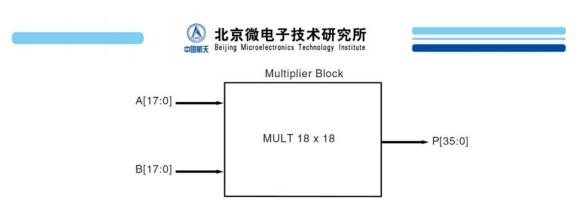

The multiplier block is an 18-bit by 18-bit signed multiplier (2's complement). Both A and B are 18-bit-wide inputs, and the output is 36 bits.Figure 29 shows a multiplier block.

Figure 29 Multiplier Block

Multiplier organization is identical to the 18 Kbit SelectRAM organization, because each multiplier is associated with an 18 Kbit block SelectRAM resource.

In addition to the built-in multiplier blocks, the CLB elements have dedicated logic to implement efficient multipliers in logic.

| Table 17 Multiplier Floor Plan |  |  |

|--------------------------------|--|--|

|--------------------------------|--|--|

| Device    | Columns | Multipliers |       |  |

|-----------|---------|-------------|-------|--|

| Device    | Columns | Per Column  | Total |  |

| BQR2V3000 | 6       | 16          | 96    |  |

Figure 30 Multipliers(4-column)

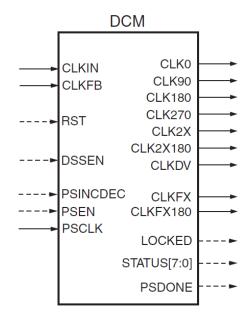

## **3.2.5** Digital Clock Manager (DCM)

The BQR2V3000 DCM offers a wide range of powerful clock management features:

• Clock De-skew: The DCM generates new system clocks (either internally or externally to the FPGA), which are phase-aligned to the input clock, thus eliminating clock distribution delays.

- Frequency Synthesis: The DCM generates a wide range of output clock frequencies, performing very flexible clock multiplication and division.

- Phase Shifting: The DCM provides both coarse phase shifting and fine-grained phase shifting with dynamic phase shift control.

The DCM utilizes fully digital delay lines allowing robust high-precision control of clock phase and frequency. It also utilizes fully digital feedback systems, operating dynamically to compensate for temperature and voltage variations during operation.

Up to four of the nine DCM clock outputs can drive inputs to global clock buffers or global clock multiplexer buffers simultaneously (see Figure 31). All DCM clock outputs can simultaneously drive general routing resources, including routes to output buffers.

Figure 31 Digital Clock Manager

The DCM can be configured to delay the completion of the BQR2V3000 configuration process until after the DCM has achieved lock. This guarantees that the chip does not begin operating until after the system clocks generated by the DCM have stabilized.

The DCM has the following general control signals:

- RST input pin: resets the entire DCM.

- LOCKED output pin: asserted High when all enabled DCM circuits have locked.

- STATUS output pins (active High): shown in Table 18.

Table 18 DCM Statue Pins

| Status Pin | Function             |

|------------|----------------------|

| 0          | Phase Shift Overflow |

#### ▲ 北京微电子技术研究所 Beijing Microelectronics Technology Institute

| 1 | CLKIN Stopped |  |

|---|---------------|--|

| 2 | CLKFX Stopped |  |

| 3 | N/A           |  |

| 4 | N/A           |  |

| 5 | N/A           |  |

| 6 | N/A           |  |

| 7 | N/A           |  |

#### **Clock De-Skew**

The DCM de-skews the output clocks relative to the input clock by automatically adjusting a digital delay line. Additional delay is introduced so that clock edges arrive at internal registers and block RAMs simultaneously with the clock edges arriving at the input clock pad. Alternatively, external clocks, which are also de-skewed relative to the input clock, can be generated for board-level routing. All DCM output clocks are phase-aligned to CLK0 and, therefore, are also phase-aligned to the input clock.

To achieve clock de-skew, the CLKFB input must be connected, and its source must be either CLK0 or CLK2X.CLKFB must always be connected, unless only the CLKFX or CLKFX180 outputs are used and de-skew is not required.

#### **Frequency Synthesis**

The DCM provides flexible methods for generating new clock frequencies. Each method has a different operating frequency range and different AC characteristics. The CLK2X and CLK2X180 outputs double the clock frequency. The CLKDV output creates divided output clocks with division options of 1.5, 2, 2.5, 3, 3.5, 4, 4.5, 5, 5.5, 6, 6.5, 7,7.5, 8, 9, 10, 11, 12, 13, 14, 15, and 16. The CLKFX and CLKFX180 outputs can be used to produce clocks at the following frequency:

#### FREQCLKFX = (M/D) \* FREQCLKIN

where M and D are two integers. By default, M=4 and D=1, which results in a clock output frequency four times faster than the clock input frequency(CLKIN).

CLK2X180 is phase shifted 180 degrees relative to CLK2X.CLKFX180 is phase shifted 180 degrees relative to CLKFX.All frequency synthesis outputs automatically have 50/50 duty cycles (with the exception of the CLKDV output whenperforming a non-integer divide in high-frequency mode).

Note: CLK2X and CLK2X180 are not available in high-frequencymode.

### **Phase Shifting**

The DCM provides additional control over clock skew through either coarse- or fine-grained phase shifting. The CLK0, CLK90, CLK180, and CLK270 outputs are each phase shifted by 1/4 of the input clock period relative to each other, providing coarse phase control.Note that CLK90 and CLK270 are not available in high-frequency mode.

Fine-phase adjustment affects all nine DCM output clocks. When activated, the phase shift between the rising edges of CLKIN and CLKFB is a specified fraction of the input clock period.

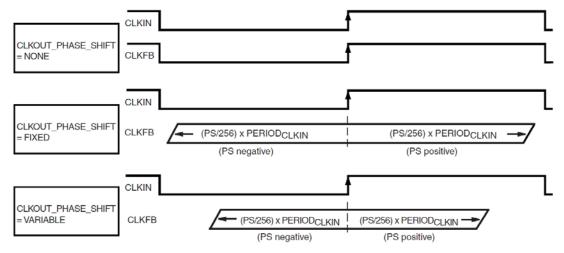

In variable mode, the PHASE SHIFT value can also be dynamically incremented or decremented as determined by PSINCDEC synchronously to PSCLK, when the PSEN input is active. Figure 32 illustrates the effects of fine-phase shifting.

Table 19 lists fine-phase shifting control pins, when used in variable mode.

| Control Pin | Direction | Function               |

|-------------|-----------|------------------------|

| PSINCDEC    | In        | Increment or decrement |

| PSEN        | In        | Enable±phase shift     |

| PSCLK       | In        | Clock for phase shift  |

| PSDONE      | Out       | Active when completed  |

Two separate components of the phase shift range must be understood:

• PHASE\_SHIFT attribute range

• FINE\_SHIFT\_RANGE DCM timing parameter range

The PHASE\_SHIFT attribute is the numerator in the following equation:

Phase Shift (ns) = (PHASE\_SHIFT/256) \* PERIODCLKIN

The full range of this attribute is always -255 to +255, but its practical range varies with CLKIN frequency, as constrained by the FINE\_SHIFT\_RANGE component, which represents the total delay achievable by the phase shift delay line. Total delay is a function of the number of delay taps used in the circuit.

Absolute range (fixed mode) = ± FINE\_SHIFT\_RANGE

Absolute range (variable mode) = ± FINE\_SHIFT\_RANGE/2

The reason for the difference between fixed and variable modes is as follows. For variable mode to allow symmetric,dynamic sweeps from -255/256 to +255/256, the DCM sets the "zero phase skew" point as the middle of the delay line,thus dividing the total delay line range in half. In fixed mode,since the PHASE\_SHIFT value never changes after configuration, the entire delay line is available for insertioninto either the CLKIN or CLKFB path (to create either positive or negative skew).

Taking both of these components into consideration, the following are some usage examples:

- If PERIODCLKIN = 2 \* FINE\_SHIFT\_RANGE, then PHASE\_SHIFT in fixed mode is limited to ± 128, and in variable mode it is limited to ± 64.

- If PERIODCLKIN = FINE\_SHIFT\_RANGE, then PHASE\_SHIFT in fixed mode is limited to ± 255, and in variable mode it is limited to ± 128.

- If PERIODCLKIN ≤ 0.5 \* FINE\_SHIFT\_RANGE, then PHASE\_SHIFT is limited to ± 255 in either mode.

## **Operating Modes**

The frequency ranges of DCM input and output clocks depend on the operating mode specified, either low-frequency mode or high-frequency mode, according to Table 20. The CLK2X, CLK2X180, CLK90, and CLK270 outputs are not available in high-frequency mode. High or low-frequency mode is selected by an attribute.

| Output Cleak   | Low-Frequency Mode |                   | High-Frequency Mode |                   |

|----------------|--------------------|-------------------|---------------------|-------------------|

| Output Clock   | <b>CLKIN Input</b> | CLK Output        | <b>CLKIN Input</b>  | CLK Output        |

| CLK0,CLK180    | CLKIN_FREQ_DLL_LF  | CLKOUT_FREQ_1X_LF | CLKIN_FREQ_DLL_HF   | CLKOUT_FREQ_1X_HF |

| CLK90,CLK270   | CLKIN_FREQ_DLL_LF  | CLKOUT_FREQ_1X_LF | NA                  | NA                |

| CLK2X,CLK2X180 | CLKIN_FREQ_DLL_LF  | CLKOUT_FREQ_2X_LF | NA                  | NA                |

Table 20 DCM Frequency Ranges

| Orteret Charle | Low-Frequency Mode |                   | High-Frequency Mode |                   |

|----------------|--------------------|-------------------|---------------------|-------------------|

| Output Clock   | CLKIN Input        | CLK Output        | CLKIN Input         | CLK Output        |

| CLKDV          | CLKIN_FREQ_DLL_LF  | CLKOUT_FREQ_DV_LF | CLKIN_FREQ_DLL_HF   | CLKOUT_FREQ_DV_HF |

| CLKFX,CLKFX180 | CLKIN_FREQ_FX_LF   | CLKOUT_FREQ_FX_LF | CLKIN_FREQ_FX_HF    | CLKOUT_FREQ_FX_HF |

BQR2V3000 DCMs are placed on the top and the bottom of each block RAM

and multiplier column. The number of DCMs as shown in Table 21.

| Table 21 Dewi Organization |         |      |  |  |

|----------------------------|---------|------|--|--|

| Device                     | Columns | DCMs |  |  |

| BQR2V3000                  | 6       | 12   |  |  |

#### Table 21 DCM Organization

## 3.2.6 .Global Clock Multiplexer Buffers

The DCM and global clock multiplexer buffers provide a complete solution for designing high-speed clocking schemes.

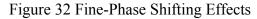

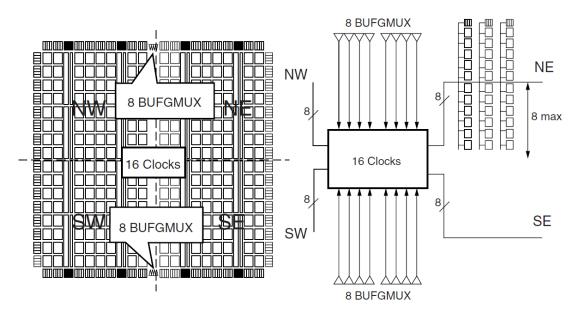

BQR2V3000 have 16 clock input pins that can also be used as regular user I/Os. Eight clock pads are on the top edge of the device, in the middle of the array, and eight are on the bottom edge, as illustrated in Figure 33.

#### Figure 33 BQR2V3000 Clock Pads

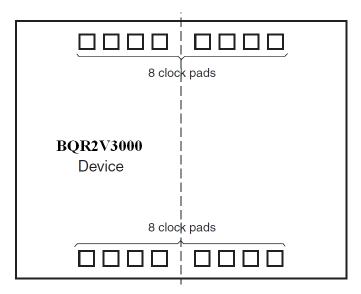

Each global clock buffer can be driven by either the clock pad to distribute a clock directly to the device, or the Digital Clock Manager (DCM). Each global clock buffer can also be driven by local interconnects. The DCM has clock output(s) that can be connected to global clock buffer inputs, as shown in Figure 34.

Figure 34 BQR2V3000 Clock Distribution Configurations

Global clock buffers are used to distribute the clock to some or all synchronous logic elements (such as registers in CLBs and IOBs, and SelectRAM blocks).Eight global clocks can be used in each quadrant of the BQR2V3000 device. Designers should consider the clock distribution detail of the device prior to pin-locking and floorplanning.Figure 35 shows clock distribution in BQR2V3000.

Figure 35 BQR2V3000 Clock Distribution

In each quadrant, up to eight clocks are organized in clock rows. A clock row supports up to 16 CLB rows (eight up and eight down). For the largest devices a new clock row is added, as necessary.

To reduce power consumption, any unused clock branches remain static.

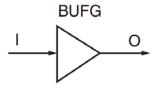

Global clocks are driven by dedicated clock buffers (BUFG), which can also be used to gate the clock (BUFGCE) or to multiplex between two independent clock inputs (BUFGMUX).

The most common configuration option of this element is as a buffer. A BUFG function in this (global buffer) mode, is shown in Figure 36.

Figure 36 BQR2V3000 BUFG Function

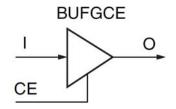

The BQR2V3000 global clock buffer BUFG can also be configured as a clock enable/disable circuit (Figure 37), as well as a two-input clock multiplexer (Figure 38). A functional description of these two options is provided below. Each of them can be used in either of two modes, selected by configuration: rising clock edge or falling clock edge.

This section describes the rising clock edge option. For the opposite option, falling clock edge, just change all "rising" references to "falling" and all "High" references to "Low", except for the description of the CE or S levels. The rising clock edge option uses the BUFGCE and BUFGMUX primitives. The falling clock edge option uses the BUFGCE 1 and BUFGMUX 1 primitives.

#### **BUFGCE**

If the CE input is active (High) prior to the incoming rising clock edge, this Low-to-High-to-Low clock pulse passes through the clock buffer. Any level change of CE during the incoming clock High time has no effect.

Figure 37 BQR2V3000 BUFGCE Function

If the CE input is inactive (Low) prior to the incoming rising clock edge, the following clock pulse does not pass through the clock buffer, and the output stays Low. Any level change of CE during the incoming clock High time has no effect. CE

must not change during a short setup window just prior to the rising clock edge on the BUFGCE input I. Violating this setup time requirement can result in an undefined runt pulse output.

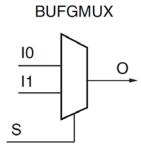

### BUFGMUX

BUFGMUX can switch between two unrelated, even asynchronous clocks. Basically, a Low on S selects the I0 input, and a High on S selects the I1 input. Switching from one clock to the other is done in such a way that the output High and Low time is never shorter than the shortest High or Low time of either input clock. As long as the presently selected clock is High, any level change of S has no effect.

#### Figure 38 BQR2V3000 BUFGMUX Function

If the presently selected clock is Low while S changes, or if it goes Low after S has changed, the output is kept Low until the other ("to-be-selected") clock has made a transition from High to Low. At that instant, the new clock starts driving the output.

The two clock inputs can be asynchronous with regard to each other, and the S input can change at any time, except for a short setup time prior to the rising edge of the presently selected clock, that is, prior to the rising edge of the BUFGMUX output O. Violating this setup time requirement can result in an undefined runt pulse output.

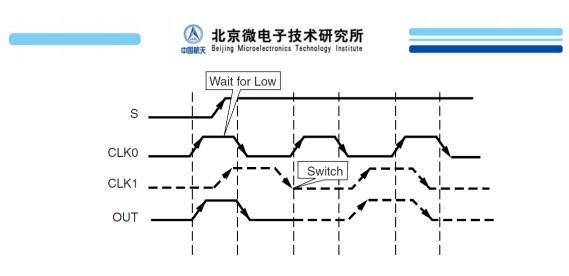

BQR2V3000 have 16 global clock multiplexer buffers. Figure 39 shows a switchover from CLK0 to CLK1. In Figure 39:

• The current clock is CLK0.

• S is activated High.

• If CLK0 is currently High, the multiplexer waits for CLK0 to go Low.

• Once CLK0 is Low, the multiplexer output stays Low until CLK1 transitions High to Low.

• When CLK1 transitions from High to Low, the output switches to CLK1.

No glitches or short pulses can appear on the output.

Figure 39 Clock Multiplexer Waveform Diagram

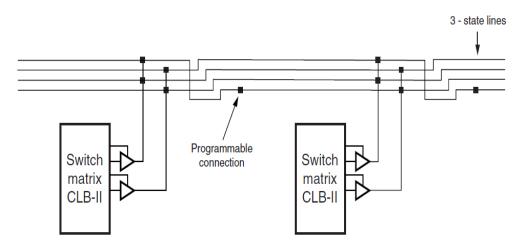

#### 3.2.7 Routing Resources

Local and global BQR2V3000 routing resources are optimized for speed and timing predictability, as well as to facilitate cores implementation. BQR2V3000 Active Interconnect Technology is a fully buffered programmable routing matrix.All routing resources are segmented to offer the advantages of a hierarchical solution. BQR2V3000 logic features like CLBs,IOBs, block RAM, multipliers, and DCMs are all connected to an identical switch matrix for access to global routing resources, as shown in Figure 40.

Figure 40 Active Interconnect Technology

Each BQR2V3000 device can be represented as an array of switch matrices with logic blocks attached, as illustrated in Figure 41.

Place-and-route software takes advantage of this regular array to deliver optimum system performance and fast compile times. The segmented routing resources are essential to guarantee IP cores portability and to efficiently handle an

incremental design flow that is based on modular implementations. Total design time is reduced due to fewer and shorter design iterations.

| Switch               | Switch               | Switch               | Switch                        | Switch           |

|----------------------|----------------------|----------------------|-------------------------------|------------------|

| Matrix IOB           | Matrix IOB           | Matrix               | Matrix DCM                    | Matrix           |

| Switch               | Switch               | Switch               | Switch                        | Switch           |

| Matrix IOB           | Matrix CLB           | Matrix CLB           | Matrix                        | Matrix           |

| Switch<br>Matrix IOB | Switch<br>Matrix CLB | Switch<br>Matrix CLB | Switch<br>Matrix<br>SelectBAM | Switch<br>Matrix |

| Switch               | Switch               | Switch               | Switch                        | Switch           |

| Matrix IOB           | Matrix CLB           | Matrix CLB           | Matrix                        | Matrix ◀►        |

| Switch               | Switch               | Switch               | Switch                        | Switch           |

| Matrix IOB           | Matrix ◀►► CLB       | Matrix CLB           | Matrix ◀-►                    | Matrix           |