## High Reliability Series Serial EEPROMs

# SPI BUS BR25□□□□family

BR25S□□□ Series

No.10001EBT08

### Description

BR25S□□□ series is a serial EEPROM of SPI BUS interface method.

#### Features

- 1) High speed clock action up to 20MHz (Max.)

- 2) Wait function by HOLDB terminal

- 3) Part or whole of memory arrays settable as read only memory area by program

- 4) 1.7~5.5V single power source action most suitable for battery use

- 5) Page write mode useful for initial value write at factory shipment

- 6) Highly reliable connection by Au pad and Au wire

- 7) For SPI bus interface (CPOL, CPHA) = (0, 0), (1, 1)

- 8) Auto erase and auto end function at data rewrite

- 9) Low current consumption

At write action (5V) : 1.5mA (Typ.) At read action (5V) : 1.0mA (Typ.) At standby action (5V) : 0.1µA (Typ.)

- 10) Address auto increment function at read action

- 11) Write mistake prevention function

Write prohibition at power on

Write prohibition by command code (WRDI)

Write prohibition by WPB pin

Write prohibition block setting by status registers (BP1, BP0)

Write mistake prevention function at low voltage

- 12) SOP8/SOP-J8/SSOP-B8/TSSOP-B8/MSOP8/TSSOP-B8J/VSON008X2030 Package

- 13) Data at shipment Memory array: FFh, status register WPEN, BP1, BP0:0

- 14) Data kept for 40 years

- 15) Data rewrite up to 1,000,000 times

### ●Page Write

| Page        | 32Byte                   | 64Byte                   |

|-------------|--------------------------|--------------------------|

| Part Number | BR25S320-W<br>BR25S640-W | BR25S128-W<br>BR25S256-W |

#### ●BR25S□□□ series

| _ | DIVZJOLL |            |                      |      |        |         |          |       |           |                  |

|---|----------|------------|----------------------|------|--------|---------|----------|-------|-----------|------------------|

|   | Capacity | Bit format | Power source voltage | SOP8 | SOP-J8 | SSOP-B8 | TSSOP-B8 | MSOP8 | TSSOP-B8J | VSON008<br>X2030 |

|   | 32Kbit   | 4K×8       | 1.7V~5.5V            | •    | •      | •       | •        | •     | •         | •                |

|   | 64Kbit   | 8K×8       | 1.7V~5.5V            | •    | •      | •       | •        | •     | •         |                  |

|   | 128Kbit  | 16K×8      | 1.7V~5.5V            | •    | •      | •       | •        |       |           |                  |

|   | 256Kbit  | 32K×8      | 1.7V~5.5V            | •    | •      |         |          |       |           |                  |

● Absolute maximum ratings (Ta=25°C)

| Parameter                       | Symbol | Limits            |    | Unit |

|---------------------------------|--------|-------------------|----|------|

| Impressed voltage               | Vcc    | -0.3~+6.5         |    | ٧    |

|                                 |        | 450(SOP8)         | *1 |      |

|                                 |        | 450(SOP-J8)       | *2 |      |

|                                 |        | 300(SSOP-B8)      | *3 |      |

| Permissible dissipation         | Pd     | 330(TSSOP-B8)     | *4 | mW   |

| uissipation                     |        | 310(MSOP8) *5     |    |      |

|                                 |        | 310(TSSOP-B8J)    | *6 |      |

|                                 |        | 300(VSON008X2030) | *7 |      |

| Storage<br>temperature<br>range | Tstg   | -65~+125          |    | °C   |

| Operating temperature range     | Topr   | -40~+85           |    | °C   |

| Terminal voltage                | _      | -0.3~Vcc+0.3      |    | ٧    |

<sup>\*</sup> When using at Ta=25°C or higher, 4.5mW(\*1, \*2), 3.0mW(\*3, \*7),3.3mW(\*4), 3.1mW(\*5, \*6) to be reduced per 1°C

## ●Memory cell characteristics (Ta=25°C , Vcc=1.7V~5.5V)

| Parameter                       |           | Limits |      |      |  |  |  |  |

|---------------------------------|-----------|--------|------|------|--|--|--|--|

| Farameter                       | Min.      | Min.   | Min. | Unit |  |  |  |  |

| Number of data rewrite times *1 | 1,000,000 | _      | _    | Time |  |  |  |  |

| Data hold years *1              | 40        | ı      | ı    | Year |  |  |  |  |

<sup>\*1</sup> Not 100% TESTED

#### Recommended action conditions

| Parameter            | Symbol          | Limits  | Unit |

|----------------------|-----------------|---------|------|

| Power source voltage | V <sub>CC</sub> | 1.7~5.5 | \    |

| Input voltage        | V <sub>IN</sub> | 0~Vcc   | V    |

## ●Input / output capacity (Ta=25°C, frequency=5MHz)

| Parameter          | Symbol           | Conditions            | Min. | Max. | Unit |

|--------------------|------------------|-----------------------|------|------|------|

| Input capacity *1  | C <sub>IN</sub>  | $V_{IN}$ =GND         | 1    | 8    | ρF   |

| Output capacity *1 | C <sub>OUT</sub> | V <sub>OUT</sub> =GND | _    | 8    | рг   |

<sup>\*1</sup> Not 100% TESTED.

●Electrical characteristics (Unless otherwise specified, Ta=-40~+85°C, Vcc=1.7~5.5V)

| Parameter                    | Cumbal |         | Limits |                                      | Unit | Conditions                                                                   |

|------------------------------|--------|---------|--------|--------------------------------------|------|------------------------------------------------------------------------------|

| Parameter                    | Symbol | Min.    | Тур.   | Max.                                 | Unit | Conditions                                                                   |

| "H" Input Voltage1           | VIH1   | 0.7xVcc | _      | Vcc+0.3                              | V    | 1.7≦Vcc≦5.5V                                                                 |

| "L" Input Voltage1           | VIL1   | -0.3    | 1      | 0.3xVcc                              | V    | 1.7≦Vcc≦5.5V                                                                 |

| "L" Output Voltage1          | VOL1   | 0       | _      | 0.4                                  | V    | IOL=2.1mA, 2.5≦Vcc<5.5V                                                      |

| "L" Output Voltage2          | VOL2   | 0       | _      | 0.2                                  | V    | IOL=1.0mA, 1.7≦Vcc<2.5V                                                      |

| "H" Output Voltage1          | VOH1   | Vcc-0.2 | _      | Vcc                                  | V    | IOH=-0.4mA, 2.5V≦Vcc<5.5V                                                    |

| "H" Output Voltage2          | VOH2   | Vcc-0.2 | _      | Vcc                                  | V    | IOH=-100μA, 1.7≦Vcc<2.5V                                                     |

| Input Leakage Current        | ILI    | -1      | _      | 1                                    | μΑ   | V <sub>IN</sub> =0~Vcc                                                       |

| Output Leakage Current       | ILO    | -1      | _      | 1                                    | μΑ   | V <sub>OUT</sub> =0~Vcc, CSB=Vcc                                             |

|                              | ICC1   | _       | _      | 0.5 <sup>*1</sup><br>1 <sup>*2</sup> | mA   | Vcc=1.8V, fSCK=5MHz, tE/W=5ms                                                |

| On a ration of Commant Maita | 1000   |         |        | 1 *1                                 | Л    | Byte Write, Page Write, Write Status register Vcc=2.5V, fSCK=10MHz, tE/W=5ms |

| Operating Current Write      | ICC2   | 1       | 1      | 1.5 *2                               | mA   | Byte Write, Page Write, Write Status register                                |

|                              | ICC3   | _       | _      | 2 *1                                 | mA   | Vcc=5.5V, fSCK=20MHz, tE/W=5ms                                               |

|                              | 1003   |         |        | 3 *2                                 | ША   | Byte Write, Page Write, Write Status register                                |

|                              | ICC4   | _       | _      | 1                                    | mA   | Vcc=1.8V, fSCK=5MHz, SO=OPEN Read, Read Status Register                      |

|                              |        |         |        |                                      |      | Vcc=2.5V, fSCK=2MHz, SO=OPEN                                                 |

|                              | ICC5   | _       | _      | 1                                    | mΑ   | Read, Read Status Register                                                   |

|                              |        |         |        |                                      |      | Vcc=2.5V, fSCK=5MHz, SO=OPEN                                                 |

|                              | ICC6   | _       | _      | 1.5                                  | mA   | Read, Read Status Register                                                   |

|                              |        |         |        | _                                    |      | Vcc=2.5V, fSCK=10MHz, SO=OPEN                                                |

| Operating Current Read       | ICC7   | _       | _      | 2                                    | mA   | Read, Read Status Register                                                   |

|                              | 1000   |         |        | _                                    |      | Vcc=5.5V, fSCK=5MHz, SO=OPEN                                                 |

|                              | ICC8   | _       | _      | 2                                    | mA   | Read, Read Status Register                                                   |

|                              | 1000   | 1       |        | 4                                    | A    | Vcc=5.5V, fSCK=10MHz, SO=OPEN                                                |

|                              | ICC9   | _       | _      | 4                                    | mA   | Read, Read Status Register                                                   |

|                              | ICC10  |         |        | 8                                    | mA   | Vcc=5.5V, fSCK=20MHz, SO=OPEN                                                |

|                              | 10010  |         |        | 0                                    | ША   | Read, Read Status Register                                                   |

| Standby Current              | ISB    | _       | _      | 2                                    | μA   | Vcc=5.5V, SO=OPEN                                                            |

| Standby Current              | 136    |         |        |                                      | μΛ   | CSB=HOLDB=WPB=Vcc, SCK=SI=Vcc or GND                                         |

<sup>\*1</sup> BR25S320/640-W

<sup>\*2</sup> BR25S128/256-W

O Radiation resistance design is not made

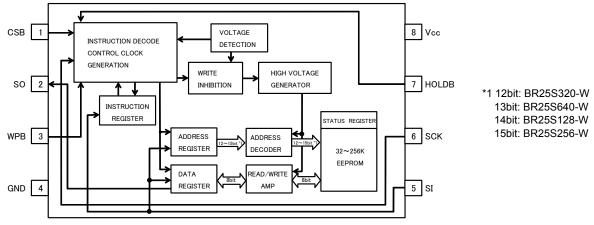

## Block diagram

Fig.1 Block diagram

●Operating timing characteristics (Ta=-40~+85°C, unless otherwise specified, load capacity C₁=30pF)

| Operating timing characteristics (1a=-40~+65 C, unless otherwise specified, load capacity Ct=50pr) |             |      |       |      |      |       |      |      |       |      |      |       |      |      |

|----------------------------------------------------------------------------------------------------|-------------|------|-------|------|------|-------|------|------|-------|------|------|-------|------|------|

| Parameter                                                                                          | Symbol      |      | €Vcc< |      |      | ≦Vcc< |      |      | €Vcc< |      |      | ≦Vcc< |      | Unit |

|                                                                                                    | Cymbol      | Min. | Тур.  | Max. |      |

| SCK frequency                                                                                      | fsck        | -    | -     | 3    | -    | -     | 5    | -    | -     | 10   | -    | -     | 20   | MHz  |

| SCK high time                                                                                      | tsckwh      | 125  | -     | -    | 80   | -     | -    | 40   | -     | -    | 20   | -     | -    | ns   |

| SCK low time                                                                                       | tsckwl      | 125  | -     | -    | 80   | -     | -    | 40   | -     | -    | 20   | -     | -    | ns   |

| CSB high time                                                                                      | tcs         | 250  | ı     | -    | 90   | -     | -    | 40   | ı     | -    | 20   | -     | -    | ns   |

| CSB setup time                                                                                     | tcss        | 100  | ı     | -    | 60   | -     | -    | 30   | ı     | -    | 15   | -     | -    | ns   |

| CSB hold time                                                                                      | tcsh        | 100  | -     | -    | 60   | -     | -    | 30   | -     | -    | 15   | -     | -    | ns   |

| SCK setup time                                                                                     | tscks       | 100  | 1     | -    | 50   | -     | -    | 20   | 1     | -    | 15   | -     | -    | ns   |

| SCK hold time                                                                                      | tsckh       | 100  | 1     | -    | 50   | -     | -    | 20   | -     | -    | 15   | -     | -    | ns   |

| SI setup time                                                                                      | tois        | 30   | 1     | -    | 20   | -     | -    | 10   | -     | -    | 5    | -     | -    | ns   |

| SI hold time                                                                                       | tDIH        | 50   | -     | -    | 20   | -     | -    | 10   | -     | -    | 5    | -     | -    | ns   |

| Data output delay time                                                                             | <b>t</b> PD | -    | -     | 125  | -    | -     | 80   | -    | -     | 40   | -    | -     | 20   | ns   |

| Output hold time                                                                                   | tон         | 0    | -     | -    | 0    | -     | -    | 0    | -     | -    | 0    | -     | -    | ns   |

| Output disable time                                                                                | toz         | -    | -     | 200  | -    | -     | 80   | -    | -     | 40   | -    | -     | 20   | ns   |

| HOLDB setting setup time                                                                           | tHFS        | 100  | -     | -    | 0    | -     | -    | 0    | -     | -    | 0    | -     | -    | ns   |

| HOLDB setting hold time                                                                            | thfh        | 100  | -     | -    | 20   | -     | -    | 10   | -     | -    | 5    | -     | -    | ns   |

| HOLDB release setup time                                                                           | tHRS        | 100  | -     | -    | 0    | -     | -    | 0    | -     | -    | 0    | -     | -    | ns   |

| HOLDB release hold time                                                                            | thrh        | 100  | -     | -    | 20   | -     | -    | 10   | -     | -    | 5    | -     | -    | ns   |

| Time from HOLDB to output High-Z                                                                   | tHOZ        | -    | -     | 100  | -    | -     | 80   | -    | -     | 40   | -    | -     | 20   | ns   |

| Time from HOLDB to output change                                                                   | tHPD        | -    | -     | 100  | -    | -     | 80   | -    | -     | 40   | -    | -     | 20   | ns   |

| SCK rise time                                                                                      | trc         | -    | -     | 1    | -    | -     | 1    | -    | -     | 1    | -    | -     | 1    | μs   |

| SCK fall time                                                                                      | tFC         | -    | -     | 1    | -    | -     | 1    | -    | -     | 1    | -    | -     | 1    | μs   |

| OUTPUT rise time *1                                                                                | tro         | -    | 1     | 100  | 1    | -     | 50   | -    | ı     | 40   | -    | -     | 20   | ns   |

| OUTPUT fall time                                                                                   | tFO         | -    | 1     | 100  | 1    | -     | 50   | -    | ı     | 40   | -    | -     | 20   | ns   |

| Write time                                                                                         | tE/W        | -    | -     | 5    | -    | -     | 5    | -    | -     | 5    | -    | -     | 5    | ms   |

<sup>\*1</sup> NOT 100% TESTED

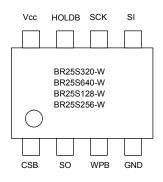

## ●Pin assignment and description

Fig.2 Pin assignment diagram

| Terminal name | Input<br>/Output | Function                                                                                    |

|---------------|------------------|---------------------------------------------------------------------------------------------|

| Vcc           | -                | Power source to be connected                                                                |

| GND           | -                | All input / output reference voltage, 0V                                                    |

| CSB           | Input            | Chip select input                                                                           |

| SCK           | Input            | Serial clock input                                                                          |

| SI            | Input            | Start bit, ope code, address, and serial data input                                         |

| SO            | Output           | Serial data output                                                                          |

| HOLDB         | Input            | Hold input Command communications may be suspended temporarily (HOLD status)                |

| WPB           | Input            | Write protect input Write command is prohibited Write status register command is prohibited |

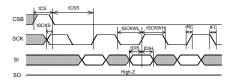

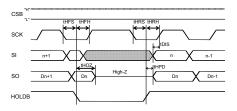

## Sync data input / output timing

Fig.3 Input timing

${\rm SI}$  is taken into IC inside in sync with data rise edge of SCK. Input address and data from the most significant bit  ${\rm MSB}$

Fig.4 Input / Output timing

SO is output in sync with data fall edge of SCK. Data is output from the most significant bit MSB.

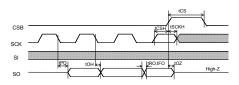

Fig.5 HOLD timing

#### AC timing characteristics conditions

| Dorometer                       | Cumbal |               | Unit      |      |       |  |

|---------------------------------|--------|---------------|-----------|------|-------|--|

| Parameter                       | Symbol | Min.          | Тур.      | Max. | Offic |  |

| Load capacity                   | CL     | -             | -         | 30   | pF    |  |

| Input rise time                 | -      | -             | -         | 50   | ns    |  |

| Input fall time                 | -      | -             | -         | 50   | ns    |  |

| Input voltage                   | -      | 0.3           | 2Vcc/0.8\ | /cc  | V     |  |

| Input / Output judgment voltage | -      | 0.3Vcc/0.7Vcc |           |      |       |  |

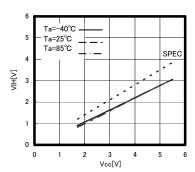

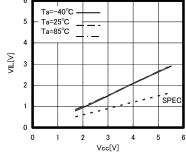

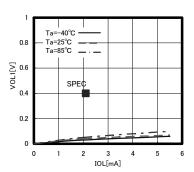

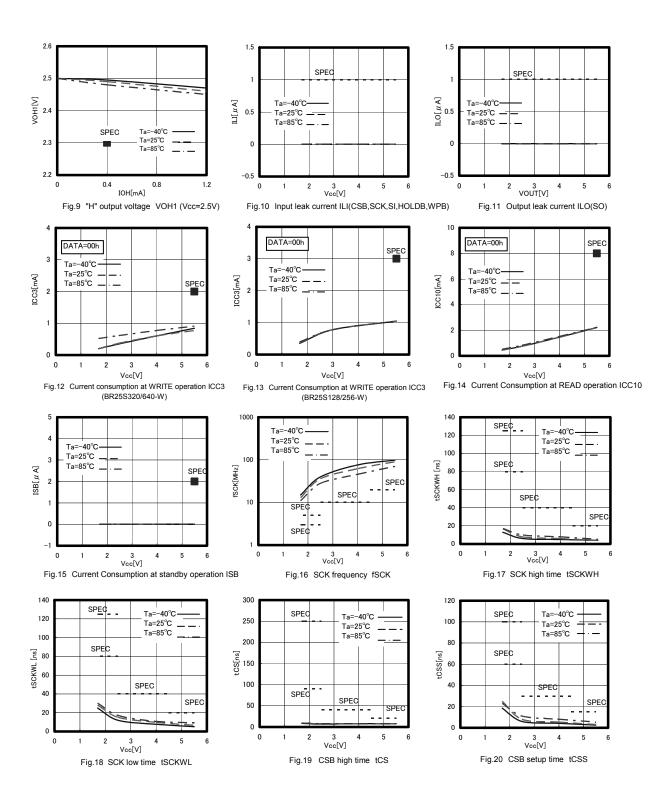

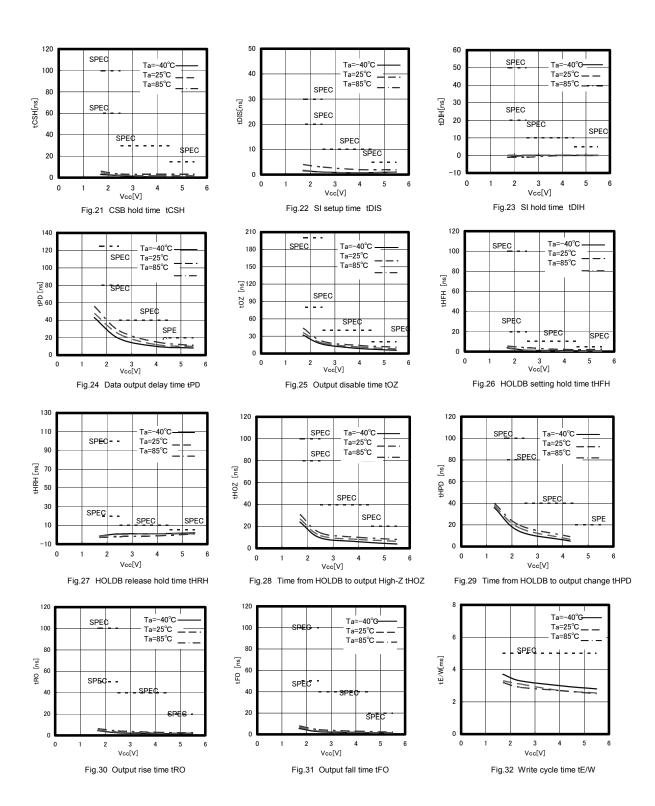

#### ● Characteristic data (The following characteristic data are Typ. Values.)

Fig.6 "H" input voltage VIH(CSB,SCK,SI,HOLDB,WPB) Fig.7 "L" input voltage VIL(CSB,SCK,SI,HOLDB,WPB)

Fig.8 "L" output voltage VOL1 (Vcc=2.5V)

#### ● Characteristic data (The following characteristic data are Typ. Values.)

## ● Characteristic data (The following characteristic data are Typ. Values.)

#### Features

#### OStatus registers

This IC has status register. The status register expresses the following parameters of 8 bits.

BP0 and BP1 can be set by write status register command. These 2 bits are memorized into the EEPROM, therefore are valid even when power source is turned off.

Rewrite characteristics and data hold time are same as characteristics of the EEPROM.

WEN can be set by write enable command and write disable command. WEN becomes write disable status when power source is turned off. R/B is for write confirmation, therefore cannot be set externally.

The value of status register can be read by read status register command.

#### 1. Contexture of status register

| Product number | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1  | bit 0 |

|----------------|-------|-------|-------|-------|-------|-------|--------|-------|

| BR25S320-W     |       |       |       |       |       |       |        |       |

| BR25S640-W     | MOEN  | •     | •     | •     | DD4   | DDO   | \A/E\1 |       |

| BR25S128-W     | WPEN  | Ü     | U     | Ü     | BP1   | BP0   | WEN    | R/B   |

| BR25S256-W     |       |       |       |       |       |       |        |       |

| bit        | Memory location | Function                                                                                                        |

|------------|-----------------|-----------------------------------------------------------------------------------------------------------------|

| WPEN       | EEPROM          | WPB pin enable / disable designation bit<br>WPEN=0=invalid<br>WPEN=1=valid                                      |

| BP1<br>BP0 | EEPROM          | EEPROM write disable block designation bit                                                                      |

| WEN        | registers       | Write and write status register write enable / disable status confirmation bit WEN=0=prohibited WEN=1=permitted |

| _<br>R∕B   | registers       | Write cycle status (READY / BUSY) status confirmation bit $R/B=0=READY$ $R/B=1=BUSY$                            |

#### 2. Write disable block setting

| BP1 | BP0 | Write disable block |             |             |             |

|-----|-----|---------------------|-------------|-------------|-------------|

| DPI |     | BR25S320-W          | BR25S640-W  | BR25S128-W  | BR25S256-W  |

| 0   | 0   | None                | None        | None        | None        |

| 0   | 1   | C00h-FFFh           | 1800h-1FFFh | 3000h-3FFFh | 6000h-7FFFh |

| 1   | 0   | 800h-FFFh           | 1000h-1FFFh | 2000h-3FFFh | 4000h-7FFFh |

| 1   | 1   | 000h-FFFh           | 0000h-1FFFh | 0000h-3FFFh | 0000h-7FFFh |

#### OWPB pin

By setting WPB=LOW, write command is prohibited. And the write command to be disabled at this moment is WRSR. However, when write cycle is in execution, no interruption can be made.

| Product number | WRSR                                     | WRITE                  |

|----------------|------------------------------------------|------------------------|

| BR25S320-W     | Prohibition possible<br>but WPEN bit "1" |                        |

| BR25S640-W     |                                          | Prohibition impossible |

| BR25S128-W     |                                          |                        |

| BR25S256-W     |                                          |                        |

#### OHOLDB pin

By HOLDB pin, data transfer can be interrupted. When SCK="0", by making HOLDB from "1" into"0", data transfer to EEPROM is interrupted. When SCK = "0", by making HOLDB from "0" into "1", data transfer is restarted.

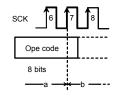

#### ■Command mode

| Command | Contents                      | Ope code |      |

|---------|-------------------------------|----------|------|

| WREN    | Write enable command          | 0000     | 0110 |

| WRDI    | Write disable command         | 0000     | 0100 |

| READ    | Read command                  | 0000     | 0011 |

| WRITE   | Write command                 | 0000     | 0010 |

| RDSR    | Read status register command  | 0000     | 0101 |

| WRSR    | Write status register command | 0000     | 0001 |

#### Timing chart

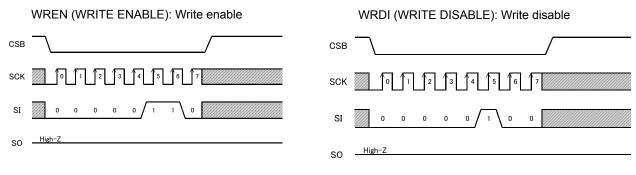

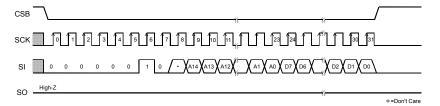

1. Write enable (WREN) / disable (WRDI) command

Fig.33 Write enable command

Fig.34 Write disable command

This IC has write enable status and write disable status. It is set to write enable status by write enable command, and it is set to write disable status by write disable command. As for these commands, set CSB LOW, and then input the respective ope codes. The respective commands are accepted at the 7-th clock rise. Even with input over 7 clocks, command becomes valid.

When to carry out write command, it is necessary to set write enable status by the write enable command. If write command is input in the write disable status, the command is cancelled. And even in the write enable status, once write command is executed, it gets in the write disable status. After power on, this IC is in write disable status.

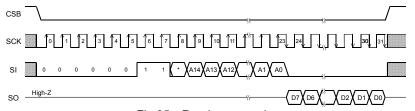

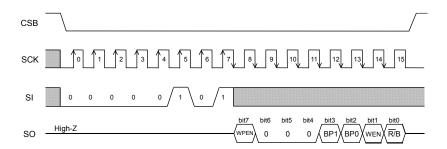

#### 2. Read command (READ)

| Fig.35 | Read | command | į |

|--------|------|---------|---|

|--------|------|---------|---|

| Product    | Address |

|------------|---------|

| number     | length  |

| BR25S320-W | A11-A0  |

| BR25S640-W | A12-A0  |

| BR25S128-W | A13-A0  |

| BR25S256-W | A14-A0  |

By read command, data of EEPROM can be read. As for this command, set CSB LOW, then input address after read ope code. EEPROM starts data output of the designated address. Data output is started from SCK fall of 23-th clock, and from D7 to D0 sequentially. This IC has increment read function. After output of data for 1 byte (8bits), by continuing input of SCK, data of the next address can be read. Increment read can read all the addresses of EEPROM. After reading data of the most significant address, by continuing increment read, data of the most insignificant address is read.

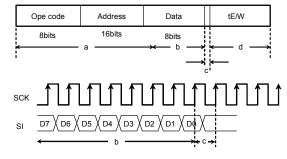

3. Write command (WRITE)

| Product    | Address |

|------------|---------|

| number     | length  |

| BR25S320-W | A11-A0  |

| BR25S640-W | A12-A0  |

| BR25S128-W | A13-A0  |

| BR25S256-W | A14-A0  |

Fig.36 Write command

By write command, data of EEPROM can be written. As for this command, set CSB LOW, then input address and data after write ope code. Then, by making CSB HIGH, the EEPROM starts writing. The write time of EEPROM requires time of tE/W (Max 5ms). During tE/W, other than read status register command is not accepted. Set CSB HIGH between taking the last data (D0) and rising the next SCK clock. At the other timing, write command is not executed, and this write command is cancelled. This IC has page write function, and after input of data for 1 byte (8 bits), by continuing data input without setting CSB HIGH, 2byte or more data can be written for one tE/W. The maximum number of write bytes is specified per device of each capacity. Up to 64 arbitrary bytes can be written (in the case of BR25S128/256-W). In page write, the insignificant 5 bit of the designated address is incremented internally at every time when data of 1 byte is input and data is written to respective addresses. When data of the maximum bytes or higher is input, address rolls over, and previously input data is overwritten.

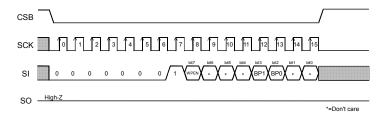

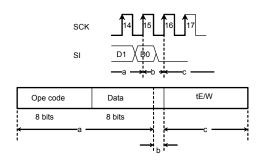

4. Write status register, Read status register command (WRSR/RDSR)

Fig.37 Write status register

Write status register command can write data of status register. The data can be written by this command are 3 bits, that is, WPEN(bit7), BP1 (bit3) and BP0 (bit2) among 8 bits of status register. By BP1 and BP0, write disable block of EEPROM can be set. As for this command, set CSB LOW, and input ope code of write status register, and input data. Then, by making CSB HIGH, EEPROM starts writing. Write time requires time of tE/W as same as write. As for CSB rise, set CSB HIGH between taking the last data bit (bit0) and the next SCK clock rising. At the other timing, command is cancelled. Write disable block is determined by BP1 BP0, and the block can be selected from 1/4 , 1/2, and entire of memory array (Refer to the write disable block setting table.). To the write disabled block, write cannot be made, and only read can be made.

Fig.38 Read status register command

#### WPB cancel valid area

WPB is normally fixed to "H" or "L" for use, but when WPB is controlled so as to cancel write status register command, pay attention to the following WPB valid timing.

While write status register command is executed, by setting WPB = "L" in cancel valid area, command can be cancelled. The area from command ope code to CSB rise at internal automatic write start becomes the cancel valid area. However, once write is started, by any input write cycle cannot be cancelled. WPB input becomes Don't Care, and cancellation becomes invalid.

Fig.39 WPB valid timing (At inputting WRSR command)

## ●HOLDB pin

By HOLDB pin, command communication can be stopped temporarily (HOLD status). The command communications are carried out when the HOLDB pin is HIGH. To get in HOLD status, at command communication, when SCK=LOW, set the HOLDB pin LOW. At HOLD status, SCK and SI become Don't Care, and SO becomes high impedance (High-Z). To release the HOLD status, set the HOLDB pin HIGH when SCK=LOW. After that, communication can be restarted from the point before the HOLD status. For example, when HOLD status is made after A5 address input at read, after release of HOLD status, by starting A4 address input, read can be restarted. When in HOLD status, keep CSB LOW. When it is set CSB=HIGH in HOLD status, the IC is reset, therefore communication after that cannot be restarted.

#### Method to cancel each command

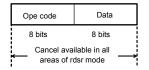

#### OREAD, RDSR

· Method to cancel: cancel by CSB = "H".

| Ope code                                   | Address | Data   |  |

|--------------------------------------------|---------|--------|--|

| 8 bits                                     | 16 bits | 8 bits |  |

| Cancel available in all areas of read mode |         |        |  |

Fig.40 READ cancel valid timing

#### OWRITE, PAGE WRITE

- a : Ope code or address input area Cancellation is available by CSB="H".

- b : Data input area (D7~D1 input area) Cancellation is available by CSB="H".

- c : Data input area (D0 area)

In this area, cancellation is not available.

When CSB is set HIGH, write starts.

- d : tE/W area

In the area c, by rising CSB, write starts.

While writing, by any input, cancellation cannot be made.

Fig.41 RDSR cancel valid timing

Fig.42 WRITE cancel valid timing

Note1) If Vcc is made OFF during write execution, designated address data is not guaranteed, therefore write it once again. Note2) If CSB is rised at the same timing as that of the SCK rise, write execution / cancel becomes unstable, therefore, it is recommended to rise in SCK = "L" area. As for SCK rise, assure timing of tCSS / tCSH or more.

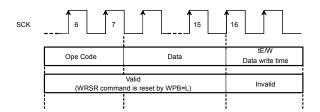

#### **OWRSR**

- a : From ope code to 15-th clock rise Cancellation is available by CSB="H".

- b : From 15-th clock rise to 16-th clock rise (write enable area)

In this area, cancellation is not available.

When CSB is set HIGH, write starts.

- c : After 16-th clock rise.

Cancellation is available by CSB="H".

However, if write starts (CSB is rised)

in the area b, cancellation cannot be made by any means.

And, by inputting on SCK clock, cancellation cannot be made.

Fig.43 WRSR cancel valid timing

Note1) If Vcc is made OFF during write execution, designated address data is not guaranteed, therefore write it once again

Note2) If CSB is rised at the same timing as that of the SCK rise, write execution / cancel becomes unstable, therefore, it is recommended to rise in SCK = "L" area. As for SCK rise, assure timing of tCSS / tCSH or more.

#### OWREN/WRDI

- a: From ope code to 7-th clock rise, cancellation is available by CSB = "H".

- $b\,:\, Cancellation \,\, is \,\, not \,\, available \,\, 7\text{-th clock}.$

Fig.44 WREN/WRDI cancel valid timing

#### I/O peripheral circuits

In order to realize stable high speed operations, pay attention to the following input / output pin conditions.

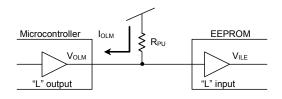

Olnput pin pull up, pull down resistance

When to attach pull up, pull down resistance to EEPROM input pin, select an appropriate value for the microcontroller VOL, IOL with considering VIL characteristics of this IC.

#### 1. Pull up resistance

Fig.45 Pull up resistance

$$R_{PU} \ge \frac{V_{CC} - V_{OLM}}{I_{OLM}} \cdots \bigcirc$$

$$V_{OLM} \le V_{ILF} \cdots \bigcirc$$

Example) When Vcc=5V,  $V_{ILE}$ =1.5V,  $V_{OLM}$ =0.4V,  $I_{OLM}$ =2mA, from the equation (1),

$$R_{PU} \ge \frac{5-0.4}{2 \times 10^{-3}}$$

$$\therefore R_{PU} \ge 2.3[k\Omega]$$

With the value of Rpu to satisfy the above equation,  $V_{OLM}$  becomes 0.4V or lower, and with  $V_{ILE}$  (=1.5V), the equation ② is also satisfied.

- V<sub>ILE</sub> :EEPROM V<sub>IL</sub> specifications

- V<sub>OLM</sub>: Microcontroller V<sub>OL</sub> specifications

- I<sub>OLM</sub> :Microcontroller I<sub>OL</sub> specifications

And, in order to prevent malfunction or erroneous write at power ON/OFF, be sure to make CSB pull up.

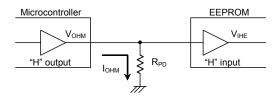

#### 2.Pull down resistance

Fig.46 Pull down resistance

$$R_{PD} \ge \frac{V_{OHM}}{I_{OHM}} \cdots 0$$

$V_{OHM} \ge V_{IHE} \cdots 0$

Example) When  $V_{CC}$ =5V,  $V_{OHM}$ = $V_{CC}$ -0.5V,  $I_{OHM}$ =0.4mA,  $V_{IHE}$ = $V_{CC}$ ×0.7V, from the equation③,

$$R_{PD} \ge \frac{5-0.5}{0.4 \times 10^{-3}}$$

$$\therefore R_{PD} \ge 11.3 [k \Omega]$$

Further, by amplitude VIHE, VILE of signal input to EEPROM, operation speed changes. By inputting Vcc/GND level amplitude of signal, more stable high speed operations can be realized. On the contrary, when amplitude of 0.8 VCC / 0.2 Vcc is input, operation speed becomes slow.\*1

In order to realize more stable high speed operation, it is recommended to make the values of  $R_{PU}$ ,  $R_{PD}$  as large as possible, and make the amplitude of signal input to EEPROM close to the amplitude of VCC / GND level. ( $^{*}$ 1 In this case, guaranteed value of operating timing is guaranteed.)

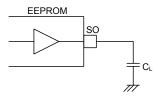

#### OSO load capacity condition

Load capacity of SO output pin affects upon delay characteristic of SO output (Data output delay time, time from HOLDB to High-Z, Output rise time, Output fall time.). In order to make output delay characteristic into better, make SO load capacity small.

Fig.47 SO load capacity

#### OOther cautions

Make the each wire length from the microcontroller to EEPROM input pin same length, in order to prevent setup / hold violation to EEPROM, owing to difference of wire length of each input.

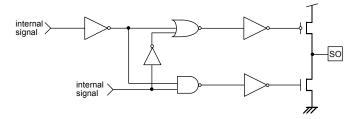

## ● Equivalent circuit Output circuit

Fig.48 SO output equivalent circuit

## Olnput circuit

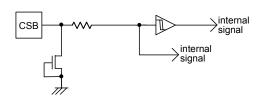

Fig.49 CSB input equivalent circuit

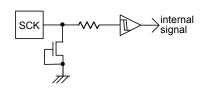

Fig.50 SCK input equivalent circuit

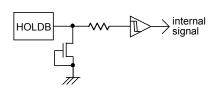

Fig.52 HOLDB input equivalent circuit

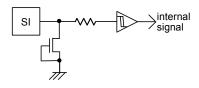

Fig.51 SI input equivalent circuit

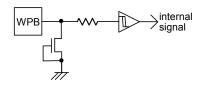

Fig.53 WPB input equivalent circuit

#### Notes on power ON/OFF

OAt standby

Set CSB "H", and be sure to set SCK, SI input "L" or "H". Do not input intermediate electric potantial.

#### OAt power ON/OFF

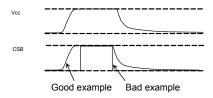

When Vcc rise or fall, set CSB="H" (=Vcc).

When CSB is "L", this IC gets in input accept status (active). If power is turned on in this status, noises and the likes may cause malfunction, erroneous write or so. To prevent these, at power ON, set CSB "H". (When CSB is in "H" status, all inputs are canceled.)

Fig.54 CSB timing at power ON/OFF

#### (Good example) CSB terminal is pulled up to Vcc.

At power OFF, take 10ms or more before supply. If power is turned on without observing this condition, the IC internal circuit may not be reset.

#### (Bad example) CSB terminal is "L" at power ON/OFF.

In this case, CSB always becomes "L" (active status), and EEPROM may have malfunction or erroneous write owing to noises and the likes.

Even when CSB input is High-Z, the status becomes like this case.

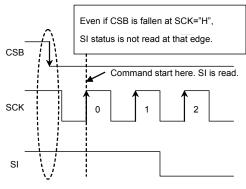

#### OOperating timing after power ON

As shown in Fig.55, at standby, when SCK is "H", even if CSB is fallen, SI status is not read at fall edge. SI status is read at SCK rise edge after fall of CSB. At standby and at power ON/OFF, set CSB "H" status.

Fig.55 Operating timing

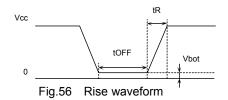

#### OAt power on malfunction preventing function

This IC has a POR (Power On Reset) circuit as mistake write countermeasure. After POR action, it gets in write disable status. The POR circuit is valid only when power is ON, and does not work when power is OFF. When power is ON, if the recommended conditions of the following tR, tOFF, and Vbot are not satisfied, it may become write enable status owing to noises and the likes.

|               | Recommended conditions of t <sub>R</sub> , t <sub>OFF</sub> , Vbot |                |               |  |  |

|---------------|--------------------------------------------------------------------|----------------|---------------|--|--|

|               | tr                                                                 | toff           | Vbot          |  |  |

| 10ms or below |                                                                    | 10ms or higher | 0.3V or below |  |  |

|               | 100ms or below                                                     | 10ms or higher | 0.2V or below |  |  |

## OLow voltage malfunction preventing function

LVCC (Vcc-Lockout) circuit prevents data rewrite action at low power, and prevents wrong write.

At LVCC voltage (Typ. =1.2V) or below, it prevent data rewrite.

#### Noise countermeasures

OVcc noise (bypass capacitor)

When noise or surge gets in the power source line, malfunction may occur, therefore, for removing these, it is recommended to attach a bypass capacitor  $(0.1\mu F)$  between IC Vcc and GND. At that time, attach it as close to IC as possible.

And, it is also recommended to attach a bypass capacitor between board Vcc and GND.

OSCK noise

When the rise time of SCK (tRC) is long, and a certain degree or more of noise exists, malfunction may occur owing to clock bit displacement. To avoid this, a Schmitt trigger circuit is built in SCK input. The hysteresis width of this circuit is set about 0.2V, if noises exist at SCK input, set the noise amplitude 0.2Vp-p or below. And it is recommended to set the rise time of SCK (tRC) 100ns or below. In the case when the rise time is 100ns or higher, take sufficient noise countermeasures. Make the clock rise, fall time as small as possible.

OWPB noise

During execution of write status register command, if there exist noises on WPB pin, mistake in recognition may occur and forcible cancellation may result. To avoid this, a Schmitt trigger circuit is built in WPB input. In the same manner, a Schmitt trigger circuit is built in CSB input, SI input and HOLDB input too.

#### ■Notes for use

- (1) Described numeric values and data are design representative values, and the values are not guaranteed.

- (2) We believe that application circuit examples are recommendable, however, in actual use, confirm characteristics further sufficiently. In the case of use by changing the fixed number of external parts, make your decision with sufficient margin in consideration of static characteristics and transition characteristics and fluctuations of external parts and our LSI.

- (3) Absolute maximum ratings

If the absolute maximum ratings such as impressed voltage and operating temperature range and so forth are exceeded, LSI may be destructed. Do not impress voltage and temperature exceeding the absolute maximum ratings. In the case of fear exceeding the absolute maximum ratings, take physical safety countermeasures such as fuses, and see to it that conditions exceeding the absolute maximum ratings should not be impressed to LSI.

- (4) GND electric potential

- Set the voltage of GND terminal lowest at any action condition. Make sure that each terminal voltage is higher than that of GND terminal.

- (5) Heat design

In consideration of permissible dissipation in actual use condition, carry out heat design with sufficient margin.

- (6) Terminal to terminal short circuit and wrong packaging

- When to package LSI onto a board, pay sufficient attention to LSI direction and displacement. Wrong packaging may destruct LSI. And in the case of short circuit between LSI terminals and terminals and power source, terminal and GND owing to foreign matter, LSI may be destructed.

- (7) Use in a strong electromagnetic field may cause malfunction, therefore, evaluate design sufficiently.

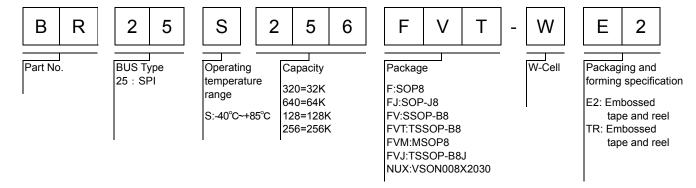

## Ordering part number

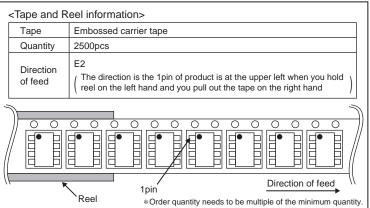

#### Package specifications

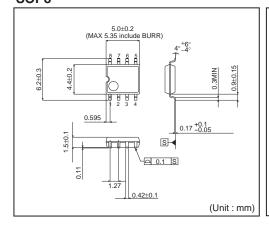

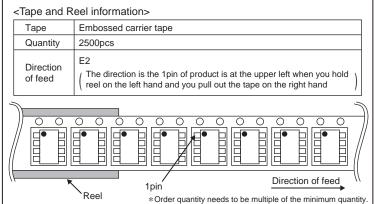

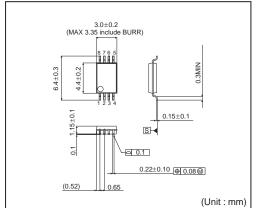

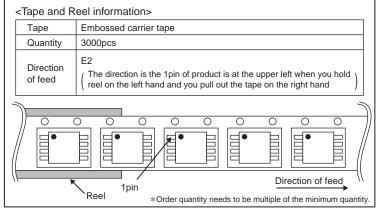

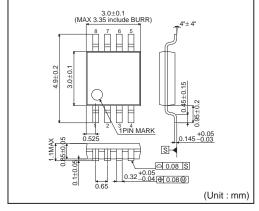

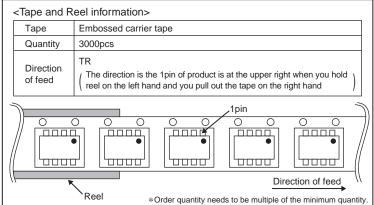

#### SOP8

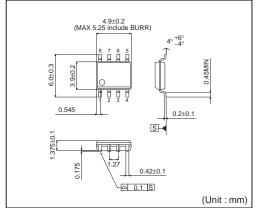

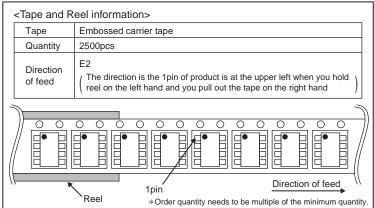

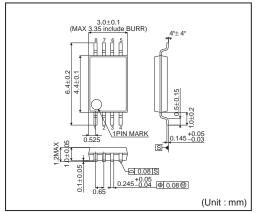

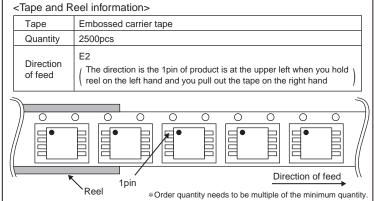

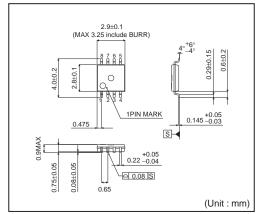

#### SOP-J8

## ● Package specifications (Continue)

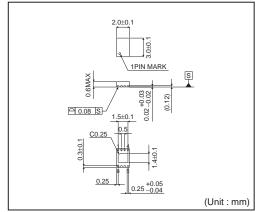

#### SSOP-B8

#### TSSOP-B8

## TSSOP-B8J

## ● Package specifications (Continue)

## MSOP8

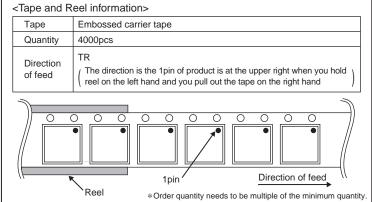

## VSON008X2030

#### Notes

No copying or reproduction of this document, in part or in whole, is permitted without the consent of ROHM Co.,Ltd.

The content specified herein is subject to change for improvement without notice.

The content specified herein is for the purpose of introducing ROHM's products (hereinafter "Products"). If you wish to use any such Product, please be sure to refer to the specifications, which can be obtained from ROHM upon request.

Examples of application circuits, circuit constants and any other information contained herein illustrate the standard usage and operations of the Products. The peripheral conditions must be taken into account when designing circuits for mass production.

Great care was taken in ensuring the accuracy of the information specified in this document. However, should you incur any damage arising from any inaccuracy or misprint of such information, ROHM shall bear no responsibility for such damage.

The technical information specified herein is intended only to show the typical functions of and examples of application circuits for the Products. ROHM does not grant you, explicitly or implicitly, any license to use or exercise intellectual property or other rights held by ROHM and other parties. ROHM shall bear no responsibility whatsoever for any dispute arising from the use of such technical information.

The Products specified in this document are intended to be used with general-use electronic equipment or devices (such as audio visual equipment, office-automation equipment, communication devices, electronic appliances and amusement devices).

The Products specified in this document are not designed to be radiation tolerant.

While ROHM always makes efforts to enhance the quality and reliability of its Products, a Product may fail or malfunction for a variety of reasons.

Please be sure to implement in your equipment using the Products safety measures to guard against the possibility of physical injury, fire or any other damage caused in the event of the failure of any Product, such as derating, redundancy, fire control and fail-safe designs. ROHM shall bear no responsibility whatsoever for your use of any Product outside of the prescribed scope or not in accordance with the instruction manual.

The Products are not designed or manufactured to be used with any equipment, device or system which requires an extremely high level of reliability the failure or malfunction of which may result in a direct threat to human life or create a risk of human injury (such as a medical instrument, transportation equipment, aerospace machinery, nuclear-reactor controller, fuel-controller or other safety device). ROHM shall bear no responsibility in any way for use of any of the Products for the above special purposes. If a Product is intended to be used for any such special purpose, please contact a ROHM sales representative before purchasing.

If you intend to export or ship overseas any Product or technology specified herein that may be controlled under the Foreign Exchange and the Foreign Trade Law, you will be required to obtain a license or permit under the Law.

Thank you for your accessing to ROHM product informations. More detail product informations and catalogs are available, please contact us.

## ROHM Customer Support System

http://www.rohm.com/contact/