## **ADVANTAGES**

- Low cost bipolar primary switch driven in a cascode configuration by a LV n-channel MOSFET

- Tight tolerance CV/CC operation

- Low component count

- High efficiency (Energy Star 2.0 compliance with margin)

- Very low no-load power (<100mW for 16W designs)</li>

- Programmable maximum switching frequency

- Programmable output cable compensation up to 10%

### **FEATURES**

- Advanced primary sensing controller achieves true CV/CC output characteristic without opto-coupler

- Full featured protection for over-temperature, input over-voltage, input under-voltage, output short-circuit

- Advanced PFM/PWM control and quasi-resonant switching for increased efficiency

- Natural switching timing jitter spreads RF spectral emissions, eases EMC compliance

- SOT23-6 package

## **APPLICATIONS**

- Adapters for network applications

- Universal standby and auxiliary power supplies

- Set top box power adapters

- Chargers for power tools

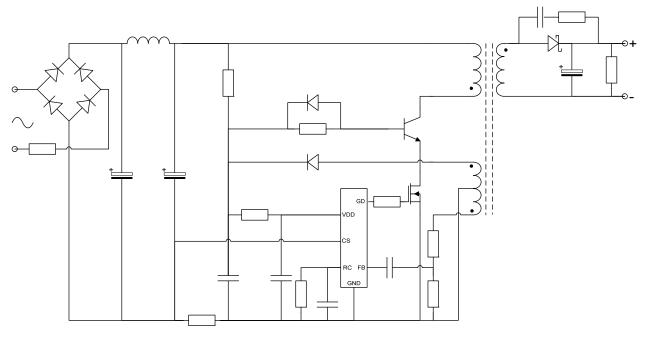

Figure 1: Typical Application Circuit

## **BLOCK DIAGRAM**

Figure 2: C2163PX2 Block Diagram

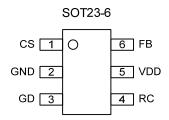

#### **PIN DEFINITIONS**

Figure 3: C2163PX2 Pin Assignment

#### **VDD Pin**

The VDD pin supplies power to the chip and dictates the operating mode (Run or Sleep).

#### **FB Pin**

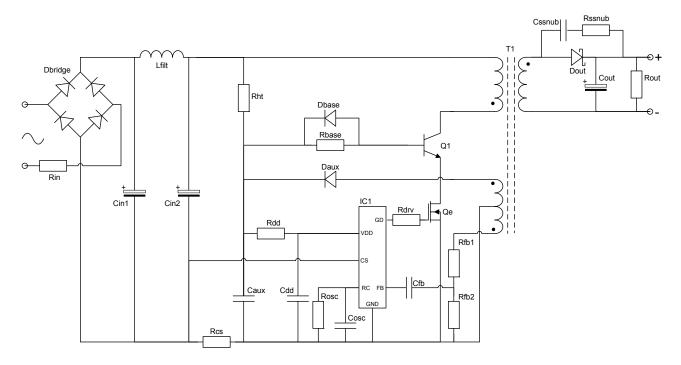

The FB pin is used to sense the transformer winding voltage waveform, scaled and AC-coupled by an external RC network (Rfb1, Rfb2 and Cfb in Figure 4).

#### CS Pin

The CS pin senses the primary switch current via the current sensing resistor (Rcs in Figure 4).

#### **RC Pin**

The RC timing network connected to the RC pin (shown as Rosc, Cosc in Figure 4) defines both the required maximum switching frequency  $F_{MAX}$  and the cable compensation.

#### **GD Pin**

The GD pin is connected to the gate of the external MOSFET transistor (Qe in Figure 4).

#### **GND Pin**

The GND pin provides the ground reference.

## **TYPICAL APPLICATION**

The C2163PX2 controller is intended primarily for 12 V adapters, but is equally applicable to other off-line applications up to 16 W requiring low standby power and high efficiency. Higher power applications are possible, limited by component selection required to achieve the necessary power supply specifications. A high degree of configurability allows a wide range of applications to be met at minimum cost. A typical application circuit is shown below.

Figure 4: Universal Input 12 W Adapter

## **Typical 12 W Adapter Performance**

| Input                                        | V <sub>IN</sub>      | 85 - 265 V ac    |

|----------------------------------------------|----------------------|------------------|

| Output                                       | V <sub>OUTNOM</sub>  | 12 V dc (± 5%)   |

|                                              | I <sub>OUTNOM</sub>  | 1 A dc (-0/+20%) |

| Cable compensation                           | G <sub>CAB</sub>     | 2 %              |

| Average Typical Efficiency (including cable) | K <sub>EFF</sub>     | > 80%            |

| No-load input power consumption              | P <sub>NO_LOAD</sub> | < 100 mW         |

| Over-temperature protection (OTP)            | T <sub>SH</sub>      | 115 °C           |

| Start-up time                                | tstart               | < 2 s            |

### PRINCIPLE OF OPERATION

Parameters used in equations are explained in the Electrical Characteristics section.

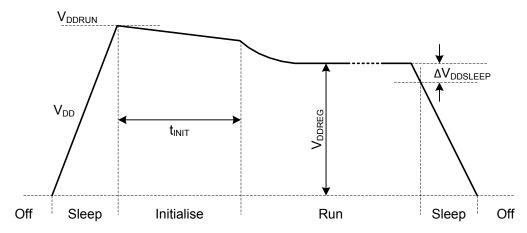

### Power-Up/Power-Down Sequences

The C2163PX2 controller is powered via the VDD pin. When the line input is first applied, a small amount of current ( $I_{DDSLEEP}$ ) is drawn from the rectified mains input via a high value start up resistor (Rht in Figure 4). When the voltage on the VDD pin ( $V_{DD}$ ) reaches a level  $V_{DDRUN}$  the controller wakes up, demands more supply current ( $I_{DDREG}$ ) and enters the Initialise mode (see Figure 5). The controller stays in Initialise for a short time during which internal circuits are enabled and then changes to Run mode. In Run mode, the controller uses an internal shunt regulator to regulate  $V_{DD}$  at  $V_{DDREG}$ .

If the VDD pin voltage drops  $\Delta V_{DDSLEEP}$  below  $V_{DDREG}$  the controller goes back into Sleep mode, reducing the supply current demand. The system will restart when input power is restored and  $V_{DD}$  reaches  $V_{DDRUN}$  again. To achieve a smooth power up sequence the VDD reservoir capacitor (Cdd in Figure 4) needs to be large enough to sustain the supply over the Initialise period and the first few cycles of Run mode, until the auxiliary rail voltage supply is established.

Figure 5: VDD Pin Waveform (V<sub>DD</sub>)

| Mode       | Description                                                                                                                                                                                                                                                                                                                                                                             |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Sleep      | From initial application of power or from Run mode if $V_{DD}$ falls below $\Delta V_{DDSLEEP}$ below $V_{DDREG}$ , the controller changes to Sleep mode. Non-essential controller circuits are powered down and the external switching transistor (Q1) is held off. Exit from Sleep mode occurs when $V_{DD}$ rises above $V_{DDRUN}$ and the controller moves to the Initialise mode. |

| Initialise | When Initialise mode is entered, internal controller circuits are initialised and two clock cycles are issued, after which the controller changes from Initialise to Run mode.                                                                                                                                                                                                          |

| Run        | Converter operation continues. The shunt regulator controls $V_{DD}$ to $V_{DDREG}$ . If $V_{DD}$ falls $\Delta V_{DDSLEEP}$ below $V_{DDREG}$ , the controller ceases power conversion and reverts to Sleep mode.                                                                                                                                                                      |

Table 1: Summary of Controller Modes

## Constant Voltage and Constant Current (CV/CC) Operation

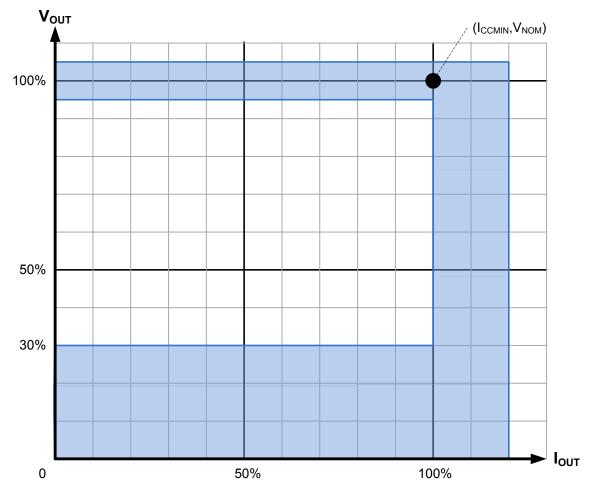

The C2163PX2 controller achieves constant voltage and constant current output within tight limits without the need for any secondary sensing components, by sensing the primary side waveforms of transformer voltage and primary switch current. Figure 6 shows the output characteristics of a typical adapter implemented with the C2163PX2.

Figure 6: Achievable Adapter Output Characteristic Using C2163PX2

## **Switching Waveforms**

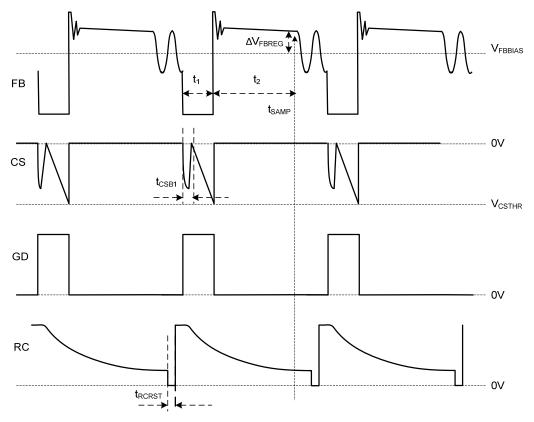

Typical switching waveforms for the FB, CS and RC inputs are shown with the GD output in Figure 7.

Figure 7: Typical Waveforms: GD, FB, CS, RC pins

## Constant Voltage (CV) Regulation

Constant voltage regulation is achieved by sensing the FB input, which is AC coupled to the auxiliary winding of the transformer, as shown in Figure 4. The FB pin is internally biased to  $V_{\text{FBBIAS}}$ . A typical voltage waveform seen on this pin is shown in Figure 7.

The waveform is analysed and sampled at  $t_{SAMP}$  to derive an estimate of the reflected output voltage. The  $t_{SAMP}$  point is identified by the change in slope of the transformer auxiliary winding waveform (as sensed by the FB input) immediately prior to the zero crossing. The difference between the sampled voltage and the FB regulation voltage ( $\Delta V_{FBREG}$ ) is used to derive the system power demand and close the voltage control loop.

The regulated output voltage is determined by the selection of the potential divider resistors (Rfb1, Rfb2 in Figure 4) and the chosen transformer turns ratio. The total parallel combination of these resistors should be typically less than 120  $\Omega$  to prevent unwanted effects of stray capacitance. The tolerances of Rfb1 and Rfb2 affect output voltage regulation and would typically be chosen to be 1% or better. Values of Rfb1, Rfb2 and Cfb are given by the equations:

$$Rfb2 = 120 \Omega$$

$$Cfb = 47nF \pm 20\%$$

$$Rfb1 = \frac{Rfb2 \left(V_{OUTNOM} \frac{N_F}{N_S} - \Delta V_{FBREG}\right)}{\Delta V_{FBREG}}$$

## **Constant Current (CC) Regulation**

The current flowing through the transformer primary winding is sensed on the CS pin by the voltage generated across the current sensing resistor (Rcs in Figure 4). The voltage seen on the CS pin is a negative-going voltage waveform as shown in Figure 7. When the voltage on the CS pin exceeds a (negative) threshold  $V_{\text{CSTHR}}$ , the primary switching transistor is rapidly turned off. The internal loop controller regulates the CS voltage threshold ( $V_{\text{CSTHR}}$  in Figure 7) between  $V_{\text{CSMIN}}$  and  $V_{\text{CSMAX}}$ , based on the average CS input voltage and CC regulation set point ( $V_{\text{CSCC}}$ ) to achieve constant output current regulation. Blanking is provided for a period of  $t_{\text{CSB1}}$  to prevent false triggering due to leading edge spikes in the waveform.

Constant Current regulation is determined by the transformer turns ratio and the value of Rcs. The value of Rcs is determined by the required output current ( $I_{OUT}$ ) and transformer primary-secondary turns ratio ( $N_P/N_S$ ) according to the approximation:

$$Rcs \approx \left(\frac{N_{P}}{N_{S}}\right) \left(\frac{V_{CSCC}}{I_{OUT}}\right)$$

The tolerance of Rcs has a direct relationship to the accuracy of the output current limit and is typically chosen to be 1%.

### **Cable Drop Compensation**

The C2163PX2 controller adjusts the output voltage of the power supply to compensate for the voltage drop seen in the output cable. The amount of compensation applied ( $G_{CAB}$ ) is programmed by the value of the capacitor connected to the RC pin, (Cosc in Figure 4) according to the equation:

$$Cosc = \frac{K_{CAB}}{G_{CAB}}$$

## **Drive Pulse and Frequency Modulation**

The C2163PX2 controls both the primary switch peak current and the switching frequency in response to the power demanded by the application load. The controller ensures that power conversion is performed in discontinuous conduction mode (DCM) at all times. The switching frequency is varied depending on the actual power demand. The maximum switching frequency is set by  $F_{MAX}$ . The C2163PX2 controller does not have a minimum switching frequency. The full-load frequency  $F_{MAX}$  (chosen in the range 40 to 66 kHz) is set by the equations:

$$F_{MAX} = \frac{1}{K_{OSC} \cdot \tau_{RCOSC} + t_{RCRST}}$$

The oscillator time constant  $\tau_{RCOSC}$  is controlled by external components Cosc, Rosc so that:

$$\tau_{RCOSC} = R_{OSC}.C_{OSC}$$

#### **Duty Cycle Control**

The maximum duty cycle is set by the primary-secondary turns ratio ( $N_P/N_S$ ) of the transformer (typically 6.7:1 for a 12 V output). For a typical universal input offline application, a maximum duty cycle of 50% is chosen for the minimum rectified supply voltage (typically 80  $V_{DC}$ ).

#### **Soft Switching**

Zero current (quasi-resonant) switching is used to minimise the switching losses in the primary switch, thereby increasing efficiency and introducing frequency jitter, to spread the RF emissions spectrum. The

primary switching BJT is turned on when the voltage across it is a minimum (as detected by the FB input), minimising the capacitive switching losses and reducing the RF emissions.

### **Cascode Switching**

The primary switch is connected in cascode configuration with a low voltage logic level MOSFET to ensure fast and efficient switching using low-cost high voltage bipolar transistors, e.g. STX13003, STBV42, TS13003, TS13005, MJE13003, MJE13005. The low voltage logic level MOSFET should have a maximum drain to source voltage,  $V_{DSS}$  of 15 - 30 V and low gate capacitance. Suitable MOSFETs include IRLML2402, SSS2202, NDS355.

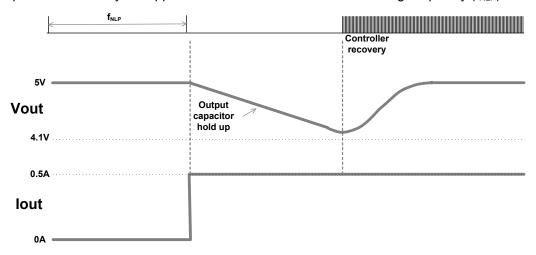

#### **Fast Load Step Response**

When a drop in output voltage is detected due to a large load step from no-load, the controller quickly ramps up output power. This prevents the output voltage from dropping further, as shown in Figure 8. The total voltage drop is determined by the application circuit and the no-load switching frequency ( $f_{NLP}$ ).

Figure 8: No-load to 0.5 A Load Step Recovery

#### **Protection Features**

#### **Short Circuit Protection**

In Short Circuit the output current is limited by the constant current regulation of the controller and will follow the adapter output characteristic as indicated in Figure 6.

#### Mains Under Voltage Protection (UVP) and Over Voltage Protection (OVP)

The regulated output voltage is reduced when the rectified input voltage falls outside the normal working voltage range, defined by  $V_{\text{UVP}}$  and  $V_{\text{OVP}}$ . The value is defined by the nominal output voltage ( $V_{\text{OUTNOM}}$ ), the primary-secondary turns ratio ( $N_P/N_S$ ) and other IC parameters by the equation:

$$V_{\text{UVP}} \approx V_{\text{OUTNOM}} \frac{N_{\text{P}}}{N_{\text{S}}} \frac{\left| \Delta V_{\text{FBUVP}} \right|}{\Delta V_{\text{FBREG}}} \qquad \qquad V_{\text{OVP}} \approx V_{\text{OUTNOM}} \frac{N_{\text{P}}}{N_{\text{S}}} \frac{V_{\text{FBBIAS}}}{\Delta V_{\text{FBREG}}}$$

#### **Over Temperature Protection (OTP)**

The on-chip OTP is triggered if the junction temperature exceeds the threshold  $T_{SH}$ , shutting down the controller. To prevent possible damage to the PCB, the OTP prevents restarting until the temperature has dropped to  $(T_{SH} - T_{SHHYST})$ .

### **Primary Switch Over Current Protection (OCP)**

The primary switch is turned off if the primary switch current exceeds a preset threshold  $V_{CSMAX}$ , as sensed by the CS input, subject to the minimum on-time  $T_{ONMIN}$ . This gives pulse by pulse over current protection.

#### **Output Over Voltage Protection**

The switching operation is inhibited when the output voltage is above the nominal range, defined by  $V_{\text{OUTOVP}}$ . The value is defined by the nominal output voltage ( $V_{\text{OUTNOM}}$ ) and the feedback OVP to regulation level ratio:

$$V_{\text{OUTOVP}} = V_{\text{OUTNOM}} \cdot G_{\text{FBOVP}}$$

## **ABSOLUTE MAXIMUM RATINGS**

CAUTION: Permanent damage may result if a device is subjected to operating conditions at or in excess of absolute maximum ratings.

| Parameter            | Symbol          | Condition                               | Min  | Max                   | Unit |

|----------------------|-----------------|-----------------------------------------|------|-----------------------|------|

| Supply voltage       | $V_{DD}$        |                                         | -0.5 | 4.5                   | V    |

| Supply current       | I <sub>DD</sub> |                                         | -20  | 90                    | mA   |

| FB input voltage     | V <sub>FB</sub> |                                         | -0.5 | V <sub>DD</sub> + 0.5 | V    |

| CS input voltage     | V <sub>CS</sub> | DC condition                            | -0.5 | V <sub>DD</sub> + 0.5 | V    |

| RC input voltage     | V <sub>RC</sub> | DC condition —                          |      | V <sub>DD</sub> + 0.5 | V    |

| GD pin voltage       | $V_{GD}$        |                                         | -0.5 | V <sub>DD</sub> + 0.5 | V    |

| FB input current     | I <sub>FB</sub> |                                         | -20  | 20                    | mA   |

| CS input current     | I <sub>CS</sub> |                                         | -20  | 20                    | mA   |

| RC input current     | I <sub>RC</sub> |                                         | -35  | 250                   | mA   |

| GD pin current       | $I_{GD}$        |                                         | -150 | 150                   | mA   |

| Junction temperature | TJ              |                                         | -25  | 125                   | °C   |

| Storage temperature  | T <sub>P</sub>  |                                         | -40  | 150                   | °C   |

| Lead temperature     | TL              | Soldering, 10 s                         |      | 260                   | °C   |

| ESD withstand        |                 | Human body model, JESD22-A114           |      | 2                     | kV   |

| ESD WILLISTATIO      |                 | Charged device Model, ANSI-ESD-STM5.3.1 |      | 500                   | V    |

## NORMAL OPERATING CONDITIONS

Unless otherwise stated, electrical characteristics are defined over the range of normal operating conditions. Functionality and performance is not defined when a device is subjected to conditions outside this range and device reliability may be compromised.

| Parameter                                    | Symbol           | Condition                        | Min | Тур  | Max | Unit |

|----------------------------------------------|------------------|----------------------------------|-----|------|-----|------|

| Supply voltage                               | $V_{DD}$         |                                  | 3.1 | 3.45 | 3.6 | V    |

| Supply current                               | I <sub>DD</sub>  |                                  |     |      | 30  | mA   |

| Full power switching frequency               | F <sub>NOM</sub> | Full-load, application dependent | 36  | 40   | 66  | kHz  |

| Transformer resonance frequency (in-circuit) | F <sub>RES</sub> |                                  | 300 |      |     | kHz  |

| Junction temperature                         | $T_J$            |                                  | -25 | 25   | 105 | °C   |

## **ELECTRICAL CHARACTERISTICS**

Unless otherwise stated:

- 1. Min and Max electrical characteristics apply over normal operating conditions.

- 2. Typical electrical characteristics apply at  $T_J = T_{J(TYP)}$  and  $I_{DD} = I_{DDREG(TYP)}$ .

- 3. The chip is operating in Run mode.

- 4. Voltages are specified relative to the GND pin.

#### **VDD Pin**

| Parameter           | Symbol               | Condition                                                      | Min | Тур                    | Max  | Unit |

|---------------------|----------------------|----------------------------------------------------------------|-----|------------------------|------|------|

|                     | $V_{\text{DDRUN}}$   | To enter Initialise mode                                       | 3.6 | 4.0                    | 4.45 | V    |

| Supply voltage      | $V_{DDREG}$          | In Run mode                                                    | 3.3 | 3.45                   | 3.6  | V    |

|                     | $\Delta V_{DDSLEEP}$ | To enter Sleep mode (measured relative to V <sub>DDREG</sub> ) |     | -600                   |      | mV   |

| Supply current      | I <sub>DDREG</sub>   | In Run mode                                                    |     |                        | 2.4  | mA   |

| Зирргу синен        | I <sub>DDSLEEP</sub> | In Sleep mode                                                  |     |                        | 5.5  | μΑ   |

| Initialisation time | t <sub>INIT</sub>    |                                                                |     | $3\tau_{\text{RCOSC}}$ |      | s    |

#### **FB Pin**

| Parameter                          | Symbol                          | Condition                                                           | Min  | Тур  | Max   | Unit  |

|------------------------------------|---------------------------------|---------------------------------------------------------------------|------|------|-------|-------|

| FB bias voltage                    | $V_{FBBIAS}$                    | Internal DC bias voltage                                            | 1.66 |      | 1.84  | V     |

| FB regulation level                | $\Delta V_{FBREG}$              | Measured relative to V <sub>FBBIAS</sub> T=25°C 394                 |      | 405  | 415.5 | mV    |

| FB slope detection threshold       | $\Delta V_{\text{FB}}/\Delta t$ |                                                                     | -280 | -200 | -120  | mV/μs |

| FB input resistance                | R <sub>FBIN</sub>               | Effective input resistance<br>0 < V <sub>FB</sub> < V <sub>DD</sub> |      | 50   |       | kΩ    |

| FB initialisation current          | I <sub>FBINIT</sub>             | V <sub>FB</sub> = 0 V                                               |      | -1.8 |       | mA    |

| FB OVP ratio                       | $G_{FBOVP}$                     |                                                                     | 1.4  |      | 1.8   |       |

| FB UVP comparator threshold offset | $\Delta V$ FBUVP                | Measured relative to V <sub>FBBIAS</sub>                            |      | -135 |       | mV    |

## **RC Pin**

| Parameter                        | Symbol             | Condition              | Min | Тур  | Max | Unit |

|----------------------------------|--------------------|------------------------|-----|------|-----|------|

| Maximum switching frequency      | F <sub>MAX</sub>   |                        | 30  |      | 66  | kHz  |

| Maximum frequency control factor | Kosc               | 220 pF < Cosc < 2.2 nF |     | 0.31 |     |      |

| Cable compensation               | G <sub>CAB</sub>   | 1 p                    | 1   |      | 10  | %    |

| Cable compensation factor        | K <sub>CAB</sub>   |                        |     | 20   |     | pF   |

| Oscillator reset time            | t <sub>RCRST</sub> |                        |     | 2.7  | 3.8 | μs   |

## **CS Pin**

| Parameter                                 | Symbol              | Condition                                      |                                                                                                                                                               | Min   | Тур   | Max   | Unit |

|-------------------------------------------|---------------------|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|------|

| CS input minimum threshold                | V <sub>CSMIN</sub>  |                                                | Minimum load                                                                                                                                                  |       | -38   |       | mV   |

| CS input maximum threshold                | $V_{CSMAX}$         | Outside CS<br>blanking time                    | Over-current protection                                                                                                                                       |       | -182  |       | mV   |

| CS turn-off response time                 | tcsoff              | t <sub>CSB1</sub>                              | $ \begin{array}{l} \text{Step } \Delta V_{\text{CS}}\text{:} \\ V_{\text{CSMAX}} + 10 \text{ mV} \\ \text{to } V_{\text{CSMAX}} - 10 \text{ mV} \end{array} $ |       | 175   |       | ns   |

| CS Input Offset                           | $\Delta V_{CSOFF}$  |                                                |                                                                                                                                                               |       | 0     |       | μV   |

| CS Input Leakage Current                  | I <sub>CSLEAK</sub> | -0.2 V < V <sub>CS</sub> < \                   | $I_{DD}$                                                                                                                                                      | -10   |       | 10    | μΑ   |

| CS input limit for CC operation (average) | V <sub>cscc</sub>   | $F = 40$ kHz, $t_1 = t_2 = 12.5$ μs, $T=25$ °C |                                                                                                                                                               | -32.5 | -31.4 | -30.3 | mV   |

| Leading edge blanking time                | t <sub>CSB1</sub>   | See Figure 7                                   |                                                                                                                                                               |       | 400   |       | ns   |

## **GD Pin**

| Parameter             | Symbol              | Condition                                        | Min | Тур | Max | Unit |

|-----------------------|---------------------|--------------------------------------------------|-----|-----|-----|------|

| Gate drive rise time  | T <sub>GDRISE</sub> | C <sub>GATE</sub> = 1 nF; 10% - 90%              |     | 30  |     | ns   |

| Gate drive fall time  | T <sub>GDFALL</sub> | GATE - 1 IIF, 10% - 90%                          |     | 30  |     | ns   |

| Gate sourcing current | I <sub>SOURCE</sub> | $V_{GD}$ = 2.0 V, $V_{DD}$ = 3.3 V               |     | 65  |     | mA   |

| Gate sinking current  | I <sub>SINK</sub>   | V <sub>GD</sub> = 2.0 V, V <sub>DD</sub> = 3.3 V |     | 75  |     | mA   |

| Minimum on-time       | t <sub>ONMIN</sub>  |                                                  |     | 575 |     | ns   |

## THERMAL CIRCUIT PROTECTION

| Parameter                    | Symbol              | Condition           | Min | Тур | Max | Unit |

|------------------------------|---------------------|---------------------|-----|-----|-----|------|

| Thermal shutdown temperature | T <sub>SH</sub>     | At silicon junction | 105 | 115 | 125 | °C   |

| Thermal shutdown hysteresis  | T <sub>SHHYST</sub> | At silicon junction |     | 30  |     | °C   |

## PACKAGE THERMAL RESISTANCE CHARACTERISTICS

#### Conditions:

- 1. Controller IC mounted on typical PCB (1.6 mm thick, 35 µm copper, CEM1);

- 2.  $\theta_{JB}$  measured to pin terminal of device at the surface of the PCB.

| Package | Junction-to-board<br>θ <sub>JB</sub> (Typical) | Junction-to-ambient<br>θ <sub>JA</sub> (Typical) | Units  |

|---------|------------------------------------------------|--------------------------------------------------|--------|

| SOT23-6 | 60                                             | 170                                              | °C / W |

## PACKAGING AND ORDERING INFORMATION

## **Package Marking**

The SOT23-6 package is marked with a short code indicating type and production lot as shown in Figure 9.

Figure 9: SOT23-6 Package Marking

## **Ordering**

| Туре     | Package | Marking | Packing Form    | Shipping      |

|----------|---------|---------|-----------------|---------------|

| C2163DV2 | SOT23 6 | PRxx    | 7" Tape & Reel  | C2163PX2-TR7  |

| C2163PX2 | 30123-0 |         | 13" Tape & Reel | C2163PX2-TR13 |

For further package and ordering information, please contact CamSemi.

#### **DATASHEET STATUS**

The status of this Datasheet is shown in the footer. Always refer to the most current version.

| Datasheet<br>Status | Product<br>Status | Definition                                                                                                                                                                                                                                                                     |

|---------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Product preview     | In development    | The Datasheet contains target specifications relating to design and development of the described IC product. Application circuits are illustrative only. Specifications are subject to change without notice.                                                                  |

| Preliminary         | In qualification  | The Datasheet contains preliminary specifications relating to functionality and performance of the described IC product. Application circuits are illustrative only. Specifications are subject to change without notice.                                                      |

| Product data        | In production     | The Datasheet contains specifications relating to functionality and performance of the described IC product which are supported by testing during development and production. Application circuits are illustrative only. Specifications are subject to change without notice. |

#### CONTACT DETAILS

Cambridge Semiconductor Ltd St Andrew's House St Andrew's Road Cambridge CB4 1DL United Kingdom

Phone: +44 (0)1223 446450 Fax: +44 (0)1223 446451

Email: <u>sales.enquiries@camsemi.com</u>

Web: www.camsemi.com

#### **DISCLAIMER**

The product information provided herein is believed to be accurate and is provided on an "as is" basis. Cambridge Semiconductor Ltd (CamSemi) assumes no responsibility or liability for the direct or indirect consequences of use of the information in respect of any infringement of patents or other rights of third parties. Cambridge Semiconductor Ltd does not grant any licence under its patent or intellectual property rights or the rights of other parties.

Any application circuits described herein are for illustrative purposes only. In respect of any application of the product described herein Cambridge Semiconductor Ltd expressly disclaims all warranties of any kind, whether express or implied, including, but not limited to, the implied warranties of merchantability, fitness for a particular purpose and non-infringement of third party rights. No advice or information, whether oral or written, obtained from Cambridge Semiconductor Ltd shall create any warranty of any kind. Cambridge Semiconductor Ltd shall not be liable for any direct, indirect, incidental, special, consequential or exemplary damages, howsoever caused including but not limited to, damages for loss of profits, goodwill, use, data or other intangible losses.

The products and circuits described herein are subject to the usage conditions and end application exclusions as outlined in Cambridge Semiconductor Ltd Terms and Conditions of Sale which can be found at <a href="https://www.camsemi.com/legal">www.camsemi.com/legal</a>.

Cambridge Semiconductor Ltd reserves the right to change specifications without notice. To obtain the most current product information available visit <a href="https://www.camsemi.com">www.camsemi.com</a> or contact us at the address shown above.