# 500mA CMOS LDO Regulator

### **FEATURES**

- Guaranteed 500mA peak output current

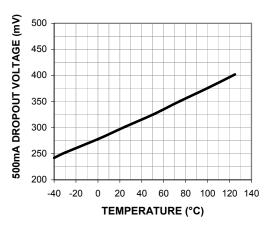

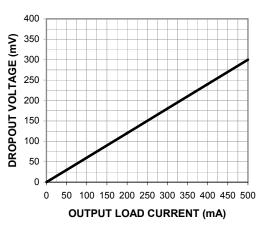

- Low dropout voltage of 300mV typical at 500mA

- Stable with ceramic output capacitor

- External 10nF bypass capacitor for low noise

- Quick-start feature

- Under voltage lockout

- No-load ground current of 55µA typical

- Full-load ground current of 85µA typical

- ±1.0% initial accuracy (V<sub>OUT</sub> ≥ 2.0V)

- ±2.0% accuracy over temperature (V<sub>OUT</sub> ≥ 2.0V)

- "Zero" current shutdown mode

- Current limit and thermal protection

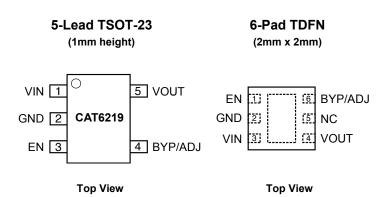

- 5-lead TSOT-23 and 6-pad TDFN packages

#### **APPLICATIONS**

- Cellular phones

- Battery-powered devices

- Consumer Electronics

#### DESCRIPTION

The CAT6219 is a 500mA CMOS low dropout regulator that provides fast response time during load current and line voltage changes.

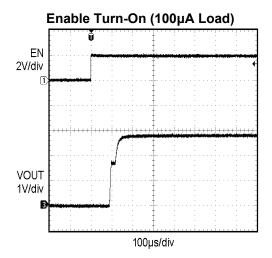

The quick-start feature allows the use of an external bypass capacitor to reduce the overall output noise without affecting the turn-on time of just 150µs.

With zero shutdown current and low ground current of 55µA typical, the CAT6219 is ideal for battery-operated devices with supply voltages from 2.3V to 5.5V. An internal under voltage lockout circuit disables the output at supply voltages under 2.15V typical.

The CAT6219 offers 1% initial accuracy and low dropout voltage, 300mV typical at 500mA. Stable operation is provided with a small value ceramic capacitor, reducing required board space and component cost.

Other features include current limit and thermal protection.

The LDO is available in fixed and adjustable output in the low profile (1mm max height) 5-lead TSOT23 and in the 6-pad 2mm x 2mm TDFN packages.

For Ordering Information details, see page 9.

#### PIN CONFIGURATION

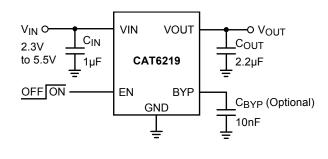

### TYPICAL APPLICATION CIRCUIT

## **PIN DESCRIPTIONS**

| Pin# | Name                        | Function                                                                     |  |

|------|-----------------------------|------------------------------------------------------------------------------|--|

| 1    | 1 VIN Supply voltage input. |                                                                              |  |

| 2    | 2 GND Ground reference.     |                                                                              |  |

| 3    | EN                          | Enable input (active high); a 2.5MΩ pull-down resistor is provided.          |  |

| 4    | BYP                         | Optional bypass capacitor connection for noise reduction and PSRR enhancing. |  |

| 4    | ADJ                         | Adjustable input. Feedback pin connected to resistor divider.                |  |

| 5    | VOUT                        | LDO Output Voltage.                                                          |  |

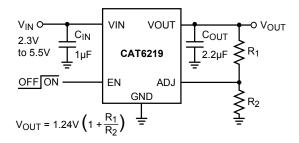

Figure 1. Adjustable Output LDO

#### PIN FUNCTION

**VIN** is the supply pin for the LDO. A small 1 $\mu$ F ceramic bypass capacitor is required between the V<sub>IN</sub> pin and ground near the device. When using longer connections to the power supply, C<sub>IN</sub> value can be increased without limit. The operating input voltage range is from 2.3V to 5.5V.

**EN** is the enable control logic (active high) for the regulator output. It has a  $2.5M\Omega$  pull-down resistor, which assures that if EN pin is left open, the circuit is disabled.

**VOUT** is the LDO regulator output. A small  $2.2\mu F$  ceramic bypass capacitor is required between the VOUT pin and ground. For better transient response, its value can be increased to  $4.7\mu F$ .

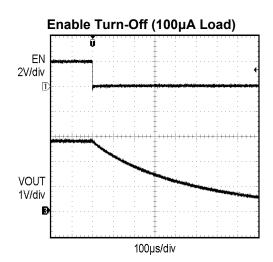

The capacitor should be located near the device. For the SOT23-5 package, a continuous 500mA output current may turn-on the thermal protection. A  $250\Omega$  internal shutdown switch discharges the output capacitor in the no-load condition.

**GND** is the ground reference for the LDO. The pin must be connected to the ground plane on the PCB.

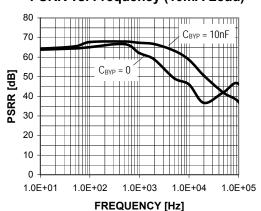

BYP is the reference bypass pin. An optional  $0.01\mu F$  capacitor can be connected between BYP pin and GND to reduce the output noise and enhance the PSRR at high frequency.

**ADJ** is the adjustable input pin for the adjustable LDO. The pin is connected to the resistor voltage divider.

#### ABSOLUTE MAXIMUM RATINGS (1)

| Parameter                                 | Rating                       | Unit |

|-------------------------------------------|------------------------------|------|

| V <sub>IN</sub>                           | 0 to 6.5                     | V    |

| V <sub>EN</sub> , V <sub>OUT</sub>        | -0.3 to V <sub>IN</sub> +0.3 | V    |

| Junction Temperature, T <sub>J</sub>      | +150                         | °C   |

| Power Dissipation, P <sub>D</sub>         | Internally Limited (2)       | mW   |

| Storage Temperature Range, T <sub>S</sub> | -65 to +150                  | °C   |

| Lead Temperature (soldering, 5 sec.)      | 260                          | °C   |

| ESD Rating (Human Body Model)             | 3                            | kV   |

# RECOMMENDED OPERATING CONDITIONS (3)

| Parameter                                           | Range                | Unit |

|-----------------------------------------------------|----------------------|------|

| V <sub>IN</sub>                                     | 2.3 to 5.5           | V    |

| V <sub>EN</sub>                                     | 0 to V <sub>IN</sub> | V    |

| Junction Temperature Range, T <sub>J</sub>          | -40 to +125          | °C   |

| Package Thermal Resistance (SOT23-5), $\theta_{JA}$ | 235                  | °C/W |

Typical application circuit with external components is shown on page 1.

- (1) Exceeding maximum rating may damage the device.

- (2) The maximum allowable power dissipation at any  $T_A$  (ambient temperature) is  $P_{Dmax} = (T_{Jmax} T_A) / \theta_{JA}$ . Exceeding the maximum allowable power dissipation will result in excessive die temperature, and the regulator will go into thermal shutdown.

- (3) The device is not guaranteed to work outside its operating rating.

# **ELECTRICAL OPERATING CHARACTERISTICS (1)**

$V_{\text{IN}}$  =  $V_{\text{OUT}}$  + 1.0V,  $V_{\text{EN}}$  = High,  $I_{\text{OUT}}$  = 100 $\mu$ A,  $C_{\text{IN}}$  = 1 $\mu$ F,  $C_{\text{OUT}}$  = 2.2 $\mu$ F, ambient temperature of 25°C (over recommended operating conditions unless specified otherwise). **Bold numbers** apply for the entire junction temperature range.

| Symbol                   | Parameter                                     | Conditions                                                 | Min  | Тур  | Max  | Unit   |  |

|--------------------------|-----------------------------------------------|------------------------------------------------------------|------|------|------|--------|--|

| \/                       | Output Valtage Accuracy                       | Initial accuracy for 1/ > 2.01/(4)                         | -1.0 |      | +1.0 | %      |  |

| V <sub>OUT-ACC</sub>     | Output Voltage Accuracy                       | Initial accuracy for $V_{OUT} \ge 2.0V^{(4)}$              | -2.0 |      | +2.0 |        |  |

| TC <sub>OUT</sub>        | Output Voltage Temp. Coefficient              |                                                            |      | 40   |      | ppm/°C |  |

| \/                       | Line Regulation                               | V <sub>IN</sub> = V <sub>OUT</sub> + 1.0V to 5.5V          | -0.2 | ±0.1 | +0.2 | %/V    |  |

| $V_{R-LINE}$             | Line Regulation                               |                                                            | -0.4 |      | +0.4 |        |  |

| \/                       | Load Pogulation                               | - 100 to 500 mA                                            |      | 1    | 1.5  | - %    |  |

| V <sub>R-LOAD</sub> Load | oad Regulation                                | I <sub>OUT</sub> = 100μA to 500 mA                         |      |      | 2    |        |  |

| $V_{DROP}$               | Dropout Voltage (2)                           | L = 500mA                                                  |      | 300  | 400  | mV     |  |

| V DROP                   | Jiopout voltage '                             | I <sub>OUT</sub> = 500mA                                   |      |      | 500  |        |  |

|                          | Ground Current                                | I <sub>OUT</sub> = 0μA                                     |      | 55   | 75   | μΑ     |  |

| $I_{GND}$                |                                               | 1001 - ΟμΑ                                                 |      |      | 90   |        |  |

|                          |                                               | I <sub>OUT</sub> = 500mA                                   |      | 85   |      |        |  |

| 1                        | Shutdown Ground Current                       | V <sub>EN</sub> < 0.4V                                     |      |      | 1    | μA     |  |

| I <sub>GND-SD</sub> Sh   | Shutdown Ground Current                       | V <sub>EN</sub> < 0.4V                                     |      |      | 2    |        |  |

| PSRR Powe                | Power Supply Rejection Ratio                  | $f = 1kHz$ , $C_{BYP} = 10nF$                              |      | 64   |      | - dB   |  |

| FORK                     | Power Supply Rejection Ratio                  | $f = 20kHz$ , $C_{BYP} = 10nF$                             |      | 54   |      | ub     |  |

| I <sub>SC</sub>          | Output short circuit current limit            | V <sub>OUT</sub> = 0V                                      | 600  | 800  |      | mA     |  |

| $T_ON$                   | Turn-On Time                                  | C <sub>BYP</sub> = 10nF                                    |      | 150  |      | μs     |  |

| $e_N$                    | Output Noise Voltage (3)                      | BW = 10Hz to 100kHz                                        |      | 45   |      | μVrms  |  |

| $R_{\text{OUT-SH}}$      | Shutdown Switch Resistance                    |                                                            |      | 250  |      | Ω      |  |

| $R_{\text{EN}}$          | Enable pull-down resistor                     |                                                            |      | 2.5  |      | ΜΩ     |  |

| $V_{\text{IN-UVLO}}$     | Under voltage lockout threshold               |                                                            |      | 2.15 |      | V      |  |

| ESR                      | C <sub>OUT</sub> equivalent series resistance |                                                            | 5    |      | 500  | mΩ     |  |

| $V_{ADJ}$                | Adjustable input voltage                      | I <sub>OUT</sub> = 100μA                                   | 1.2  | 1.24 | 1.27 | V      |  |

| Enable Ir                | put                                           |                                                            |      |      |      |        |  |

| V <sub>HI</sub> Lo       | Logic High Level                              | V <sub>IN</sub> = 2.3 to 5.5V                              | 1.8  |      |      |        |  |

|                          |                                               | $V_{IN}$ = 2.3 to 5.5V, 0°C to +125°C junction temperature | 1.6  |      |      | V      |  |

| $V_{LO}$                 | Logic Low Level                               | V <sub>IN</sub> = 2.3 to 5.5V                              |      |      | 0.4  | V      |  |

| I <sub>EN</sub>          | Fachla land Course                            | V <sub>EN</sub> = 0.4V                                     |      | 0.15 | 1    | μA     |  |

|                          | Enable Input Current                          | $V_{EN} = V_{IN}$                                          |      | 1.5  | 4    |        |  |

| Thermal Protection       |                                               |                                                            |      |      |      |        |  |

| T <sub>SD</sub>          | Thermal Shutdown                              |                                                            |      | 160  |      | °C     |  |

| T <sub>HYS</sub>         | Thermal Hysteresis                            |                                                            |      | 10   |      | °C     |  |

- (1) Specification for 2.85V output version unless specified otherwise.

- (2) Dropout voltage is defined as the input-to-output differential at which the output voltage drops 2% below its nominal value measured at 1V differential. During test, the input voltage stays always above the minimum 2.3V.

- (3) Specification for 1.8V output version.

- (4) For VOUT < 2.0V, the initial accuracy is  $\pm 2\%$  and across temperature  $\pm 3\%$ .

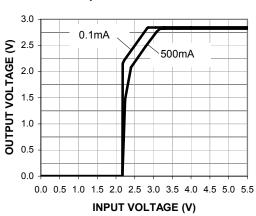

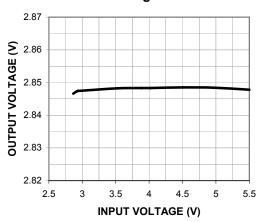

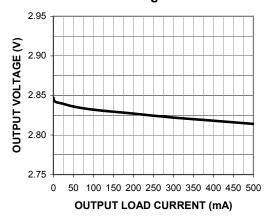

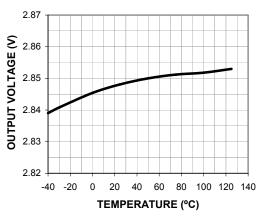

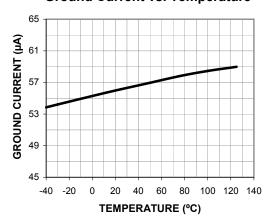

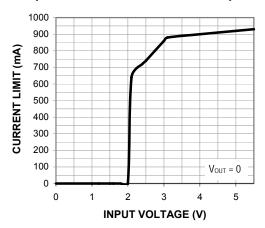

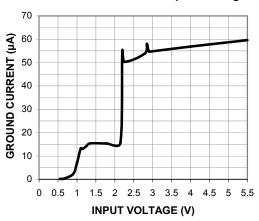

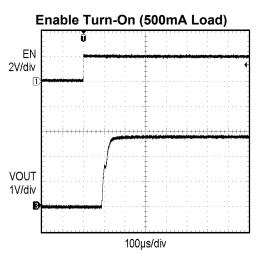

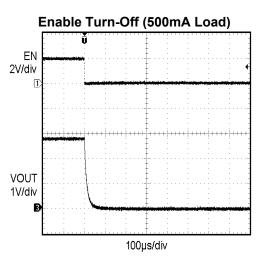

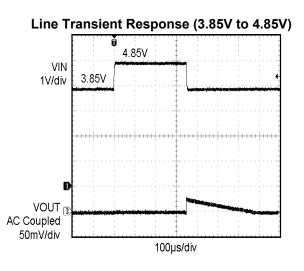

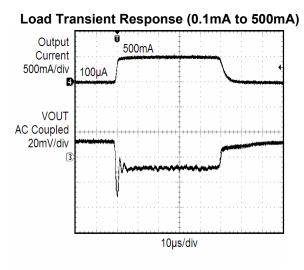

# TYPICAL CHARACTERISTICS (shown for 2.85V output version)

$V_{IN}$  = 3.85V,  $I_{OUT}$  = 100 $\mu$ A,  $C_{IN}$  = 1 $\mu$ F,  $C_{OUT}$  = 2.2 $\mu$ F,  $C_{BYP}$  = 10nF,  $T_A$  = 25°C unless otherwise specified.

### **Dropout Characteristics**

# Line Regulation

### **Load Regulation**

# **Output Voltage vs. Temperature**

#### **Ground Current vs. Load Current**

### **Ground Current vs. Temperature**

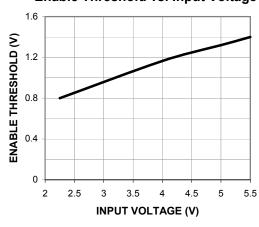

# TYPICAL CHARACTERISTICS (shown for 2.85V output option)

$V_{IN}$  = 3.85V,  $I_{OUT}$  = 100 $\mu$ A,  $C_{IN}$  = 1 $\mu$ F,  $C_{OUT}$  = 2.2 $\mu$ F,  $C_{BYP}$  = 10nF,  $T_A$  = 25°C unless otherwise specified.

# **Output Short-circuit Current vs. Input Voltage**

# **Ground Current vs. Input Voltage**

## **Dropout vs. Temperature (500mA Load)**

**Dropout vs. Load Current**

# **Enable Threshold vs. Input Voltage**

PSRR vs. Frequency (10mA Load)

# TRANSIENT CHARACTERISTICS (shown for 2.85V output option)

$V_{IN}$  = 3.85V,  $I_{OUT}$  = 100 $\mu$ A,  $C_{IN}$  = 1 $\mu$ F,  $C_{OUT}$  = 2.2 $\mu$ F,  $C_{BYP}$  = 10nF,  $T_A$  = 25°C unless otherwise specified.

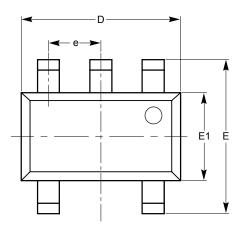

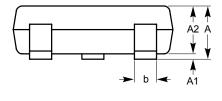

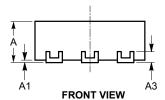

# **PACKAGE OUTLINE DRAWINGS**

TSOT-23 5-Lead (TD) (1)(2)

**TOP VIEW**

| SYMBOL | MIN      | NOM  | MAX  |

|--------|----------|------|------|

| Α      |          |      | 1.00 |

| A1     | 0.01     | 0.05 | 0.10 |

| A2     | 0.80     | 0.87 | 0.90 |

| b      | 0.30     |      | 0.45 |

| С      | 0.12     | 0.15 | 0.20 |

| D      | 2.90 BSC |      |      |

| Е      | 2.80 BSC |      |      |

| E1     | 1.60 BSC |      |      |

| е      | 0.95 TYP |      |      |

| L      | 0.30     | 0.40 | 0.50 |

| L1     | 0.60 REF |      |      |

| L2     | 0.25 BSC |      |      |

| θ      | 0°       |      | 8°   |

SIDE VIEW

**END VIEW**

For current Tape and Reel information, download the PDF file from: http://www.catsemi.com/documents/tapeandreel.pdf.

- (1) All dimensions are in millimeters. Angles in degrees.

- (2) Complies with JEDEC standard MO-193.

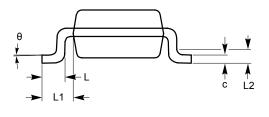

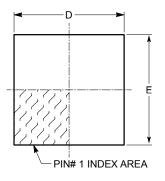

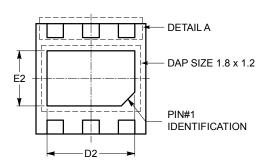

# TDFN 6-Pad 2mm x 2mm (VP5) $^{(1)(2)}$

**TOP VIEW**

SIDE VIEW

**BOTTOM VIEW**

| SYMBOL | MIN      | NOM  | MAX  |

|--------|----------|------|------|

| Α      | 0.70     | 0.75 | 0.80 |

| A1     | 0.00     | 0.02 | 0.05 |

| A3     | 0.20 REF |      |      |

| b      | 0.25     | 0.30 | 0.35 |

| D      | 1.90     | 2.00 | 2.10 |

| D2     | 1.50     | 1.60 | 1.70 |

| Е      | 1.90     | 2.00 | 2.10 |

| E2     | 0.90     | 1.00 | 1.10 |

| е      | 0.65 TYP |      |      |

| L      | 0.15     | 0.25 | 0.35 |

For current Tape and Reel information, download the PDF file from: http://www.catsemi.com/documents/tapeandreel.pdf.

- (1) All dimensions are in millimeters.

- (2) Complies with JEDEC standard MO-229.

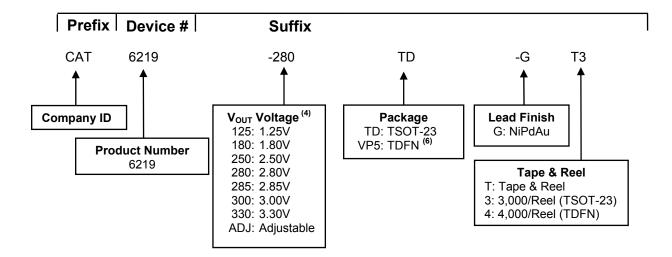

## **EXAMPLE OF ORDERING INFORMATION**

| Ordering Number       | V <sub>OUT</sub> Voltage <sup>(5)</sup> | Package   | Quantity per Reel |

|-----------------------|-----------------------------------------|-----------|-------------------|

| CAT6219-125TD-GT3     | 1.25V                                   | TSOT-23-5 | 3,000             |

| CAT6219-180TD-GT3     | 1.80V                                   | TSOT-23-5 | 3,000             |

| CAT6219-250TD-GT3     | 2.50V                                   | TSOT-23-5 | 3,000             |

| CAT6219-280TD-GT3     | 2.80V                                   | TSOT-23-5 | 3,000             |

| CAT6219-285TD-GT3 (4) | 2.85V                                   | TSOT-23-5 | 3,000             |

| CAT6219-300TD-GT3     | 3.00V                                   | TSOT-23-5 | 3,000             |

| CAT6219-330TD-GT3     | 3.30V                                   | TSOT-23-5 | 3,000             |

| CAT6219-ADJTD-GT3     | 1.25V to 5V                             | TSOT-23-5 | 3,000             |

| CAT6219-330VP5-GT4    | 3.30V                                   | TDFN-6    | 4,000             |

For Product Top Mark Codes, click here: http://www.catsemi.com/techsupport/producttopmark.asp

- (1) All packages are RoHS-compliant (Lead-free, Halogen-free).

- (2) The standard lead finish is NiPdAu pre-plated (PPF) lead frames.

- (3) The device used in the above example is a CAT6219-280TD-GT3 (V<sub>OUT</sub> = 2.80V, in a TSOT-23 package, NiPdAu, Tape & Reel, 3,000/Reel).

- (4) Standard voltages are 1.80V, 2.80V and 3.30V. For other voltage options, please contact your nearest Catalyst Semiconductor Sales office.

- (5) All output voltage options have the same marking.

- (6) Contact factory for availability.

- (7) Package Marking for CAT6219 family is "RV.

#### **REVISION HISTORY**

| Date          | Rev. | Reason                                                                                                          |  |

|---------------|------|-----------------------------------------------------------------------------------------------------------------|--|

| 20-Apr-07     | Α    | Initial Release                                                                                                 |  |

| 07-Nov-07     | В    | Update Package Outline Drawings Update Example of Ordering Information Add "MD-" to Document Number             |  |

| 08-Feb-08     | С    | Update Electrical Operating Characteristics                                                                     |  |

| 20-May-08 D l |      | Add Adjustable and other voltage options Update Package Outline Drawing – TDFN 6-Pad Add link to Top Mark Codes |  |

#### Copyrights, Trademarks and Patents

© Catalyst Semiconductor, Inc.

Trademarks and registered trademarks of Catalyst Semiconductor include each of the following: Adaptive Analog™, Beyond Memory™, DPP™, EZDim™, LDD™, MiniPot™, Quad-Mode™ and Quantum Charge Programmable™

Catalyst Semiconductor has been issued U.S. and foreign patents and has patent applications pending that protect its products.

CATALYST SEMICONDUCTOR MAKES NO WARRANTY, REPRESENTATION OR GUARANTEE, EXPRESS OR IMPLIED, REGARDING THE SUITABILITY OF ITS PRODUCTS FOR ANY PARTICULAR PURPOSE, NOR THAT THE USE OF ITS PRODUCTS WILL NOT INFRINGE ITS INTELLECTUAL PROPERTY RIGHTS OR THE RIGHTS OF THIRD PARTIES WITH RESPECT TO ANY PARTICULAR USE OR APPLICATION AND SPECIFICALLY DISCLAIMS ANY AND ALL LIABILITY ARISING OUT OF ANY SUCH USE OR APPLICATION, INCLUDING BUT NOT LIMITED TO, CONSEQUENTIAL OR INCIDENTAL DAMAGES.

Catalyst Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Catalyst Semiconductor product could create a situation where personal injury or death may occur.

Catalyst Semiconductor reserves the right to make changes to or discontinue any product or service described herein without notice. Products with data sheets labeled "Advance Information" or "Preliminary" and other products described herein may not be in production or offered for sale.

Catalyst Semiconductor advises customers to obtain the current version of the relevant product information before placing orders. Circuit diagrams illustrate typical semiconductor applications and may not be complete.

Catalyst Semiconductor, Inc. Corporate Headquarters 2975 Stender Way Santa Clara, CA 95054 Phone: 408.542.1000

Fax: 408.542.1200 www.catsemi.com

Document No: MD-10009

Revision: D

Issue date: 05/20/08