# CDK3404

# 8-bit, 180MSPS, Triple Video DACs

#### ww.datasheet4u.com

# FEATURES

- 8-bit resolution, 180MSPS

- ±2.5% gain matching

- ±0.5% linearity error

- Sync and blank controls

- 1.0V<sub>pp</sub> video into 37.50 or 750 load

- Internal bandgap voltage reference

- Low glitch energy

- Single +3.3V power supply

#### **APPLICATIONS**

- Video signal conversion

- RGB

- YCrCr

- Composite, Y, C

- Multimedia systems

- Image processing

- PC Graphics

# **General Description**

CDK3404 is a low-cost triple D/A converters that are tailored to fit graphics and video applications where speed is critical.

CMOS-level inputs are converted to analog current outputs that can drive 25-37.5 $\Omega$  loads corresponding to doubly-terminated 50-75 $\Omega$  loads. A sync current following  $\overline{\text{SYNC}}$  input timing is added to the  $IO_G$  output.  $\overline{\text{BLANK}}$  will override RGB inputs, setting  $IO_G$ ,  $IO_B$  and  $IO_R$  currents to zero when  $\overline{\text{BLANK}} = L$ . Although appropriate for many applications, the internal 1.25V reference voltage can be overridden by the  $V_{REF}$  input.

Few external components are required, just the current reference resistor, current output load resistors, bypass capacitors, and decoupling capacitors.

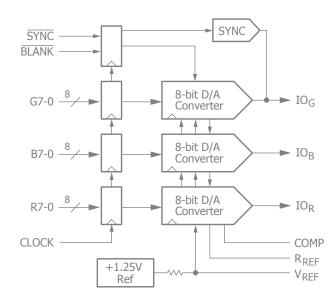

Package is a 48-lead TQFP. Fabrication technology is CMOS. Performance is guaranteed from -40°C to +125°C.

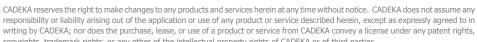

# **Block Diagram**

# **Ordering Information**

|   | Part Number   | Package | Pb-Free | RoHS Compliant | Operating Temp Range | Packaging Method | Package Quantity |

|---|---------------|---------|---------|----------------|----------------------|------------------|------------------|

|   | CDK3404CTQ48  | TQFP-48 | Yes     | Yes            | -40°C to +125°C      | Tray             | 250              |

| ( | CDK3404CTQ48Y | TQFP-48 | Yes     | Yes            | -40°C to +125°C      | Tray             | 1,250            |

Moisture sensitivity level for all parts is MSL-3.

# Pin Configuration

TQFP-48

# Pin Assignments

| Pin No.                             | Pin Name            | Description                    |  |  |  |  |  |

|-------------------------------------|---------------------|--------------------------------|--|--|--|--|--|

| Clock and F                         | Clock and Pixel I/O |                                |  |  |  |  |  |

| 26                                  | CLK                 | Clock Input                    |  |  |  |  |  |

| 47-40                               | R7-0                | Red Pixel Data Inputs          |  |  |  |  |  |

| 9–2                                 | G7-0                | Green Pixel Data Inputs        |  |  |  |  |  |

| 23–16                               | B7-0                | Blue Pixel Data Inputs         |  |  |  |  |  |

| Controls                            | Controls            |                                |  |  |  |  |  |

| 11                                  | SYNC                | Sync Pulse Input               |  |  |  |  |  |

| 10                                  | BLANK               | Blanking Input                 |  |  |  |  |  |

| Video Outp                          | uts                 |                                |  |  |  |  |  |

| 33                                  | IOR                 | Red Current Output             |  |  |  |  |  |

| 32                                  | IOG                 | Green Current Output           |  |  |  |  |  |

| 29                                  | IOB                 | Blue Current Output            |  |  |  |  |  |

| Voltage Re                          | ference             |                                |  |  |  |  |  |

| 35                                  | V <sub>REF</sub>    | Voltage Reference Output/Input |  |  |  |  |  |

| 36                                  | R <sub>REF</sub>    | Current-Setting Resistor       |  |  |  |  |  |

| 34                                  | COMP                | Compensation Capacitor         |  |  |  |  |  |

| Power and                           | Ground              |                                |  |  |  |  |  |

| 30, 31                              | V <sub>DDA</sub>    | Analog Power Supply            |  |  |  |  |  |

| 12                                  | V <sub>DDD</sub>    | Digital Power Supply           |  |  |  |  |  |

| 1, 14, 15,<br>27, 28, 38,<br>39, 48 | GND                 | Ground                         |  |  |  |  |  |

| 13, 24, 25,<br>37                   | NC                  | No Connect                     |  |  |  |  |  |

# **Absolute Maximum Ratings**

The safety of the device is not guaranteed when it is operated above the "Absolute Maximum Ratings". The device should not be operated at these "absolute" limits. Adhere to the "Recommended Operating Conditions" for proper device function. The information contained in the Electrical Characteristics tables and Typical Performance plots reflect the operating conditions noted on the tables and plots.

www.datasheet4u.com

| Min   | Max                                           | Unit                                                                                                                                                     |

|-------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |                                               |                                                                                                                                                          |

| -0.5  | 4.0                                           | V                                                                                                                                                        |

| -0.5  | 4.0                                           | V                                                                                                                                                        |

|       |                                               |                                                                                                                                                          |

| -0.5  | $V_{DDD} + 0.5$                               | V                                                                                                                                                        |

| -5.0  | 5.0                                           | mA                                                                                                                                                       |

|       |                                               |                                                                                                                                                          |

| -0.5  | V <sub>DDA</sub> + 0.5                        | V                                                                                                                                                        |

| -10.0 | 10.0                                          | mA                                                                                                                                                       |

|       |                                               |                                                                                                                                                          |

| -0.5  | V <sub>DD</sub> + 0.5                         | V                                                                                                                                                        |

| -60.0 | 60.0                                          | mA                                                                                                                                                       |

|       | unlimited                                     | sec                                                                                                                                                      |

|       | -0.5<br>-0.5<br>-0.5<br>-5.0<br>-0.5<br>-10.0 | -0.5 4.0<br>-0.5 4.0<br>-0.5 V <sub>DDD</sub> + 0.5<br>-5.0 5.0<br>-0.5 V <sub>DDA</sub> + 0.5<br>-10.0 10.0<br>-0.5 V <sub>DD</sub> + 0.5<br>-60.0 60.0 |

# **Reliability Information**

| Parameter                                     |  | Min | Max  | Unit |

|-----------------------------------------------|--|-----|------|------|

| Temperature                                   |  |     |      |      |

| Operating, Ambient                            |  | -40 | 125  | °C   |

| Junction                                      |  |     | 150  | °C   |

| Lead Soldering (10 seconds)                   |  |     | 300  | °C   |

| Vapor Phase Soldering (1 minute)              |  |     | 220  | °C   |

| Storage                                       |  | -65 | 150  | °C   |

| Package Thermal Resistance (θ <sub>JA</sub> ) |  | 6   | °C/W |      |

#### Notes:

- 1. Functional operation under any of these conditions is NOT implied.

Performance and reliability are guaranteed only if Operating Conditions are not exceeded.

- 2. Applied voltage must be current limited to specified range.

- 3. Forcing voltage must be limited to specified range.

- 4. Current is specified as conventional current flowing into the device.

# Recommended Operating Conditions

| Symbol           | Parameter                      | Min | Тур  | Max  | Unit |

|------------------|--------------------------------|-----|------|------|------|

| V <sub>DD</sub>  | Power Supply Voltage           | 3.0 | 3.3  | 3.6  | V    |

| V <sub>REF</sub> | Reference Voltage, External    | 1.0 | 1.25 | 1.5  | V    |

| C <sub>C</sub>   | Compensation Capacitor         |     | 0.1  |      | μF   |

| R <sub>L</sub>   | Output Load                    |     | 37.5 |      | Ω    |

| T <sub>A</sub>   | Ambient Temperature, Still Air | -40 |      | +125 | °C   |

www.DataSheet4U.com

### **Electrical Characteristics**

$(T_A = 25$ °C,  $V_{DDA} = V_{DDD} = 3.3$ V,  $V_{REF} = 1.25$ V,  $R_L = 37.5\Omega$ , unless otherwise noted)

| Symbol                  | Parameter                                         | Conditions                      | Min   | Тур  | Max   | Units |

|-------------------------|---------------------------------------------------|---------------------------------|-------|------|-------|-------|

| _                       |                                                   | T <sub>A</sub> = 25°C (1)       |       | 80   | 85    | mA    |

| $I_{DD}$                | Power Supply Current                              | $T_A = -40$ °C to $+125$ °C (2) |       |      | 95    | mA    |

| vvv <b>P.D</b> atasheet | 4u. <b>Total</b> Power Dissipation <sup>(2)</sup> | $T_A = -40$ °C to +125°C        |       |      | 300   | mW    |

| Digital Inputs          | 5                                                 |                                 |       |      |       |       |

| V <sub>IH</sub>         | Input Voltage, HIGH (1)                           | $T_A = -40$ °C to +125°C        | 2.5   |      |       | V     |

| V <sub>IL</sub>         | Input Voltage, LOW (1)                            | $T_A = -40$ °C to $+125$ °C     |       |      | 0.8   | V     |

| $I_{\mathrm{IH}}$       | Input Current, HIGH (1)                           | $T_A = -40$ °C to +125°C        | -1    |      | 1     | μΑ    |

| $I_{\mathrm{IL}}$       | Input Current, LOW (1)                            | $T_A = -40$ °C to +125°C        | -1    |      | 1     | μΑ    |

| C <sub>I</sub>          | Input Capacitance                                 |                                 |       | 4    |       | pF    |

| Analog Outpu            | uts                                               |                                 |       |      |       |       |

|                         | Output Current (1)                                |                                 |       |      | 30    | mA    |

| R <sub>O</sub>          | Output Resistance                                 |                                 |       | 40   |       | kΩ    |

| C <sub>O</sub>          | Output Capacitance                                |                                 |       | 7    |       | pF    |

| Reference Ou            | utput                                             |                                 |       |      |       |       |

| V <sub>REF</sub>        | Reference Voltage Output (1)                      | $T_A = -40$ °C to $+125$ °C     | 1.135 | 1.25 | 1.365 | V     |

#### Notes:

- 1. 100% tested at 25°C.

- 2. Parameter is guaranteed (but not tested) by design and characterization data.

# **Switching Characteristics**

$(T_A = 25^{\circ}C, V_{DDA} = V_{DDD} = 3.3V, V_{REF} = 1.25V, R_L = 37.5\Omega$ , unless otherwise noted)

| Symbol            | Parameter                           | Conditions                      | Min | Тур | Max | Units |

|-------------------|-------------------------------------|---------------------------------|-----|-----|-----|-------|

| Clock Input       |                                     | <u> </u>                        |     |     |     |       |

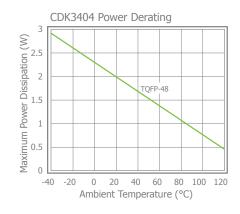

|                   | Conversion Rate (1)                 | $T_A = -40$ °C to +125°C        |     |     | 180 | MSPS  |

| t <sub>PWH</sub>  | Pulse-width HIGH (2)                | $T_A = -40$ °C to +125°C        | 2   |     |     | ns    |

| t <sub>PWL</sub>  | Pulse-width LOW (2)                 | $T_A = -40$ °C to +125°C        | 2   |     |     | ns    |

| Data Inputs       |                                     |                                 | ·   |     |     |       |

|                   | Cathori                             | T <sub>A</sub> = 25°C (1)       | 1.5 |     |     | ns    |

| $t_S$             | Setup                               | $T_A = -40$ °C to $+125$ °C (2) | 2   |     |     | ns    |

|                   |                                     | T <sub>A</sub> = 25°C (1)       |     |     | 0.6 | ns    |

| t <sub>H</sub>    | Hold                                | $T_A = -40$ °C to $+125$ °C (2) |     |     | 0.6 | ns    |

| Data Output       | ts, with 50Ω doubly terminated load |                                 |     |     |     |       |

| t <sub>D</sub>    | Clock to Output Delay               | $T_A = -40$ °C to +125°C        |     | 1.6 |     | ns    |

| t <sub>R</sub>    | Output Risetime                     | $T_A = -40$ °C to +125°C        |     | 0.6 |     | ns    |

| t <sub>F</sub>    | Output Falltime                     | $T_A = -40$ °C to +125°C        |     | 0.4 |     | ns    |

| t <sub>SET</sub>  | Settling Time                       |                                 |     | 2.5 |     | ns    |

| t <sub>SKEW</sub> | Output Skew                         |                                 |     | 0.3 |     | ns    |

#### Notes:

- 1. 100% production tested at +25°C.

- 2. Parameter is guaranteed (but not tested) by design and characterization data.

# **DC** Performance

$(T_A = 25$ °C,  $V_{DDA} = V_{DDD} = 3.3$ V,  $V_{REF} = 1.25$ V,  $R_L = 37.5\Omega$ , unless otherwise noted)

| Symbol        | Parameter                    | Conditions                                                                                                                    | Min   | Тур  | Max  | Units       |

|---------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-------|------|------|-------------|

|               | Resolution                   |                                                                                                                               | 8     |      |      | bits        |

| TAIL          | Take and Linearity Function  | T <sub>A</sub> = 25°C (1)                                                                                                     | -0.5  |      | 0.5  | LSB         |

| www.datasheet | Integral Linearity Error     | $T_A = -40$ °C to $+125$ °C (2)                                                                                               | -0.5  |      | 0.5  | LSB         |

| DAII          | Differential Linearity Func  | T <sub>A</sub> = 25°C (1)                                                                                                     | -0.5  |      | 0.5  | bits<br>LSB |

| DNL           | Differential Linearity Error | $T_A = -40$ °C to $+125$ °C (2)                                                                                               | -0.5  |      | 0.5  | LSB         |

|               | Offset Error                 | $T_A = -40$ °C to $+125$ °C (2)                                                                                               |       |      | 0.01 | %FS         |

|               | Gain Matching Error          | $T_A = -40$ °C to $+125$ °C (1)                                                                                               | -2.5  |      | 2.5  | %FS         |

|               | Absolute Gain Error          | $T_A = -40$ °C to $+125$ °C (1)                                                                                               | -3.5  |      | 3.5  | %FS         |

|               |                              | T <sub>A</sub> = 25°C (1)                                                                                                     | 18.0  | 18.7 | 19.4 | mA          |

|               |                              | $T_A = -40$ °C to $+125$ °C (2)                                                                                               | 18.0  | 18.7 | 19.4 | mA          |

|               | Full-Scale Output Current    | $T_{A} = -40^{\circ}\text{C}$ to $+125^{\circ}\text{C}$ , With internal reference. Trim RSET to calibrate full-scale current. |       | 18.7 |      | mA          |

| PSRR          | Power Supply Rejection Ratio | $T_A = -40$ °C to $+125$ °C (2)                                                                                               | -0.01 | 0    | 0.01 | %/%         |

#### Notes:

- 1. 100% production tested at +25°C.

- 2. Parameter is guaranteed (but not tested) by design and characterization data.

### **AC Performance**

$(T_A = 25$ °C,  $V_{DDA} = V_{DDD} = 3.3$ V,  $V_{REF} = 1.25$ V,  $R_L = 37.5\Omega$ , unless otherwise noted)

| Symbol         | Parameter            | Conditions | Min | Тур | Max | Units |  |  |

|----------------|----------------------|------------|-----|-----|-----|-------|--|--|

| Analog Outputs |                      |            |     |     |     |       |  |  |

|                | Glitch Energy        |            |     | 20  |     | pVsec |  |  |

|                | DAC-to-DAC Crosstalk |            |     | 30  |     | dB    |  |  |

|                | Data Feedthrough     |            |     | 50  |     | dB    |  |  |

|                | Clock Feedthrough    |            |     | 60  |     | dB    |  |  |

# Notes:

- 1. 100% production tested at +25°C.

- 2. Parameter is guaranteed (but not tested) by design and characterization data.

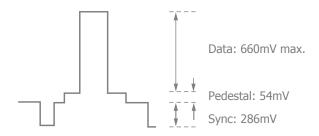

Table 1. Output Voltage vs. Input Code,  $\overline{SYNC}$  and  $\overline{BLANK}$ ,  $V_{REF}=1.25V$ ,  $R_{REF}=348\Omega$ ,  $R_L=37.5\Omega$

| RGB7-0 (MSBLSB)       |      | BLUE AND RED | ,        |      | GREEN |          |

|-----------------------|------|--------------|----------|------|-------|----------|

| KGD/-U (MSDLSD)       | SYNC | BLANK        | Vout (V) | SYNC | BLANK | Vout (V) |

| 1111 1111             | 1    | 1            | 0.700    | 1    | 1     | 1.007    |

| www.datasheet4u.com11 | 0    | 1            | 0.700    | 0    | 1     | 0.700    |

| 1111 1110             | 1    | 1            | 0.697    | 1    | 1     | 1.004    |

| 1111 1101             | 1    | 1            | 0.659    | 1    | 1     | 1.001    |

| •                     | •    | •            | •        | •    | •     | •        |

| •                     | •    | •            | •        | •    | •     | •        |

| 1000 0000             | 1    | 1            | 0.351    | 1    | 1     | 0.658    |

| 0111 1111             | 1    | 1            | 0.349    | 1    | 1     | 0.656    |

| 0111 1111             | 0    | 1            | 0.349    | 0    | 1     | 0.349    |

| •                     | •    | •            | •        | •    | •     | •        |

| •                     | •    | •            | •        | •    | •     | •        |

| 0000 0010             | 1    | 1            | 0.005    | 1    | 1     | 0.312    |

| 0000 0001             | 1    | 1            | 0.003    | 1    | 1     | 0.310    |

| 0000 0000             | 1    | 1            | 0.000    | 1    | 1     | 0.307    |

| 0000 0000             | 0    | 1            | 0.000    | 0    | 1     | 0.000    |

| XXXX XXXX             | 1    | 0            | 0.000    | 1    | 0     | 0.307    |

| XXXX XXXX             | 0    | 0            | 0.000    | 0    | 0     | 0.000    |

Figure 1. CDK3404 Timing Diagram

# **Functional Description**

Within the CDK3404 are three identical 8-bit D/A converters, each with a current source output. External loads are required to convert the current to voltage outputs. Data inputs RGB7-0 are overridden by the BLANK input. SYNC

www.胂tactivates/sync current from I<sub>OS</sub> for sync-on-green

video signals.

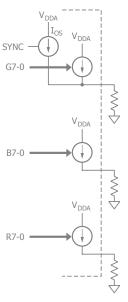

Figure 2. CDK3404 Current Source Structure

# **Digital Inputs**

Incoming GBR data is regsitered on the rising edge of the clock input, CLK. Analog outputs follow the rising edge of CLK after a delay,  $t_{\rm DO}$ .

#### Clock Input - CLK

Pixel data is registered on the rising edge of CLK. CLK should be driven by a dedicated buffer to avoid reflection induced jitter, overshoot, and undershoot.

### Pixel Data Inputs - R7-0, B7-0, G7-0

RGB digital inputs are registered on the rising edge of CLK.

# SYNC and BLANK

$\overline{\text{SYNC}}$  and  $\overline{\text{BLANK}}$  inputs control the output level (Figure 3 and Table 1, on the previous page) of the D/A converters during CRT retrace intervals.  $\overline{\text{BLANK}}$  forces the D/A outputs to the blanking level while  $\overline{\text{SYNC}} = \text{L}$  turns off a current source,  $I_{OS}$ , that is connected to the green D/A converter.  $\overline{\text{SYNC}} = \text{H}$  adds a 112/256 fraction of full-scale current to the green output.  $\overline{\text{SYNC}} = \text{L}$  extinguishes the sync current during the sync tip.

$\overline{\text{BLANK}}$  gates the D/A inputs. If  $\overline{\text{BLANK}} = \text{HIGH}$ , the D/A inputs control the output currents to be added to the output blanking level. If  $\overline{\text{BLANK}} = \text{Low}$ , data inputs and the pedestal are disabled.

Figure 3. Normal Output Levels

### Sync Pulse Input - SYNC

Bringing  $\overline{\text{SYNC}}$  LOW, disables a current source which superimposes a sync pulse on the  $IO_G$  output.  $\overline{\text{SYNC}}$  and pixel data are registered on the rising edge of CLK.  $\overline{\text{SYNC}}$  does not override any other data and should be used only during the blanking interval. If sync pulses are not required,  $\overline{\text{SYNC}}$  should be connected to GND.

### Blanking Input - BLANK

When  $\overline{\text{BLANK}}$  is LOW, pixel data inputs are ignored and the D/A converter outputs are driven to the blanking level.  $\overline{\text{BLANK}}$  is registered on the rising edge of CLK.

# D/A Outputs

Each D/A output is a current source from the  $V_{DDA}$  supply. Expressed in current units, the GBR transformation from data to current is as follows:

$G = G7-0 \& \overline{BLANK} + \overline{SYNC} * 112$

$B = B7-0 \& \overline{BLANK}$

R = R7-0 & BLANK

Typical LSB current step is  $73.2\mu$ A. To obtain a voltage output, a resistor must be connected to ground. Output voltage depends upon this external resistor, the reference voltage, and the value of the gain-setting resistor connected between R<sub>RFF</sub> and GND.

To implement a doubly-terminated  $75\Omega$  transmission line, a shunt  $75\Omega$  resistor should be placed adjacent to the analog output pin. With a terminated  $75\Omega$  line connected to the analog output, the load on the CDK3404 current source is  $37.5\Omega$ .

www.DataSheet4U.com

The CDK3404 may also be operated with a single  $75\Omega$ terminating resistor. To lower the output voltage swing to the desired range, the nominal value of the resistor on R<sub>REF</sub> should be doubled.

### R, G, and B Current Outputs - IO<sub>R</sub>, IO<sub>G</sub>, IO<sub>B</sub>

www.datasheet4u.com

Current source outputs can drive VESA VSIS, and RS-343A/SMPTE-170M compatible levels into doubly-terminated 75 $\Omega$  lines. Sync pulses can be added to the green output. When SYNC is HIGH, the current added to IO<sub>G</sub> is:

$IO_S = 2.33 (V_{REF}/R_{REF})$

### Current-Setting Resistor - R<sub>REF</sub>

Full-scale output current of each D/A converter is determined by the value of the resistor connected between R<sub>REF</sub> and GND. Nominal value of R<sub>REF</sub> is found from:

$$R_{RFF} = 5.31 (V_{RFF}/I_{FS})$$

where I<sub>FS</sub> is the full-scale (white) output current (in amps) from the D/A converter (without sync). Sync is  $0.439 * I_{FS}$ .

D/A full-scale (white) current may also be calculated from:

$$I_{FS} = V_{FS}/R_L$$

Where  $V_{FS}$  is the white voltage level and  $R_L$  is the total resistive load ( $\Omega$ ) on each D/A converter. V<sub>FS</sub> is the blank to full-scale voltage.

# Voltage Reference

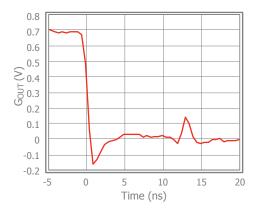

Full scale current is a multiple of the current I<sub>SFT</sub> through an external resistor, R<sub>SFT</sub> connected between the R<sub>RFF</sub> pin and GND. Voltage across R<sub>SET</sub> is the reference voltage, V<sub>REF.</sub> which can be derived from either the 1.25 volt internal bandgap reference or an external voltage reference connected to  $V_{REF}$ . To minimize noise, a  $0.1\mu F$  capacitor should be connected between  $V_{\text{REF}}$  and ground.  $I_{\text{SET}}$  is mirrored to each of the GBR output current sources. To minimize noise, a 0.1µF capacitor should be connected between the COMP pin and the analog supply voltage  $V_{DDA}$ .

### Voltage Reference Output/Input - V<sub>RFF</sub>

An internal voltage source of +1.25V is output on the  $V_{RFF}$ pin. An external +1.25V reference may be applied to override the internal reference. Decoupling V<sub>RFF</sub> to GND with a 0.1µF ceramic capacitor is required.

### Power and Ground

Required power is a single +3.3V supply. To minimize power supply induced noise, analog +3.3V should be connected to  $V_{DDD}$  and  $V_{DDA}$  pins with  $0.1\mu F$  and  $0.01\mu F$  decoupling capacitors placed adjacent to each  $V_{\mbox{\scriptsize DD}}$  pin or pin pair.

The high slew-rate of digital data makes capacitive coupling to the outputs of any D/A converter a potential problem. Since the digital signals contain high-frequency components of the CLK signal, as well as the video output signal, the resulting data feedthrough often looks like harmonic distortion or reduced signal-to-noise performance. All ground pins should be connected to a common solid ground plane for best performance.

# **Applications Dicussion**

Figure 5 (on the following page) illustrates a typical CDK3404 interface circuit. In this example, an optional 1.2V bandgap reference is connected to the  $V_{REF}$  output, overriding the internal voltage reference source.

www.datasheet4u.com

# Grounding

It is important that the CDK3404 power supply is well-regulated and free of high-frequency noise. Careful power supply decoupling will ensure the highest quality video signals at the output of the circuit. The CDK3404 has separate analog and digital circuits. To keep digital system noise from the D/A converter, it is recommended that power supply voltages come from the system analog power source and all ground connections (GND) be made to the analog ground plane. Power supply pins should be individually decoupled at the pin.

# Printed Circuit Board Layout

Designing with high-performance mixed-signal circuits demands printed circuits with ground planes. Overall system performance is strongly influenced by the board layout. Capacitive coupling from digital to analog circuits may result in poor D/A conversion. Consider the following suggestions when doing the layout:

- 1. Keep the critical analog traces ( $V_{REF}$ ,  $I_{REF}$ , COMP,  $IO_S$ ,  $IO_R$ ,  $IO_G$ ) as short as possible and as far as possible from all digital signals. The CDK3404 should be located near the board edge, close to the analog out-put connectors.

- 2. The power plane for the CDK3404 should be separate from that which supplies the digital circuitry. A single power plane should be used for all of the  $V_{DD}$  pins. If the power supply for the CDK3404 is the same as that of the system's digital circuitry, power to the CDK3404 should be decoupled with  $0.1\mu F$  and  $0.01\mu F$  capacitors and isolated with a ferrite bead.

- 3. The ground plane should be solid, not cross-hatched. Connections to the ground plane should have very short leads.

- 4. If the digital power supply has a dedicated power plane layer, it should not be placed under the CDK3404, the voltage reference, or the analog outputs. Capacitive coupling of digital power supply noise from this layer to the CDK3404 and its related analog circuitry can have an adverse effect on performance.

- 5. CLK should be handled carefully. Jitter and noise on this clock will degrade performance. Terminate the clock line carefully to eliminate overshoot and ringing.

# **Improved Transisiton Times**

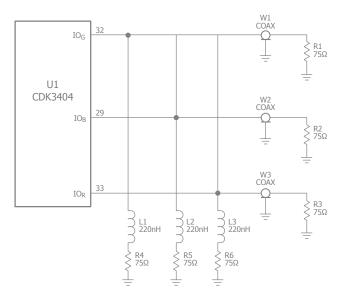

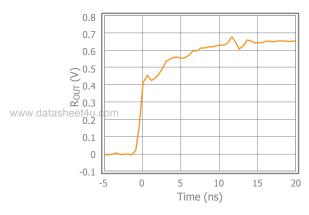

Output shunt capacitance dominates slowing of output transition times, whereas series inductance causes a small amount of ringing that affects overshoot and settling time. With a doubly terminated  $75\Omega$  load, transition times can be improved by matching the capacitive impedance output of the CDK3404. Output capacitance can be matched with a 220nH inductor in series with the  $75\Omega$  source termination.

Figure 4. Schematic, Transition Time Sharpening Circuit

A 220nH inductor trims the performance of a 4ft cable, quite well. In Figures xx through xx, the glitch at 12.5ns, is due to a reflection from the source. Not shown, are smaller glitches at 25 and 37.5ns, corresponding to secondary and tertiary reflections. Inductor values should be selected to match the length and type of the cable.

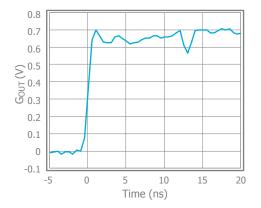

Figure 5. Unmatched t<sub>R</sub>

Figure 6. Matched t<sub>R</sub>

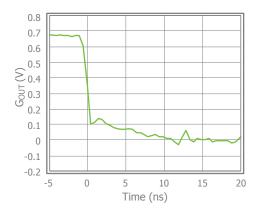

Figure 7. Unmatched t<sub>F</sub>

Figure 8. Matched t<sub>F</sub>

Figure 9. Typical Interface Circuit Diagram

Evaluation boards are available (CEB3400), contact CADEKA for more information.

### **Related Products**

- CDK3400/3401 Triple 10-bit 180MSPS DACs

- CDK3404 Triple 8-bit 180MSPS DAC

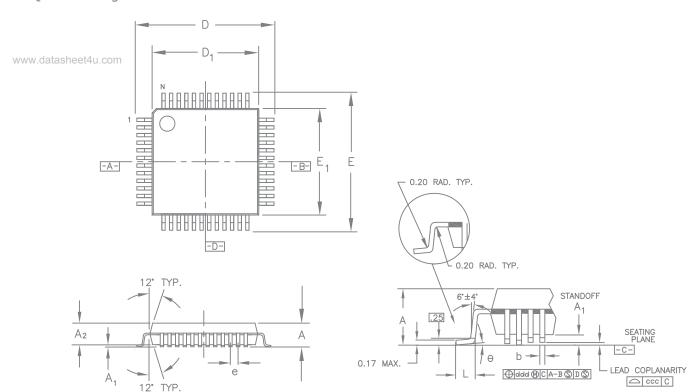

### **Mechanical Dimensions**

### LQFP-48 Package

| LEAD                          | COUNT   | 48            | BL            |  |

|-------------------------------|---------|---------------|---------------|--|

| DIMS.                         | TOL.    |               |               |  |

| A                             | MAX.    | 1.20          | 1.60          |  |

| A <sub>1</sub>                |         | .05 MIN.      | .15 MAX.      |  |

| A <sub>2</sub>                | ±.05    | 1.00          | 1.40          |  |

| D                             | ±.20    | 9.            | 00            |  |

| D <sub>1</sub>                | ±.10    | 7.00          |               |  |

| Е                             | ±.20    | 9.00          |               |  |

| E <sub>1</sub>                | ±.10    | 7.00          |               |  |

| L                             | +.15/10 | .6            | 0             |  |

| е                             | BASIC   | .5            | 50            |  |

| ф                             | ±.05    | .2            | 22            |  |

| Θ                             |         | 0°-           | -7°           |  |

| ddd                           | MAX.    | .08           |               |  |

| ccc                           | MAX.    | .С            | )8            |  |

| JEDEC REFERE<br>VARIATION DES |         | MS-026<br>ABC | MS-026<br>BBC |  |

#### NOTES.

- 1. All dimensions in mm.

- 2. Dimension shown are nominal with tolerances indicated.

- 3. Foot length 'L' is measured at gage plane 0.25mm above seating plane.

- 4. L/F: Eftec 64T Cu or equivalent, 0.127mm (0.005") thick

### For additional information regarding our products, please visit CADEKA at: cadeka.com

CADEKA Headquarters Loveland, Colorado

T: 970.663.5452

T: 877.663.5452 (toll free)

CADEKA, the CADEKA logo design, COMLINEAR and the COMLINEAR logo design are trademarks or registered trademarks of CADEKA Microcircuits LLC. All other brand and product names may be trademarks of their respective companies.

responsibility or liability arising out of the application or use of any product or service described herein, except as expressly agreed to in writing by CADEKA; nor does the purchase, lease, or use of a product or service from CADEKA convey a license under any patent rights, copyrights, trademark rights, or any other of the intellectual property rights of CADEKA or of third parties.