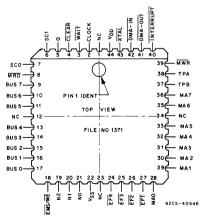

### TERMINAL ASSIGNMENT

| CLOCK  |         | 40 VDD        |

|--------|---------|---------------|

| WAIT   | 2       | 39 XTAL       |

| CLEAR  | 3       | 38 DMA IN     |

| Q —    | 4       | 37 DMA OUT    |

| SC I   | 5       | 36 INTERRUPT  |

| sco —  | 6       | 35 MWR        |

| MRD -  | 7       | 34 TPA        |

| BUS 7  | 8       | 33 TP8        |

| BUS 6  | 9       | 32 MA7        |

| BUS 5  | 10      | 31 MA6        |

| BUS 4  | 11      | 30- MA5       |

| BUS 3  | 12      | 29 MA4        |

| BUS 2  | 13      | 28 MA3        |

| BUS I  | 14      | 27 MA2        |

| BUS 0  | 15      | 26 MAI        |

| EMS/ME | 16      | 25 MAO        |

| N2     | 17      | 24 EFT        |

| NI     | 18      | 23 EF2        |

| NO     | 19      | 22 EF3        |

| Vss —  | 20      | 21 EF4        |

|        | L       |               |

|        | TOP VIE | EW 92CS-34980 |

# **CMOS 8-Bit Microcomputer With On-Chip RAM, ROM, and Counter/Timer**

**Performance Features:**

- Instruction time of 3.2 µs, -40 to +85° C

- 123 instructions-upwards sofware compatible with CDP1802, CDP1805A, and CDP1806A

- BCD arithmetic instructions

- Low-power IDLE mode

- Pin compatible with CDP1802, CDP1805A, and CDP1806A except for terminal 16 (terminal 18 for chip-carrier package)

- 64K-byte memory address capability = 16 x 16 matrix of on-board registers

- On-chip crystal or RC controlled oscillator

- 2 K bytes of on-chip ROM 64 bytes of on-chip RAM

The RCA-CDP1804AC is a functional and performance enhancement of the CDP1802, CDP1805A, and CDP1806A CMOS 8-bit register-oriented microprocessor series and is designed for use in a wide variety of generalpurpose applications.

.

The CDP1804AC hardware enhancements include a 2Kbyte ROM, a 64-byte RAM, and a 8-bit presettable down counter. The Counter/Timer, which generates an internal interrupt request, can be programmed for use in timebase, event-counting, and pulse-duration measurement applications. The Counter/Timer underflow output can also be directed to the Q output terminal.

The CDP1805AC and CDP1806AC which are identical to the CDP1804AC, except for the on-chip memory, should be used for CDP1804AC development purposes.

The CDP1804AC software enhancements include 32 more instructions than the CDP1802. The 32 additional software instructions include subroutine call and return capability, enhanced data transfer manipulation. counter/timer control, improved interrupt handling, single-instruction loop counting, and BCD arithmetic.

8-bit Counter/Timer

Upwards software and hardware compatibility are maintained when substituting a CDP1804AC for other CDP1800-series microprocessors. Pinout is identical except for the replacement of Vcc with EMS/ME.

The CDP1804AC has an operating voltage range of 4 V to 6.5 V and is supplied in a 40-lead hermetic dual-in-line ceramic package (D suffix), in a 40-lead dual-in-line plastic package (E suffix), and in a 44-lead plastic chipcarrier package (Q suffix).

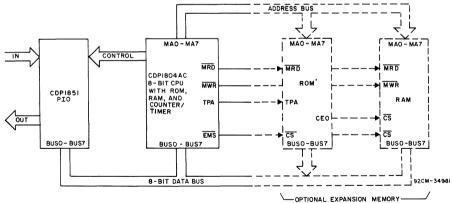

Fig. 1 – Typical CDP1804AC microprocessor system.

#### MAXIMUM RATINGS, Absolute-Maximum Values:

| DC SUPPLY-VOLTAGE RANGE, (Vod):                                                             |

|---------------------------------------------------------------------------------------------|

| (Voltage referenced to Vss Terminal)0.5 to +7 V                                             |

| INPUT VOLTAGE RANGE, ALL INPUTS                                                             |

| DC INPUT CURRENT, ANY ONE INPUT                                                             |

| POWER DISSIPATION PER PACKAGE (Po).                                                         |

| For T <sub>A</sub> = -40 to +60° C (PACKAGE TYPE E)                                         |

| For T <sub>A</sub> = +60 +85°C (PACKAGE TYPE E) Derate Linearly at 12 mW/°C to 200 mW       |

| For T <sub>A</sub> = -55 to +100° C (PACKAGE TYPE D)                                        |

| For T <sub>A</sub> = +100 to +125°C (PACKAGE TYPE D)                                        |

| For T <sub>A</sub> = -40°C to +85°C (PACKAGE TYPE Q)*                                       |

| DEVICE DISSIPATION PER OUTPUT TRANSISTOR                                                    |

| For TA = FULL PACKAGE-TEMPERATURE RANGE (All Package Types)                                 |

| OPERATING-TEMPERATURE RANGE (TA):                                                           |

| PACKAGE TYPE D                                                                              |

| PACKAGE TYPE E AND Q40 to +85°C                                                             |

| STORAGE TEMPERATURE RANGE (Tato)                                                            |

| LEAD TEMPERATURE (DURING SOLDERING) <sup>.</sup>                                            |

| At distance 1/16 $\pm$ 1/32 in (1 59 $\pm$ 0 79 mm) from case for 10 s max $+265^{\circ}$ C |

\* Printed-circuit board mount: 57 mm x 57 mm minimum area x 1.6 mm thick G10 epoxy glass, or equivalent.

**RECOMMENDED OPERATING CONDITIONS at T<sub>A</sub> = -40 to +85° C** For maximum reliability, nominal operating conditions should be selected so that operation is always within the following ranges:

| CHARACTERISTIC                                                                       | CONDITION  | LIMITS<br>CDP1804ACD<br>CDP1804ACE |       | UNITS    |

|--------------------------------------------------------------------------------------|------------|------------------------------------|-------|----------|

|                                                                                      | V₀₀<br>(V) | MIN.                               | MAX.  | -        |

| DC Operating Voltage Range                                                           | —          | 4                                  | 6.5   |          |

| Input Voltage Range                                                                  | _          | Vss                                | VDD   | - V      |

| Minimum Instruction Time* (fcL=5 MHz)                                                | 5          | 3.2                                | —     | μs       |

| Maximum DMA Transfer Rate                                                            | 5          | _                                  | 0.625 | Mbytes/s |

| Maximum Clock Input Frequency,<br>Load Capacitance (CL) = 50 pF                      | 5          | DC                                 | 5     |          |

| Maximum External Counter/Timer<br>Clock Input Frequency to EF1, EF2 t <sub>cLx</sub> | 5          | DC                                 | 2     | – MHz    |

\* Equals 2 machine cycles - one Fetch and one Execute operation for all instructions except Long Branch, Long Skip, NOP, and "68" family instructions, which are more than two cycles

STATIC ELECTRICAL CHARACTERISTICS at TA = -40 to +85° C, VDD  $\pm$  5%, Except as noted

| CHARACTERISTIC                                      |                 | C         | CONDITIONS                        |                        |      | LIMITS               |      |       |

|-----------------------------------------------------|-----------------|-----------|-----------------------------------|------------------------|------|----------------------|------|-------|

|                                                     |                 |           |                                   |                        |      | DP1804AC<br>DP1804AC | ,    | UNITS |

|                                                     |                 | Vo<br>(V) | VIN<br>(V)                        | V <sub>DD</sub><br>(V) | Min. | Тур.•                | Max. |       |

| Quiescent Device Current                            | IDD             | -         | 0, 5                              | 5                      | -    | 50                   | 200  | μA    |

| Output Low Drive (Sink) Current<br>(Except XTAL)    | lol             | 0.4       | 0, 5                              | 5                      | 1.6  | 4                    |      |       |

| XTAL Output                                         | IOL             | 0.4       | 5                                 | 5                      | 0.2  | 0.4                  | _    |       |

| Output High Drive (Source) Current<br>(Except XTAL) | Іон             | 4.6       | 0, 5 <sup>(</sup>                 | 5                      | -1.6 | -4                   | _    | - mA  |

| XTAL                                                | Іон             | 4.6       | 0                                 | 5                      | -0.1 | -0.2                 |      |       |

| Output Voltage Low-Level                            | Vol             | -         | 0,5                               | 5                      |      | 0                    | 0.1  |       |

| Output Voltage High Level                           | Vон             | -         | 0, 5                              | 5                      | 4.9  | 5                    |      |       |

| Input Low Voltage (BUS 0 - BUS 7, EMS/ME)           | VIL             | 0.5, 4.5  | _                                 | 5                      |      | _                    | 1.5  |       |

| Input High Voltage (BUS 0 - BUS 7, EMS/ME)          | ViH             | 0.5, 4.5  |                                   | 5                      | 3.5  |                      | _    |       |

| Schmitt Trigger Input Voltage                       |                 |           |                                   |                        |      |                      |      | v     |

| (Except BUS 0 — BUS 7, EMS/ME)                      |                 |           |                                   |                        |      |                      |      |       |

| Positive Trigger Threshold                          | ٧p              |           |                                   |                        | 2.2  | 2.9                  | 3.6  |       |

| Negative Trigger Threshold                          | VN              | 0.5, 4.5  | —                                 | 5                      | 0.9  | 1.9                  | 2.8  |       |

| Hysteresis                                          | Vн              |           |                                   |                        | 0.3  | 0.9                  | 1.6  |       |

| Input Leakage Current                               | l <sub>in</sub> | _         | 0, 5                              | 5                      |      | ±0.1                 | ±5   |       |

| 3-State Output Leakage Current                      | Іоит            | 0, 5      | 0, 5                              | 5                      | _    | ±0.2                 | ±5   | μA    |

| Input Capacitance                                   | CIN             | -         |                                   | -                      | _    | 5                    | 7.5  |       |

|                                                     | Соит            |           | —                                 | —                      | _    | 10                   | 15   | - pF  |

| Total Power Dissipation <sup>∆</sup><br>Bun         |                 | _         |                                   | 5                      | _    | 35                   | 50   | mW    |

| Tdle "00" at M(0000)                                |                 |           | —                                 | 5                      |      | 12                   | 18   |       |

| Minimum Data Retention Voltage                      | VDR             |           | V <sub>DD</sub> = V <sub>DR</sub> |                        | _    | 2                    | 2.4  | v     |

| Data Retention Current                              | IDR             |           | V <sub>DD</sub> = 2.4             |                        | -    | 25                   | 100  | μA    |

### TERMINAL ASSIGNMENT

<sup>44-</sup>Lead Plastic Chip-Carrier Package (Q Suffix)

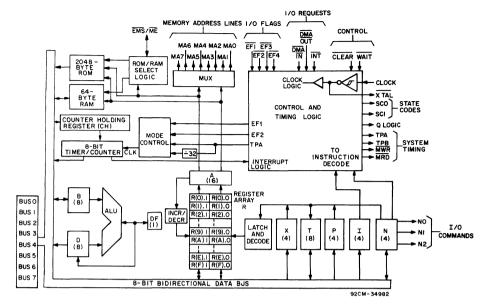

Fig. 2 - Block diagram for CDP1804AC.

#### **Enhanced 1804AC Operation**

### ROM/RAM

The 2K-byte ROM is mask-programmable and maskselectable in any 2K block of the available 64K address space in the RUN (ROM/RAM) mode. (The procedure is detailed in the Mask-Programming section at the end of the data sheet.)

The 64-byte RAM is mask-selectable in any 64-byte block of memory in the RUN (ROM/RAM) mode. It may also be externally selected via the ME input in the RUN (RAM only) mode.

The EMS/ME pin serves a dual function. In the RUN (ROM/RAM) mode, EMS acts as an active low output to indicate when the internal ROM or RAM is not selected. This provides a convenient chip-select signal for any optional expansion memory devices and a stable-address latch signal for synchronous RAMs. In the RUN (RAM only) mode, ME acts as an active low input and is used to select the internal RAM, which is not mask-selected in this mode. Decoding is performed externally and the RAM may reside in any 64-byte block.

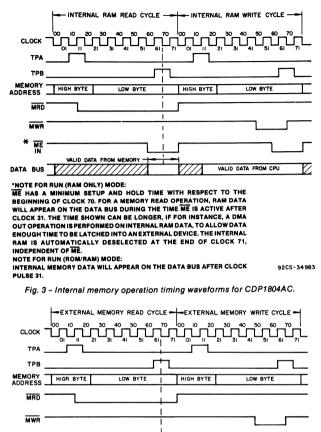

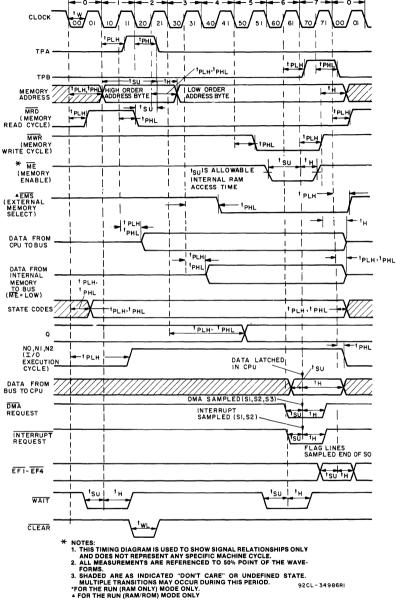

### Timing

Timing for the CDP1804AC is the same as the CDP1802 microprocessor series, with the following exceptions:

- 4.5 clock cycles are provided for memory access instead of 5.

- Q changes 1/2 clock cycle earlier during the SEQ and REQ instructions.

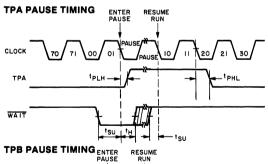

- Flag lines (EF1-EF4) are sampled at the end of the S0 cycle instead of at the beginning of the S1 cycle.

- Pause can only occur on the low-to-high transition of either TPA or TPB, instead of any negative clock transition.

#### **Special Features**

<u>Schmitt</u> triggers are provided on all inputs, except EMS/ME, and BUS 0 - BUS 7, for maximum immunity from noise and slow signal transitions. A Schmitt trigger in the oscillator section allows operation with an RC or crystal.

The CDP1802 series LOAD mode is not retained. This mode (WAIT, CLEAR=0) is the RUN (ROM/RAM) mode on the CDP1804AC.

A low power mode is provided, which is initiated via the IDLE instruction. In this mode all external signals, except the oscillator, are stopped on the low-to-high transition of TPB. All outputs remain in their previous states, MRD is set to a logic "1", and the data bus floats. The IDLE mode is exited by a DMA or INT condition. The INT includes both external interrupts and interrupts generated by the Counter/Timer. The only restrictions are that the Timer mode, which uses the TPA + 32 clock source, and the underflow condition of the Pulse Width Measurement modes are not available to exit the IDLE mode.

### TIMING WAVEFORMS FOR POSSIBLE OPERATING MODES

\*FOR RUN (ROM/RAM) MODE ONLY. NOTE: FOR THE RUN (RAM ONLY) MODE ME MUST BE HIGH DURING EXTERNAL MEMORY ACCESSES.

DATA LATCHED IN CPU

9205-34984

VALID DATA FROM CPU

Fig. 4 - External memory operation timing waveforms for CDP1804AC.

1

#### SIGNAL DESCRIPTIONS

#### Bus 0 to BUS 7 (Data Bus):

8-bit bidirectional DATA BUS lines. These lines are used for transferring data between the memory, the microprocessor, and I/O devices.

DATA BUS

#### N0 to N2 (I/O) Lines):

Activated by an I/O instruction to signal the I/O control logic of a data transfer between memory and I/O

interface. These lines can be used to issue command codes or device selection codes to the I/O devices. The N bits are low at all times except when an I/O instruction is being executed. During this time their state is the same as the corresponding bits in the N register. The direction of data flow is defined in the I/O instruction by bit N3 (internally) and is indicated by the level of the MRD signal:

$\frac{MRD}{MRD} = V_{DD}:$  Input data from I/O to CPU and Memory MRD = V<sub>SS</sub>: Output data from Memory to I/O

### EF1 to EF4 (4 Flags):

These inputs enable the I/O controllers to transfer status information to the processor. The levels can be tested by the conditional branch instructions. They can be used in conjunction with the INTERRUPT request line to establish interrupt priorities. The flag(s) are sampled at the end of every S0 cycle. EF1 and EF2 are also used for event counting and pulse-width measurement in conjunction with the Counter/Timer.

### INTERRUPT, DMA-IN, DMA-OUT (3 I/O Requests)

DMA-IN and DMA-OUT are sampled during TPB every S1, S2, and S3 cycle. INTERRUPT is sampled during TPB every S1 and S2 cycle.

Interrupt Action: X and P are stored in T after executing current instruction; designator X is set to 2; designator P is set to 1; interrupt enable (MIE) is reset to 0 (inhibit); and instruction execution is resumed. The interrupt action requires one machine cycle (S3).

**DMA Action:** Finish executing current instruction; R(0) points to memory area for data transfer; data is loaded into or read out of memory; and R(0) is incremented.

Note: In the event of concurrent DMA and INTERRUPT requests, DMA-IN has priority followed by DMA-OUT and then Interrupt. (The Interrupt request is not internally latched and must be held true after DMA).

#### SC0, SC1, (2 State Code Lines):

These outputs indicate that the CPU is: 1) fetching an instruction, or 2) executing an instruction, or 3) processing a DMA request, or 4) acknowledging an interrupt request. The levels of state code are tabulated below. All states are valid at TPA.

| State Type     | State Code Lines |     |  |  |

|----------------|------------------|-----|--|--|

|                | SC1              | SC0 |  |  |

| S0 (Fetch)     | L                | L   |  |  |

| S1 (Execute)   | L                | н   |  |  |

| S2 (DMA)       | н                | L   |  |  |

| S3 (Interrupt) | н                | н   |  |  |

H = V<sub>DD</sub>, L = V<sub>SS</sub>.

### TPA, TPB (2 Timing Pulses):

Positive pulses that occur once in each machine cycle (TPB follows TPA). They are used by I/O controllers to interpret codes and to time interaction with the data bus. The trailing edge of TPA is used by the memory system to latch the higher-order byte of the multiplexed 16-bit memory address.

### MA0 to MA7 (8 Memory Address Lines):

In each cycle, the higher-order byte of a 16-bit memory address appears on the memory address lines MA0-7 first. Those bits required by the memory system can be strobed into external address latches by timing pulse TPA. The low-order byte of the 16-bit address appears on the address lines 1/2 clock after the termination of TPA.

### MWR (Write Pulse):

A negative pulse appearing in a memory-write cycle, after the address lines have stabilized.

### MRD (Read Level):

A low level on MRD indicates a memory read cycle. It can be used to control three-state outputs from the addressed memory and to indicate the direction of data transfer during and I/O instruction.

### Q:

Single bit output from the CPU which can be set or reset, under program control. During SEQ or REQ instruction execution, Q is set or reset between the trailing edge of TPA and the leading edge of TPB. The Q-line can also be controlled by the Counter/Timer underflow via the Enable Toggle Q instruction. The Enable Toggle Q command connects the Q-line flip-flop to the output of the counter, such that each time the counter decrements from 01 to its cleared by a LOAD COUNTER (LDC) instruction with the COUNTER INTERRUPT (BCI) instruction with the counter interrupt flip-flop set.

#### CLOCK:

Input for externally generated single-phase clock. The maximum clock frequency is 5 MHZ at  $V_{DD}$  = 5 V. The clock is counted down internally to 8 clock pulses per machine cycle.

### XTAL:

Connection to be used with clock input terminal, for an external crystal, if the on-chip oscillator is utilized.

### WAIT, CLEAR (2 Control Lines):

Provide four control modes as listed in the following truth table:

| CLEAR | WAIT | MODE           |

|-------|------|----------------|

| L     | L    | RUN (ROM/RAM)  |

| L     | н    | RESET          |

| н     | L    | PAUSE          |

| н     | н    | RUN (RAM ONLY) |

### ME (Memory Enable) RUN (RAM ONLY) Mode

This active low input is used to select or deselect the internal RAM. It must be active prior to clock 70 for an internal RAM access to take place. Internal RAM data will appear on the data bus during the time that  $\overline{\text{ME}}$  is active (after clock 31). Thus, if this data is to be latched into an external device (i.e., during an OUTPUT instruction or DMA-OUT cycle),  $\overline{\text{ME}}$  should be wide enough to provide enough time for valid data to be latched. The internal RAM is automatically deselected after clock 71.  $\overline{\text{ME}}$  is ineffective when  $\overline{\text{MRD}} \circ \overline{\text{MWR}} = 1$ .

In the RUN (RAM ONLY) mode the internal RAM is not internally mask-decoded. Decoding of the starting address is performed externally, and may reside in any 64-byte block of memory.

### EMS (External Memory Select) RUN (ROM/RAM) Mode

This active low output is used for external memory expansion. It is low when external memory is being addressed and high at all other times. It is initiated 1.5 clock periods after TPA (at which time all addresses <u>are</u> stable) and terminates at the end of the cycle. Use of EMS for memory selection allows 3.5 clock cycles for data access.

Note that in the RUN (ROM/RAM) mode data from the internal ROM or RAM, when selected, will appear on the data bus after clock 31.

#### VDD, VSS, (Power Levels):

$V_{ss}$  is the most negative supply voltage terminal and is normally connected to ground.  $V_{Do}$  is the positive supply voltage terminal. All outputs swing from  $V_{ss}$  to  $V_{DD}$ . The recommended input voltage swing is from  $V_{ss}$  to  $V_{DD}$ .

#### ARCHITECTURE

Fig. 2 shows a block diagram of the CDP1804AC. The principal feature of this system is a register array (R) consisting of sixteen 16-bit scratchpad registers. Individual registers in the array (R) are designated (selected) by a 4-bit binary code from one of the 4-bit registers labeled N, P, and X. The contents of any register can be directed to any one of the following paths:

- 1. the external memory (multiplexed, higher-order byte first, on to 8 memory address lines)

- 2. the D register (either of the two bytes can be gated to D)

- the increment/decrement circuit where it is increased or decreased by one and stored back in the selected 16-bit register

- 4. to any other 16-bit scratch-pad register in the array.

The four paths, depending on the nature of the instruction, may operate independently or in various combinations in the same machine cycle.

Most instructions consist of two 8-clock-pulse machine cycles. The first cycle is the fetch cycle, and the second and more if necessary—are execute cycles. During the fetch cycle the four bits in the P designator select one of the 16 registers R(P) as the current program counter. The selected register R(P) contains the address of the memory location from which the instruction is to be fetched. When the instruction is read out from the memory, the higher-order 4 bits of the instruction byte are loaded into the I register and the lower-order 4 bits into the N register. The content of the program counter is automatically incremented by one so that R(P) is now "pointing" to the next byte in the memory.

The X designator selects one of the 16 registers R(X) to "point" to the memory for an operand (or data) in certain ALU or I/O operations.

The N designator can perform the following five functions depending on the type of instruction fetched:

- 1. designate one of the 16 registers in R to be acted upon during register operations

- 2. indicate to the I/O devices a command code or device-selection code for peripherals

- indicate the specific operation to be executed during the ALU instructions, types of tests to be performed during the Branch instructions, or the specific operation required in a class of miscellaneous instructions

- indicate the value to be loaded into P to designate a new register to be used as the program counter R(P)

- 5. indicate the value to be loaded into X to designate a new register to be used as data pointer R(X).

The registers in R can be assigned by a programmer in three different ways as program counters, as data pointers, or as scratchpad locations (data registers) to hold two bytes of data.

#### **Program Counters**

Any register can be the main program counter; the address of the selected register is held in the P designator. Other registers in R can be used as subroutine program counters. By a single instruction the contents of the P register can be changed to effect a "call" to a subroutine. When interrupts are being serviced, register R(1) is used as the program counter for the user's interrupt servicing routine. After reset, and during a DMA operation, R(0) is used as the program counter. At all other times the register designated as program counter is at the discretion of the user.

#### **Data Pointers**

The registers in R may be used as data pointers to indicate a location in memory. The register designated by X (i.e., R(X)) points to memory for the following instructions (see Table I):

- 1. ALU operations

- 2. output instructions

- input instructions

- 4. register to memory transfer

- 5. memory to register transfer

- 6. interrupt and subroutine handling.

The register designated by N (i.e., R(N)) points to memory for the "load D from memory" instructions 0N and 4N and the "Store D" instruction 5N. The register designated by P (i.e., the program counter) is used as the data pointer for ALU instructions F8-FD, FF, 7C, 7D, 7F, and the RLDI instruction 68CN. During these instruction executions, the operation is referred to as "data immediate".

Another important use of R as a data pointer supports the built-in Direct-Memory-Access (DMA) function. When a DMA-In or DMA-Out request is received, one machine cycle is "stolen". This operation occurs at the end of the execute machine cycle in the current instruction. Register R(0) is always used as the data pointer during the DMA operation. The data is read from (DMA-Out) or written into (DMA-In) the memory location pointed to by the R(0) register. At the end of the transfer, R(0) is incremented by one so that the processor is ready to act upon the next DMA byte transfer request. This feature in the CDP1804AC architecture saves a substantial amount of logic when fast exchanges of blocks of data are required, such as with magnetic discs or during CRT-displayrefresh cycles.

### **Data Registers**

When registers in R are used to store bytes of data. instructions are provided which allow D to receive from or write into either the higher-order- or lower-order-byte portions of the register designated by N. By this mechanism (together with loading by data immediate) program pointer and data pointer designations are initialized. Also, this technique allows scratchpad registers in R to be used to hold general data. By employing increment or decrement instructions, such registers may be used as loop counters. The new RLDI, RLXA, RSXD, and RNX instructions also allow loading, storing, and exchanging the full 16-bit contents of the R registers without affecting the D register. The new DBNZ instruction allows decrementing and branching-on-notzero of any 16-bit R register also without affecting the D register.

#### The Q Flip Flop

An internal flip flop, Q, can be set or reset by instruction and can be sensed by conditional branch instructions. It can also be driven by the underflow output of the Counter/Timer. The output of Q is also available as a microprocessor output.

#### **Register Summary**

| -    |         |                                |

|------|---------|--------------------------------|

| D    | 8 Bits  | Data Register (Accumulator)    |

| DF   | 1 Bit   | Data Flag (ALU Carry)          |

| В    | 8 Bits  | Auxiliary Holding Register     |

| R    | 16 Bits | 1 of 16 Scratchpad Registers   |

| Р    | 4 Bits  | Designates which Register is   |

|      |         | Program Counter                |

| X    | 4 Bits  | Designates which Register is   |

|      |         | Data Pointer                   |

| N    | 4 Bits  | Holds Low-Order Instr. Digit   |

| I    | 4 Bits  | Holds High-Order Instr. Digit  |

| Т    | 8 Bits  | Holds old X, P after Interrupt |

|      |         | (X is high nibble)             |

| Q    | 1 Bit   | Output Flip-Flop               |

| CNTR | 8-Bits  | Counter/Timer                  |

| СН   | 8 Bits  | Holds Counter Jam Value        |

| MIE  | 1 Bit   | Master Interrupt Enable        |

| CIE  | 1 Bit   | Counter Interrupt Enable       |

| XIE  | 1 Bit   | External Interrupt Enable      |

| CIL  | 1 Bit   | Counter Interrupt Latch        |

#### Interrupt Servicing

Register R(1) is always used as the program counter whenever interrupt servicing is initiated. When an interrupt request occurs and the interrupt is allowed by the program (again, nothing takes place until the completion of the current instruction), the contents of the X and P registers are stored in the temporary register T, and X and P are set to new values; hex digit 2 in X and hex digit 1 in P. Master Interrupt Enable is automatically deactivated to inhibit further interrupts. The user's interrupt routine is now in control; the contents of T may be saved by means of a single SAV instruction (78) in the memory location pointed to by R(X) or the contents of T, D, and DF may be saved using a single DSAV instruction (6876). At the conclusion of the interrupt, the user's routine may restore the pre-interrupted value of X and P with either a RET instruction (70) which permits further interrupts, or a DIS instruction (71), which disables further interrupts.

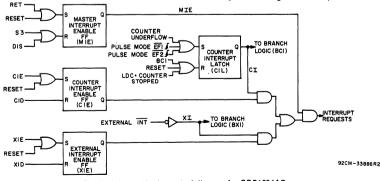

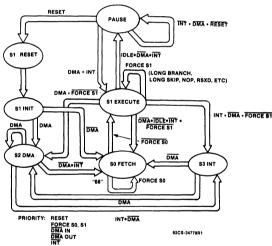

# Interrupt Generation and Arbitration (See Fig. 5)

Interrupt requests can be generated from the following sources:

- 1. Externally through the interrupt input (Request not latched)

- Internally due to Counter/Timer response (Request is latched)

- a. On the transition from count (01)<sub>16</sub> to its next value (counter underflow)

- b. On the s transition of EF1 in pulse measurement mode 1

- c. On the *s* transition of EF2 in pulse measurement mode 2

For an interrupt to be serviced by the CPU, the appropriate Interrupt Enable flip-flops must be set. Thus, the External Interrupt Enable flip-flop must be set to service an external interrupt request, and the Counter Interrupt Enable flip-flop must be set to service an internal Counter/Timer interrupt request. In addition, the Master Interrupt Enable flip-flop (as used in the CDP1802A) must be set to service either type of request. All 3 flip-flops are initially enabled with the application of a hardware reset, and, can be selectively enabled or disabled with software: CIE, CID instructions for the CIE flip-flop; XIE, XID instructions for the XIE flip-flop; RET, DIS instructions for the MIE flip-flop.

Short branch instructions on Counter Interrupt (BCI) and External Interrupt (BXI) can be placed in the user's interrupt service routine to provide a means of identifying and prioritizing the interrupt source. Note, however, that since the External Interrupt request is not latched, it must remain active until the short branch is executed if this priority arbitration scheme is used.

Interrupt requests can also be polled if automatic interrupt service is not desired (MIE=0). With the Counter Interrupt and External Interrupt short branch instructions, the branch will be taken if an interrupt request is pending, regardless of the state of any of the 3 Interrupt Enable flip-flops. The latched counter interrupt request signal will be reset when the branch is taken, when the CPU is reset, or with a LDC instruction with the Counter stopped. Note that exiting a counter-initiated interrupt routine without resetting the counter interrupt latch will result in immediately re-entering the interrupt routine.

Fig. 5 – Interrupt logic-control diagram for CDP1804AC.

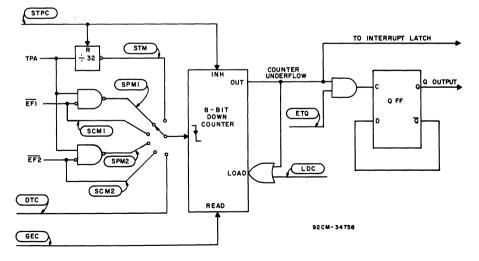

### Counter/Timer and Controls (See Fig. 6)

This logic consists of a presettable 8-bit down-counter (Modulo N type), and a conditional divide-by-32 prescaler. After counting down to  $(01)_{16}$  the counter returns to its initial value at the next count and sets the Counter Interrupt Latch. It will continue decrementing on subsequent counts. If the counter is preset to  $(00)_{16}$  a full 256 counts will occur.

During a Load Counter instruction (LDC) if the counter was stopped with a STPC instruction, the counter and its holding register (CH) are loaded with the value in the D register and any previous counter interrupt is cleared. If the LDC is executed when the counter is running, the contents of the D register are loaded into the holding register (CH) only and any previous counter interrupt is not cleared. (LDC resets the Counter Interrupt Latch only when the counter is stopped). After counting down to (01)<sub>16</sub> the next count will load the new initial value into the counter, set the Counter Interrupt Latch, and operation will continue.

The Counter/Timer has the following five programmable modes:

- Event Counter 1: Input to counter is connected to the EF1 terminal. The high-to-low transition decrements the counter.

- Event Counter 2: Input to counter is connected to the EF2 terminal. The high-to-low transition decrements the counter.

- 3. Timer: Input to counter is from the divide-by-32 prescaler clocked by TPA. The prescaler is decremented on the low-to-high transition of TPA. The divide-by-32 prescaler is reset when the counter is in a mode other than the Timer mode, system reset, or stopped by a STPC.

- 4. Pulse Duration Measurement 1: Input to counter connected to TPA. Each low-to-high transition of

TPA decrements the counter if the input signal at <u>EF1</u> terminal (gate input) is low. On the transition of <u>EF1</u> to the positive state, the count is stopped, the mode is cleared, and the interrupt request latched. If the counter underflows while the input is low, interrupt will also be set, but counting will continue.

5. Pulse Duration Measurement 2: Operation is identical to Pulse Duration Measurement 1, except EF2 is used as the gate input.

The modes can be changed without affecting the stored count.

Those modes which use  $\overline{EF1}$  and  $\overline{EF2}$  terminals as inputs do not exclude testing these flags for branch instructions.

The Stop Counter (STPC) instruction clears the counter mode and stops counting. The STPC instruction should be executed prior to a GEC instruction, if the counter is in the Event Counter Mode 1 or 2.

In addition to the five programmable modes, the Decrement Counter Instruction (DTC) enables the user to count in software. In order to avoid conflict with counting done in other modes, the instruction should be used only after the mode has been cleared by a Stop Counter instruction.

The Enable Toggle Q instruction (ETQ) connects the Qline flip-flop to the output of the counter, such that each time the counter decrements from 01 to its next value, the Q output changes state. This action is independent of the counter mode and the Interrupt Enable flip-flops. The Enable Toggle Q condition is cleared by an LDC with the Counter/Timer stopped; system Reset, or a BCI with CI=1. Note that SEQ and REQ instructions are independent of ETQ.—they can Set or Reset Q while the counter is running.

Fig. 6 - Counter/Timer diagram for CDP1804AC.

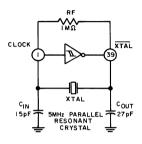

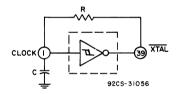

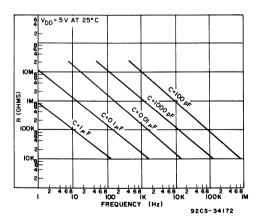

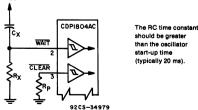

#### On-Chip Clock (See Figs. 7, 8 and 9)

Clock circuits may use either an external crystal or an RC network.

A typical crystal oscillator circuit is shown in Fig. 7. The crystal is connected between terminals 1 and 39 (CLOCK and XTAL) in parallel with a resistance. RF (1 megohm typ.). Frequency trimming capacitors, C<sub>IN</sub> and C<sub>OUT</sub>, may be required at terminals 1 and 39. For additional information on crystal oscillators, see ICAN-6565.

Because of the Schmitt Trigger input, an RC oscillator can be used as shown in Fig. 8. The frequency is approximately 1/RC (See Fig. 9).

92CS-38099

Fig. 7 - Typical 5-MHz crystal oscillator.

Fig. 8 - RC network for oscillator.

Fig. 9 – Nominal component values as a function of frequency for the RC oscillator.

#### CONTROL MODES

| CLEAR | WAIT | MODE           |

|-------|------|----------------|

| L     | L    | RUN (ROM/RAM)  |

| L     | н    | RESET          |

| н     | L    | PAUSE          |

| н     | н    | RUN (RAM ONLY) |

The function of the modes are defined as follows:

#### RESET

The levels of the CDP1804A external signal lines will asynchronously be forced by RESET to the following states:

Q=0

SC1,SC0=0,1

BUS 0-7=0

EMS/ME=INPUT

(EXECUTE)

MA0-7=RO.1

MRD=1

N0, N1, N2=0, 0, 0

TPA=0

TPB=0

MWR=1

TPA=0

#### Internal changes caused by RESET are:

I, N instruction register is cleared to 00. XIE and CIE are set to allow interrupts following initialize. CIL is cleared (any pending counter interrupt is cleared), counter is stopped, the counter mode is cleared, and ETQ is disabled.

#### **Initialization Cycle**

The first machine cycle following termination of **RESET is** an initialization cycle which requires 9 clock pulses. During this cycle the CPU remains in S1 and the following additional changes occur:

I → MIĒ

X,  $P \rightarrow T$  (The old value of X, P will be put into T. This only has meaning following an orderly Reset with power applied).

X, P, RO  $\leftarrow$  0 (X, P and RO are cleared).

Interrupt and DMA servicing is suppressed during the initialization cycle. The next cycle is an S0 or an S2 but never an S1 or S3. The use of a 71 instruction followed by 00 at memory locations 0000 and 0001, may be used to reset MIE so ac to preclude interrupts until ready for them.

### Reset and Initialize do not affect:

D (Accumulator)

- DF

- R1, R2, R3, R4, R5, R6, R7, R8, R9, RA, RB, RC, RD, RE, RF

CH (Counter Holding Register) Counter (the counter is stopped but the value is unaffected)

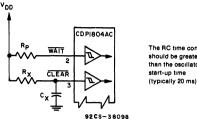

#### **Power-up Reset/Run Circuits**

Power-up Reset/Run (ROM/RAM) and Reset/Run (RAM only) can be realized with the circuits shown in Fig. 10 and 11.  $\dot{V}_{--}$

Fig. 10 - Reset/Run (ROM/RAM) diagram.

The RC time constant should be greater than the oscillator

Fig. 11 - Reset/Run (RAM only) diagram.

### PAUSE

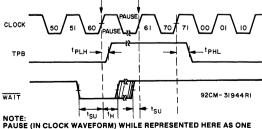

Pause is a low power mode which stops the internal CPU timing generator and freezes the state of the processor. The CPU may be held in the Pause mode indefinitely. Hardware pause can occur at two points in a machine cycle, on the low to high transition of either TPA or TPB. A TPB pause can also be initiated by software with the execution of an IDLE instruction. In the pause mode, the oscillator continues to run but subsequent clock transitions are ignored. TPA and TPB remain at their previous state (see Fig. 12).

Pause is entered from RUN (RAM only) by dropping WAIT low, and from RUN (ROM/RAM) by raising CLEAR high. Appropriate setup and hold times must be met.

If Pause is entered while in the event counter mode, the appropriate Flag transition will continue to decrement the counter.

Hardware-initiated pause is exited to RUN (RAM only) by raising the Wait line, and the RUN (ROM/RAM) by lowering CLEAR. Pause entered with an IDLE instruction requires DMA, INTERRUPT or RESET to resume execution.

CLOCK CYCLE IN DURATION, COULD BE INFINITELY LONG. Fig. 12 - Pause mode timing waveforms.

### RUN

May be initiated from the Pause or Reset mode functions. If initiated from Pause, the CPU resumes operation at the point it left off. If paused at TPA, it will resume on the next high-to-low clock transition, while if paused at TPB. it will resume on the next low-to-high clock transition. (See Fig. 12). When initiated from the Reset operation, the first machine cycle following Reset is always the initialization cycle. The initialization cycle is then followed by a DMA (S2) cycle or fetch (S0) from location 0000 in memory.

### SCHMITT TRIGGER INPUTS

All inputs except BUS 0 - BUS 7 and ME contain a Schmitt Trigger circuit, which is especially useful on the CLEAR input as a power-up RESET (See Fig. 10 and 11) and the CLOCK input (See Fig. 7 and 8).

### STATE TRANSITIONS

The CDP1804AC state transitions are shown in Fig. 13. Each machine cycle requires the same period of time, 8 clock pulses, except the initialization cycle (INT) which requires 9 clock pulses. Reset is asynchronous and can be forced at any time.

Fig. 13 - State transition diagram.

#### INSTRUCTION SET

The CDP1804AC instruction summary is given in Table I. Hexadecimal notation is used to refer to the 4-bit binary codes.

In all registers bits are numbered from the least significant bit (LSB) to the most significant bit (MSB) starting with 0.

R(W): Register designated by W, where W=N or X, or P

#### TABLE I - INSTRUCTION SUMMARY

R(W).0: Lower-order byte of R(W) R(W).1: Higher-order byte of R(W) Operation Notation

M (R(N))→D; R(N) + 1→R(N)

This notation means: The memory byte pointed to by R(N) is loaded into D, and R(N) is incremented by 1.

|                               | NO. OF  |          |                   |                                                    |  |  |  |  |

|-------------------------------|---------|----------|-------------------|----------------------------------------------------|--|--|--|--|

|                               | MACHINE |          | OP                |                                                    |  |  |  |  |

| INSTRUCTION                   | CYCLES  | MNEMONIC | CODE              | OPERATION                                          |  |  |  |  |

| MEMORY REFERENCE              |         |          |                   |                                                    |  |  |  |  |

| LOAD IMMEDIATE                | 2       | LDI      | F8                | M(R(P))→D; R(P)+1→R(P)                             |  |  |  |  |

| REGISTER LOAD IMMEDIATE       | 5       | RLDI     | 68CN <sup>■</sup> | M(R(P))→R(N).1; M(R(P))+1→                         |  |  |  |  |

|                               |         |          |                   | R(N).0; R(P)+2→R(P)                                |  |  |  |  |

| LOAD VIA N                    | 2       | LDN      | 0N                | M(R(N))→D; FOR N NOT 0                             |  |  |  |  |

| LOAD ADVANCE                  | 2       | LDA      | 4N                | M(R(N))→D; R(N)+1→R(N)                             |  |  |  |  |

| LOAD VIA X                    | 2       | LDX      | F0                | M(R(X))→D                                          |  |  |  |  |

| LOAD VIA X AND ADVANCE        | 2       | LDXA     | 72                | $M(R(X)) \rightarrow D; R(X)+1 \rightarrow R(X)$   |  |  |  |  |

| REGISTER LOAD VIA X AND       | 5       | RLXA     | 686N              | M(R(X))→R(N).1; M(R(X)+1)→                         |  |  |  |  |

| ADVANCE                       |         |          |                   | R(N).0; R(X))+2→R(X)                               |  |  |  |  |

| STORE VIA N                   | 2       | STR      | 5N                | D→M(RN))                                           |  |  |  |  |

| STORE VIA X AND DECREMENT     | 2       | STXD     | 73                | $D \rightarrow M(R(X)); R(X) - 1 \rightarrow R(X)$ |  |  |  |  |

| REGISTER STORE VIA X AND      | 5       | RSXD     | 68AN              | R(N).0→M(R(X)); R(N).1→                            |  |  |  |  |

| DECREMENT                     |         |          |                   | M(R(X)-1); R(X)-2→R(X)                             |  |  |  |  |

| REGISTER OPERATIONS           |         |          |                   |                                                    |  |  |  |  |

| INCREMENT REG N               | 2       | INC      | 1N                | R(N)+1→R(N)                                        |  |  |  |  |

| DECREMENT REG N               | 2       | DEC      | 2N                | R(N)-1→R(N)                                        |  |  |  |  |

| DECREMENT REG N AND LONG      | 5       | DBNZ     | 682N              | R(N)-1→R(N); IF R(N) NOT 0,                        |  |  |  |  |

| BRANCH IF NOT EQUAL 0         |         |          |                   | M(R(P))→R(P).1, M(R(P)+1)→                         |  |  |  |  |

|                               |         |          |                   | R(P).0, ELSE R(P)+2→R(P)                           |  |  |  |  |

| INCREMENT REG X               | 2       | IRX      | 60                | R(X)+1→R(X)                                        |  |  |  |  |

| GET LOW REG N                 | 2       | GLO      | 8N                | R(N).0→D                                           |  |  |  |  |

| PUT LOW REG N                 | 2       | PLO      | AN                | D→R(N).0                                           |  |  |  |  |

| GET HIGH REG N                | 2       | GHI      | 9N                | R(N).1→D                                           |  |  |  |  |

| PUT HIGH REĠ N                | 2       | PHI      | BN                | D→R(N).1                                           |  |  |  |  |

| REGISTER N TO REGISTER X COPY | 4       | RNX      | 68BN              | R(N)→R(X)                                          |  |  |  |  |

| LOGIC OPERATIONS (Note 5)     |         |          |                   |                                                    |  |  |  |  |

| OR                            | 2       | OR       | F1                | M(R(X)) OR D→D                                     |  |  |  |  |

| OR IMMEDIATE                  | 2       | ORI      | F9                | M(R(P)) OR D→D;                                    |  |  |  |  |

|                               |         |          |                   | R(P)+1→R(P)                                        |  |  |  |  |

| EXCLUSIVE OR                  | 2       | XOR      | F3                | M(R(X)) XOR D→D                                    |  |  |  |  |

| EXCLUSIVE OR IMMEDIATE        | 2       | XRI      | FB                | M(R(P)) XOR D→D;                                   |  |  |  |  |

|                               |         |          |                   | R(P)+1→R(P)                                        |  |  |  |  |

| AND                           | 2       | AND      | F2                | M(R(X)) AND D→D                                    |  |  |  |  |

| AND IMMEDIATE                 | 2       | ANI      | FA                | $M(R(P))$ AND $D \rightarrow D$ ;                  |  |  |  |  |

|                               |         |          |                   | R(P)+1→R(P)                                        |  |  |  |  |

| SHIFT RIGHT                   | 2       | SHR      | F6                | SHIFT D RIGHT, LSB(D)→DF,                          |  |  |  |  |

|                               |         |          |                   | 0→MSB(D)                                           |  |  |  |  |

| SHIFT RIGHT WITH CARRY        | 2       |          | 76▲               | SHIFT D RIGHT, LSB(D)→DF,                          |  |  |  |  |

| RING SHIFT RIGHT              | 2       | RSHR 🕻   |                   | DF-MSB(D)                                          |  |  |  |  |

|                               |         |          |                   |                                                    |  |  |  |  |

| SHIFT LEFT                    | 2       | SHL      | FE                | SHIFT D LEFT, MSB(D)→DF,                           |  |  |  |  |

|                               |         |          |                   | 0→LSB(D)                                           |  |  |  |  |

Previous contents of T register are destroyed during instruction execution.

AThis instruction is associated with more than one mnemonic. Each mnemonic is individually listed.

### Table I — INSTRUCTION SUMMARY (Cont'd)

|                                    | NO. OF  |            |             |                                        |

|------------------------------------|---------|------------|-------------|----------------------------------------|

|                                    | MACHINE |            | OP          |                                        |

| INSTRUCTION                        | CYCLES  | MNEMONIC   | CODE        | OPERATION                              |

| LOGIC OPERATIONS (Note 5) (Cont'd) |         |            |             |                                        |

| SHIFT LEFT WITH CARRY              | 2       | SHLC ן     | 7E <b>▲</b> | SHIFT D LEFT, MSB(D)→DF,               |

| RING SHIFT LEFT                    | 2       | RSHL }     |             | DF→LSB(D)                              |

| ARITHMETIC OPERATIONS (Note 5)     | L       | L          |             |                                        |

| ADD                                | 2       | ADD        | F4          | M(R(X))+D→DF, D                        |

| DECIMAL ADD                        | 4       | DADD       | 68F4        | M(R(X))+D→DF, D                        |

|                                    |         |            |             | DECIMAL ADJUST→DF, D                   |

| ADD IMMEDIATE                      | 2       | ADI        | FC          | M(R(P))+D→DF, D; R(P)+1→R(P)           |

| DECIMAL ADD IMMEDIATE              | 4       | DADI       | 68FC        | M(R(P))+D→DF,D                         |

|                                    |         |            |             | R(P)+1→R(P)                            |

|                                    |         |            |             | DECIMAL ADJUST→DF, D                   |

| ADD WITH CARRY                     | 2       | ADC        | 74          | M(R(X))+D+DF→DF, D                     |

| DECIMAL ADD WITH CARRY             | 4       | DADC       | 6874        | M(R(X))+D+DF→DF, D                     |

|                                    | 1       |            |             | DECIMAL ADJUST→DF, D                   |

| ADD WITH CARRY, IMMEDIATE          | 2       | ADCI       | 7C          | M(R(P))+D+DF→DF, D                     |

|                                    |         |            |             | R(P)+1→R(P)                            |

| DECIMAL ADD WITH CARRY,            | 4       | DACI       | 687C        | M(R(P))+D+DF→DF, D                     |

| IMMEDIATE                          |         |            |             | R(P)+1→R(P)                            |

|                                    |         |            |             | DECIMAL ADJUST→DF, D                   |

| SUBTRACT D                         | 2       | SD         | F5          | M(R(X))-D→DF, D                        |

| SUBTRACT D IMMEDIATE               | 2       | SDI        | FD          | $M(R(P))-D \rightarrow DF, D;$         |

|                                    |         |            |             | R(P)+1→R(P)                            |

| SUBTRACT D WITH BORROW             | 2       | SDB        | 75          | M(R(X))-D-(NOT DF)→DF, D               |

| SUBTRACT D WITH                    | 2       | SDBI       | 7D          | M(R(P))-D-(NOT DF)→DF, D;              |

| BORROW, IMMEDIATE                  |         |            |             | R(P)+1→R(P)                            |

| SUBTRACT MEMORY                    | 2       | SM         | F7          | D-M(R(X))→DF, D                        |

| DECIMAL SUBTRACT MEMORY            | 4       | DSM        | 68F7        | $D-M(R(X)) \rightarrow DF, D$          |

|                                    |         |            |             | DECIMAL ADJUST-DF. D                   |

| SUBTRACT MEMORY IMMEDIATE          | 2       | SMI        | FF          | D-M(R(P))→DF, D;                       |

|                                    | _       |            |             | R(P)+1→R(P)                            |

| DECIMAL SUBTRACT MEMORY.           | 4       | DSMI       | 68FF        | D-M(R(P))→DF, D                        |

| IMMEDIATE                          |         |            |             | $R(P)+1 \rightarrow R(P)$              |

|                                    |         |            |             | DECIMAL ADJUST-DF, D                   |

| SUBTRACT MEMORY WITH BORROW        | 2       | <b>SMB</b> | 77          | D-M(R(X))-(NOT DF)→DF, D               |

| DECIMAL SUBTRACT MEMORY            | 4       | DSMB       | 6877        | $D-M(R(X))-(NOT DF) \rightarrow DF, D$ |

| WITH BORROW                        |         |            |             | DECIMAL ADJUST-DF, D                   |

| SUBTRACT MEMORY WITH               | 2       | SMBI       | 7F          | D-M(R(P))-(NOT DF)→DF, D               |

| BORROW, IMMEDIATE                  | -       |            |             | B(P)+1→B(P)                            |

| DECIMAL SUBTRACT MEMORY            | 4       | DSBI       | 687F        | D-M(R(P))-(NOT DF)→DF, D               |

| WITH BORROW, IMMEDIATE             |         |            |             | R(P)+1→R(P)                            |

|                                    |         |            |             | DECIMAL ADJUST-DF, D                   |

| BRANCH INSTRUCTIONS SHORT BRA      | ANCH    | <b>.</b>   | ••••••      |                                        |

| SHORT BRANCH                       | 2       | BR         | 30          | M(R(P))→R(P).0                         |

| NO SHORT BRANCH (SEE SKP)          | 2       | NBR        | 38▲         | $R(P)+1 \rightarrow R(P)$              |

| SHORT BRANCH IF D = 0              | 2       | BZ         | 32          | IF D = 0, M(R(P))→R(P).0               |

|                                    | -       |            |             | ELSE R(P)+1→R(P)                       |

|                                    | 1       | 1          | 1           |                                        |

| SHORT BRANCH IF D NOT 0            | 2       | BNZ        | I 3A        | IF D NOT 0, M(R(P))→R(P).0             |

AThis instruction is associated with more than one mnemonic. Each mnemonic is individually listed.

Table I — INSTRUCTION SUMMARY (Cont'd)

| Table I - INSTRUCTION SUMMARY (Con | NO. OF  |          |           |                                                                 |

|------------------------------------|---------|----------|-----------|-----------------------------------------------------------------|

|                                    | MACHINE |          | OP        |                                                                 |

| INSTRUCTION                        | CYCLES  | MNEMONIC | CODE      | OPERATION                                                       |

| BRANCH INSTRUCTIONS - SHORT BRA    |         |          | CODE      | OFERATION                                                       |

| SHORT BRANCH IF DF = 1             | 2       | BDF      | 33▲       | IF DF = 1, M(R(P))→R(P).0                                       |

| SHORT BRANCH IF POS OR ZERO        | 2       | BPZ      |           | ELSE R(P)+1→R(P)                                                |

| SHORT BRANCH IF EQUAL OR           | 2       | BGE )    |           |                                                                 |

| GREATER                            | -       | 501      |           |                                                                 |

| SHORT BRANCH IF DF = 0             | 2       | BNF ר    | зв▲       | IF D = 0, M(R(P))→R(P).0                                        |

| SHORT BRANCH IF MINUS              | 2       | BM {     |           | ELSE R(P)+1→R(P)                                                |

| SHORT BRANCH IF LESS               | 2       | BL )     |           |                                                                 |

| SHORT BRANCH IF Q = 1              | 2       | BQ       | 31        | IF Q = 1. M(R(P))→R(P).0                                        |

|                                    | _       |          | •         | ELSE R(P)+1→R(P)                                                |

| SHORT BRANCH IF Q = 0              | 2       | BNQ      | 39        | $IF Q = 0, M(R(P)) \rightarrow R(P).0$                          |

|                                    | -       | 2.10     |           | ELSE R(P)+1→R(P)                                                |

| SHORT BRANCH IF EF1 = 1            | 2       | B1       | 34        | IF EF1 = 1, M(R(P))→R(P).0                                      |

| $\overline{(EF1 = V_{ss})}$        | -       | 5.       |           | ELSE R(P)+1→R(P)                                                |

| SHORT BRANCH IF EF1 = 0            | 2       | BN1      | 3C        | IF EF1 = 0, M(R(P))→R(P).0                                      |

| $(EF1 = V_{DD})$                   | _       | 2        |           | ELSE R(P)+1→R(P)                                                |

| SHORT BRANCH IF EF2 = 1            | 2       | B2       | 35        | IF EF2 = 1, M(R(P)) $\rightarrow$ R(P).0                        |

| $\overline{(EF2} = V_{SS})$        |         |          |           | ELSE R(P)+1→R(P)                                                |

| SHORT BRANCH IF EF2 = 0            | 2       | BN2      | 3D        | IF EF2 = 0, $M(R(P)) \rightarrow R(P).0$                        |

| $(EF2 = V_{DD})$                   | -       | DIVE     | 00        | ELSE R(P)+1 $\rightarrow$ R(P)                                  |

| SHORT BRANCH IF EF3 = 1            | 2       | B3       | 36        | IF EF3 = 1, M(R(P))→R(P).0                                      |

| $\overline{(EF3 = V_{ss})}$        | -       | 20       |           | ELSE R(P)+1→R(P)                                                |

| SHORT BRANCH IF EF3 = 0            | 2       | BN3      | 3E        | IF EF3 = 0, $M(R(P)) \rightarrow R(P).0$                        |

| $(EF3 = V_{DD})$                   | -       | Bito     |           | ELSE R(P)+1→R(P)                                                |

| SHORT BRANCH IF EF4 = 1            | 2       | B4       | 37        | $IF EF4 = 1, M(R(P)) \rightarrow R(P).0$                        |

| (EF4 = Vss)                        | -       | 2,       |           | ELSE R(P)+1 $\rightarrow$ R(P)                                  |

| SHORT BRANCH IF EF4 = 0            | 2       | BN4      | 3F        | $IF EF4 = 0, M(R(P)) \rightarrow R(P).0$                        |

| $(EF4 = V_{DD})$                   | _       | 5        | •         | ELSE R(P)+1 $\rightarrow$ R(P)                                  |

| SHORT BRANCH ON                    | 3       | BCI      | 683E*     | IF CI=1, M(R(P))→R(P).0; 0→CI                                   |

| COUNTER INTERRUPT                  | -       |          |           | ELSE R(P)+1→R(P)                                                |

| SHORT BRANCH ON                    | 3       | BXI      | 683F      | IF XI=1, M(R(P))→R(P).0                                         |

| EXTERNAL INTERRUPT                 | ů.      | 2711     |           | ELSE R(P)+1→R(P)                                                |

| BRANCH INSTRUCTIONS - LONG BRAN    | СН      |          |           |                                                                 |

| LONG BRANCH                        | 3       | LBR      | C0        | $M(B(B)) \rightarrow B(B) = 1$ $M(B(B)+1) \rightarrow B(B) = 0$ |

| NO LONG BRANCH                     | 3       | NLBR     | C0<br>C8▲ | M(R(P))→R(P).1, M(R(P)+1)→R(P).0<br>R(P)+2→R(P)                 |

| LONG BRANCH IF D = 0               | 3       | LBZ      | C0-       |                                                                 |

| LONG BRANCH IF D = 0               | 3       | LDZ      | 02        | IF D = 0, M(R(P))→R(P).1<br>M(P(P)+1)→P(P) 0                    |

|                                    |         |          |           | M(R(P)+1)→R(P).0<br>ELSE R(P)+2→R(P)                            |

| LONG BRANCH IF D NOT 0             | 3       | LBNZ     | CA        | IF D NOT 0, $M(R(P)) \rightarrow R(P).1$                        |

| LONG BRANCH IF D NOT 0             | 3       | LDINZ    | UA.       | $M(R(P)+1) \rightarrow R(P).0$                                  |

|                                    |         |          |           | $ELSE R(P)+2 \rightarrow R(P)$                                  |

|                                    | 3       | LBDF     | СЗ        |                                                                 |

| LONG BRANCH IF DF = 1              | 3       | LBUF     | 03        | IF DF = 1, M(R(P))→R(P).1<br>M(R(P)+1)→R(P).0                   |

|                                    |         |          |           |                                                                 |

| LONG BRANCH IF DF = 0              | 3       | LBNF     | СВ        | ELSE R(P)+2 $\rightarrow$ R(P)                                  |

| LONG BRANCH IF DF = 0              | 3       | LDINF    |           | IF DF = 0, $M(R(P)) \rightarrow R(P).1$                         |

|                                    |         |          |           | M(R(P)+1)→R(P).0<br>ELSE R(P)+2→R(P)                            |

| LONG BRANCH IF Q = 1               | 3       | LBQ      | C1        | F Q = 1, M(R(P))→R(P).1                                         |

|                                    | 5       |          |           | $M(R(P)+1) \rightarrow R(P).0$                                  |

|                                    |         |          |           |                                                                 |

| LONG BRANCH IF Q = 0               | 3       | LBNQ     | C9        | ELSE R(P)+2→R(P)<br>IF Q = 0, M(R(P))→R(P).1                    |

|                                    | , s     | LBNQ     |           |                                                                 |

|                                    |         |          |           | M(R(P)+1)→R(P).0<br>ELSE R(P)+2→R(P)                            |

| A                                  |         | L        | 1         |                                                                 |

AThis instruction is associated with more than one mnemonic. Each mnemonic is individually listed.

•IETQ cleared by LDC with the Counter/Timer stopped, reset of CPU, or BCI • (CI=1).

CI = Counter Interrupt, XI = External Interrupt.

2

Table I — INSTRUCTION SUMMARY (Cont'd)

| [                            | NO. OF  |          |               |                                                                |

|------------------------------|---------|----------|---------------|----------------------------------------------------------------|

|                              | MACHINE |          | OP            |                                                                |

| INSTRUCTION                  | CYCLES  | MNEMONIC | CODE          | OPERATION                                                      |

| SKIP INSTRUCTIONS            | •       |          |               |                                                                |

| SHORT SKIP (SEE NBR)         | 2       | SKP      | 38▲           | R(P)+1→R(P)                                                    |

| LONG SKIP (SEE NLBR)         | 3       | LSKP     | C8 <b>▲</b>   | R(P)+→R(P)                                                     |

| LONG SKIP IF D = 0           | 3       | LSZ      | CE            | IF D = 0, R(P)+2→R(P)                                          |

|                              |         |          |               | ELSE CONTINUE                                                  |

| LONG SKIP IF D NOT 0         | 3       | LSNZ     | C6            | IF D NOT 0, R(P)+2→R(P)                                        |

|                              |         |          |               | ELSE CONTINUE                                                  |

| LONG SKIP IF DF = 1          | 3       | LSDF     | CF            | IF DF = 1, R(P)+2→R(P)                                         |

|                              |         |          |               | ELSE CONTINUE                                                  |

| LONG SKIP IF DF = 0          | 3       | LSNF     | C7            | IF DF = 0, R(P)+2→R(P)                                         |

|                              |         |          |               | ELSE CONTINUE                                                  |

| LONG SKIP IF Q = 1           | 3       | LSQ      | CD            | IF Q = 1, R(P)+2→R(P)                                          |

|                              |         |          |               | ELSE CONTINUE                                                  |

| LONG SKIP IF Q = 0           | 3       | LSNQ     | C5            | IF Q = 0, R(P)+2→R(P)                                          |

|                              |         |          |               | ELSE CONTINUE                                                  |

| LONG SKIP IF MIE = 1         | 3       | LSIE     | cc            | IF MIE = 1, $R(P)+2 \rightarrow R(P)$                          |

| CONTROL INSTRUCTIONS         | 1       | <u>}</u> |               | ELSE CONTINUE                                                  |

| CONTROL INSTRUCTIONS         | r       | r        |               |                                                                |

| IDLE                         | 2       | IDL      | 00#           | STOP ON TPB; WAIT FOR DMA OR                                   |

|                              |         |          |               | INTERRUPT; BUS FLOATS                                          |

| NO OPERATION                 | 3       | NOP      | C4            | CONTINUE                                                       |

| SET P                        | 2       | SEP      | DN            | N→P                                                            |

| SET X                        | 2       | SEX      | EN            | N→X                                                            |

| SET Q                        | 2       | SEQ      | 7B            | 1→Q                                                            |

| RESET Q                      | 2       | REQ      | 7A            | 0→Q                                                            |

| PUSH X, P TO STACK           | 2       | MARK     | 79            | $(X, P) \rightarrow T; (X, P) \rightarrow M(R(2))$             |

|                              |         |          |               | THEN $P \rightarrow X$ ; $R(2) \rightarrow 1 \rightarrow R(2)$ |

|                              |         |          |               | ,                                                              |

| TIMER/COUNTER INSTRUCTIONS   |         |          |               |                                                                |

| LOAD COUNTER                 | 3       | LDC      | 6806°         | CNTR STOPPED: D→CH, CNTR:                                      |

| LOAD COUNTER                 |         |          | 0000          | 0=CI.CNTR RUNNING: D→CH                                        |

| GET COUNTER                  | 3       | GEC      | 6808          | CNTR→D                                                         |

|                              | 3       | STPC     | 6800          | STOP CNTR CLOCK:                                               |

| STOP COUNTER                 | 3       | SIFC     | 6600          | 0→÷32 PRESCALER                                                |

|                              |         | DTO      | 0001          | CNTR-1→CNTR                                                    |

| DECREMENT TIMER/COUNTER      | 3       | DTC      | 6801          |                                                                |

| SET TIMER MODE AND START     | 3       | STM      | 6807          | TPA÷32→ CNTR                                                   |

| SET COUNTER MODE 1 AND START | 3       | SCM1     | 6805          |                                                                |

| SET COUNTER MODE 2 AND START | 3       | SCM2     | 6803          |                                                                |

| SET PULSE WIDTH MODE 1       | 3       | SPM1     | 6804          | TPA.EF1→ CNTR CLOCK;                                           |

| AND START                    |         |          |               | EF1 🖌 STOPS COUNT                                              |

| SET PULSE WIDTH MODE 2       | 3       | SPM2     | 6802          | TPA.EF2 CNTR CLOCK;                                            |

| AND START                    | 1       |          |               | EF2 🖌 STOPS COUNT                                              |

| ENABLE TOGGLE Q              | 3       | ETQ      | 6809 <b>•</b> | IF CNTR = 01 • NEXT                                            |

|                              |         |          |               | CNTR CLOCK ✓ : Q→Q                                             |

▲This instruction is associated with more than one mnemonic. Each mnemonic is individually listed

#An IDLE instruction initiates an S1 cycle All external signals, except the oscillator, are stopped on the low-to-high transition of TPB. All outputs remain in their previous states, MRD, MWR, EMS are set to a logic '1' and the data bus floats. The processor will continue to IDLE until an I/O request (INTERRUPT, DMA-IN, or DMA-OUT) is activated. When the request is acknowledged, the IDLE cycle is terminated and the I/O request is serviced, and the normal operation is resumed. (To respond to an INTERRUPT during an IDLE, MIE and either CIE or XIE must be enabled).

• ETQ cleared by LDC with the Counter/Timer stopped, reset of CPU or BCI · (CI = 1)

CI = Counter Interrupt, XI = External Interrupt.

### Table I — INSTRUCTION SUMMARY (Cont'd)

|                                                                                                                            | NO. OF                |                                 |                                    |                                                                                                                                                                                                                                                                                  |

|----------------------------------------------------------------------------------------------------------------------------|-----------------------|---------------------------------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INSTRUCTION                                                                                                                | MACHINE<br>CYCLES     | MNEMONIC                        | OP<br>CODE                         | OPERATION                                                                                                                                                                                                                                                                        |

| INTERRUPT CONTROL                                                                                                          |                       |                                 |                                    |                                                                                                                                                                                                                                                                                  |

| EXTERNAL INTERRUPT ENABLE<br>EXTERNAL INTERRUPT DISABLE<br>COUNTER INTERRUPT ENABLE<br>COUNTER INTERRUPT DISABLE<br>RETURN | 3<br>3<br>3<br>3<br>2 | XIE<br>XID<br>CIE<br>CID<br>BET | 680A<br>680B<br>680C<br>680D<br>70 | 1→XIE<br>0→XIE<br>1→CIE<br>0→CIE<br>M(R(X))→X, P;                                                                                                                                                                                                                                |

| DISABLE                                                                                                                    | 2                     | DIS                             | 71                                 | R(X)+1→R(X); 1→MIE<br>M(R(X)→X, P;<br>R(X)+1→R(X); 0→MIE                                                                                                                                                                                                                         |

| SAVE<br>SAVE T, D, DF                                                                                                      | 2<br>6                | SAV<br>DSAV                     | 78<br>6876                         | $\begin{array}{l} (X_{1}) + T \rightarrow (R(X)) \\ T \rightarrow (R(X)) \\ R(X) - 1 \rightarrow R(X), T \rightarrow M(R(X)), \\ R(X) - 1 \rightarrow R(X), D \rightarrow M(R(X)), \\ R(X) - 1 \rightarrow R(X), SHIFT D \\ RIGHT WITH CARRY, D \rightarrow M(R(X)) \end{array}$ |

| INPUT-OUTPUT BYTE TRANSFER                                                                                                 |                       |                                 |                                    |                                                                                                                                                                                                                                                                                  |

| OUTPUT 1                                                                                                                   | 2                     | OUT 1                           | 61                                 | $M(R(X)) \rightarrow BUS; R(X) + 1 \rightarrow R(X);$                                                                                                                                                                                                                            |

| OUTPUT 2                                                                                                                   | 2                     | OUT 2                           | 62                                 | N LINES = 1<br>M(R(X))→BUS; R(X)+1→R(X);                                                                                                                                                                                                                                         |

| OUTPUT 3                                                                                                                   | 2                     | ОПТ 3                           | 63                                 | N LINES = 2<br>M(R(X))→BUS; R(X)+1→R(X);                                                                                                                                                                                                                                         |

| OUTPUT 4                                                                                                                   | 2                     | OUT 4                           | 64                                 | N LINES = 3<br>M(R(X))→BUS; R(X)+1→R(X);<br>N LINES = 4                                                                                                                                                                                                                          |

| OUTPUT 5                                                                                                                   | 2                     | OUT 5                           | 65                                 | N LINES - 4<br>M(R(X))→BUS; R(X)+1→R(X);<br>N LINES = 5                                                                                                                                                                                                                          |

| OUTPUT 6                                                                                                                   | 2                     | OUT 6                           | 66                                 | N LINES = 5<br>M(R(X))→BUS; R(X)+1→R(X);<br>N LINES = 6                                                                                                                                                                                                                          |